Semiconductor package device

A packaging device and semiconductor technology, which is applied in the direction of semiconductor devices, semiconductor/solid-state device parts, electric solid-state devices, etc., can solve the problems of insufficient internal space of the package body and the inability to use small semiconductor chips in the voltage regulator, and achieve the goal of reducing space Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The invention can be embodied in many different forms. Representative embodiments are shown in the drawings and described in detail herein. The present disclosure contains examples or illustrations of principles, and the disclosed embodiments of the invention are not to be limited to the illustrated embodiments.

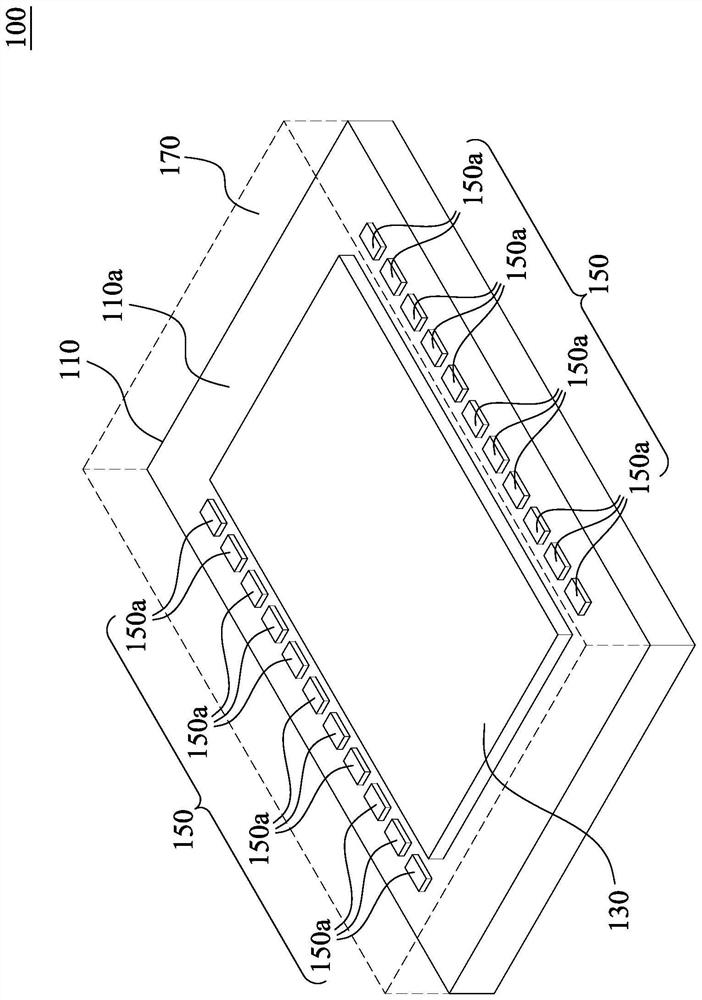

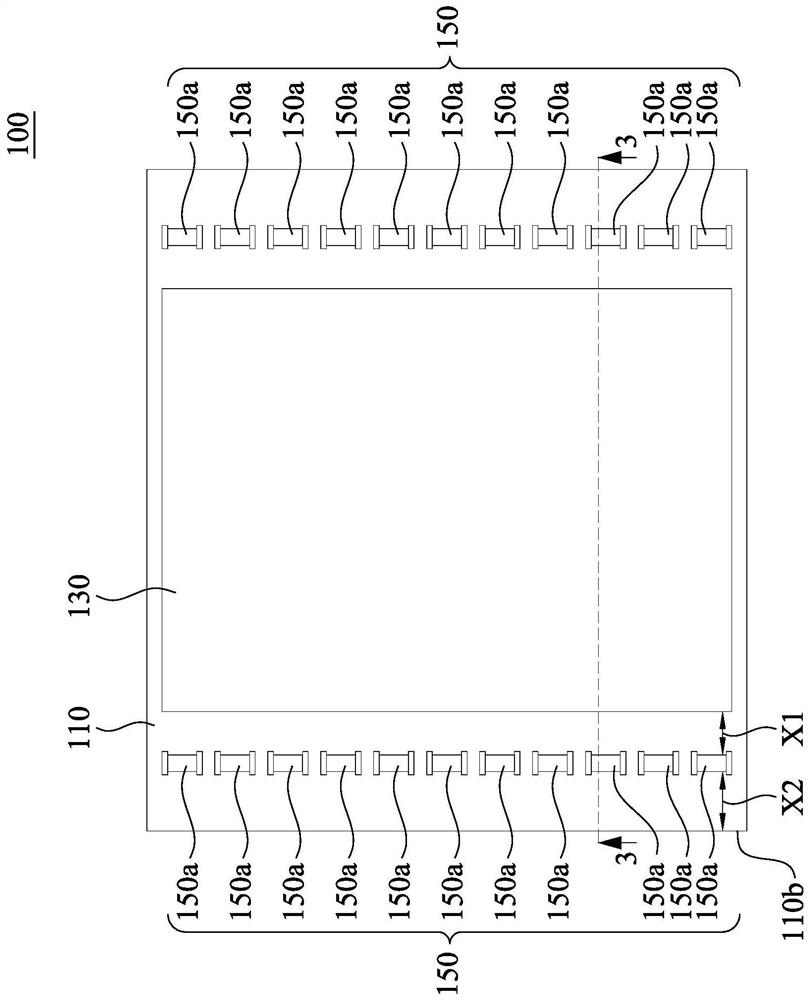

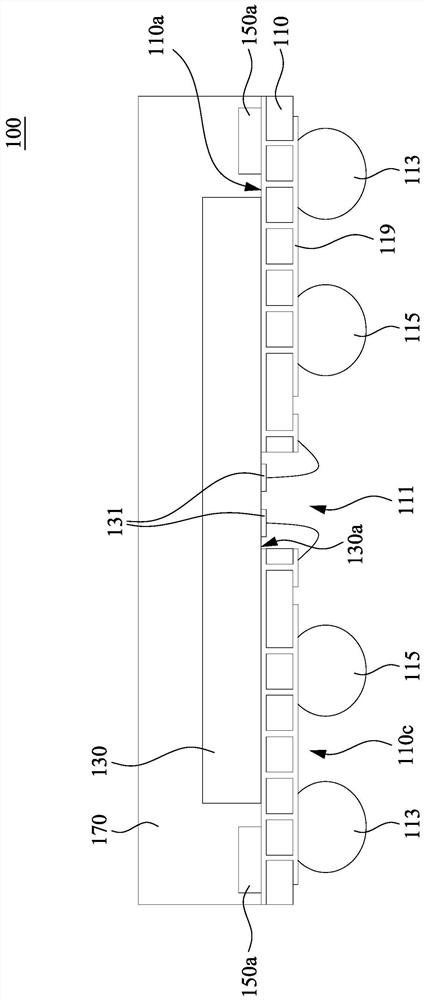

[0031] Please refer to Figure 1 to Figure 4 . figure 1 It is a three-dimensional schematic view of the semiconductor packaging device 100 . figure 2 shown as figure 1 , a schematic top view of the semiconductor packaging device 100 . image 3 shown as figure 2 , the cross-sectional view of the semiconductor package device 100 is drawn along the section line 3-3. Figure 4 shown as figure 1 , a circuit diagram of the semiconductor package device 100 . In one embodiment of the present invention, the semiconductor package device 100 includes a substrate 110 , a memory chip 130 , and a decoupling array 150 . The substrate 110 has an upper surface 110a,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com