Integrated circuit non-pessimistic path analysis method for GPU accelerated calculation

An integrated circuit and path analysis technology, which is applied in computing, computer-aided design, electrical digital data processing, etc., can solve problems such as limiting the application of static timing analysis, low computing efficiency, and poor parallel ability, so as to reduce data transmission overhead and improve The effect of parallelism and efficiency improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] Below in conjunction with accompanying drawing, through embodiment, further illustrate the present invention.

[0042] The present invention provides an integrated circuit non-pessimistic path analysis method for GPU-accelerated computing. Based on the non-pessimistic path analysis algorithm at the forefront of academia, it innovatively introduces algorithms and data structures for the core steps in the non-pessimistic path analysis. Price transformation, so that it can adapt to the calculation model and architecture of GPU, and then can complete the intensive calculation in non-pessimistic timing analysis in parallel on multiple GPUs, reducing the calculation cost of non-pessimistic path analysis, so that it can be used in the chip design automation process in a wider range of applications.

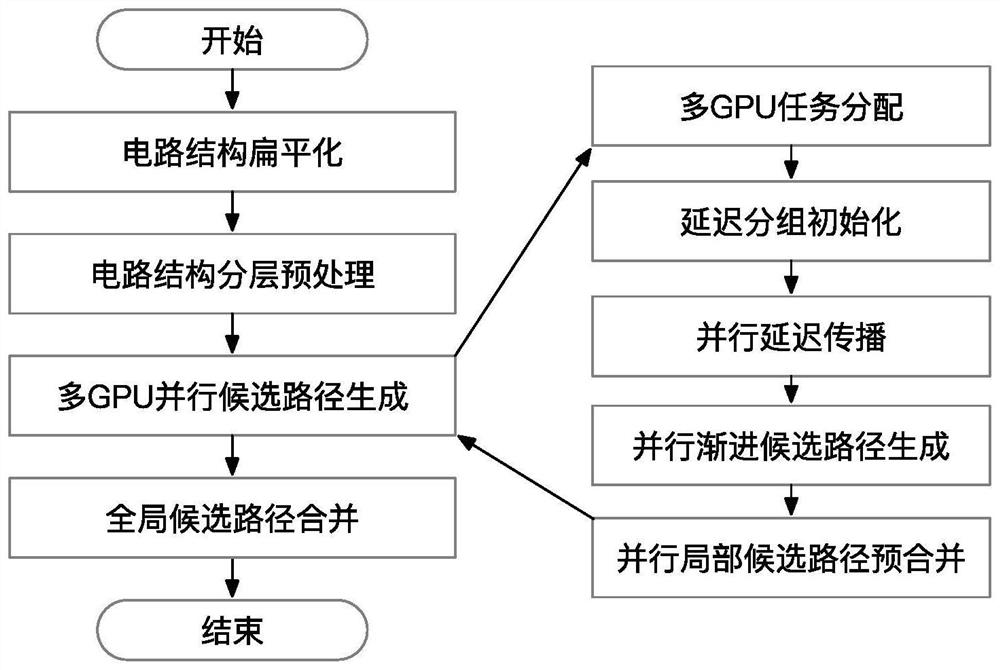

[0043] The method steps of the present invention for processing no-pessimistic path analysis are as follows: figure 1 as shown, figure 1 The solid arrows in indicate the process...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More