Coarse-grained reconfigurable array parallel instruction configuration device and processor

A configuration device and coarse-grained technology, applied in the direction of concurrent instruction execution, machine execution device, electrical digital data processing, etc., can solve problems such as unacceptable circuit complexity, and achieve the goal of increasing instruction transmission speed, reducing hardware cost, and reducing the number Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] In order to make the purpose, technical solution and advantages of the present invention clearer and clearer, the present invention will be further described below in conjunction with the accompanying drawings and specific embodiments. Apparently, the described embodiments are only some of the embodiments of the present invention, but not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

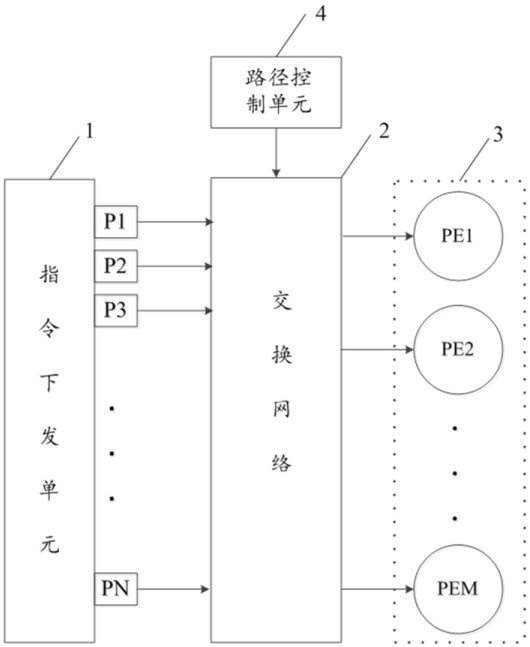

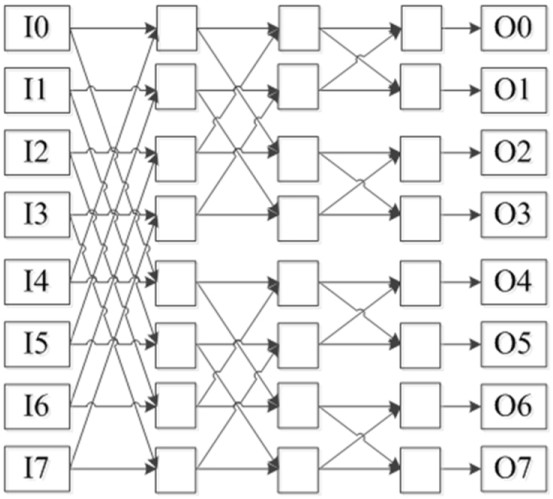

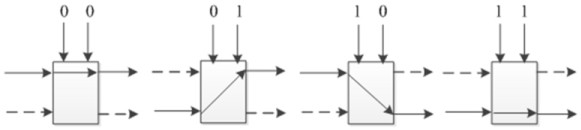

[0036] figure 1 It is a block diagram of a coarse-grained reconfigurable array parallel instruction configuration device according to an embodiment of the present invention. The device includes an instruction issuing unit 1, a processing unit 3, a switching network 2, and a path control unit 4; the switching network 2 adopts a butterfly structure , there are n input ports and n output ports, the N output ports o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More