Direct current offset calibration system and method

A technology of DC offset and calibration system, applied in control/regulation system, transmission system, adjusting electrical variables, etc., can solve the problem of low-pass filter circuit occupying device area, affecting the working speed of high-speed receiver circuit, etc., to eliminate DC effect of dissonance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] Below in conjunction with accompanying drawing, structural principle and working principle of the present invention are specifically described:

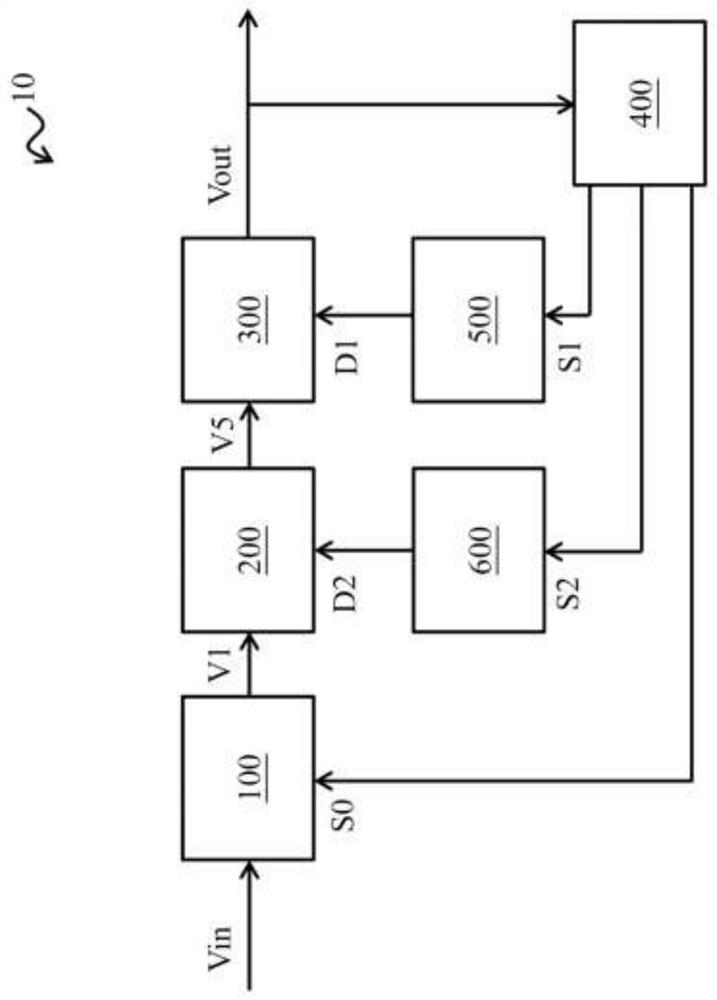

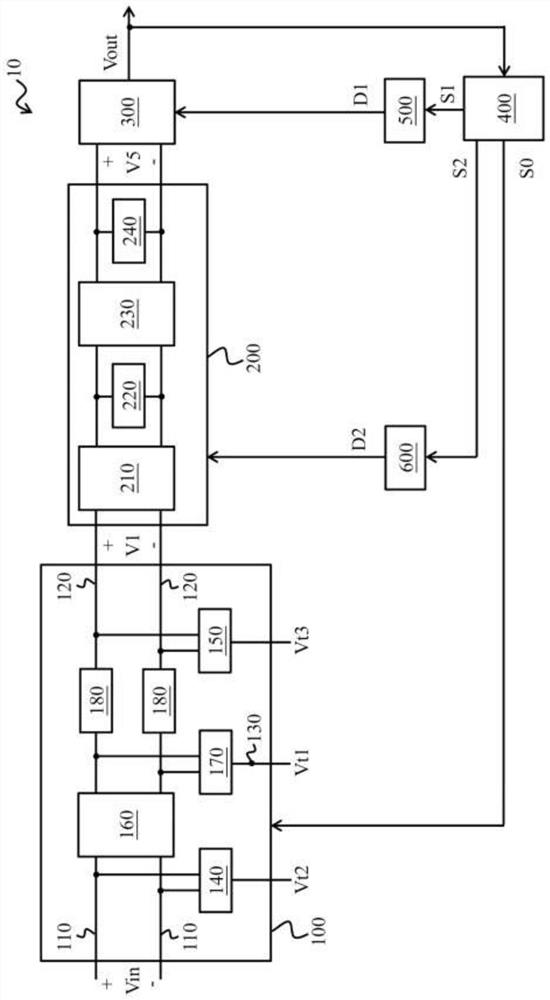

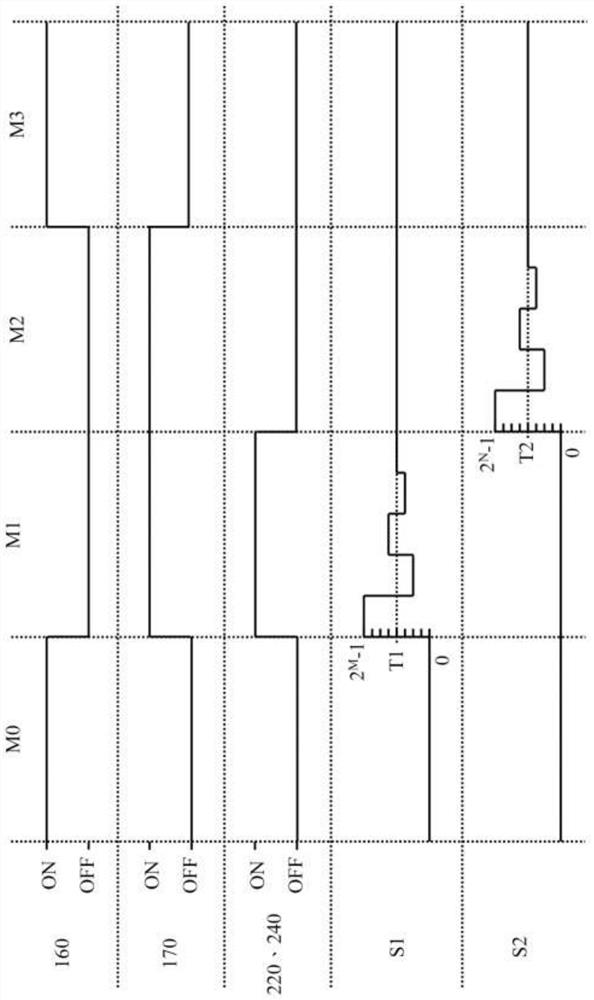

[0029] figure 1 is a schematic block diagram of a DC offset calibration system 10 according to some embodiments of the present invention, figure 2 is a schematic circuit diagram of a DC offset calibration system 10 according to some embodiments of the present invention, image 3 It is a timing diagram of the DC offset calibration system 10 of some embodiments of the present invention. Please also see figure 1 , figure 2 and image 3 , in some embodiments, the DC offset calibration system 10 is arranged at the receiver end to process the differential input signal Vin, and the DC offset calibration system 10 is suitable for operating in one of the working mode M3, the first calibration mode M1 and the second calibration M2 mode . The DC offset calibration system 10 includes a matching circuit 100 , an equalization circui...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More