FPGA code stream data compression and decompression method

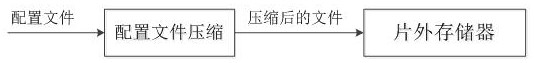

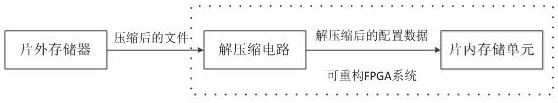

A compression method and decompression technology, applied in the field of FPGA applications, can solve problems such as the inability to reduce configuration time, reduce storage size and data transmission time, and reduce compression rate, so as to reduce the possibility of being cracked, improve configuration efficiency, and improve configuration speed effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

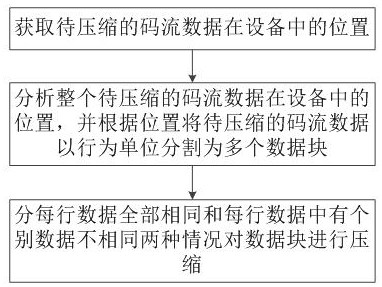

[0036] Such as image 3 As shown, the compression method of the FPGA code stream data of the present embodiment comprises the following steps:

[0037] Step 1. Obtain the location of the code stream data to be compressed in the device;

[0038] Step 2, analyzing the position of the entire code stream data to be compressed in the device, and dividing the code stream data to be compressed into multiple data blocks in line units according to the position;

[0039] Step 3: The data blocks are compressed according to two cases: all the data in each row are the same and some data in each row are different.

[0040] In this embodiment, the specific method for compressing the data block is divided into two cases where the data in each row is all the same and the data in each row is different as described in step 3:

[0041] Analyze whether the data of each row of data blocks is all the same. When the data of each row of data blocks is all the same, the method of skipping the entire ...

Embodiment 2

[0047] Such as Figure 4 As shown, the decompression method of the FPGA code stream data of the present embodiment, the method is: whether to enable full compression or segmented partial compression in the analysis code stream data, when enabling full compression, adopt the partial decompression method to decompress Compression; when segmented partial compression is enabled, the segmented partial decompression method is used for decompression;

[0048] Among them, the method of decompressing by using the partial decompression method is: analyzing the keyword representing one row data block and the keywords representing several row data blocks in the code stream data, and controlling the configuration according to the keyword and the decompression protocol. skipped addresses and data;

[0049] Wherein, the decompression method using segmented partial decompression method is: parsing some special keywords in the code stream data, and configuring corresponding data and addresses...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More