Convolution hardware acceleration method and convolution hardware acceleration circuit

A hardware acceleration and convolution technology, applied in the field of convolutional neural network and chip design, to achieve the effect of reducing repeated reading, improving utilization, and avoiding repeated reading

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

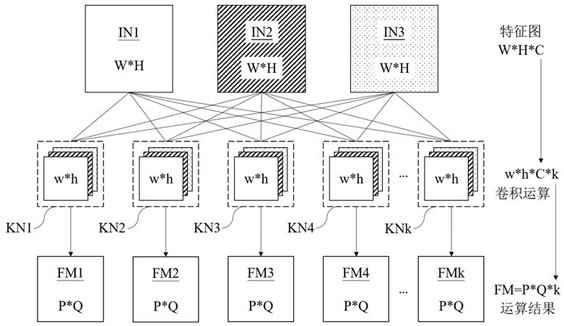

[0032] figure 1 A schematic diagram of the convolution operation. The color coding methods of digital images include RGB, YUV, YCbCr and so on. Taking RGB color coding as an example, each pixel in a digital image can be composed of red sub-pixels, green sub-pixels and blue sub-pixels; that is, if the resolution or resolution of a digital image is W*H square pixels, then the digital image can be represented by C two-dimensional matrices. For example, a digital image can be composed of multiple feature maps IN1, IN2, and IN3, and the total data volume of the digital image is W*H*C, where W is the width of the feature map, and H is the height of the feature map , C is the dimension (or number of channels).

[0033] Assuming that a digital image needs to be convolved with a set of convolution kernels (kernel), similarly, each of a set of convolution kernels can be represented by C two-dimensional matrices, then a set of convolution kernels The total amount of data is w*h*C*k, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More