Compiler support method for alleviating false sharing problem

A compiler and false sharing technology, applied in the field of high-performance computing, can solve the problems of false sharing, the cache structure does not guarantee horizontal consistency, etc., to achieve the effect of increasing the interval, reducing the false sharing problem, and improving the write-back efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

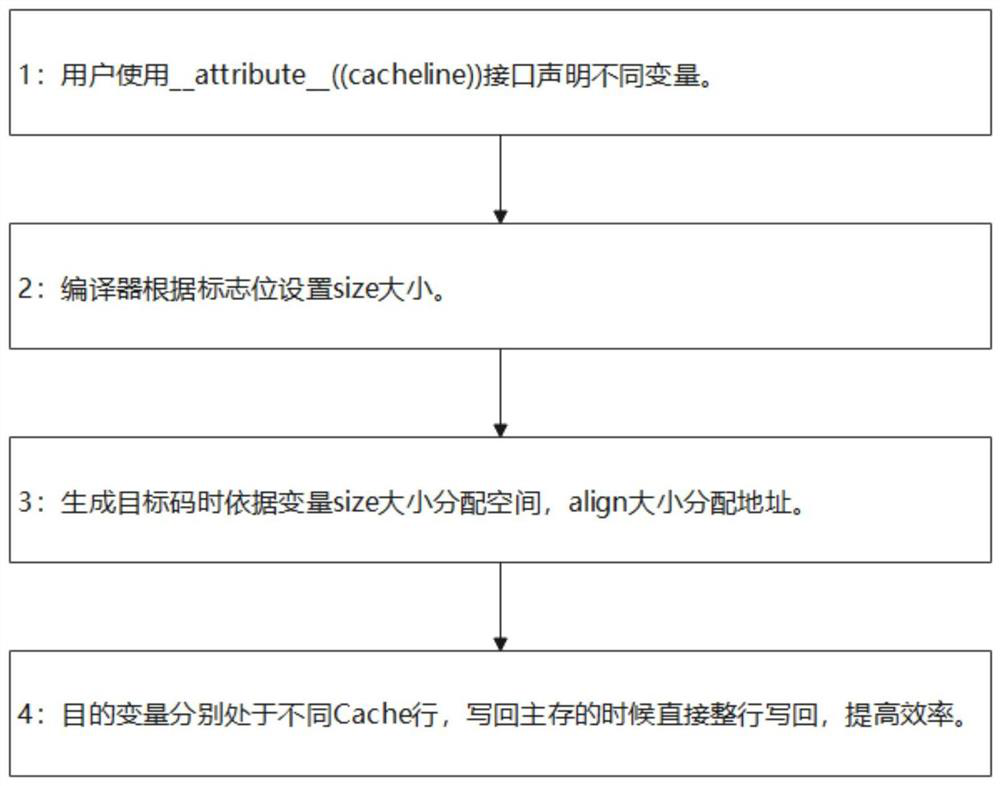

[0018] Embodiment: The present invention provides a compiler support method for alleviating the false sharing problem, which specifically includes the following steps:

[0019] The __attribute__((cacheline)) interface based on configuration, the __attribute__((cacheline)) interface is used for variables that may have false sharing;

[0020] Include the following steps:

[0021] S1. In the program, the user uses the __attribute__((cacheline)) interface for variable declarations that may be falsely shared between multi-threaded caches, and the compiler performs the next operation on the variables using this interface;

[0022] S2. The compiler sets the flag bit cacheline in the base class tree_decl_common structure of the declared tree node to 1, sets align to the size of the cache line, and sets user_align in the base class tree_base structure of tree_decl_common to 1;

[0023] S3. When the compiler generates the assembly code of the variable, it determines the tree_decl_commo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More