Neural network processing-oriented data output circuit structure scheduled according to priorities

A priority scheduling, neural network technology, applied in the field of data output circuit structure, can solve problems such as large clock delay, and achieve the effect of ensuring orderly writeback, improving data writeback efficiency, and improving transmission efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

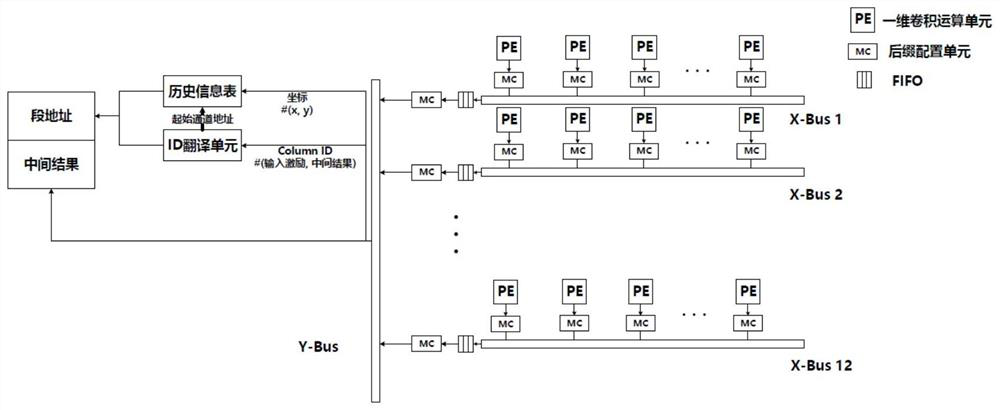

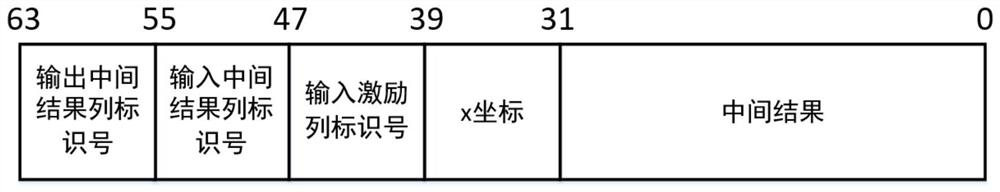

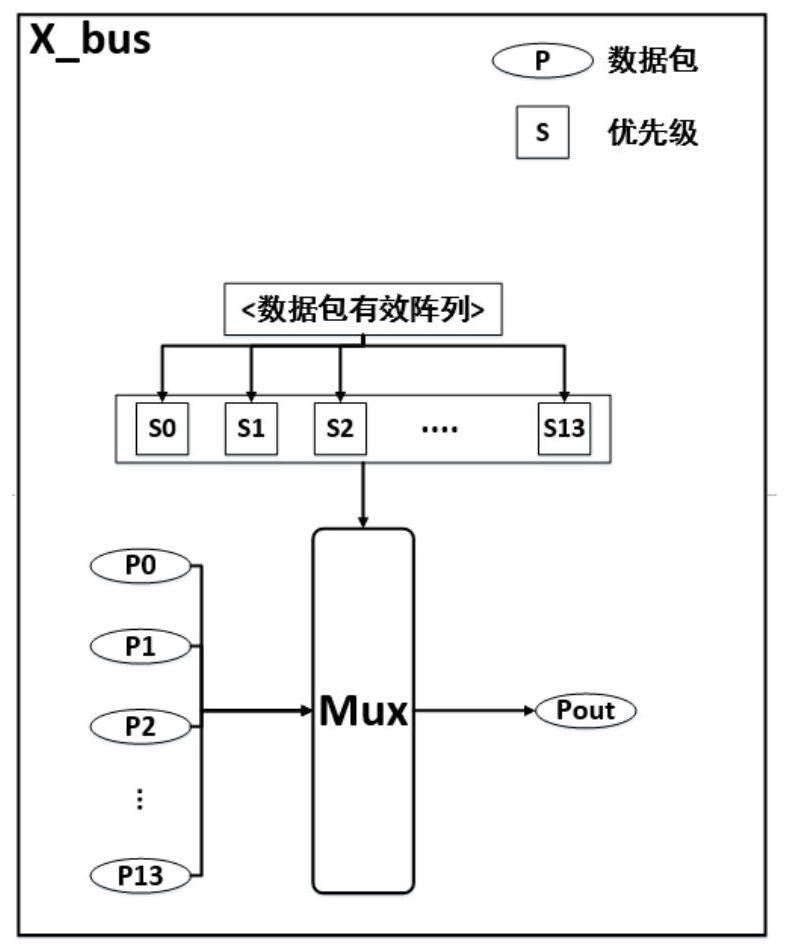

[0026] Embodiment 1: The basic block diagram of the data output circuit structure scheduled according to the priority is as follows figure 1 shown. The workflow of this design is as follows: the input is the intermediate result from the operation array, and the x-coordinate and column identification number are added through the suffix hive connected to it. In each clock cycle, the X-bus unit module 1 will traverse all the calculation units. Once the calculation unit generates intermediate results, it will accept the intermediate results of the calculation units according to the data priority and send the intermediate results to the suffix configuration connected to it. Unit module 3, add the y coordinate and row identification number. If the multi-line convolution operation unit produces results at the same time, the Y-bus unit module 2 transmits the intermediate result data packet on the X-bus according to the preset data priority, and sends the data packet to the address ca...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More