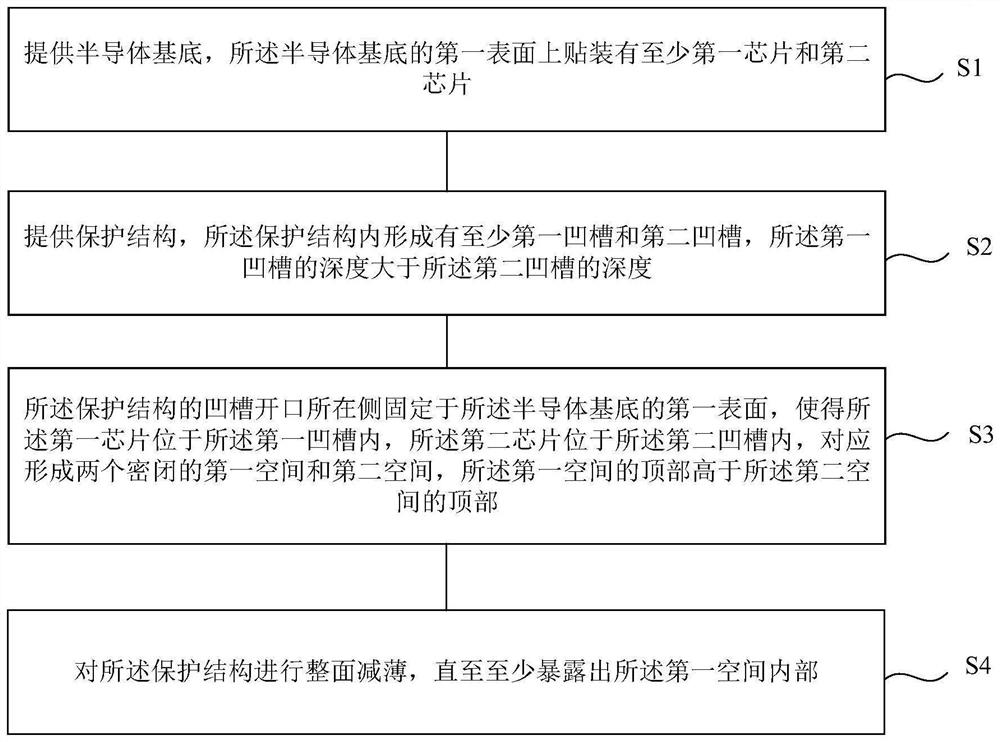

Chip packaging structure, forming method and electronic equipment

A chip packaging structure, chip technology, applied in the direction of circuits, electrical components, phonon exciters, etc., can solve the problems that the epoxy resin cavity cannot meet the airtightness requirements, low integration, large substrate packaging volume, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

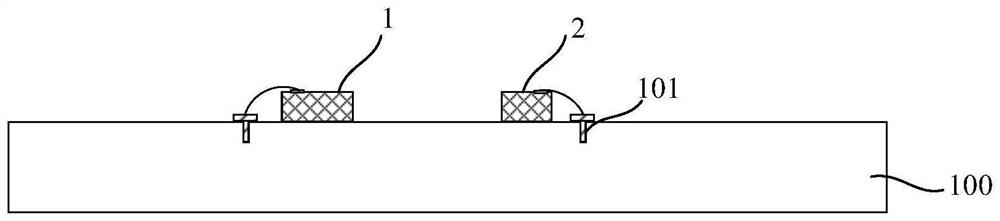

[0031] As mentioned in the background technology, in the prior art, epoxy resin cofferdams are usually used to form a specific airtight space on the PCB substrate during packaging, and a specific exposure area is formed through a glass cover to meet the airtightness of the chip. sex and exposure requirements. The chip integration realized by the substrate process has a large package volume and a low integration level, and the epoxy resin cavity cannot meet the airtightness requirements. To this end, the inventor proposes a new method for forming a chip packaging structure, through a semiconductor substrate and a protective structure, the protective structure includes at least a first space and a second space, the first space is a first groove, and the The second space is an airtight cavity, the first depth from the bottom of the first groove to the opening is greater than the second depth from the bottom to the top in the airtight cavity; the first chip is located in the first...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More