Processing unit task scheduling method and device

A processing unit and task scheduling technology, applied in the directions of multi-program device, program startup/switching, resource allocation, etc., can solve the problems of underutilization of computing resources, unbalanced load, underutilization of dynamic performance parameters, etc., to avoid Local optimal scheduling, improving the effect of improving execution efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments, wherein the schematic embodiments and descriptions are only used to explain the present invention, but are not intended to limit the present invention.

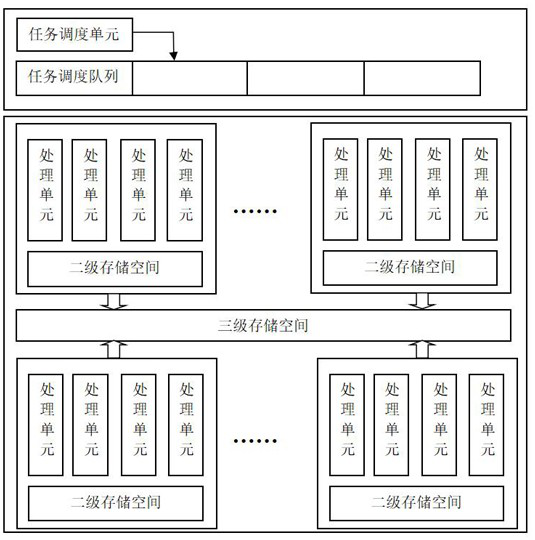

[0029] as attached figure 1 As shown, the processing unit task scheduling device provided by the present invention includes a plurality of processing unit blocks, task scheduling units, and task scheduling queues; wherein: the processing unit block includes one or more processing units, and each processing unit is internally provided with a level storage space; the one or more processing units share level two storage space; multiple processing unit blocks share level three storage space; attached figure 1 In , the number of processing units and the number of processing unit blocks are examples;

[0030] Preferably: the tertiary storage space is Cache space or main memory space;

[0031] Pref...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More