Formation method of semiconductor structure

A semiconductor and sidewall structure technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of threshold voltage drift, poor uniformity of contact holes, inconsistent metal gate resistance, etc., and achieve high uniformity , high uniformity, good effect of high consistency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] It should be noted that the "surface" and "upper" in this specification are used to describe the relative positional relationship in space, and are not limited to direct contact.

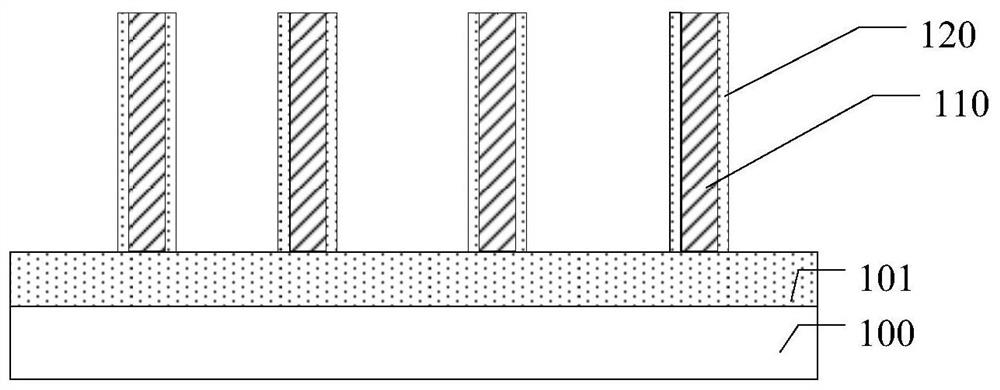

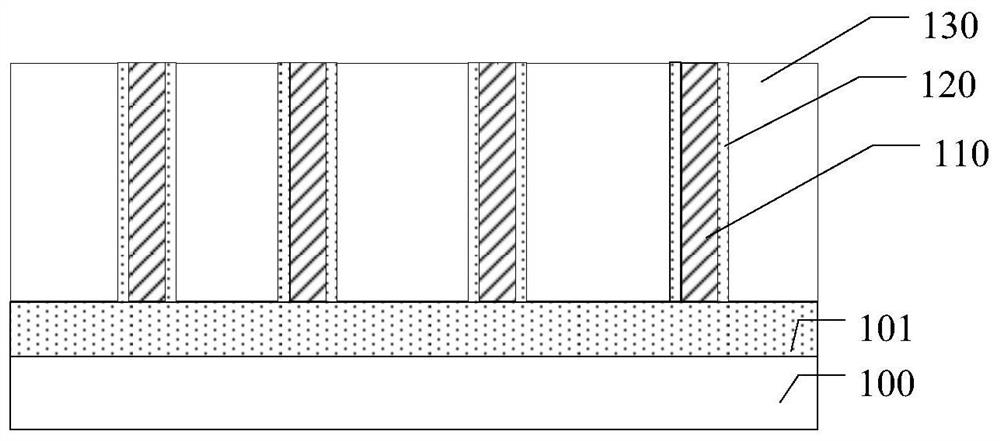

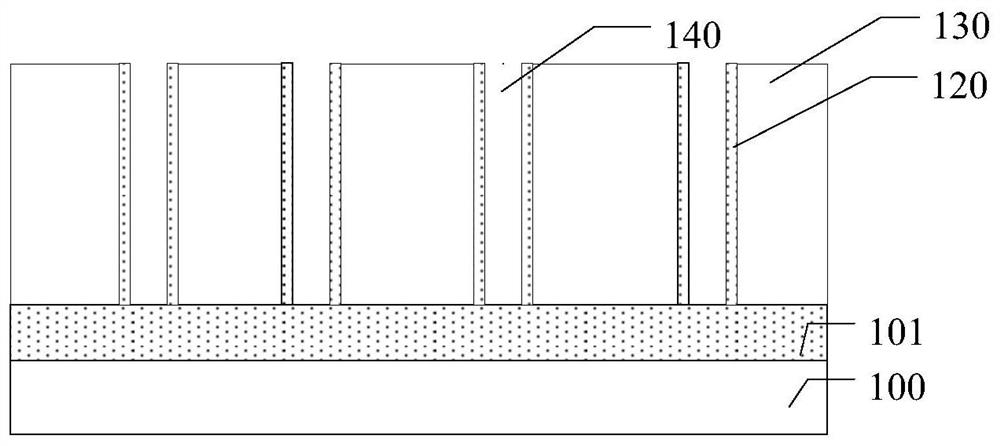

[0038] Firstly, the reason for the poor performance of the existing semiconductor structure will be described in detail with reference to the accompanying drawings. Figure 1 to Figure 4 It is a structural schematic diagram of each step of a method for forming a conventional semiconductor structure.

[0039] Please refer to figure 1 , providing a base, the base includes a substrate 100, a fin 101 located on the surface of the substrate 100, and an isolation layer (not shown in the figure), the isolation layer covers part of the surface of the side wall of the fin 101, and the base has The dummy gate structure 110 across the fin portion 101 has sidewall structures 120 on both sides of the dummy gate structure 110 .

[0040] Please refer to figure 2 , forming a dielectric layer 130 on the s...

PUM

| Property | Measurement | Unit |

|---|---|---|

| relative permittivity | aaaaa | aaaaa |

| relative permittivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More