Server time synchronization device and method and server

A server time and synchronization device technology, applied in the server field, can solve problems such as error-prone, cost-increased, and timing is not easy to control, so as to avoid conflict risks, improve user experience, and simple principle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

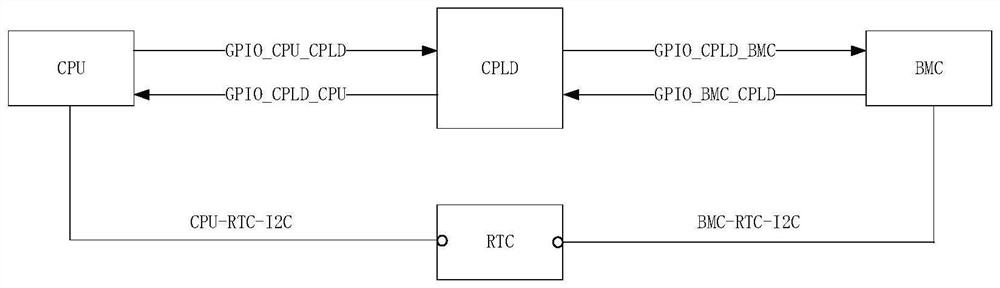

[0038] Embodiment 1 of the present invention proposes a server time synchronization device. The present invention realizes the link switching between the central processing unit and the clock chip and the substrate management controller and the clock chip through a certain logic control signal, so as to ensure that both the central processing unit and the substrate manager can read the time of the clock chip when needed, and Both the CPU and the BMC can actively re-synchronize after the clock chip time is updated.

[0039] The device includes a first control module, a programmable logic chip, a second control module and a clock chip; the programmable logic chip is connected to the first control module and the second control module respectively; the clock chip is also connected to the first control module and the second control module respectively The two control modules are connected in communication; the first control module is used to issue the first instruction for operatin...

Embodiment 2

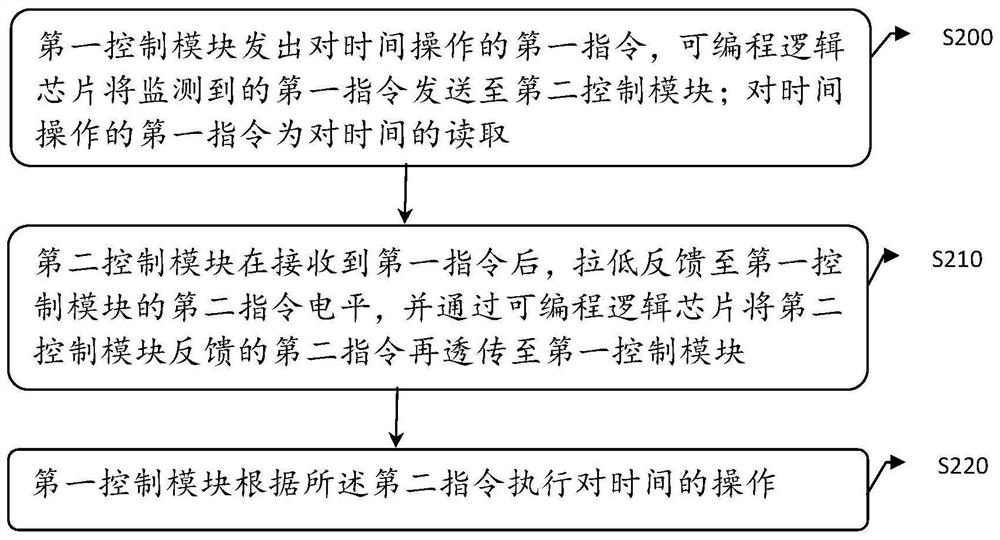

[0055] Based on the server time synchronization device proposed in Embodiment 1 of the present invention, Embodiment 2 of the present invention also proposes a server time synchronization method, such as figure 2 It is a flow chart of the time reading operation issued by the first control module of the server time synchronization method in Embodiment 2 of the present invention. In this process, the first control module issues a read operation on the time.

[0056] In step S200, the first control module issues a first instruction for time operation, and the programmable logic chip sends the monitored first instruction to the second control module; the first instruction for time operation is to read time;

[0057] In step S210, after receiving the first instruction, the second control module pulls down the level of the second instruction fed back to the first control module, and transmits the second instruction fed back by the second control module through the programmable logi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More