Constructed integrated circuit with balance structure

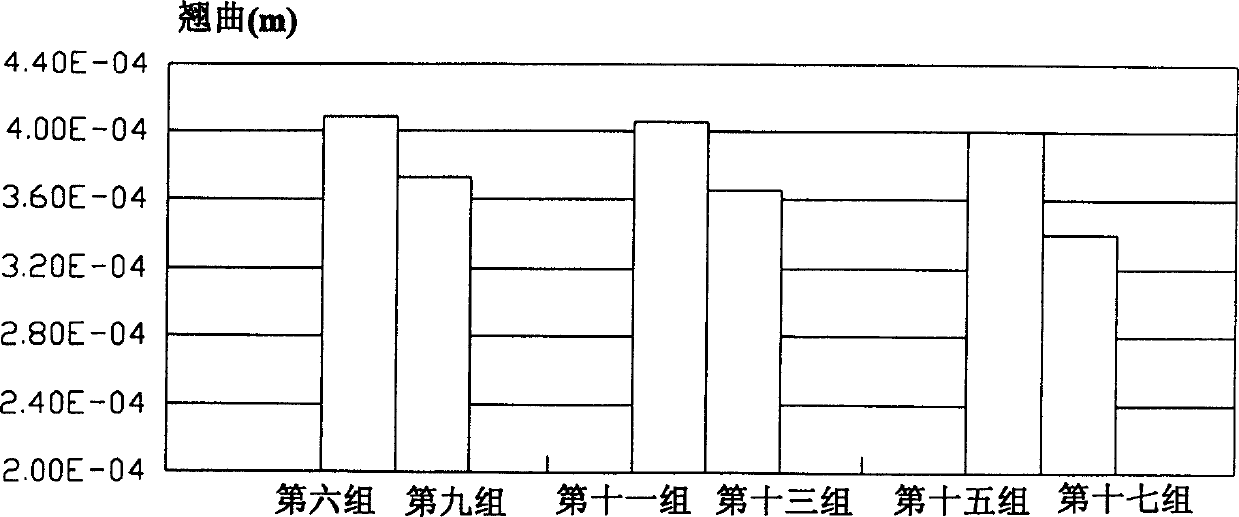

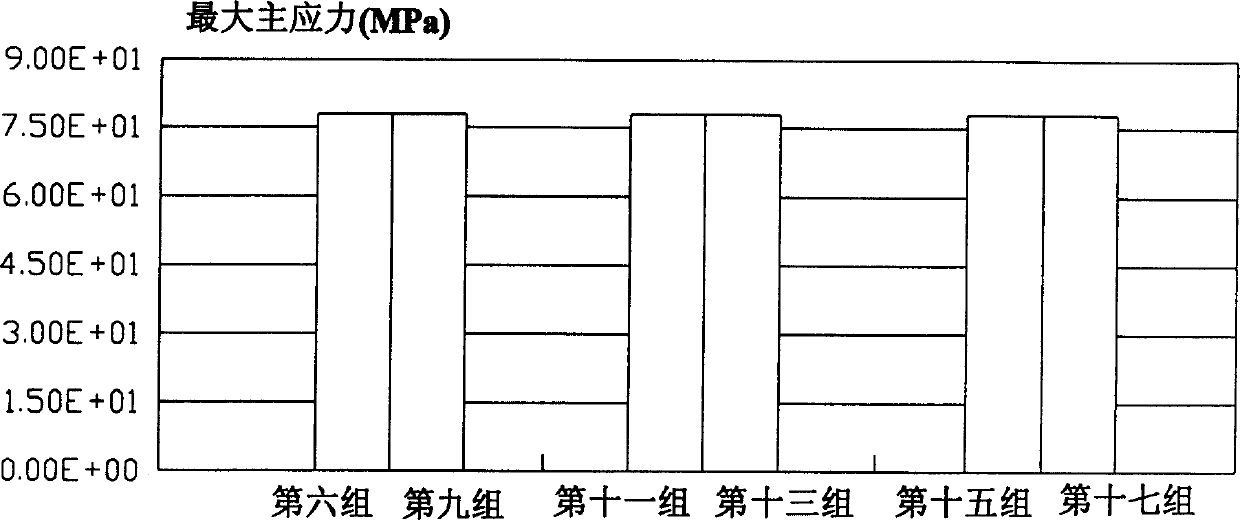

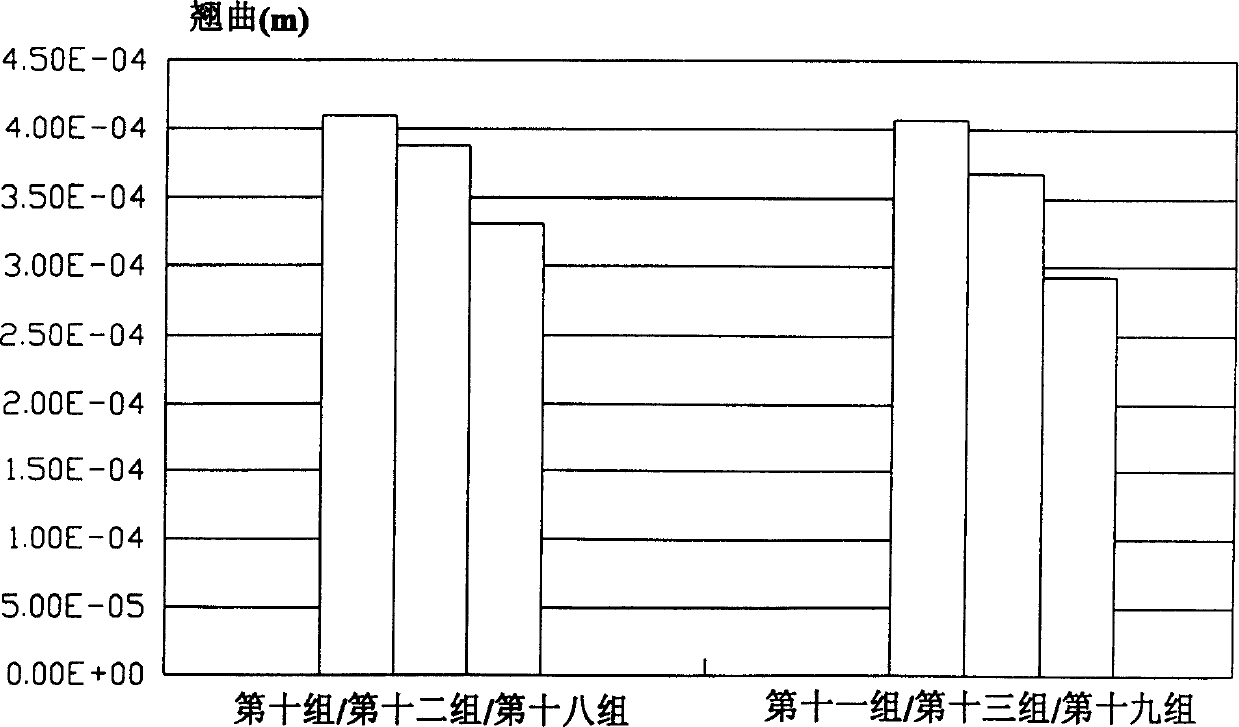

A technology of integrated circuits and balanced structures, applied in circuits, electrical components, electrical solid-state devices, etc., can solve the problems of thermal stress concentration, uneven stress distribution, warpage of assembled integrated circuits, etc., to reduce the volume and avoid thermal stress. The effect of concentration, improving stability and yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Example Embodiment

The specific implementation of the present invention will be described in detail below in conjunction with the drawings and embodiments.

The present invention provides a balanced structure installed in a packaged integrated circuit, which utilizes balanced modules arranged on a substrate to reduce the degree of warpage of the packaged integrated circuit. Referring to Figure 1 and Figure 2, this is a schematic diagram of the integrated circuit before the process of assembling the potting mold mixture. The chips 100 and 102 can be connected to the substrate by a plurality of solder bumps 110 (refer to FIG. 1). The chips 100 and 102 can also be bonded to the substrate 120 by the bonding layers 150 and 152, and then go through a wire bonding process to connect the chips 100 and 102 to the substrate 120 by a plurality of metal wires 154 (refer to FIG. 2 ). Referring to Figures 3 and 4, this is a schematic diagram of an integrated circuit that connects a plurality of balance modules on ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com