Method for producing high accuracy delayed signal by using multiple signal source and its device

A delay signal and multiple signal technology, applied in the direction of generating/distributing signals, can solve the problems of low error range, insurmountable, time is not easy to grasp, etc., achieve high accuracy, solve the problem of unsynchronized, adjustable delay time Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

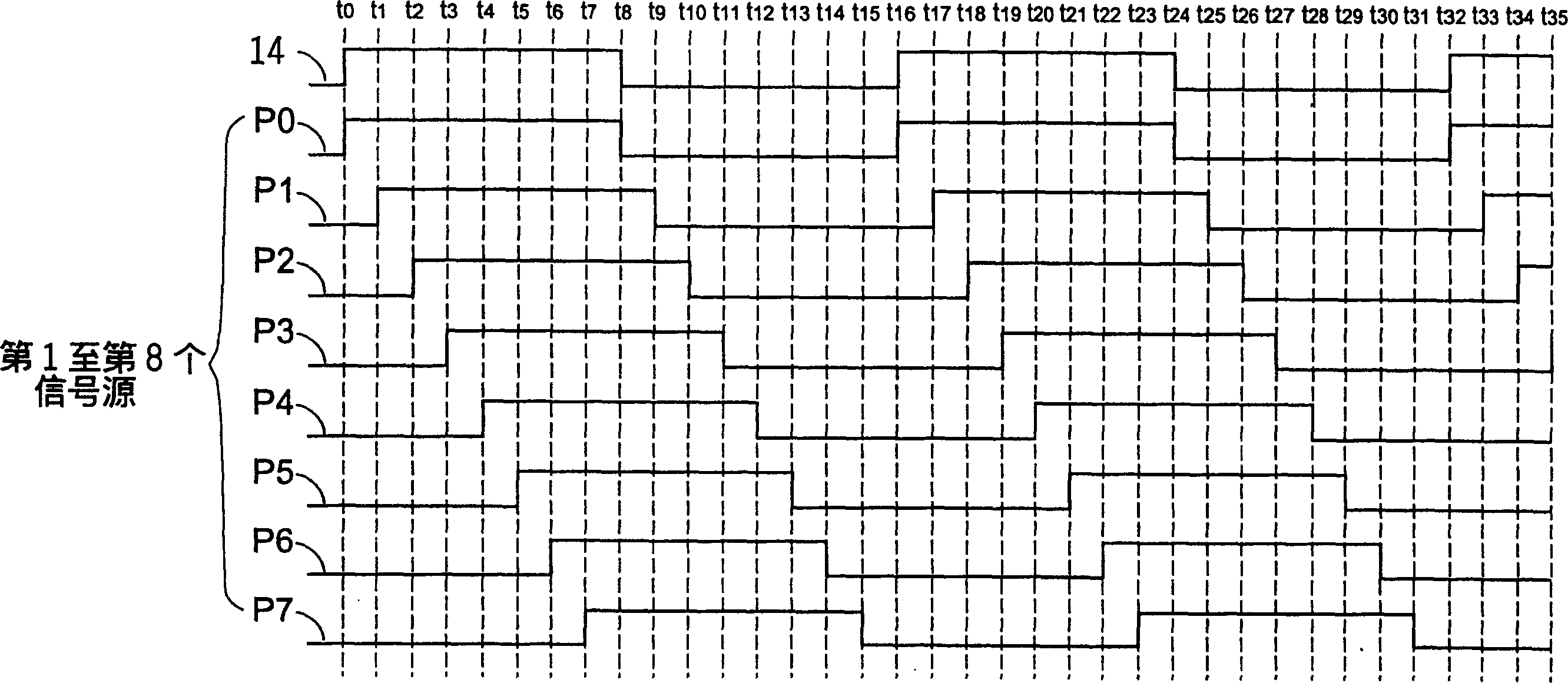

[0054] Such as Figure 2A As shown, it is a conceptual example diagram of generating multiple signal sources (multiplesignal source) in the preferred implementation method of this case; that is, in Figure 2A Among them, a high-frequency signal can be used to generate multiple signal sources (for example, the 1st to 8th signal sources P0-P7); wherein, any two adjacent signal sources differ by one clock period; and, the The 8 signal sources P0~P7 can be 8 locks produced by a phase-locked loop (Phase-Locked Loop, PLL) device (because it is prior art, so Fig. 2 does not show) that inputs this high-frequency signal phase loop signal.

[0055] Such as Figure 2B shown, for the use of Figure 2A The waveform diagram of the multiple signal sources to generate the delayed signal is shown in . exist Figure 2B In t1 and t3, the signal sources P1 and P3 are respectively selected for output, so that the first and second output signals 21 and 22 respectively produce a level state tra...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More