Scalable low-latency switch for usage in interconnect structure

A technology of interconnection structures and interconnection lines, applied in data exchange networks, digital transmission systems, electrical components, etc., can solve problems such as inability to support multiple different communication protocols

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

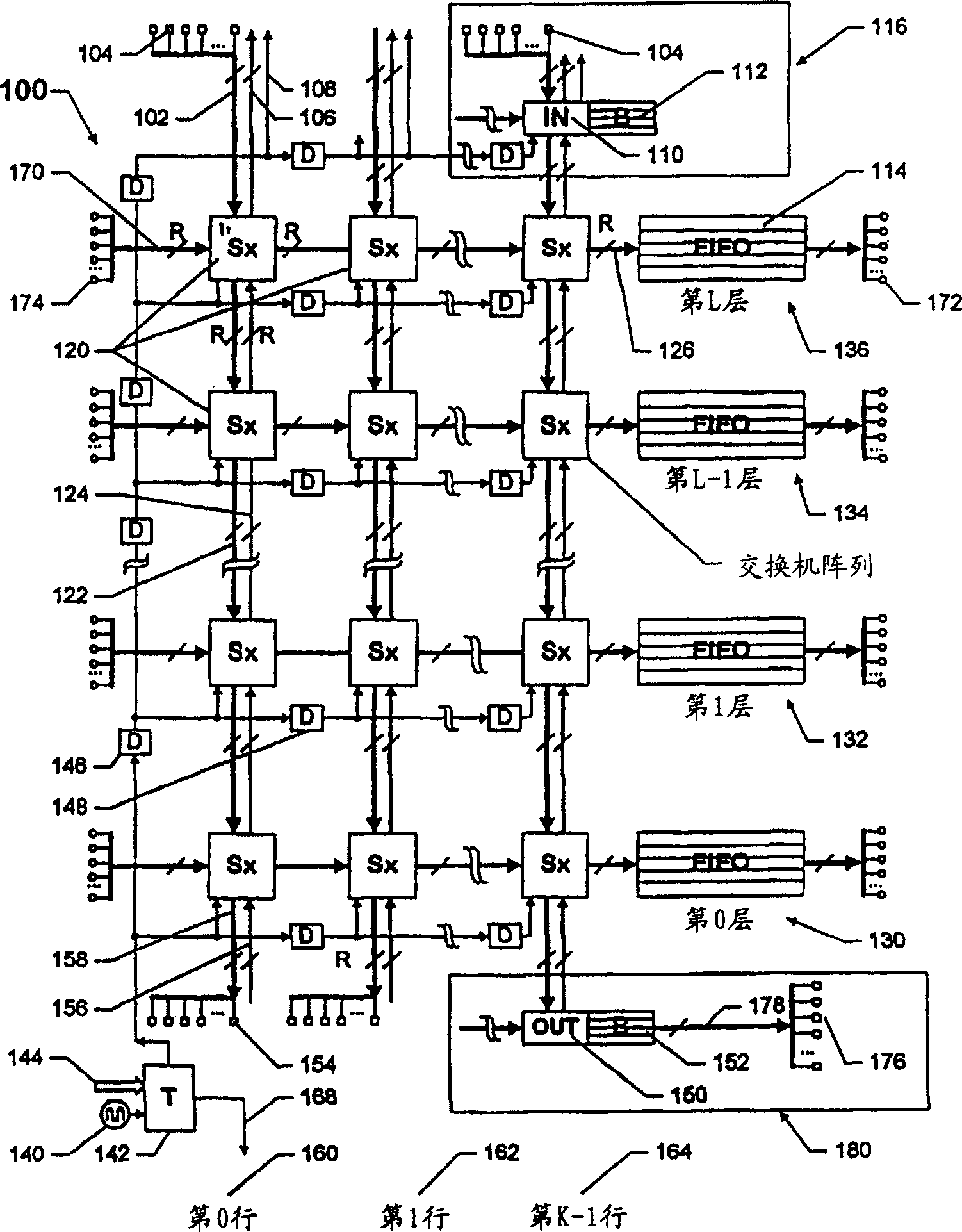

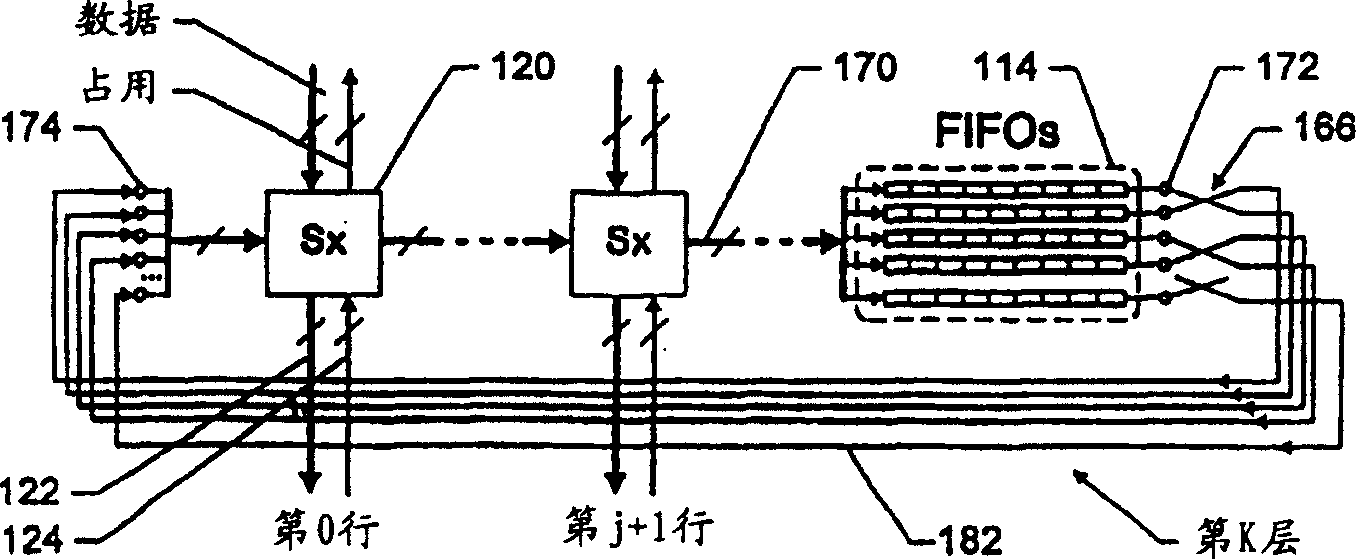

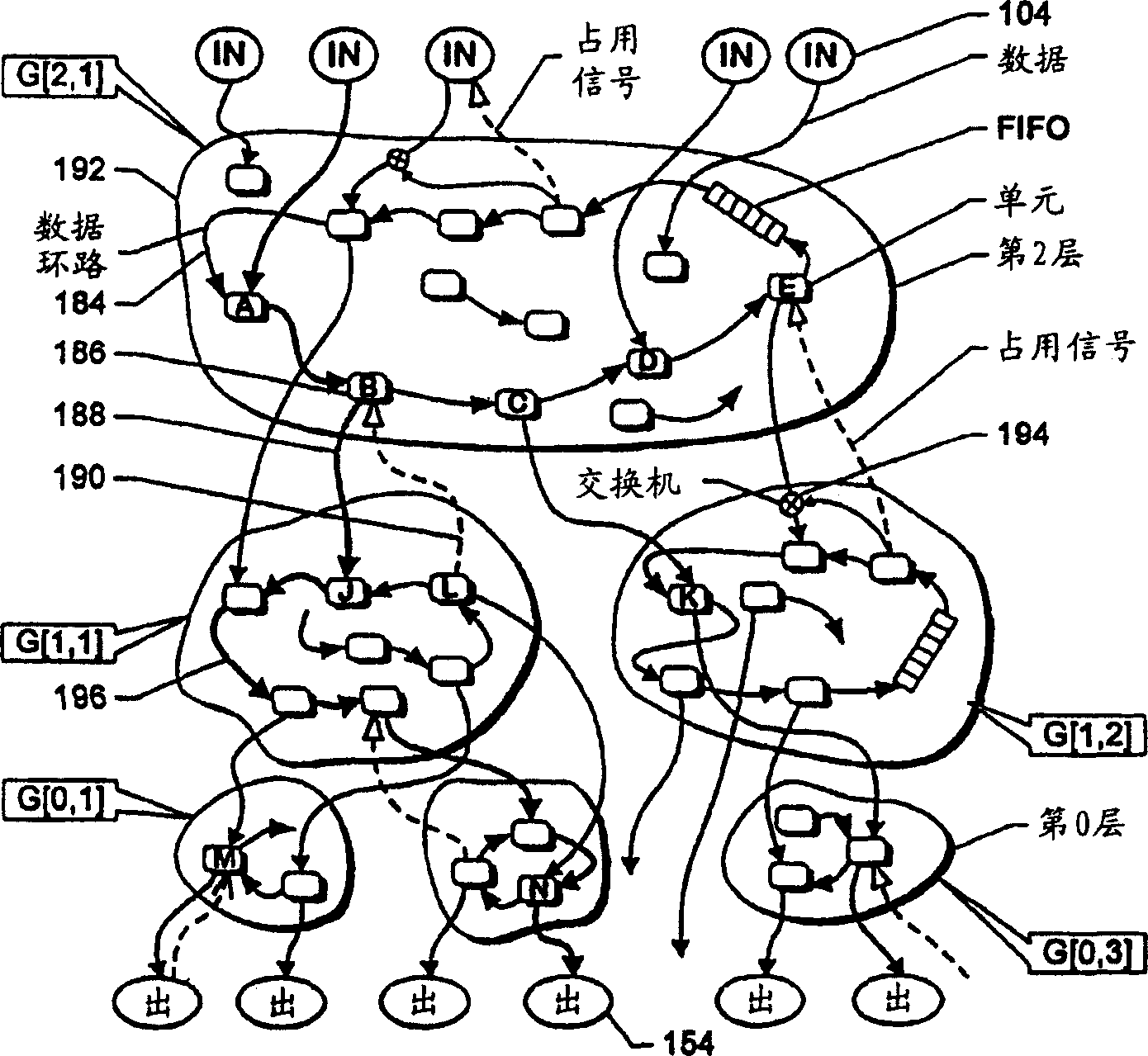

[0103] Scalable low-latency switches for high-bandwidth communications and computer networking applications have many interactive fabrics to perform many types of functions and a wide range of capacity and performance characteristics. The first embodiment describes a switch derived from a power of two design rule, supports message wormhole routing, only handles a single message length, point-to-point message transmission, has a fixed number of columns per layer, and does not fit a flat latency distributed. The description of the first embodiment of the switch 100 forms the basis for establishing desired additional functions and features. Additional functions and features typically include multicast (one-to-many) transmission capability, switching of messages of various lengths, low latency transmission, multi-chip implementation, and control of a fiber optic switch. Various embodiments of this interconnect structure are discussed in detail in Reed's US Patent Application Seri...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More