Constant reducing processor capable of supporting shortening code length

A technology of processors and constants, which is applied in the effective technical field of invalid areas and unused areas, can solve the problems of increasing processing time, increasing the processing time of task context conversion, etc., achieving the effect of reducing code length and improving practical value

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0105] As a processor that achieves the above-mentioned first object, the processor in Embodiment 1 is characterized in that it restores it to the original A function of 1 constant.

[0106] (command format)

[0107] First, the structure of instructions decoded by this processor will be described.

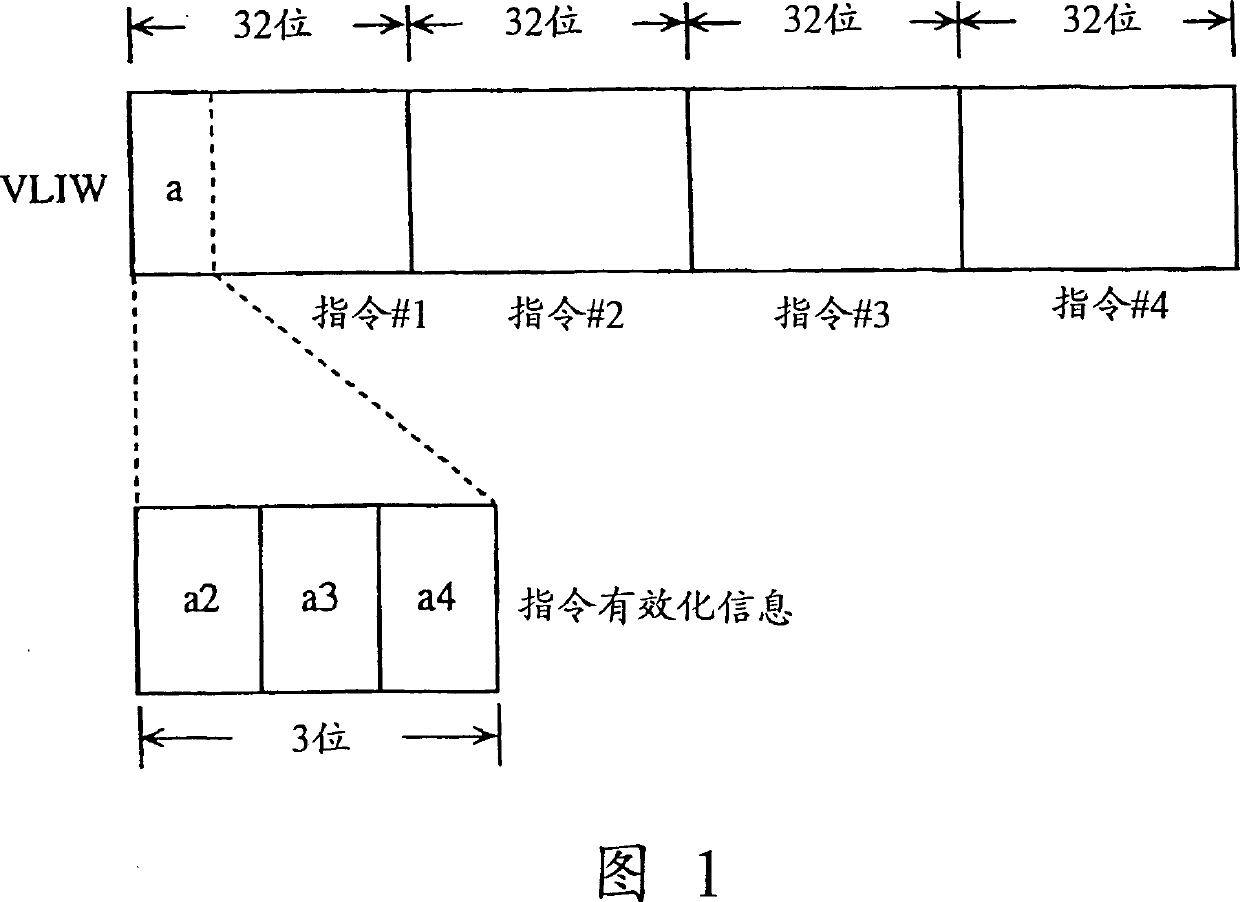

[0108] This processor is a processor adopting VLIW architecture (hereinafter referred to as "VLIW processor"), which decodes and executes 32-bit fixed-length instructions.

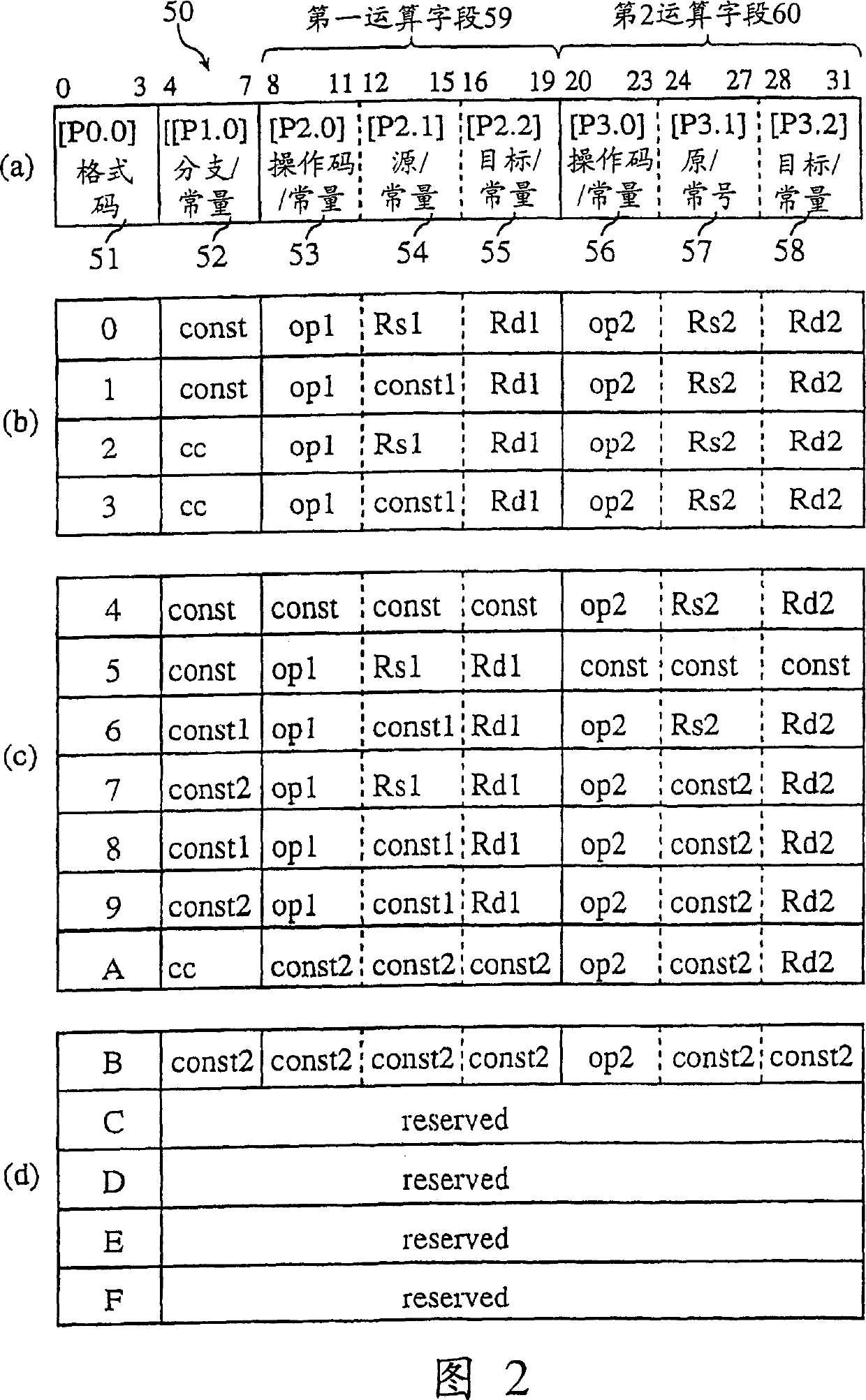

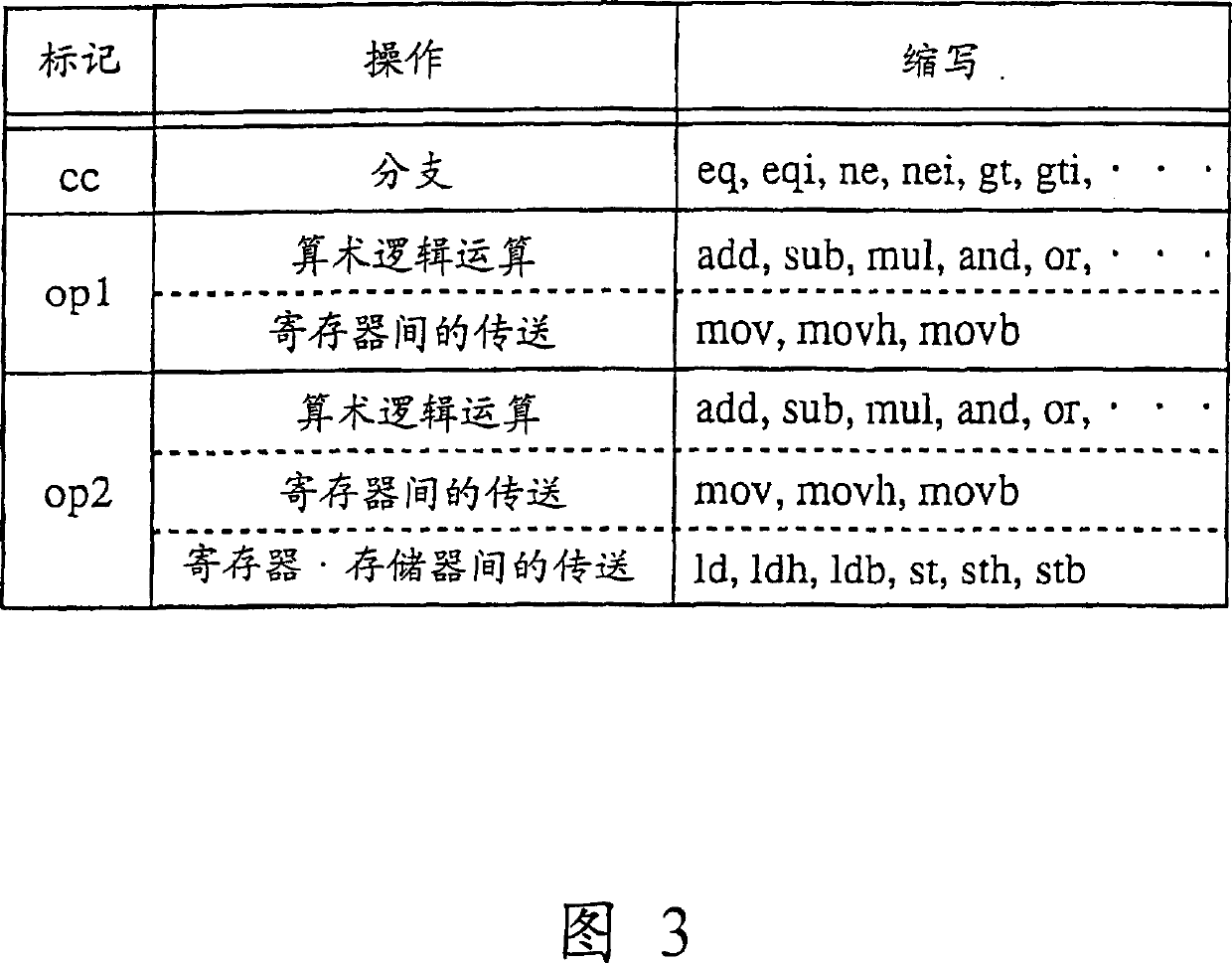

[0109] FIG. 2(a) shows the field configuration of an instruction 50 executed by a processor related to the present invention. Figure 2(b) to Figure 2(d) show 16 command formats. Figure 2(b) shows an instruction format that can specify three operations at the same time, Figure 2(c) shows an instruction format that can specify two operations at the same time, and Figure 2(d) shows an instruction format that can specify one operation at the same time.

[0110] This instruction 50 has a length of 32 bits and co...

Embodiment 2

[0427] The processor according to Embodiment 2 will be described below. The processor according to the second embodiment is a processor that achieves the above-mentioned second object, and is characterized in that it has a function of avoiding useless operations in switching tasks back and forth by saving and restoring values of constant registers only when necessary. Also, a numerical value beginning with 0b represents a binary number.

[0428] (The hardware structure of the processor)

[0429]FIG. 30 is a block diagram showing a hardware structure of a processor 500 according to the second embodiment. This processor is composed of an instruction register 510 , an instruction decoding circuit 520 , an execution unit 530 and an instruction reading unit 540 . In this figure, the peripheral circuit connected to the processor 500 is also shown, that is, the external memory 540 for saving the context and context of tasks.

[0430] The instruction reading unit 540 is composed ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More