Manufacture method of contact hole and manufacture method of semiconductor element

A manufacturing method and contact hole technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as complex process, substrate surface damage, junction leakage, etc., to increase the process window, ensure uniformity, The effect of simplifying the process steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

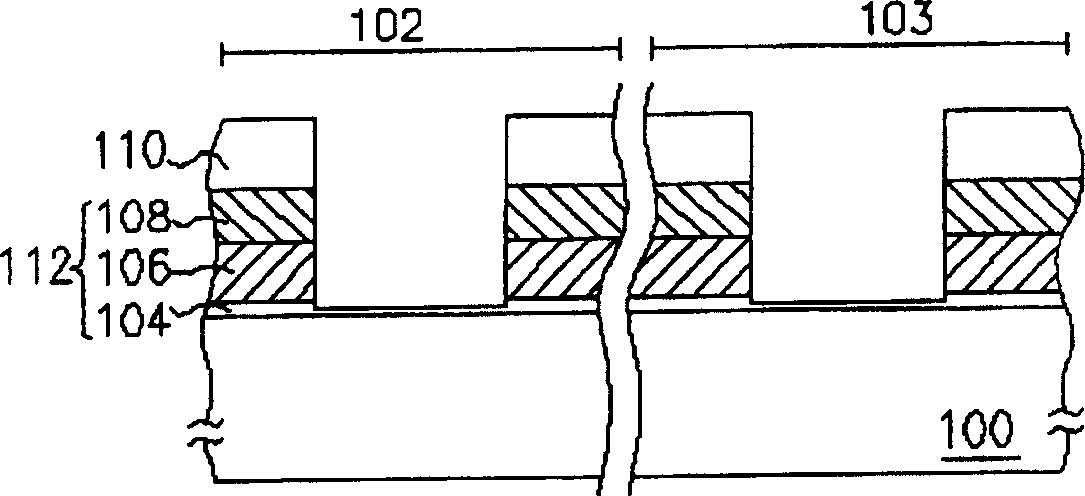

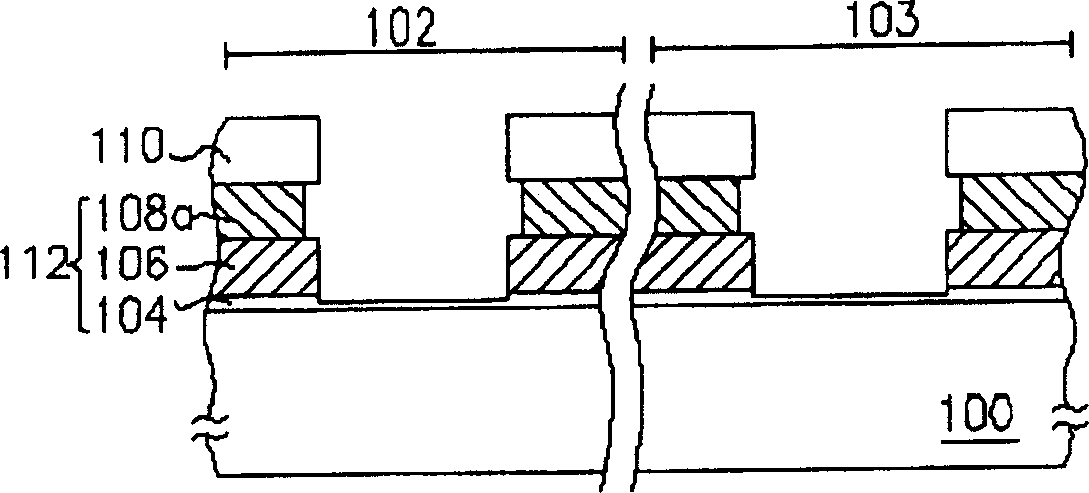

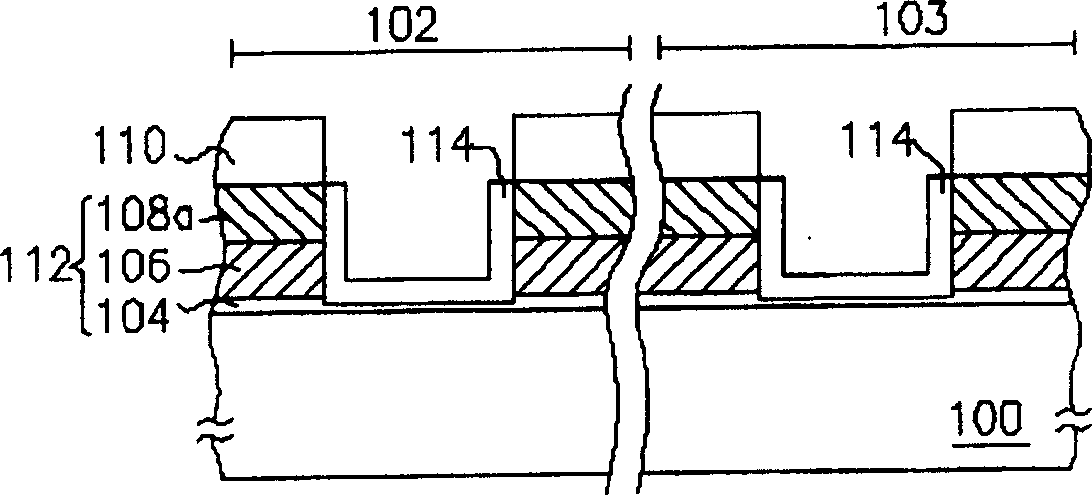

[0042] Figure 2A to Figure 2F Shown is a cross-sectional view of a manufacturing process of a contact hole according to a preferred embodiment of the present invention.

[0043] Please refer to Figure 2A Firstly, a substrate 100 is provided, on which several conductive structures 112 have been formed, and a top cover layer 110 is formed on the top of the conductive structures 112 . Wherein, the area 102 marked in the figure is the area where the bit line contact hole is planned to be formed later, and the area 103 is the area where the bit line contact hole is not planned to be formed later. Therefore, the area 102 is the area where the bit line contact hole is planned to be formed in the memory cell area, and the area 103 is, for example, the area where the bit line contact hole is not expected to be formed in the peripheral circuit area or the memory cell area.

[0044]In a preferred embodiment, the conductive structure 112 is, for example, a gate structure, which is com...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More