Synchronous timing calibrating circuit and method

A technology for synchronizing timing and correcting circuits, applied in the directions of synchronizing devices, synchronizing devices, radio/induction link selection and arrangement, etc., which can solve the problems of increased computational processing, circuit scale and correction processing.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

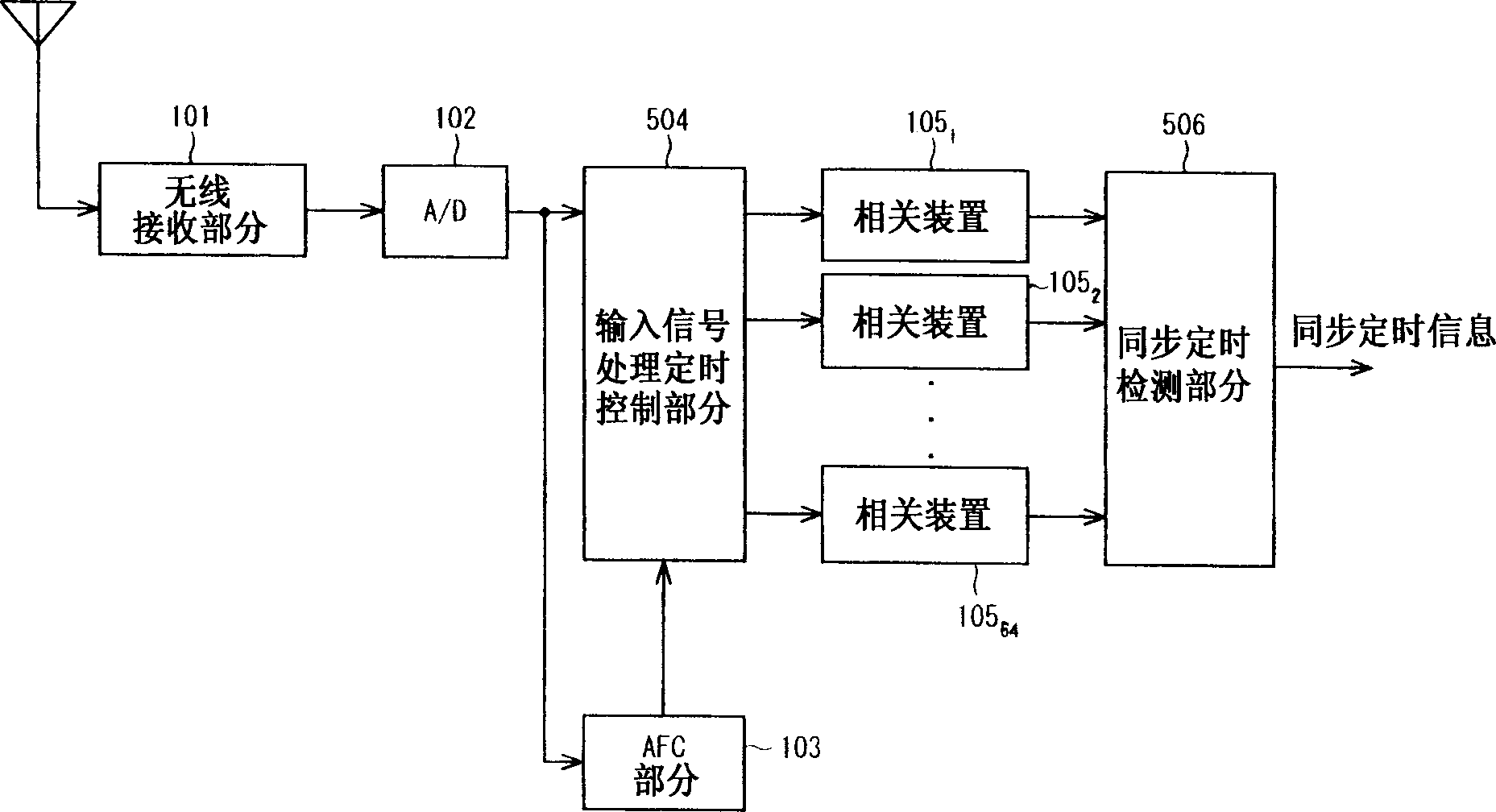

[0036] Figure 4 is a block diagram showing the structure of a CDMA receiver having a synchronous timing correction circuit according to the first embodiment of the present invention. Figure 4 1, the same constituent units or parts as in FIG. 1 are assigned the same reference numerals as in FIG. 1, and explanations thereof are omitted.

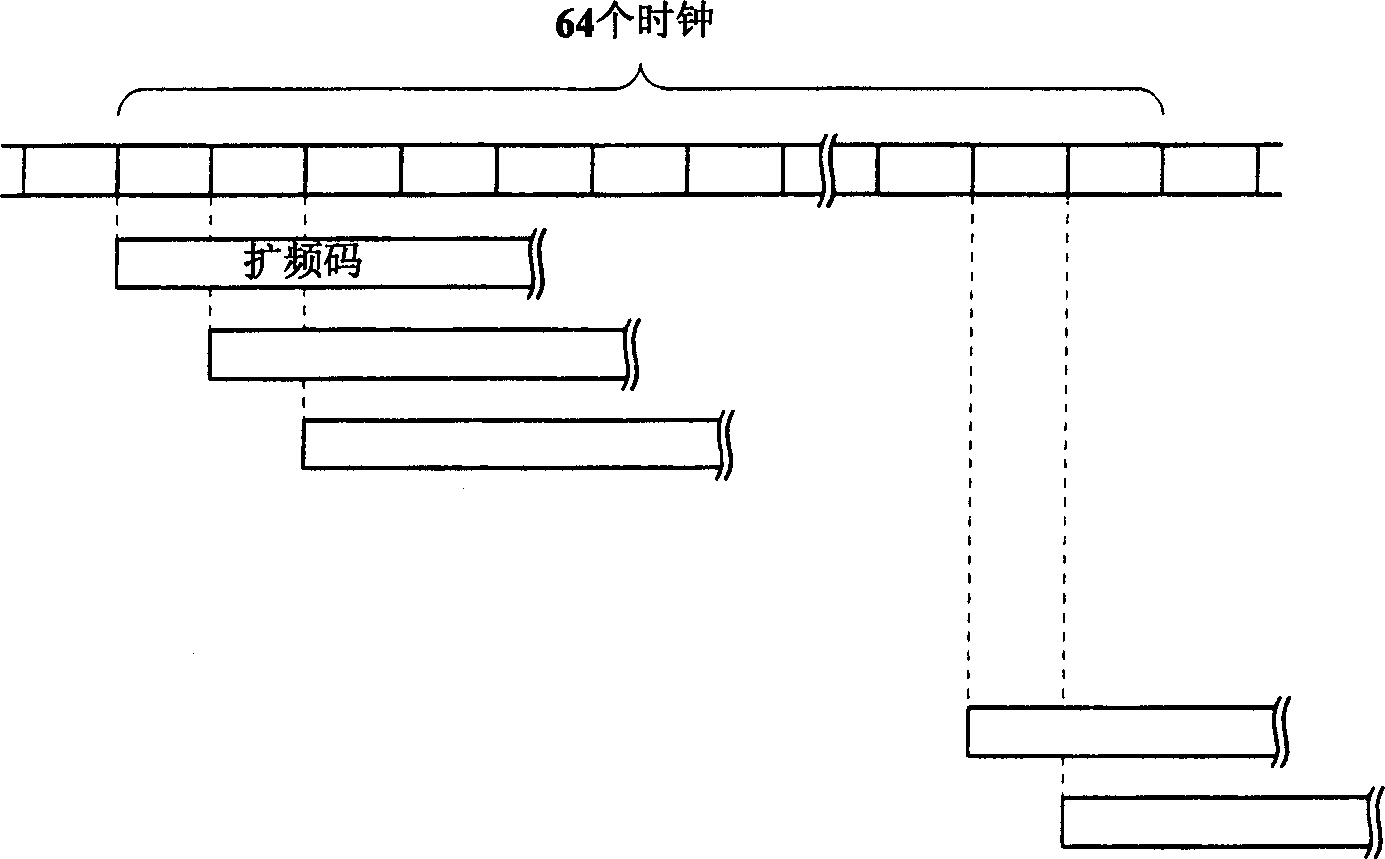

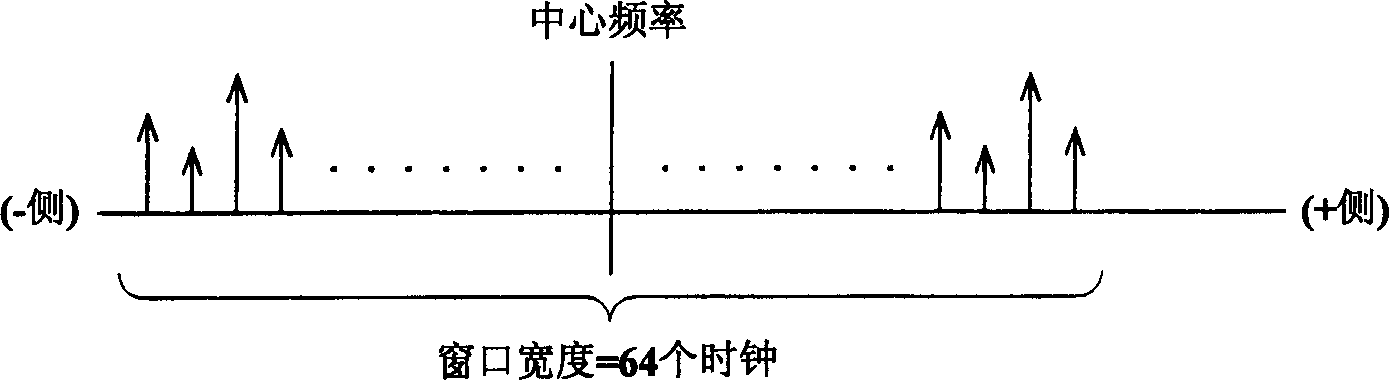

[0037] The synchronization timing correction circuit of this embodiment includes an input signal processing timing control section 104 having a window moving means 107, a correlation means 105 1 -105 8 , and a synchronization timing detection section 106 having an offset judging means 108.

[0038]The offset judging means 108 is obtained from each correlation means 105 by comparing with each other 1 -105 8 Correlation value, detect the offset and offset direction between the center value of the currently set window frequency and the synchronization timing (the maximum timing of the synchronization value) that can obtain the maximum correlat...

no. 2 example

[0052] Next, a synchronous timing correction circuit of a second embodiment of the present invention will be explained. The synchronous timing correction circuit in this embodiment is almost the same in structure as the first embodiment, but the difference between these two synchronous timing circuits lies in the difference in the determination method for determining the offset by the offset judging means 108 .

[0053] Next, an offset judgment method of the synchronous timing correction circuit in this second embodiment will be explained.

[0054] In the offset judging method of this embodiment, a judgment value Y(n) as a criterion of whether the window frequency center value should be changed is calculated according to the following equation (1), when the judgment value Y(n) exceeds a predetermined reference value , to change the frequency center value of the window.

[0055] Y(n)=Z×Y(n-1)+(1-Z)×T

[0056] Among them, Y(n) is the judgment value of this time, Y(n-1) is the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More