Chip packaging structure

A chip packaging structure and chip technology, applied in the direction of electrical components, electrical solid devices, circuits, etc., can solve the problem of high cost and achieve the effect of reducing packaging costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

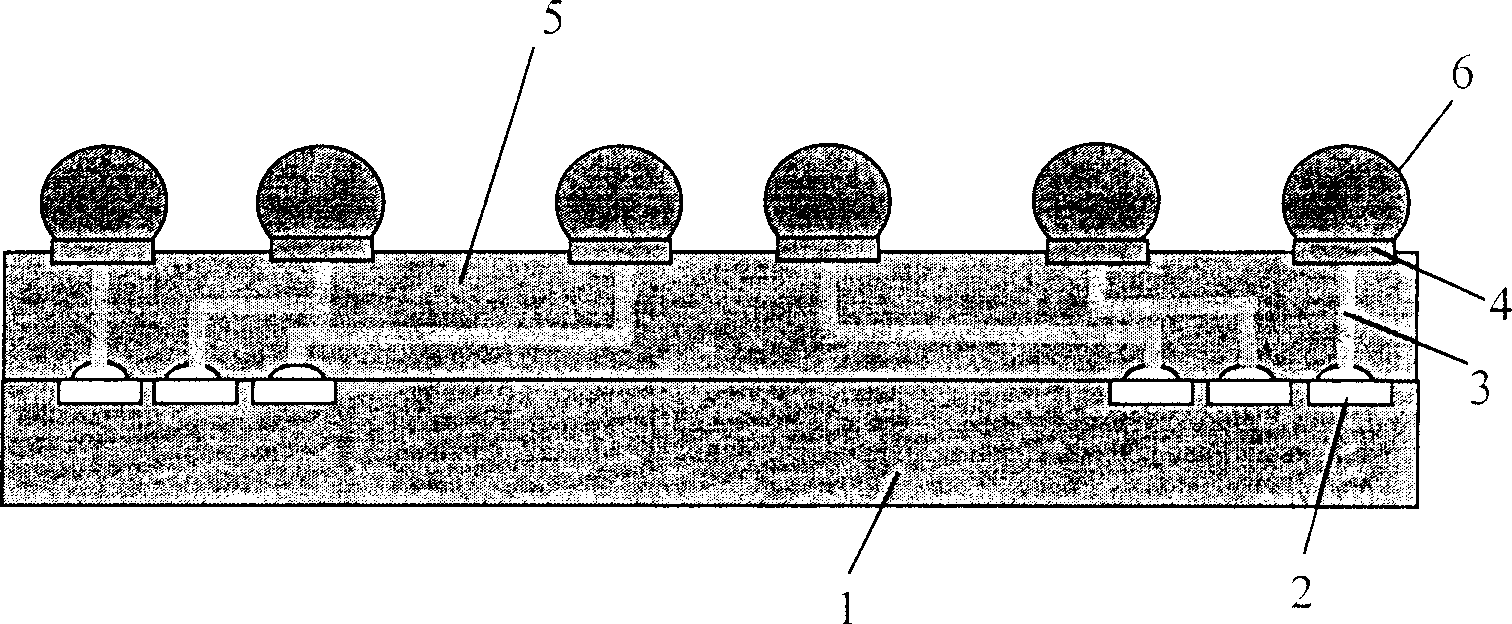

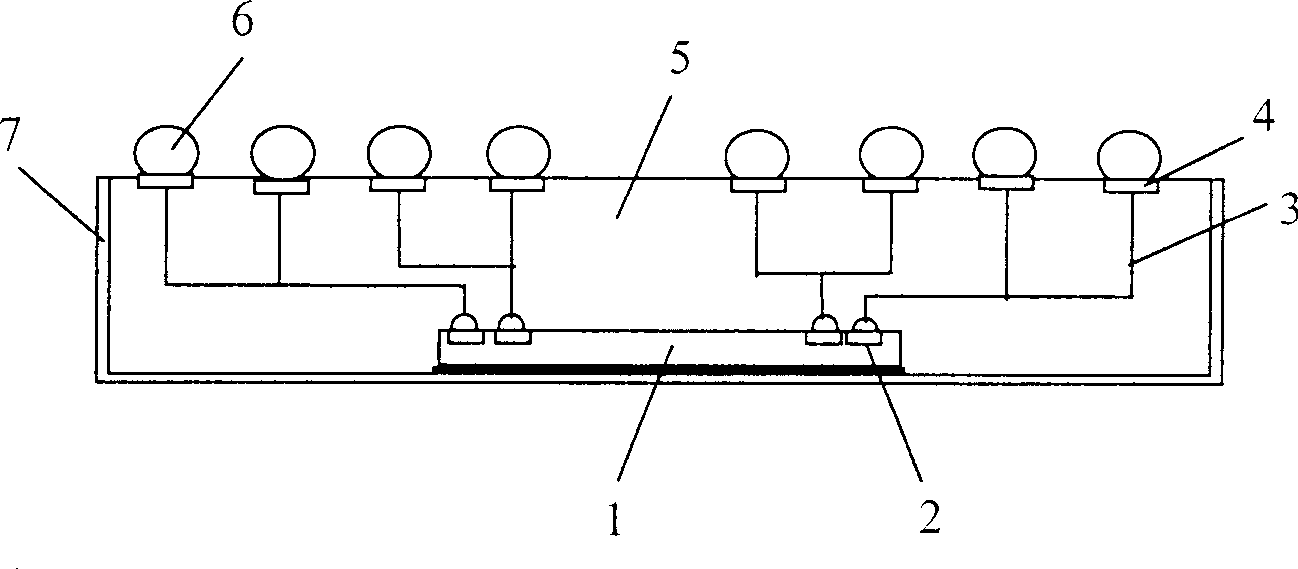

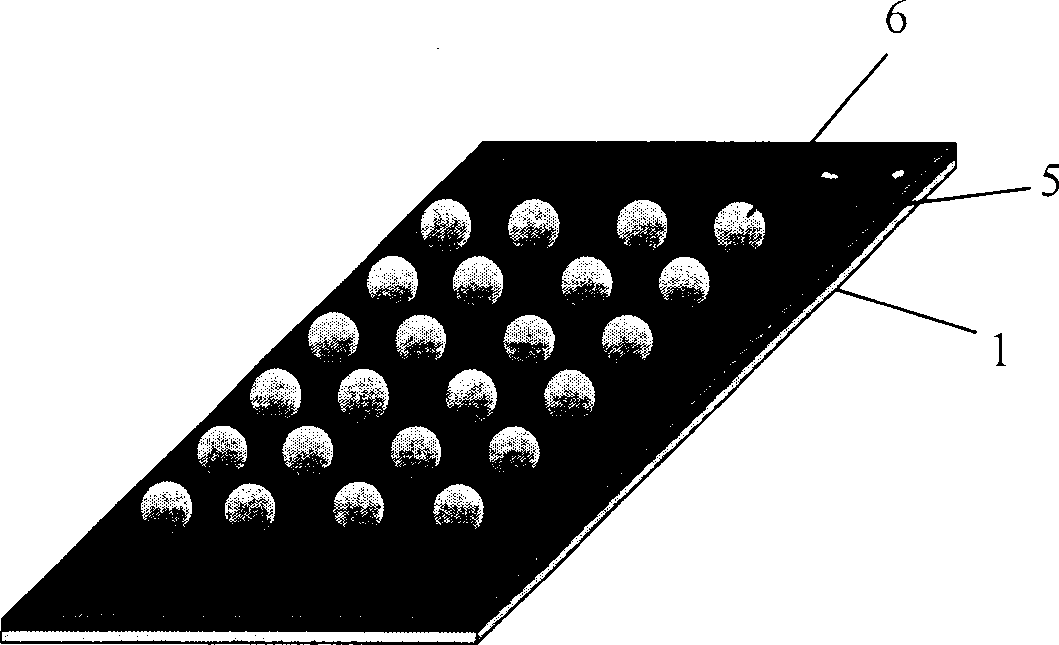

[0017] Such as figure 1 as shown, figure 1 A schematic diagram of the internal structure of the improved chip packaging structure of the present invention is shown. Please refer to figure 1 In the figure, 1 is a chip to be packaged. On the upper surface of the chip 1, there is a lead pad 2. The lead pad 2 is electrically connected to the pad 4 on the same side of the chip through a metal connection wire 3. The metal connecting wire 3 between the pad 2 and the pad 2 is filled with a filler 5, and the filler 5 is generally made of an insulating material, such as a polymer such as epoxy resin or thermosetting resin. Solder balls 6 are welded on the pads 4 by conventional techniques, thereby completing the packaging process of the chip.

[0018] The chip package structure of the present invention and Figure 4 and 5 Compared with the traditional chip packaging structure shown, the substrate is omitted, and the wiring method of the chip is simplified, so the cost of chip pac...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More