System and method for using dynamic random access memory and flash memory

A technology of random access memory and memory system, which is applied in the field of memory systems and can solve problems such as weakening SRAM compatibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 2

[0254] Figure 27A with 27B A second embodiment of a memory module suitable for use in the memory system of the present invention is shown. Figure 27A is the top view of the memory module, Figure 27B It is a sectional view formed along the line A-A' of the top view.

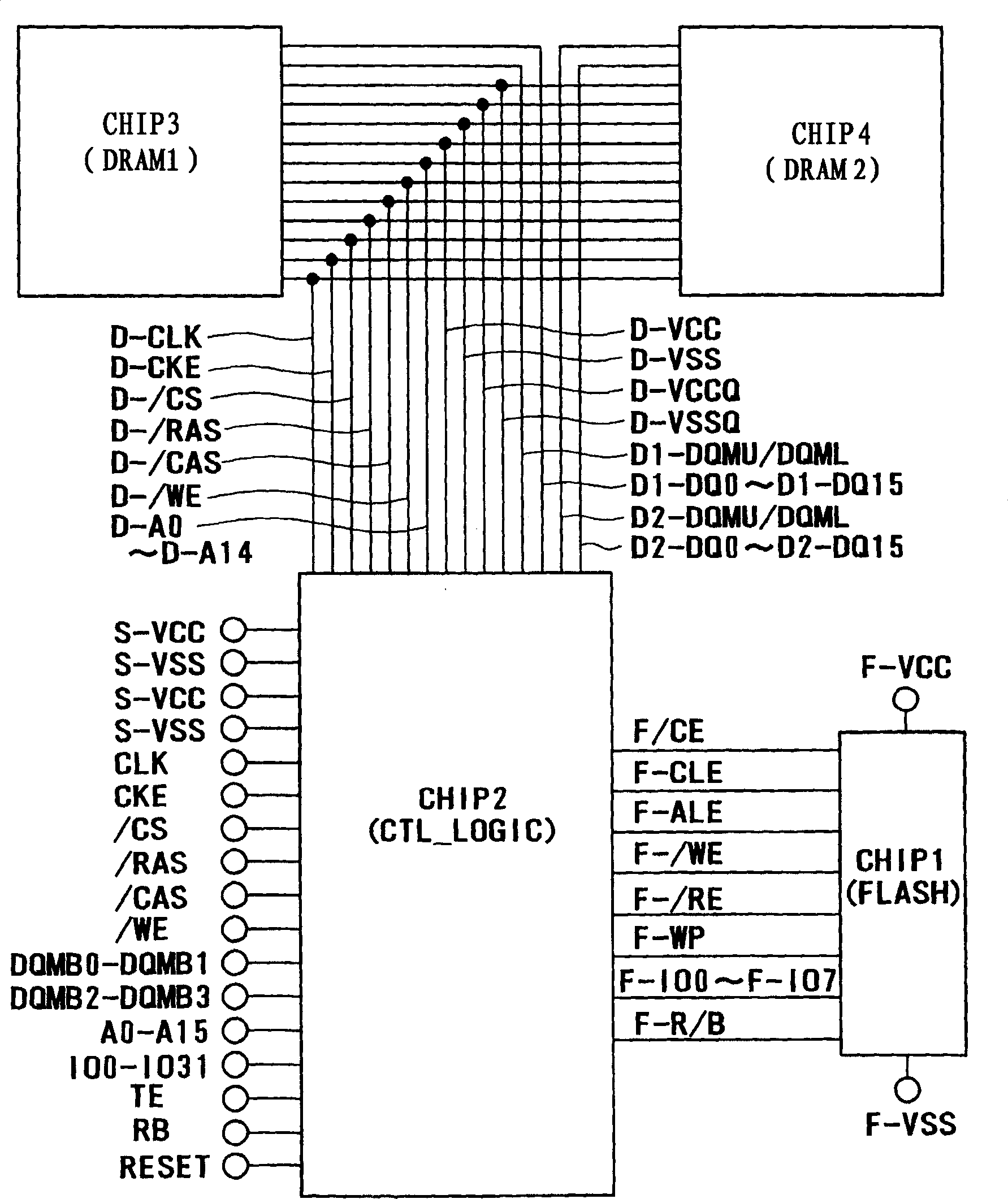

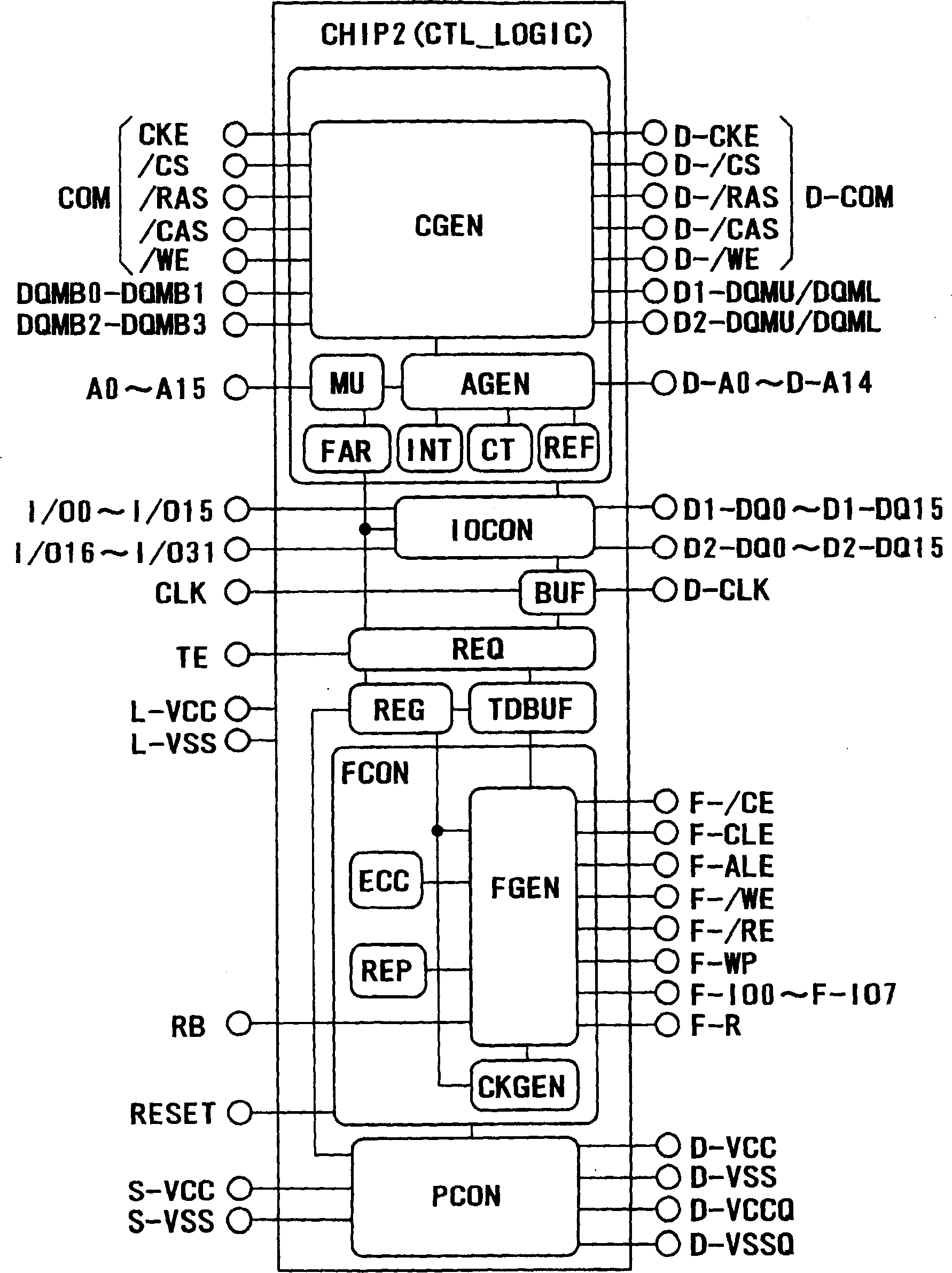

[0255] In the memory module of this embodiment, CHIP1 (FLASH), CHIP2 (CTL_LOGIC), CHIP3 (DRAM1) and CHIP4 (DRAM2) are mounted on a PCB board mounted on the device through a ball grid array (BGA) (for example, by a ring on a printed circuit board made of oxygen glass substrate). A bare chip of a general-purpose DRAM in which signal and power pads are arranged in rows in a so-called chip center is used for CHIP3 and CHIP4, but is not limited thereto. A bare chip of general-purpose FLASH in which signal and power pads are arranged in rows at one end of the so-called chip is used for CHIP1, but is not limited thereto.

[0256] The soldering point on CHIP1 and the soldering point on the PCB are connected to eac...

Embodiment 3

[0264] Figure 29 An embodiment of a cellular phone using a memory module suitable for the memory system of the present invention is shown. Cellular phone includes: antenna ANT, radio block RF, baseband block BB, speech codec block SP, loudspeaker SK, microphone MK, processor CPU, liquid crystal display LCD, keyboard KEY and embodiment 1 or embodiment 2 Described memory module MEM.

[0265] The operations performed during a telephone call will be described below.

[0266] Speech received through the antenna ANT is amplified by the radio block RF and input to the baseband block BB, in which the analog signal of the speech is converted into a digital signal, error correction decoding is performed, and the signal is output to speech codec block SP. The speech codec block converts the digital signal into an analog signal and outputs the signal to the speaker SK. Therefore, the voice of the other party at the other end can be heard through the speaker.

[0267] Operations perf...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More