Duty-cycle-efficent SRAM cell test

A storage unit and storage structure technology, applied in static memory, digital memory information, information storage, etc., can solve problems such as device failure, difficulty in detecting bit line contact resistance, and failure to detect defects, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

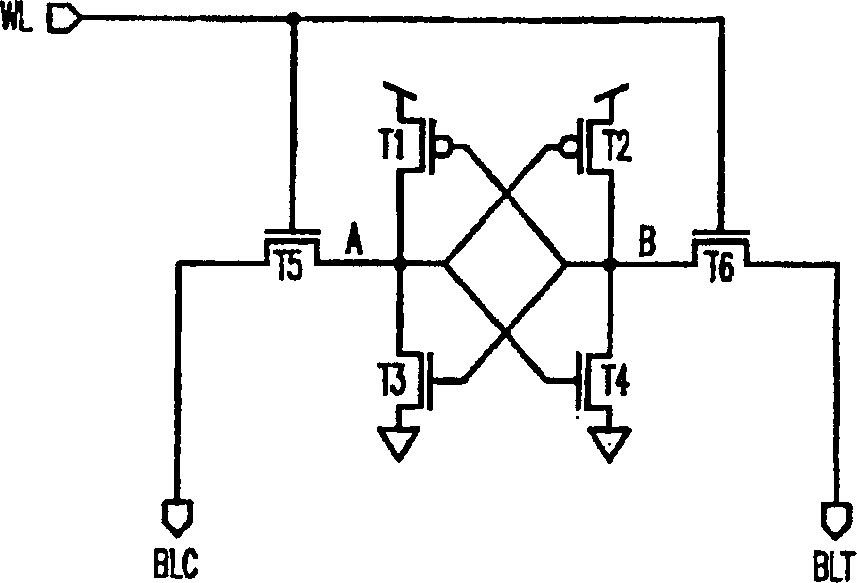

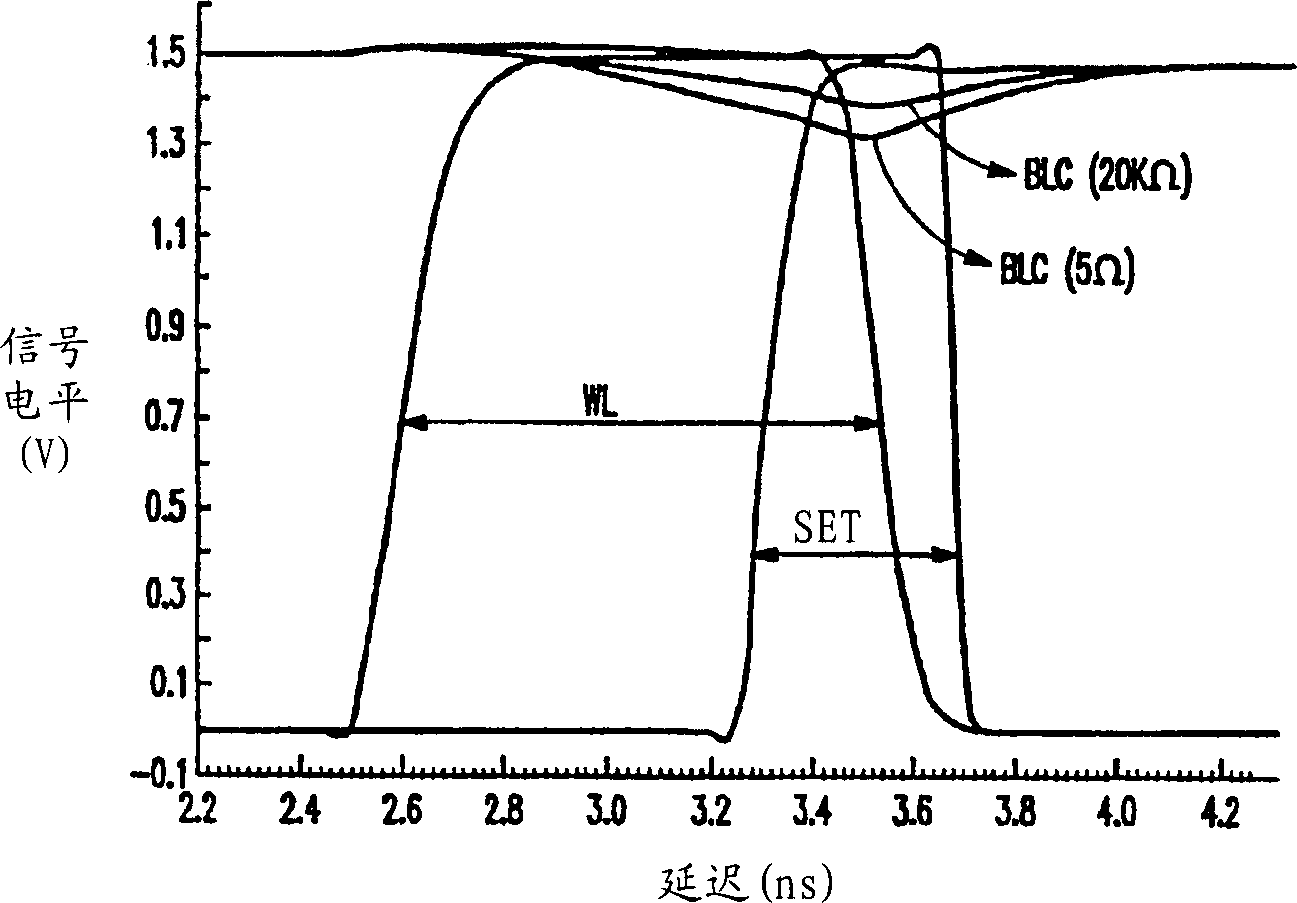

[0027] As mentioned above, there is a need to identify bitline contacts whose resistance values are even marginally higher than optimal. It is difficult for the prior art to detect slightly increased bit line contact resistance, because even with extremely high bit line contact resistance values, the write activity to and the read activity from the memory cell can be performed initially. However, initial testing performed immediately after manufacture may not detect defects that develop only after the device has been subjected to actual consumer use for some time.

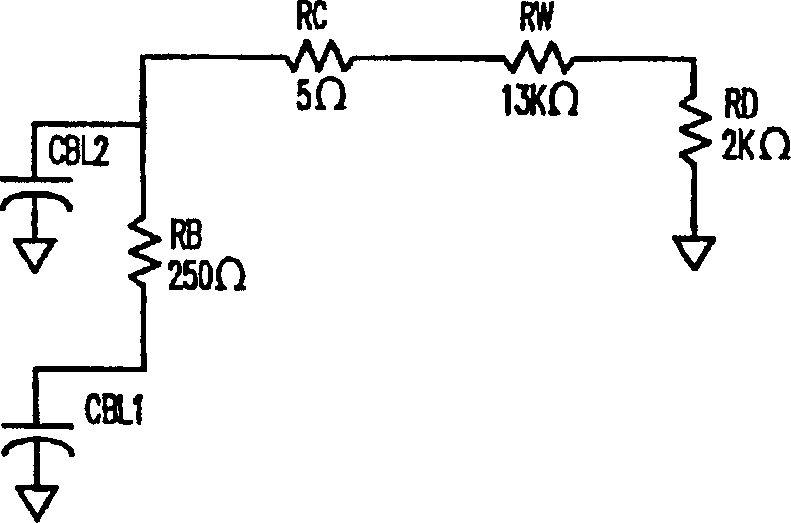

[0028] The invention described below overcomes these problems by providing a structure and method that provides substantial stress to the bit line contacts. This allows those bit line contacts which are initially acceptable only on the edges (and which may become defective after some time of use) to be directly identifiable immediately after manufacture. More specifically, the present invention provides a test m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More