Method for resolving satisfiability problem of very large scale integrated circuit (VLSIC) verification

A large-scale integrated circuit, solution technology, applied in the direction of circuits, electrical components, electrical digital data processing, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

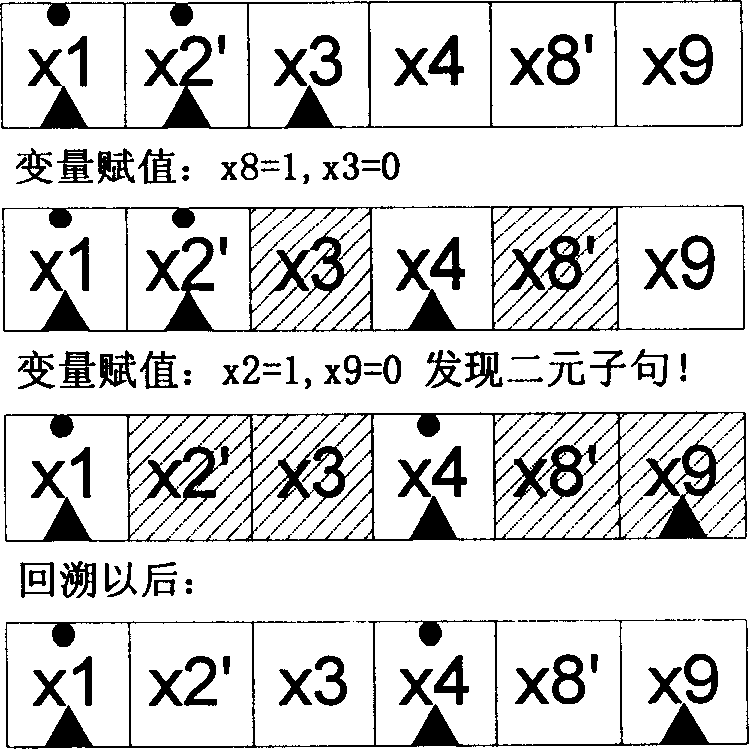

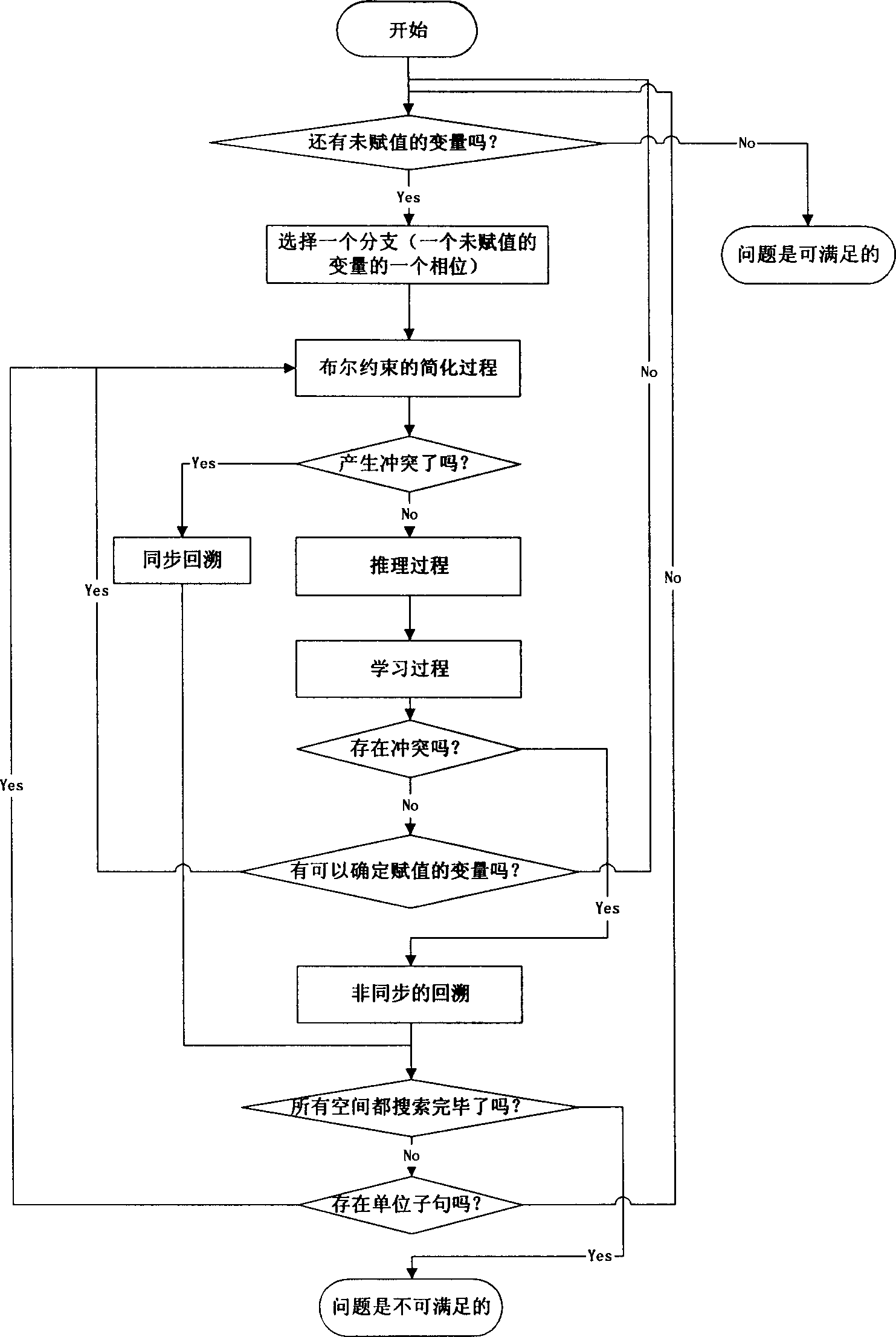

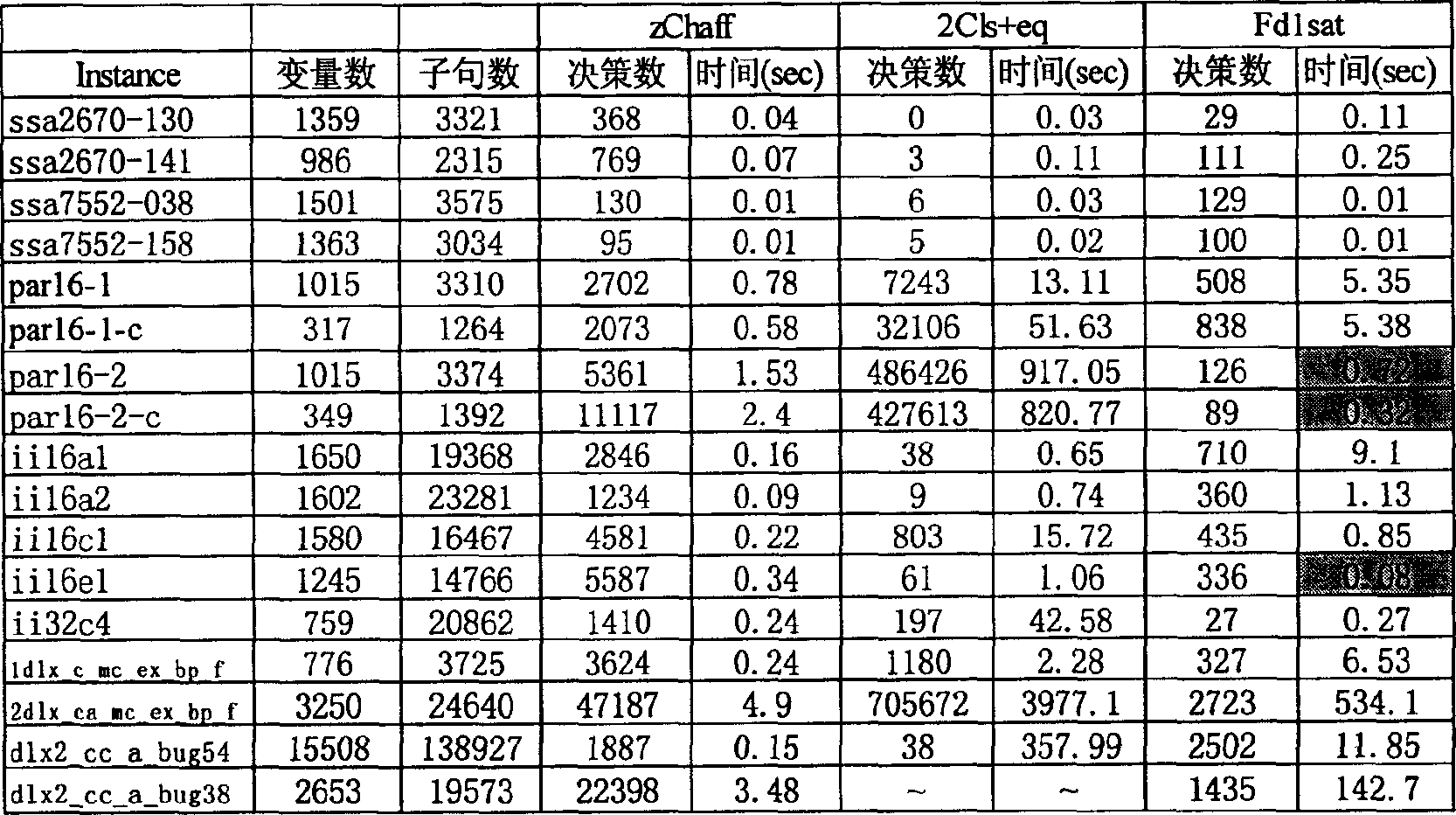

[0023]According to the present invention, the method for solving the satisfiability problem of VLSI verification includes five steps: decision process, Boolean constraint simplification process, backtracking process, learning process and reasoning process. According to this method, we design the corresponding algorithm program. The specific calculation steps are as follows:

[0024] 1. Scan the clauses of the original question and initialize the current values of all variables;

[0025] 2. Select the variable with the largest current value as the decision variable this time, and assign a value according to the current value of the variable. For example, the variable x is a decision variable, and x has a higher current value than x', then let x=1, otherwise, let x=0; if it is found that all variables have been assigned in the process, it means that the original problem can be satisfied , output the assignment of the variable and exit.

[0026] 3. According to the assignmen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More