Partial integrated compression tree generating method based on mixed compression structure

A hybrid compression and tree compression technology, which is applied in the calculation using number system representation and non-contact manufacturing equipment for calculation. cost, the effect of reducing the total delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

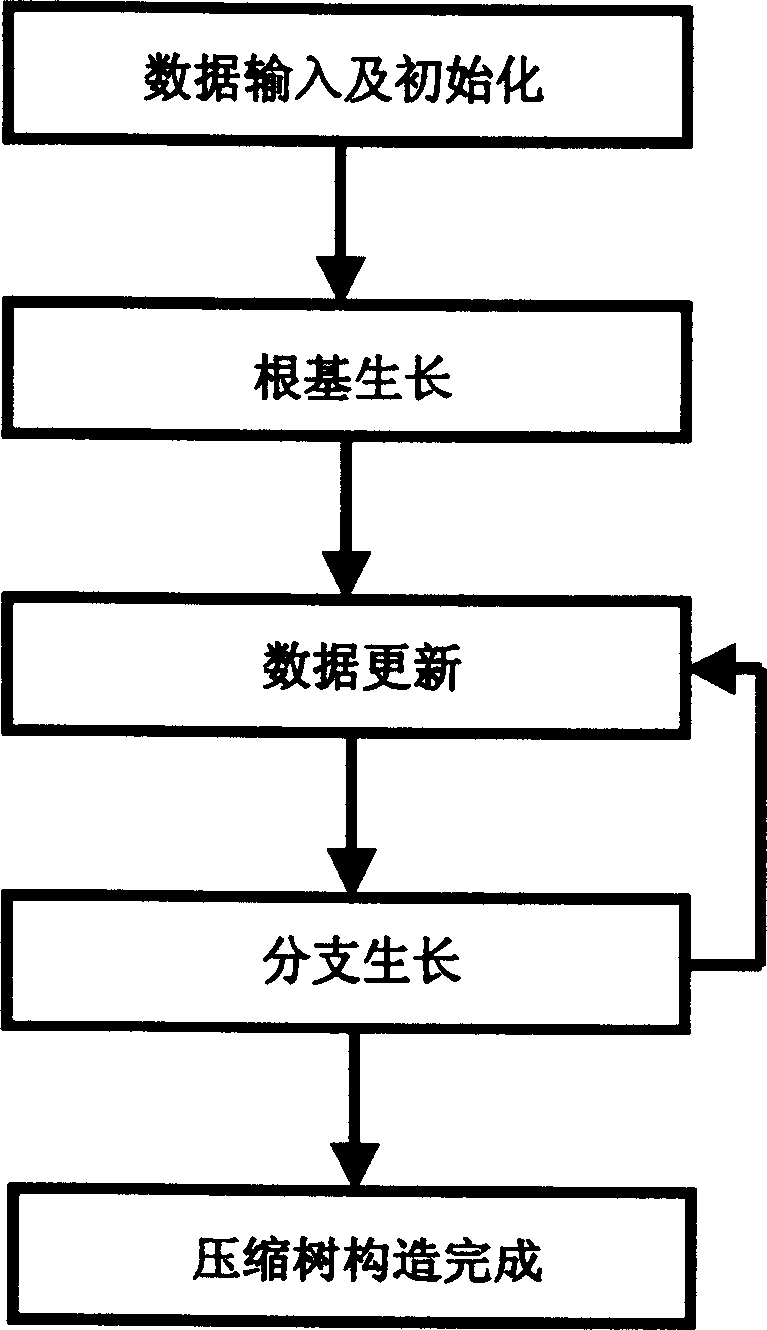

Method used

Image

Examples

Embodiment

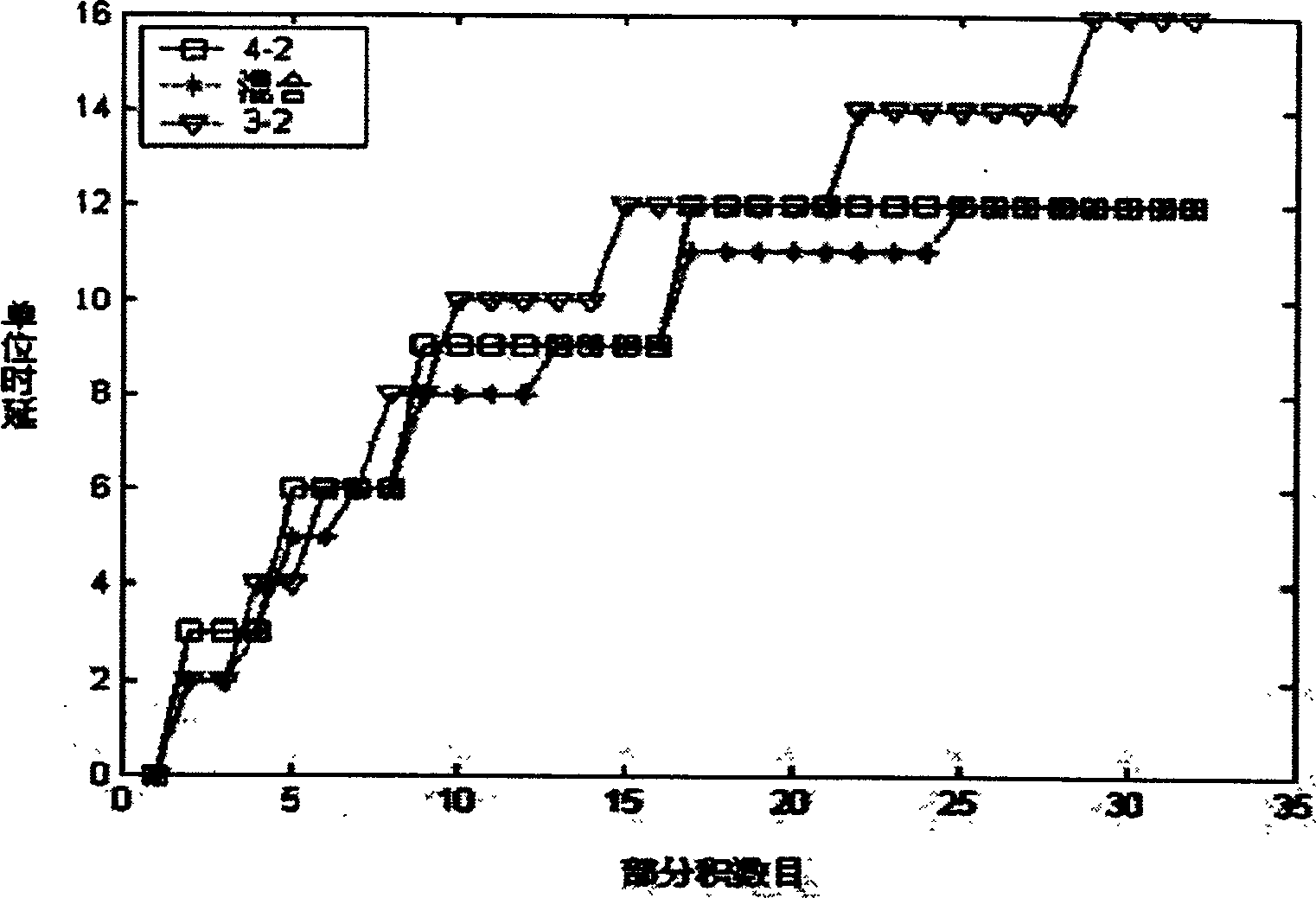

[0024] Implement an 8×8 multiplier and use a non-Booth coded Wallace-tree structure. At this time, the total number of columns of the partial product of the multiplier is 15, and the number of partial products to be compressed on each column is: 1, 2, 3 , 4, 5, 6, 7, 8, 7, 6, 5, 4, 3, 2, 1. Take the calculation of column 8 as an example:

[0025] Step 1: The current column number is 8, the current layer number is 1; the current column number is less than the total number of columns of the partial product of the multiplier, 15, and the next step is executed;

[0026] Step 2: The number of bits to be compressed currently is 12 and not less than 4, and a 4:2 compressor is used as the root of the entire partial product compression tree;

[0027] Step 3: The maximum number of signals that the current layer can accept is 5, the number of carry-reserved signals generated is 1, the number of carry-out signals is 1, the number of partial products to be compressed in the current column...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More