Double CPU communication systems based on PCI shared memory

A technology of shared memory and communication system, applied in the field of dual CPU communication system, to achieve the effect of ensuring communication efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

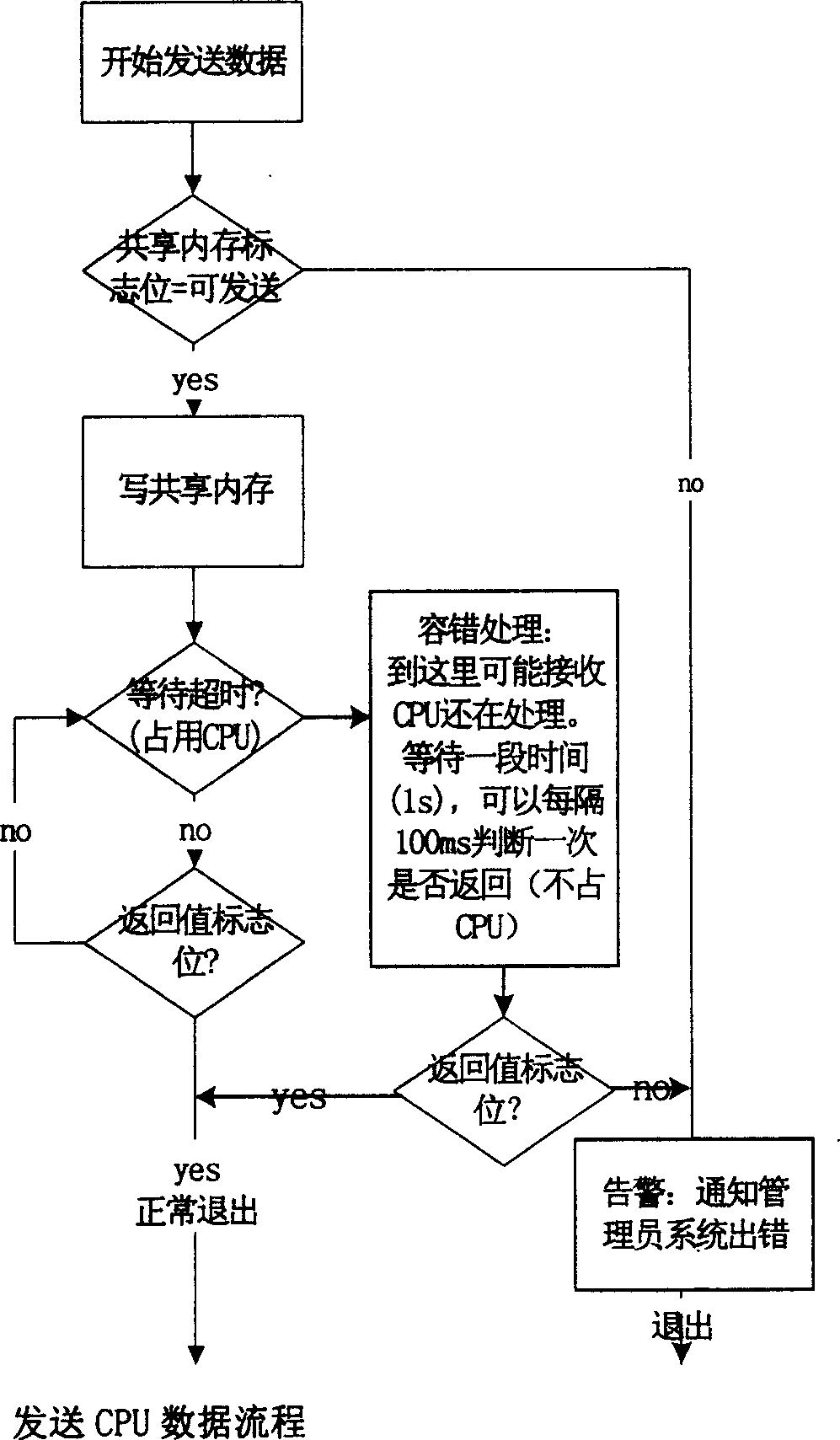

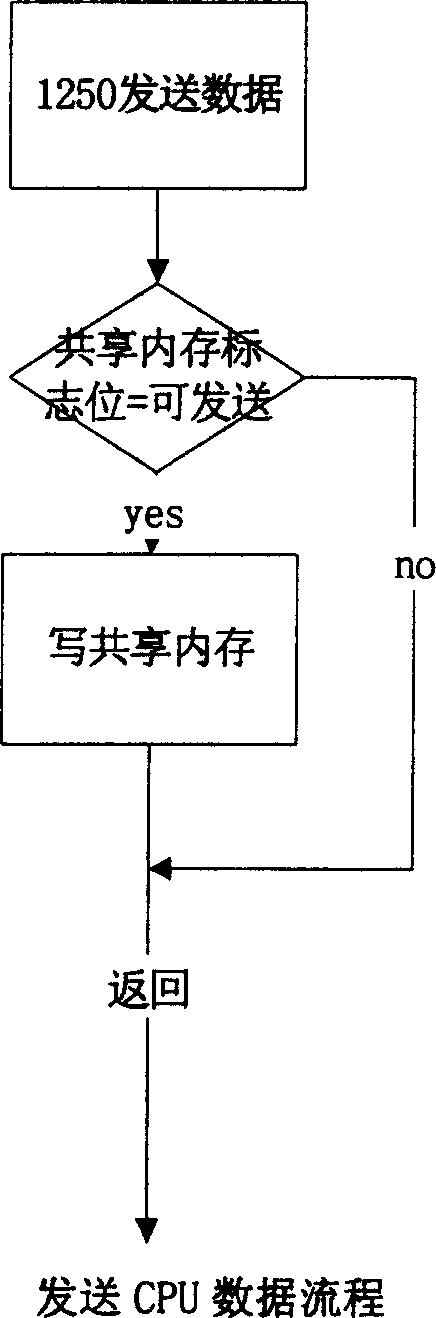

[0020] In this system, BCM1250 microprocessor allocates 16M physical memory as shared memory, and sets the address mapping register in PCI configuration space; PPC8245 microprocessor reserves 16M memory address space, and sets BARO register in PCI configuration space. Through the configuration of both parties, the PPC8245 microprocessor can access the 16M physical memory on the BCM1250 microprocessor through the PCI bus to complete the initialization of the PCI device. At the same time, the BCM1250 microprocessor can interrupt the PPC8245 microprocessor through the INTA, and the PPC8245 microprocessor can Interrupt the BCM1250 microprocessor through MAILBOX to realize the interrupt communication between the two.

[0021] The shared memory is divided into a communication channel from the PPC8245 microprocessor to the BCM1250 microprocessor and a communication channel from the BCM1250 microprocessor to the PPC8245 microprocessor. Referring to Figure 1, the first 8M of the shared...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More