Semiconductor memory device and semiconductor integrated circuit device

A storage device and semiconductor technology, applied in the direction of information storage, static memory, digital memory information, etc., can solve the problems of increased power consumption, inability to maintain data, frequent refresh operations, etc., and achieve the optimization of operation time and simplification of refresh control Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 approach

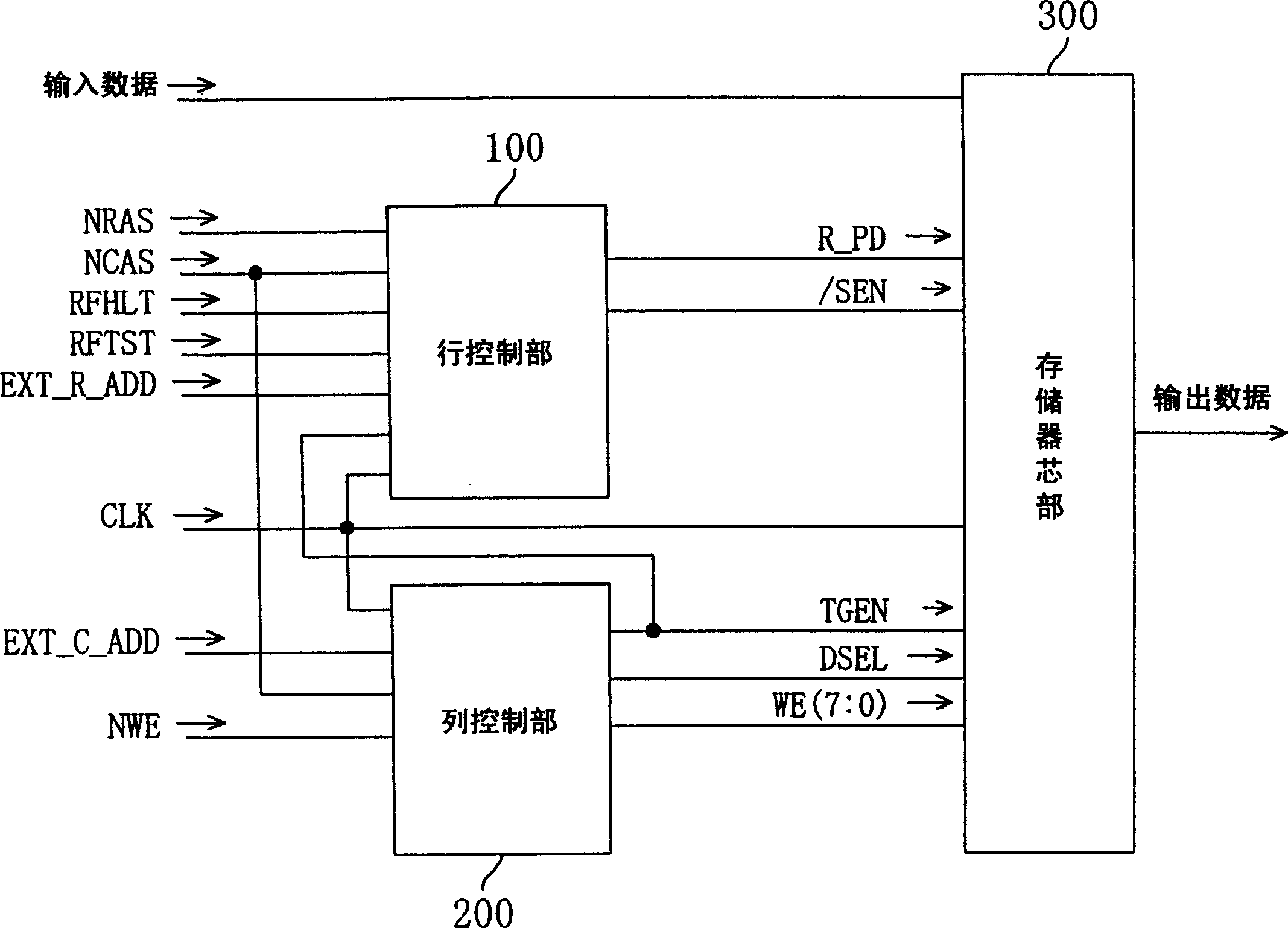

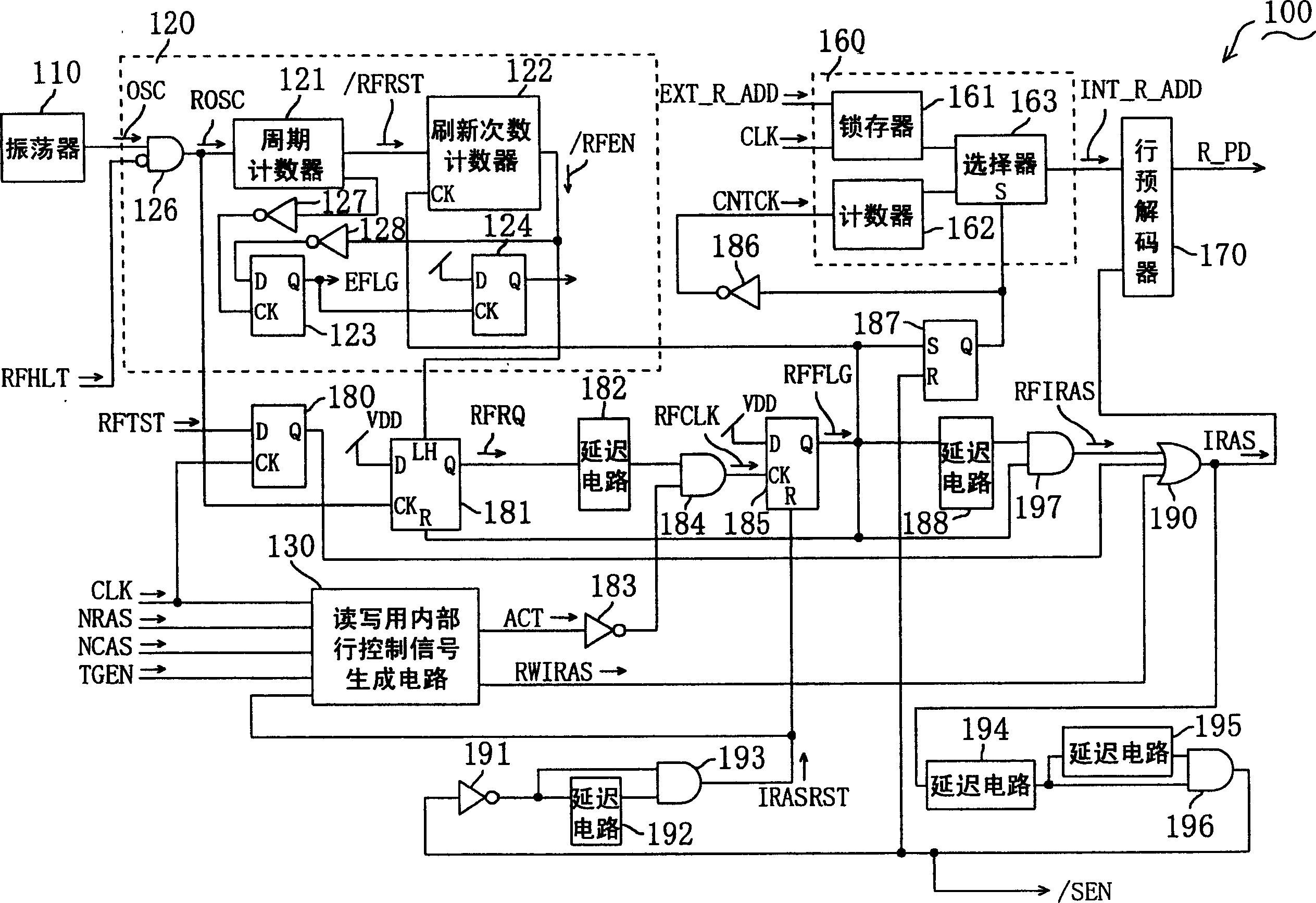

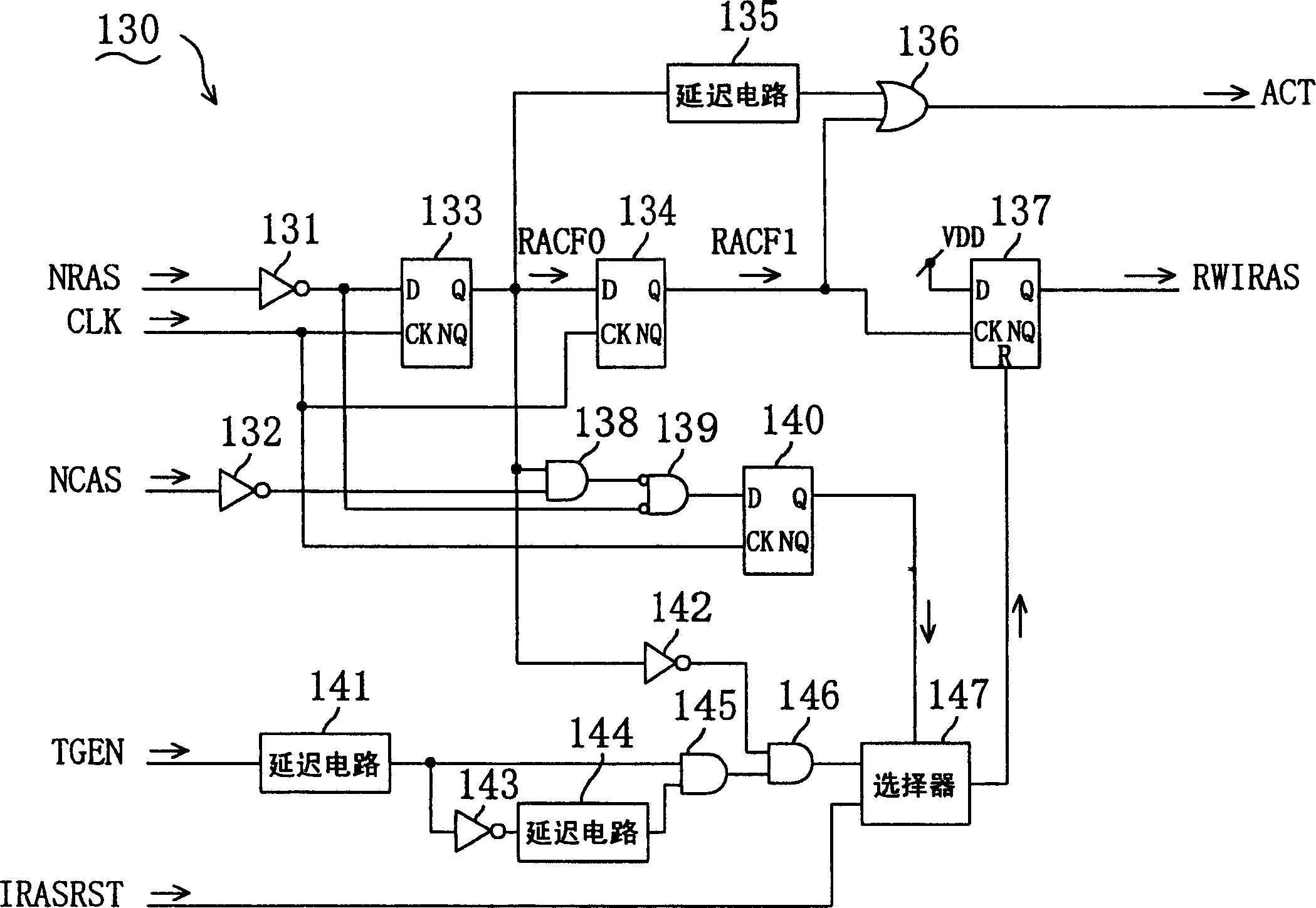

[0045] -Overall composition-

[0046] figure 1 A schematic circuit block diagram showing the structure of the semiconductor memory device according to the first embodiment. As shown in the figure, the semiconductor memory device of this embodiment includes: a memory cell array having memory cells arranged in rows and columns; word lines extending along the row direction of the memory cell array; word lines extending along the column direction of the memory cell array; A memory core 300 such as a bit line for amplifying a signal read from a memory cell, a sense amplifier, etc.; a row control circuit 100 for controlling selection and non-selection of a word line; and a column for controlling selection and non-selection of a bit line, etc. Control circuit 200.

[0047] The row control circuit 100 receives a row control signal NRSA, a column control signal NCAS, a refresh stop signal RFHLT, a test refresh signal RFTST, an external row address EXT_R_ADD, and an external clock CL...

no. 2 approach

[0088] Figure 7 A schematic configuration diagram showing a semiconductor integrated circuit device according to a second embodiment of the present invention. As shown in the figure, the semiconductor integrated circuit device of this embodiment includes: a logic unit 400 composed of a CMOS device including a CPU or various arithmetic circuits; and a memory unit 500 (DRAM) which is figure 1 The semiconductor memory device shown. exist Image 6 In the shown semiconductor integrated circuit device, the structure of the memory unit 500 is the same as that in the first embodiment Figure 1 ~ Figure 4 Same as shown. A CPU, a plurality of arithmetic circuits, and the like are arranged in the logic unit 400 .

[0089] Then, a row control signal NRAS, a column control signal NCAS, a read enable NWE, an external row address EXT_R_ADD, an external column address EXT_C_ADD, input data, and the like are transferred from the logic section 400 to the memory section 500 . These signal...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More