Semiconductor design layout pattern formation method and graphic pattern formation unit

A semiconductor and layout technology, used in semiconductor/solid-state device manufacturing, computer-aided design, CAD circuit design, etc., to solve problems such as insufficient correction accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

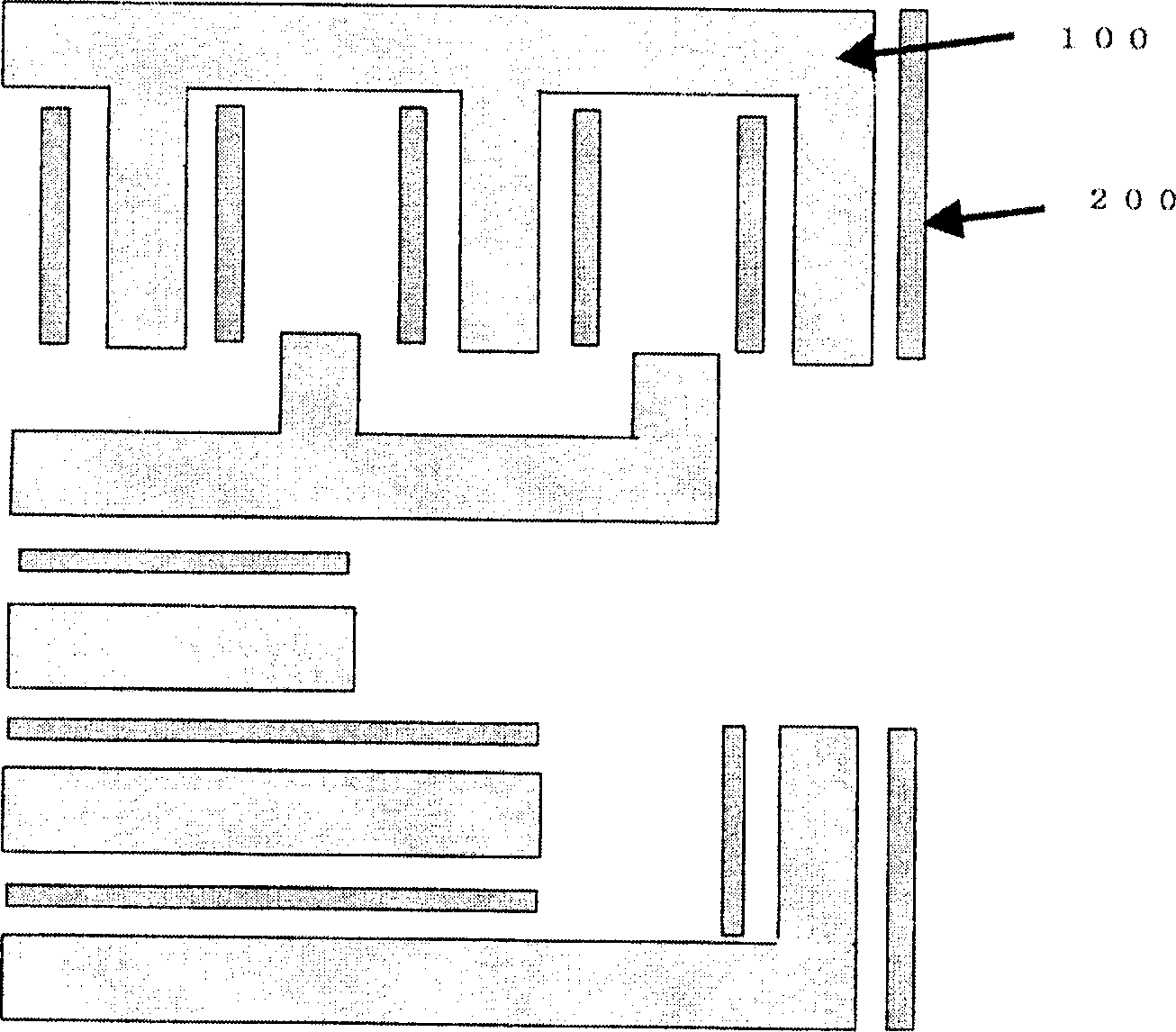

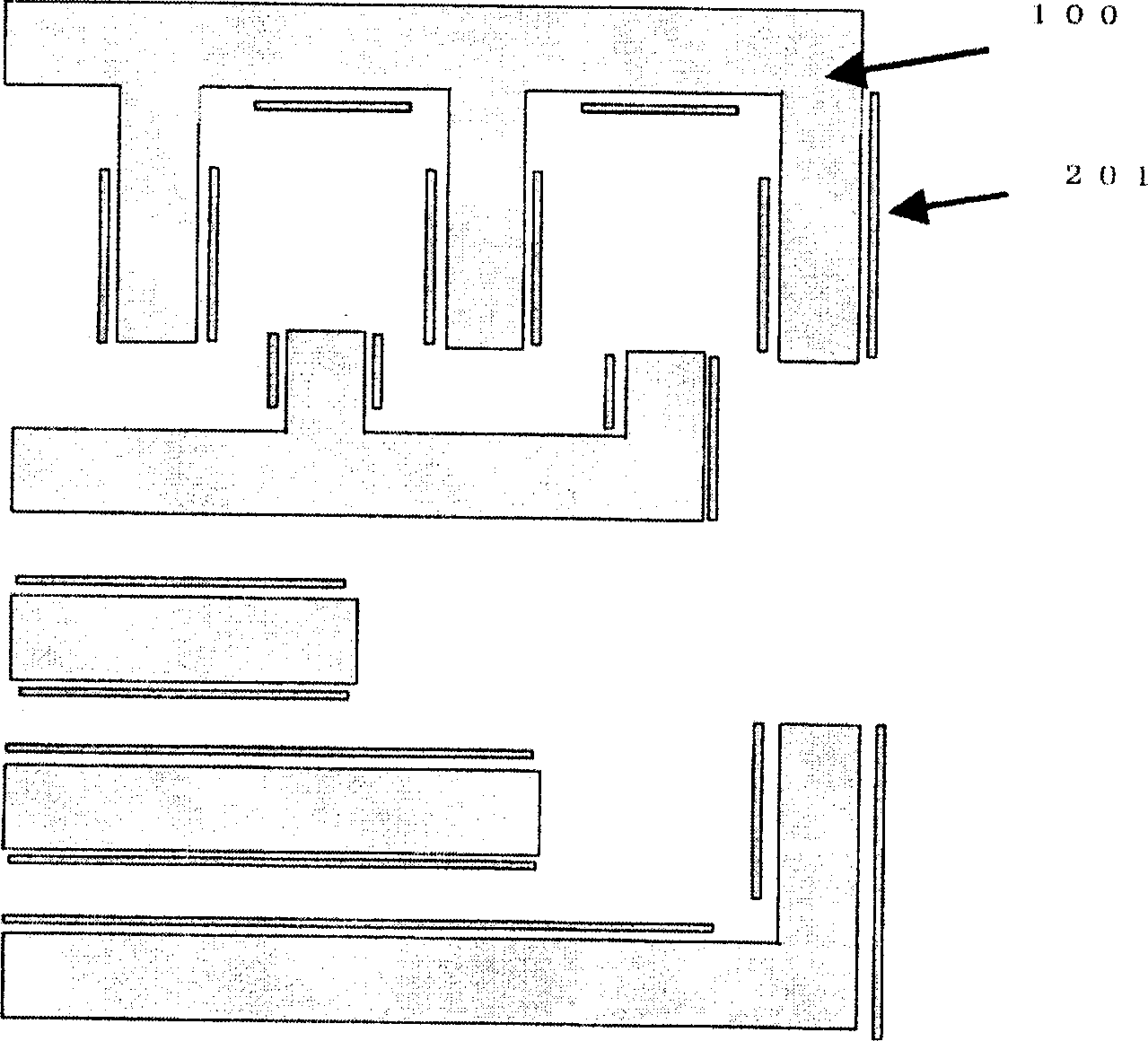

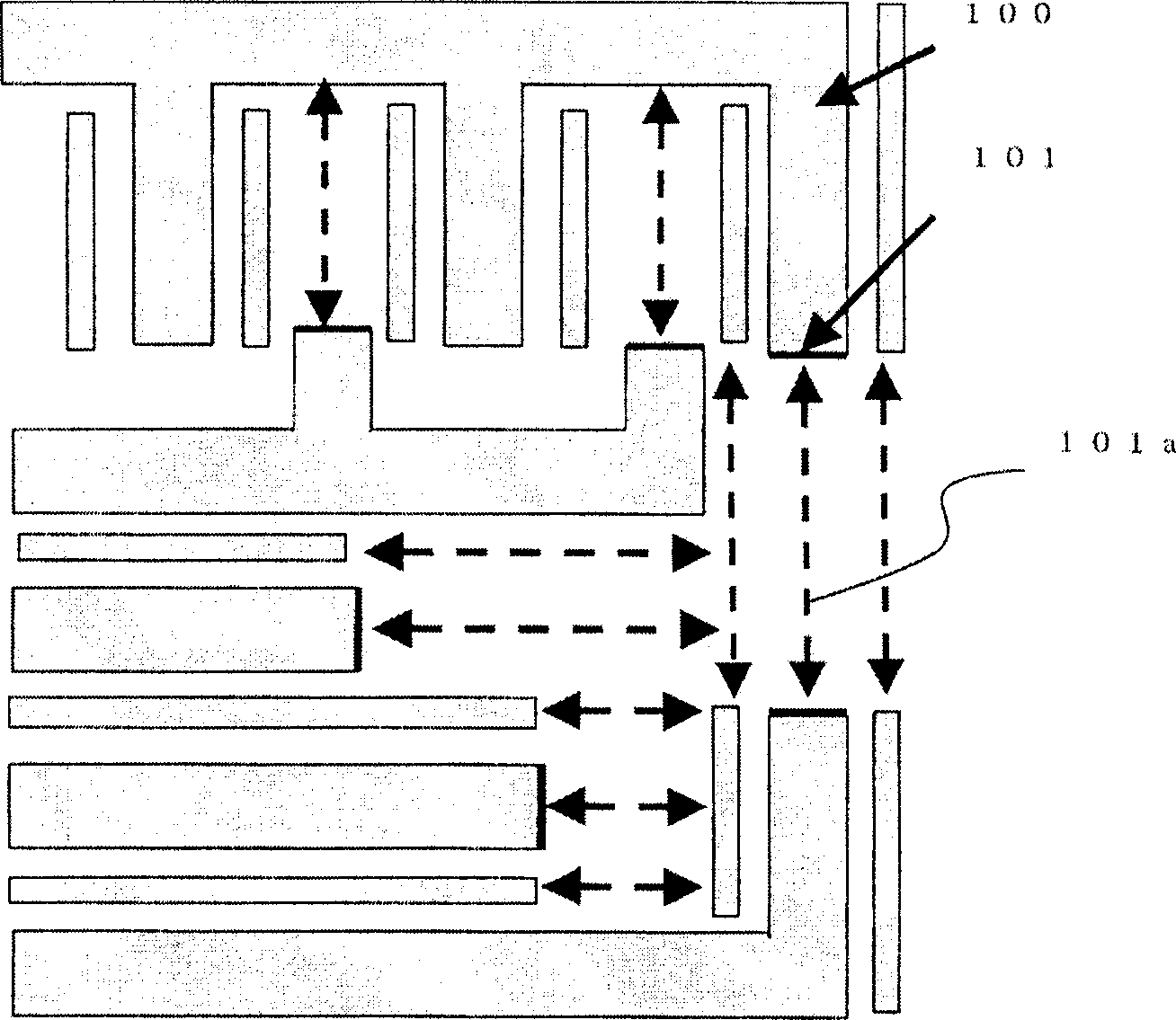

[0048] Refer to the following figure 1 A first embodiment of the present invention is described. figure 1 It is a layout plan view after forming a virtual graphic pattern according to the semiconductor design layout forming method of the first embodiment of the present invention.

[0049] exist figure 1 In , the entire layout is denoted as 100, and a dummy pattern is denoted as 200. Such as figure 1 As shown, in order to make the effect of each line end on the wafer uniform, a dummy graphic pattern 200 that has nothing to do with other wiring is placed between each wiring (non-wiring area), so that the wiring design is not included in the design layout 100. In the case of having the same pitch, make the wiring have the same pitch. That is, this pattern forming method includes the step of forming the above-mentioned dummy graphic pattern 200 , which is set so that the interval between the dummy graphic pattern 200 and the wiring becomes the same. Thereby, the receding ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More