Method of forming low dielectric constant interlayer dielectric film

A technology of low dielectric constant layer and dielectric thin film, which is applied in coatings, circuits, electrical components, etc., can solve problems including the combination of thin films, mechanical and electrical properties, and achieve the effects of safe handling, easy acquisition, and easy formation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0098] All experiments were performed in a 200 mm DxZ chamber equipped with an Advance Energy 2000rf generator on an Applied Materials Precision-5000 system using a dopant-free TEOS process kit. The experimental method included the following basic steps: initial setting and stabilization of the gas flow, supply of RF energy to generate the plasma and induce deposition, and purge / evacuate the chamber before removing the wafer. Subsequently, after each deposition with in-place C 2 f 6 +O 2 The cleaning of the chamber is followed by a step of drying the chamber.

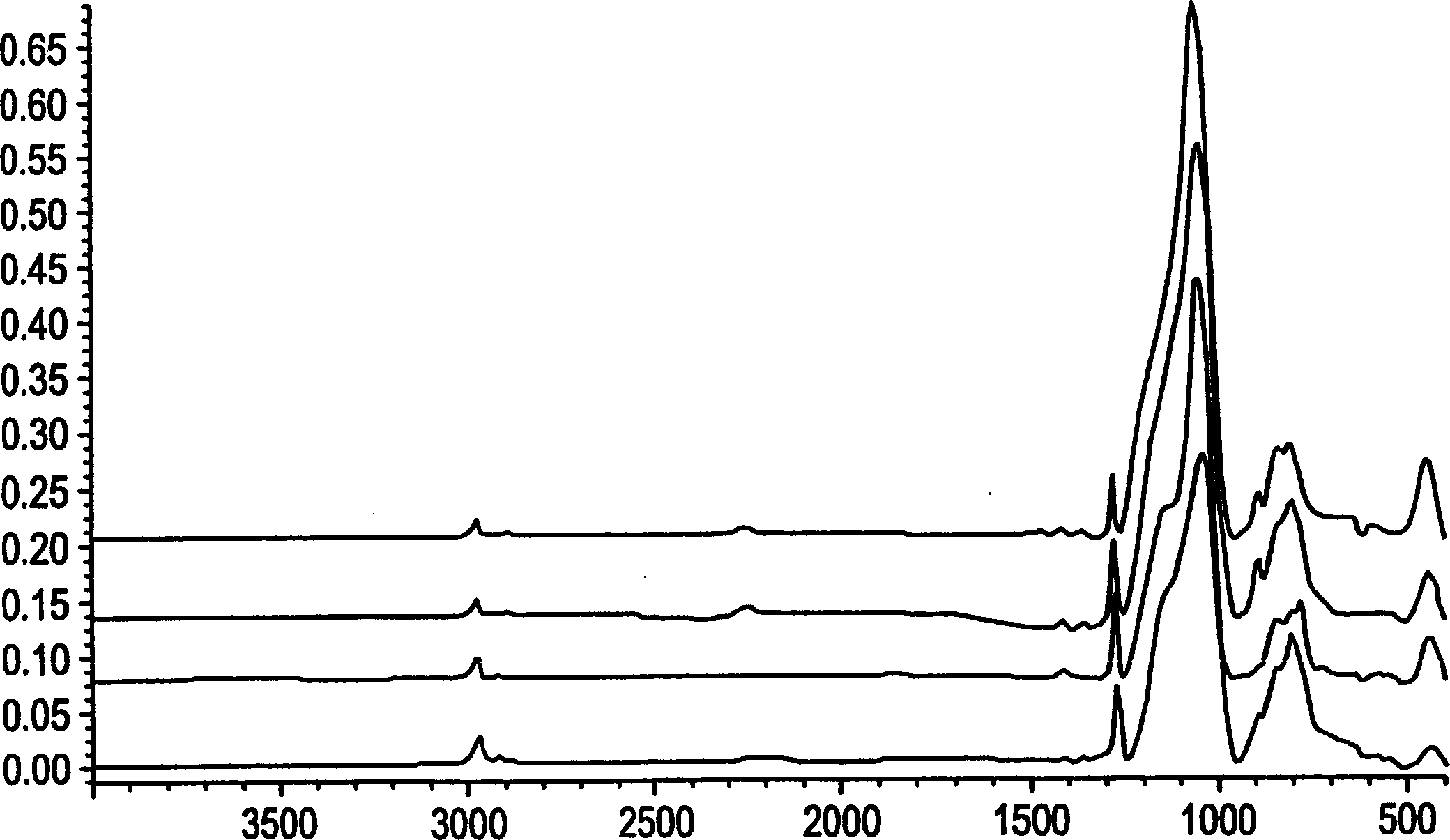

[0099] The dielectric constants of low resistivity p-type wafers (<0.02 ohm-cm) were determined using the Hg probe technique. Transmission infrared spectroscopy was performed on high resistivity wafers and all data were normalized based on film thickness. Thickness and refractive index were measured by reflectometer with 5 point average. Adhesion was measured with a tape pull test. Mechanical properties (such as Y...

Embodiment 7

[0122] A contemplated embodiment of the invention based on the use of dimethoxymethylsilane (DMOMS) as the organosilane precursor for a 200 mm silicon wafer substrate is shown in Table 8 below.

[0123] Room pressure (Torr)

[0124] It is expected that the k value will be in the range of 2.7-3.0, the Young's modulus is about 15 GPa, and the nanoindentation hardness is about 2 GPa.

[0125] A contemplated embodiment of the invention based on the use of phenoxydimethylsilane (PODMS) as the organosilane precursor for a 200 mm silicon wafer substrate is shown in Table 9 below.

[0126] Room pressure (Torr)

[0127] It is expected that the k value will be in the range of 2.7-3.0, the Young's modulus is about 15 GPa, and the nanoindentation hardness is about 2 GPa.

[0128] A contemplated embodiment of the invention based on the use of di-tert-butoxymethylsilane (DTBMS) as the organosilane precursor for a 200 mm silicon wafer substrate is shown in Table 10 below....

PUM

| Property | Measurement | Unit |

|---|---|---|

| hardness | aaaaa | aaaaa |

| hardness | aaaaa | aaaaa |

| hardness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More