Voltage level converter

A voltage level, voltage source technology, applied in the direction of logic circuit connection/interface layout, logic circuit coupling/interface using field effect transistors, etc., can solve the problems of slow switching speed, thick gate, high threshold voltage, etc. and jitter reduction effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

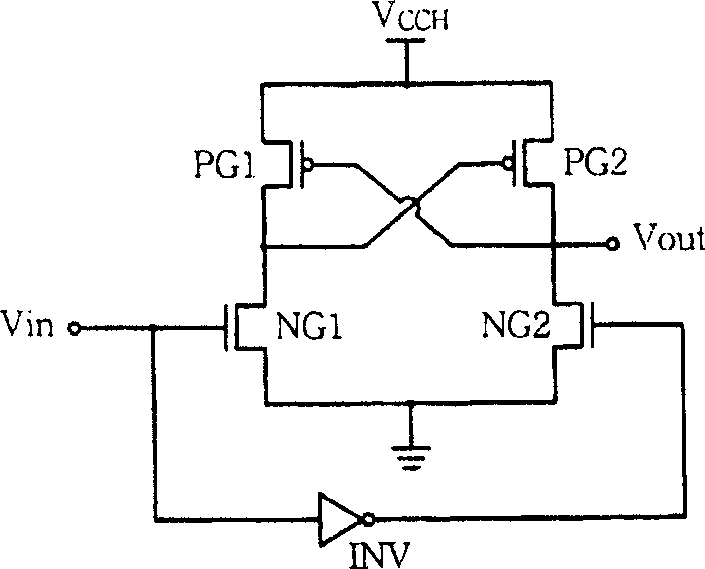

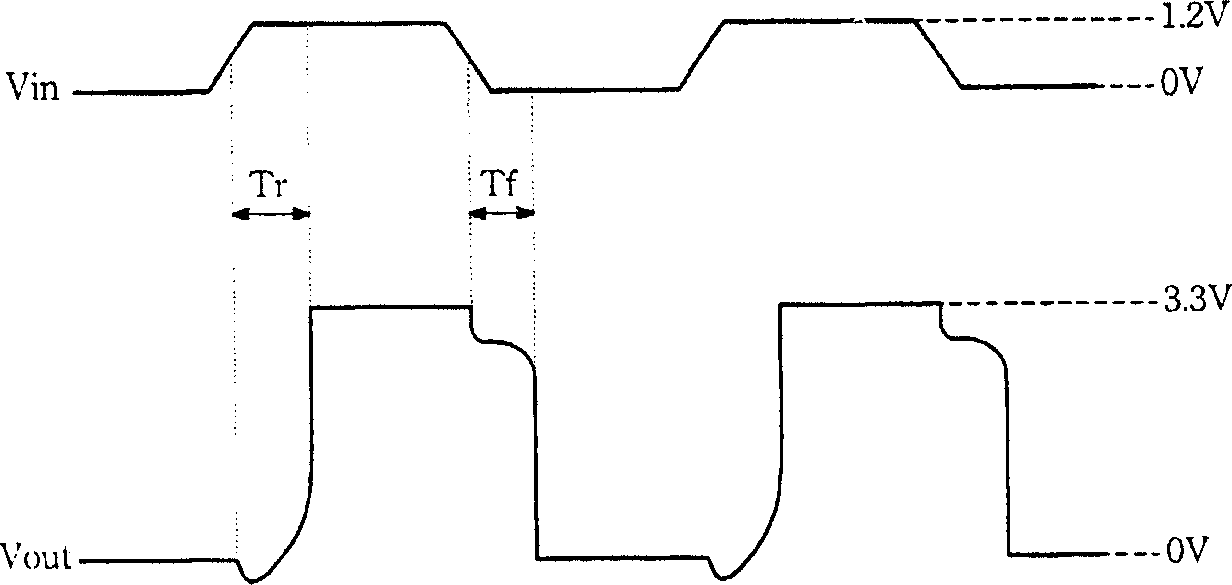

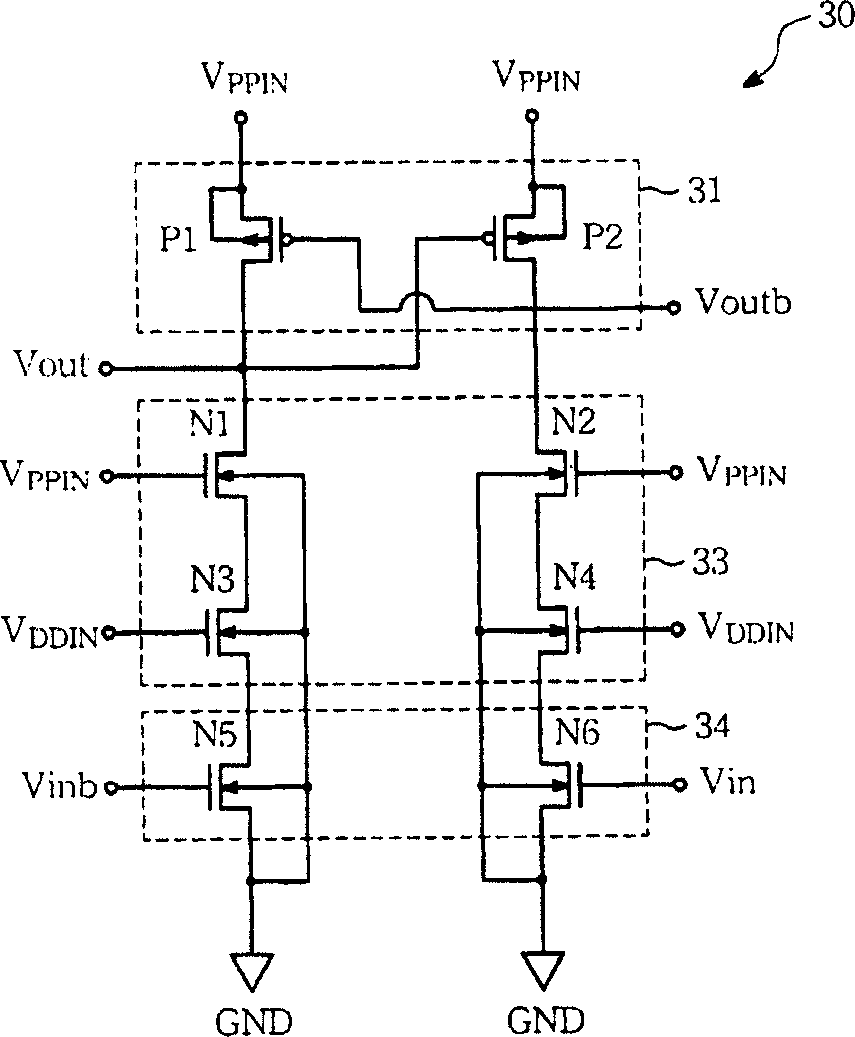

[0033] see image 3 , shows an embodiment of the voltage level shifter of the present invention. As shown in the figure, the voltage level shifter 30 has a pull-up circuit 31, a voltage drop circuit 33, and a pull-down circuit 34, the pull-up circuit 31 has two PMOS transistors P1 and P2, and the voltage drop circuit 33 has There are four NMOS transistors N1, N2, N3 and N4, and the pull-down circuit 34 has two NMOS transistors N5 and N6. In this embodiment, a DC voltage VPPIN and a DC voltage source VDDIN are provided as the operating voltage of the voltage level shifter 30, and the NMOS transistors N5 and N6 are connected to the ground GND for driving the voltage level shifter 30 to An input voltage Vin is converted into an output voltage Vout, wherein the DC voltage VPPIN is 3.3 volts, the DC voltage VDDIN is 1.2 volts, the input voltage Vin is a rectangular wave between 0 volts and 1.2 volts, and the output voltage Vout is between 0 volts and the corresponding wave betwee...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More