Patents

Literature

170 results about "Voltage noise" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

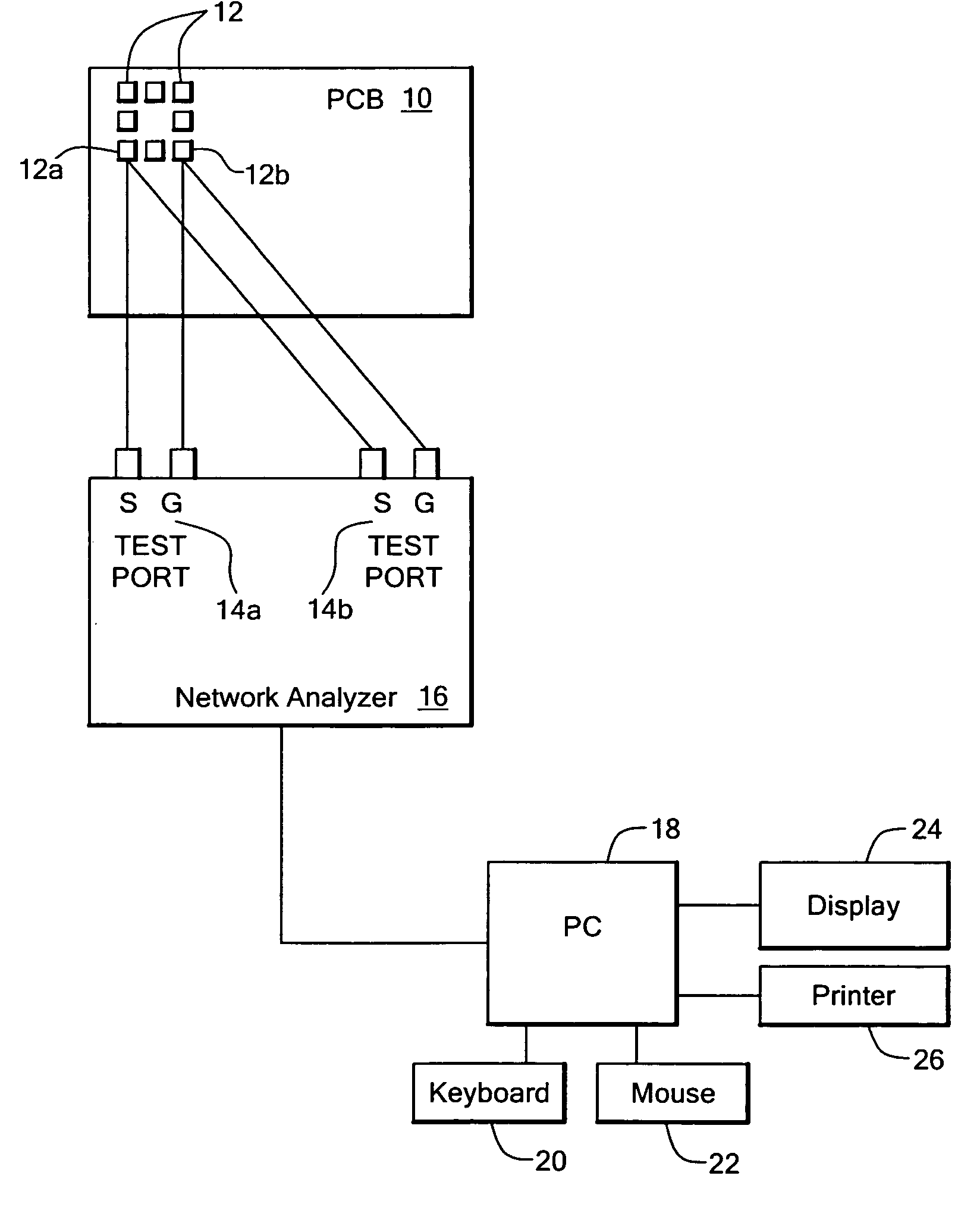

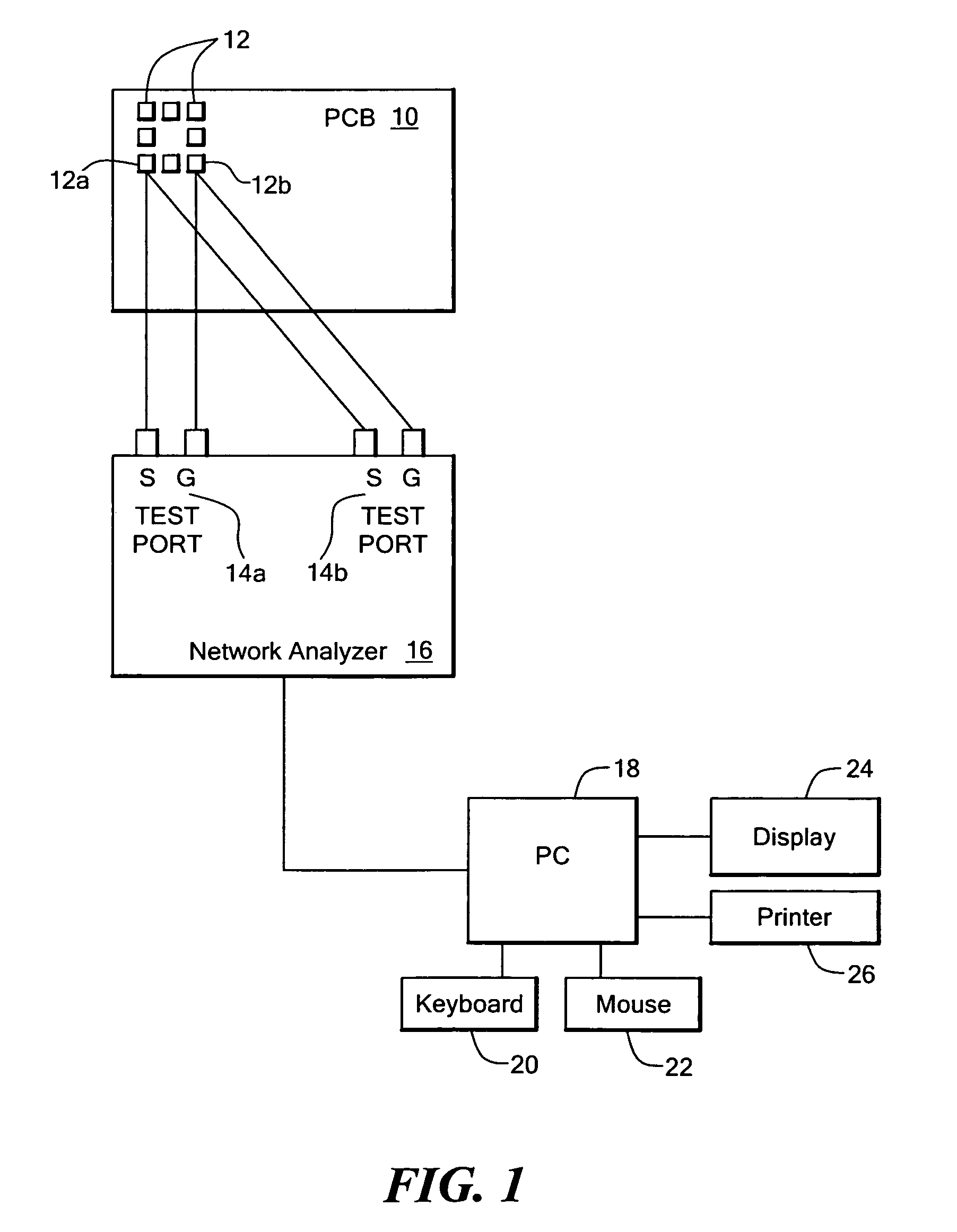

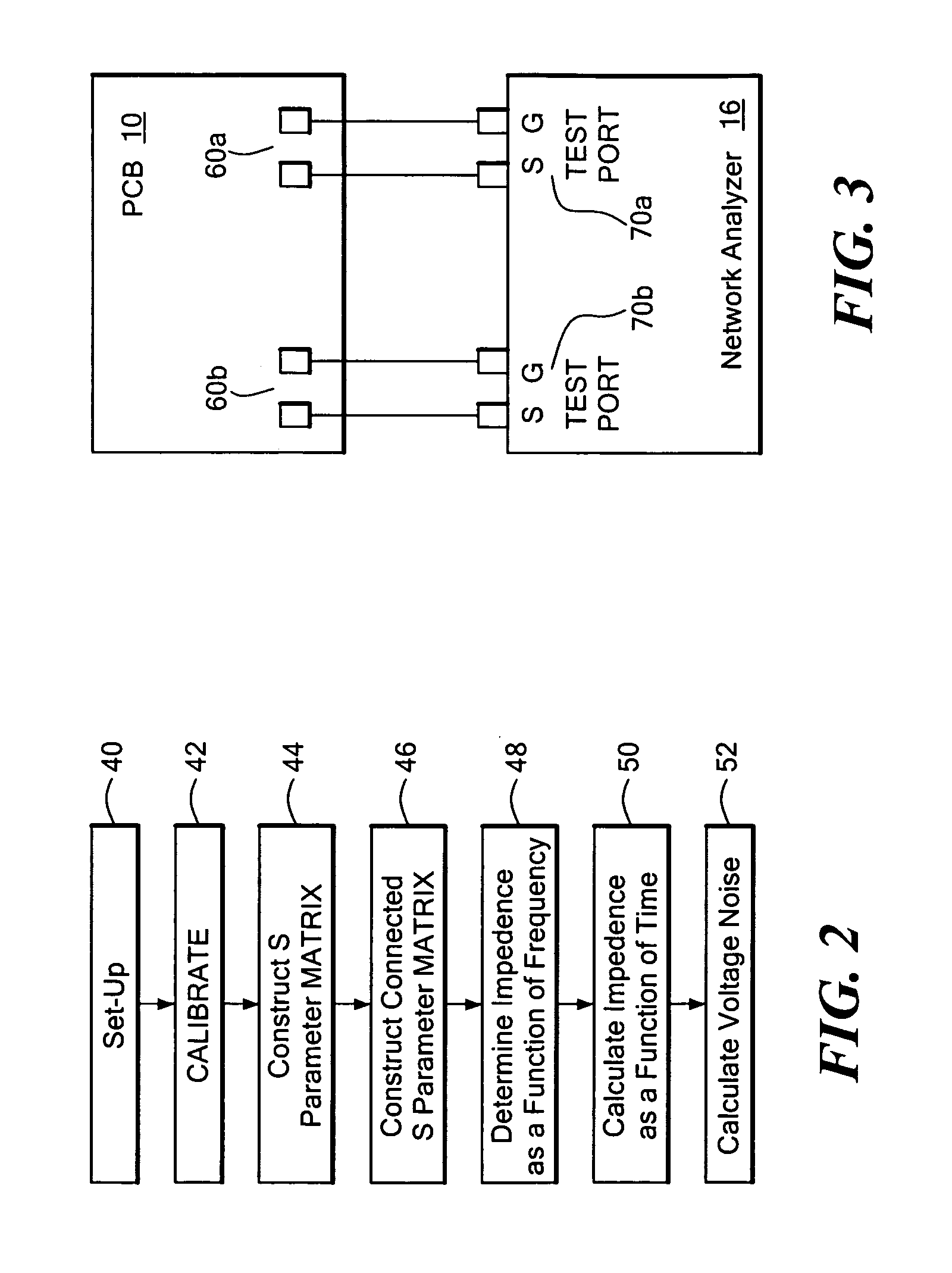

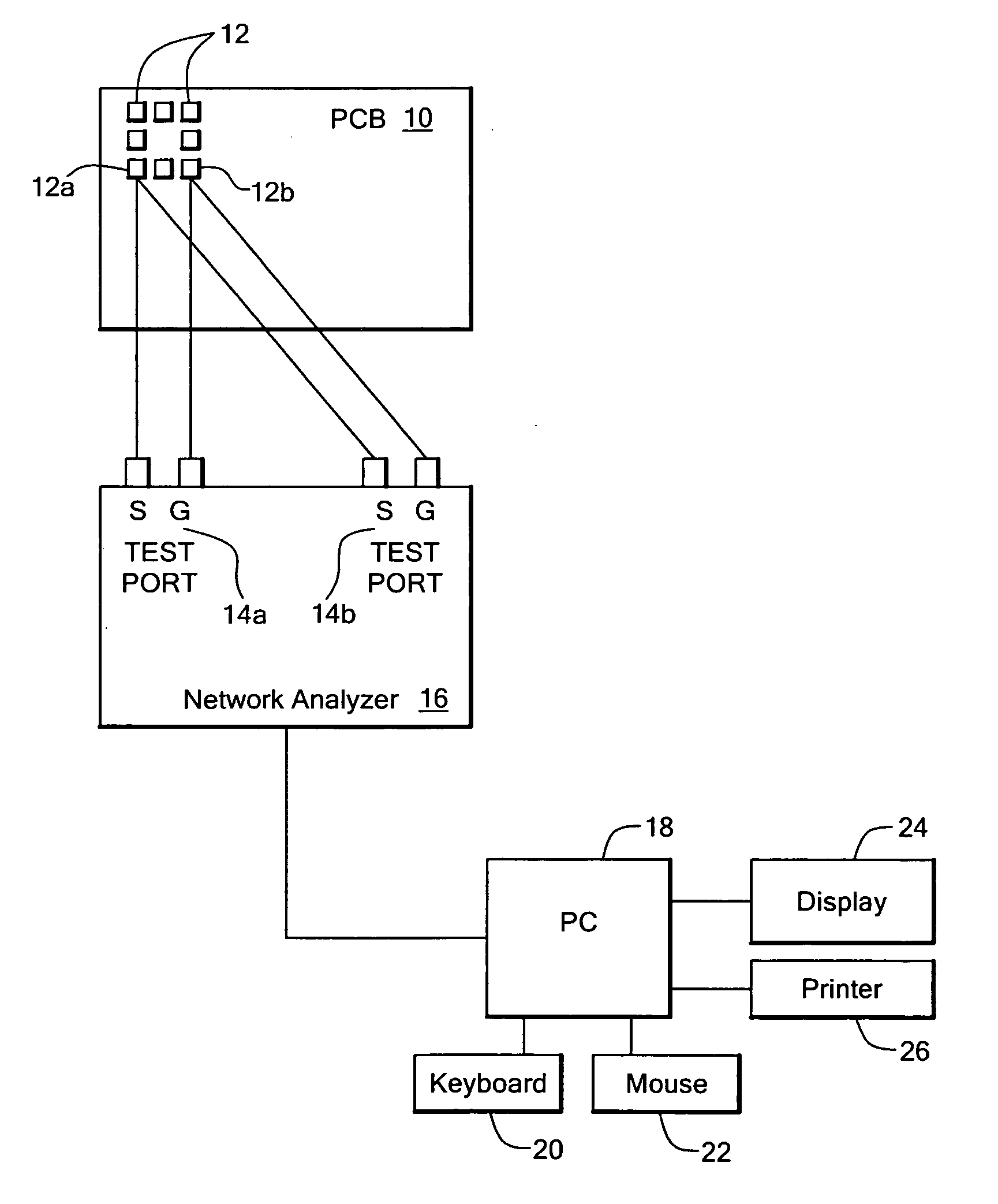

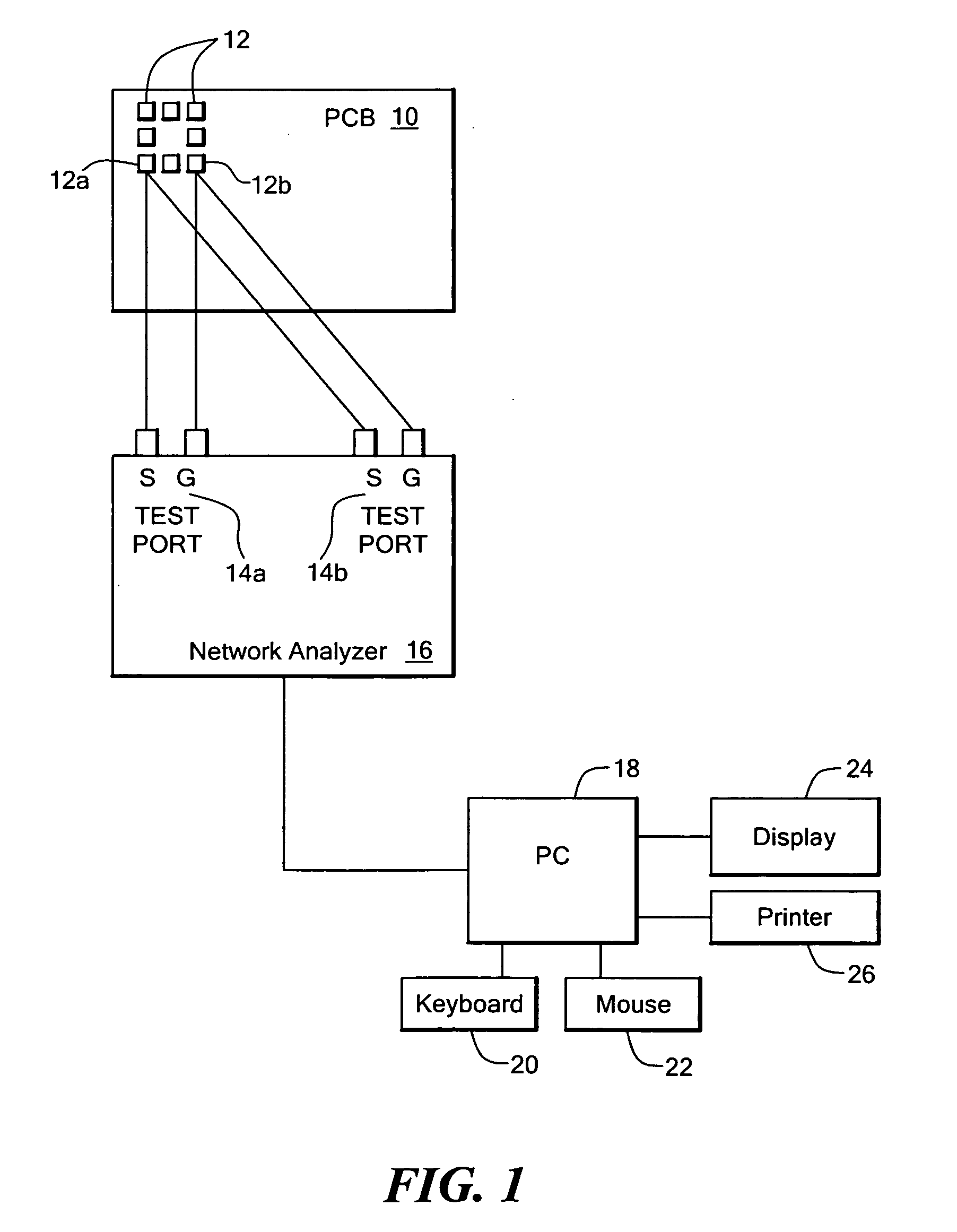

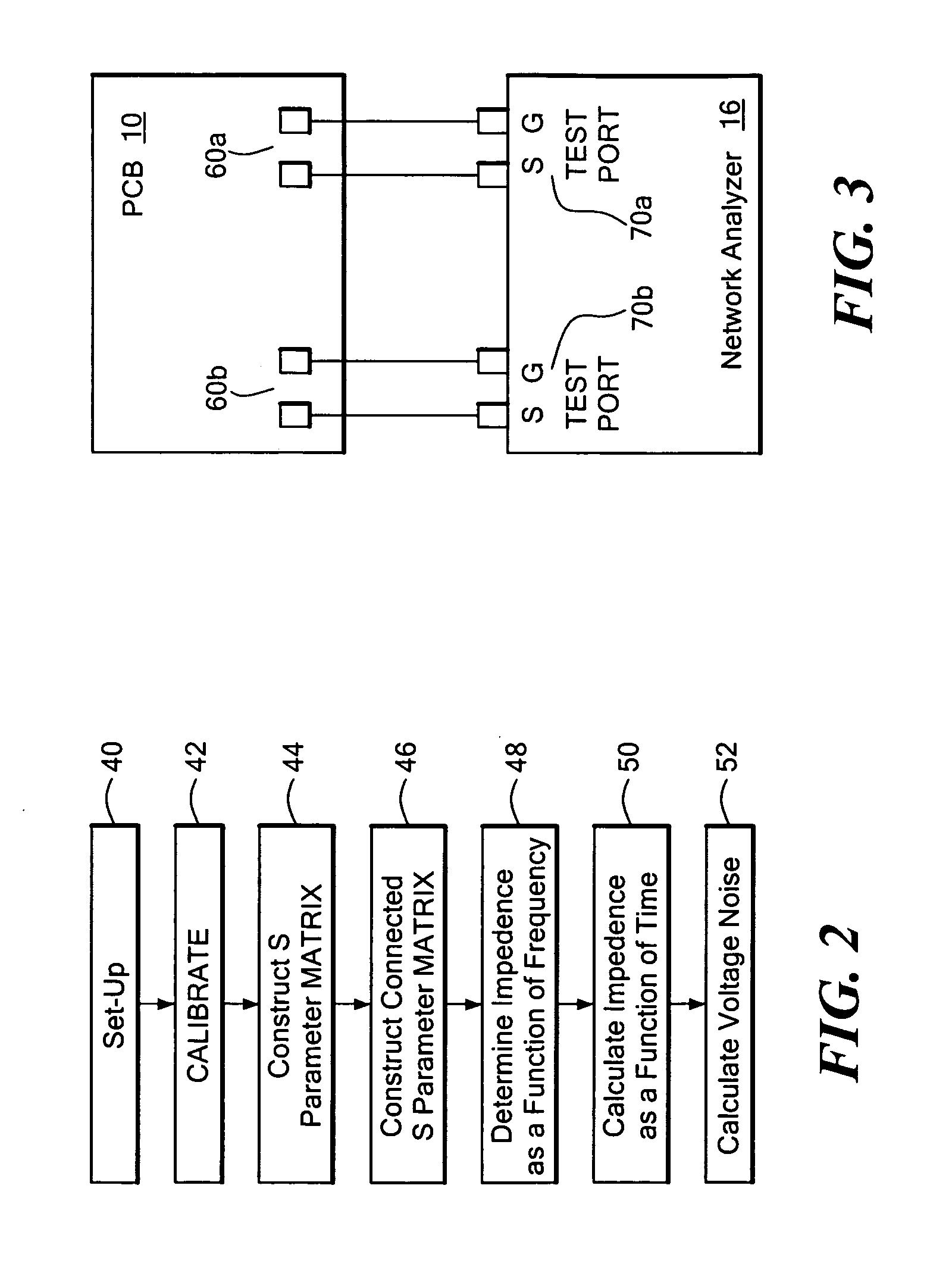

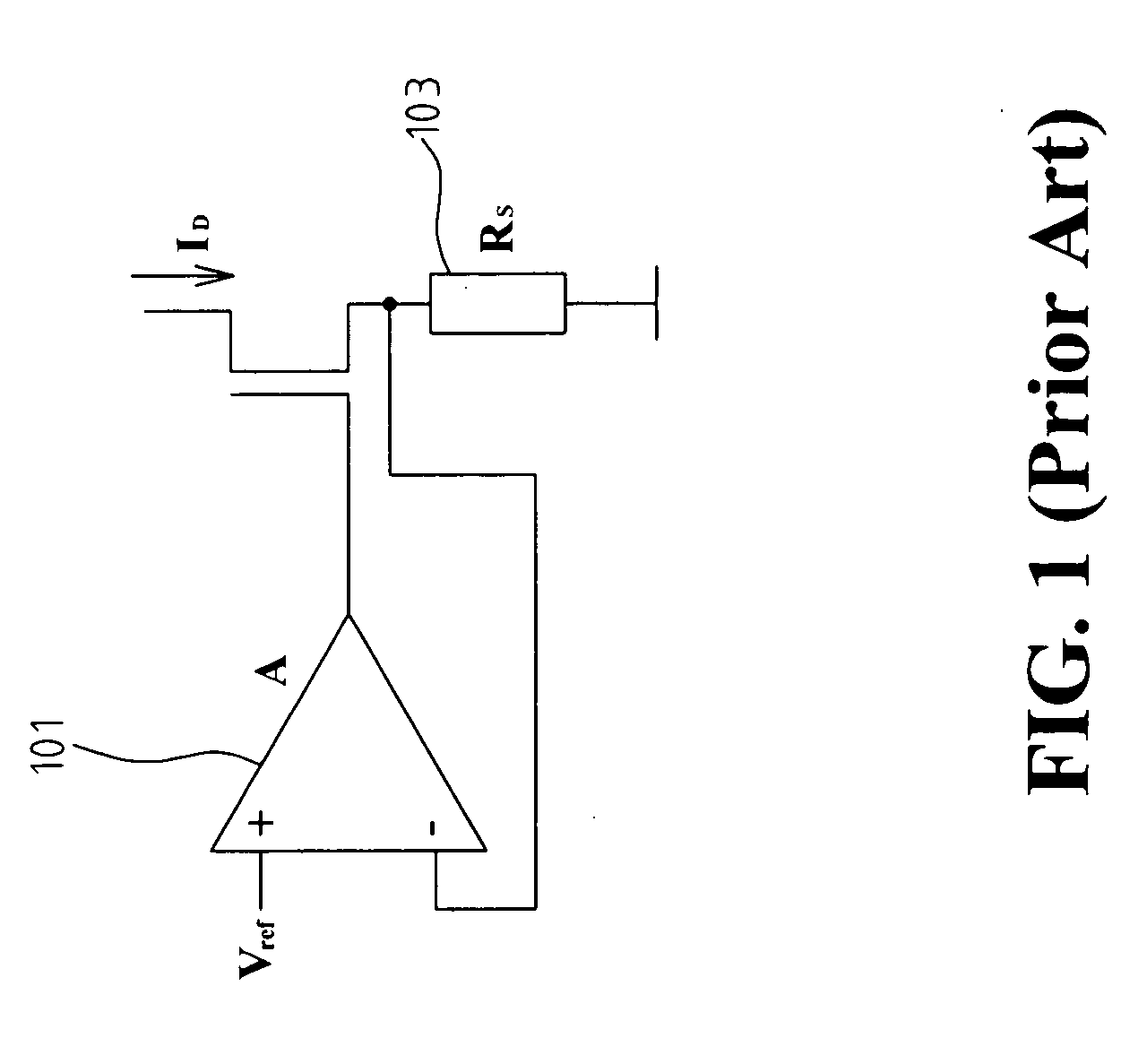

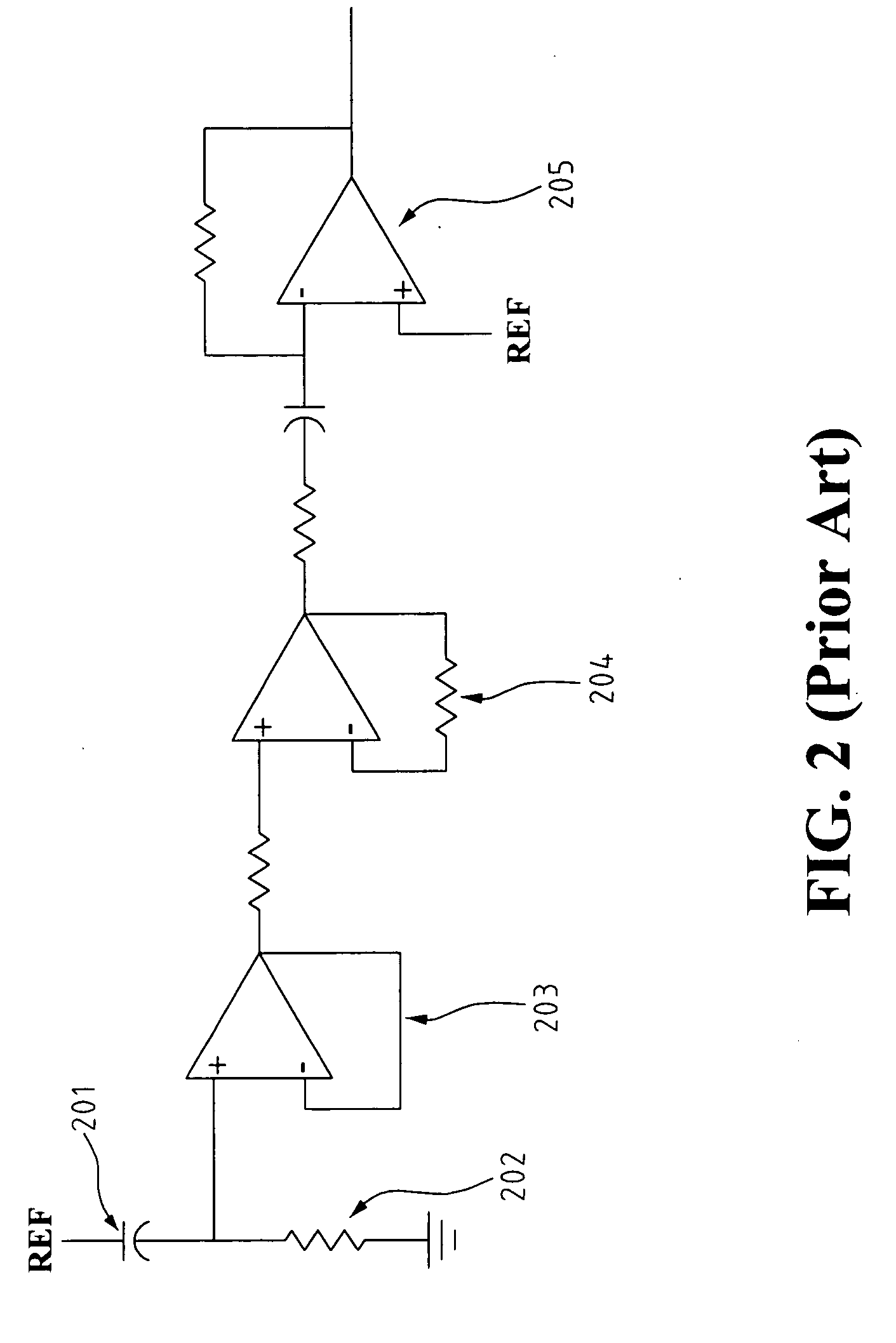

Method and system of characterizing a device under test

A system and method of characterizing a device under test wherein a signal is injected into the device under test, the response to the injected signal is measured to determine the impedance of the device under test in the frequency domain, the impedance is converted to the time domain, and the voltage noise of the device under test is calculated based on the impedance of the device under test in the time domain.

Owner:COLE J BRADFORD

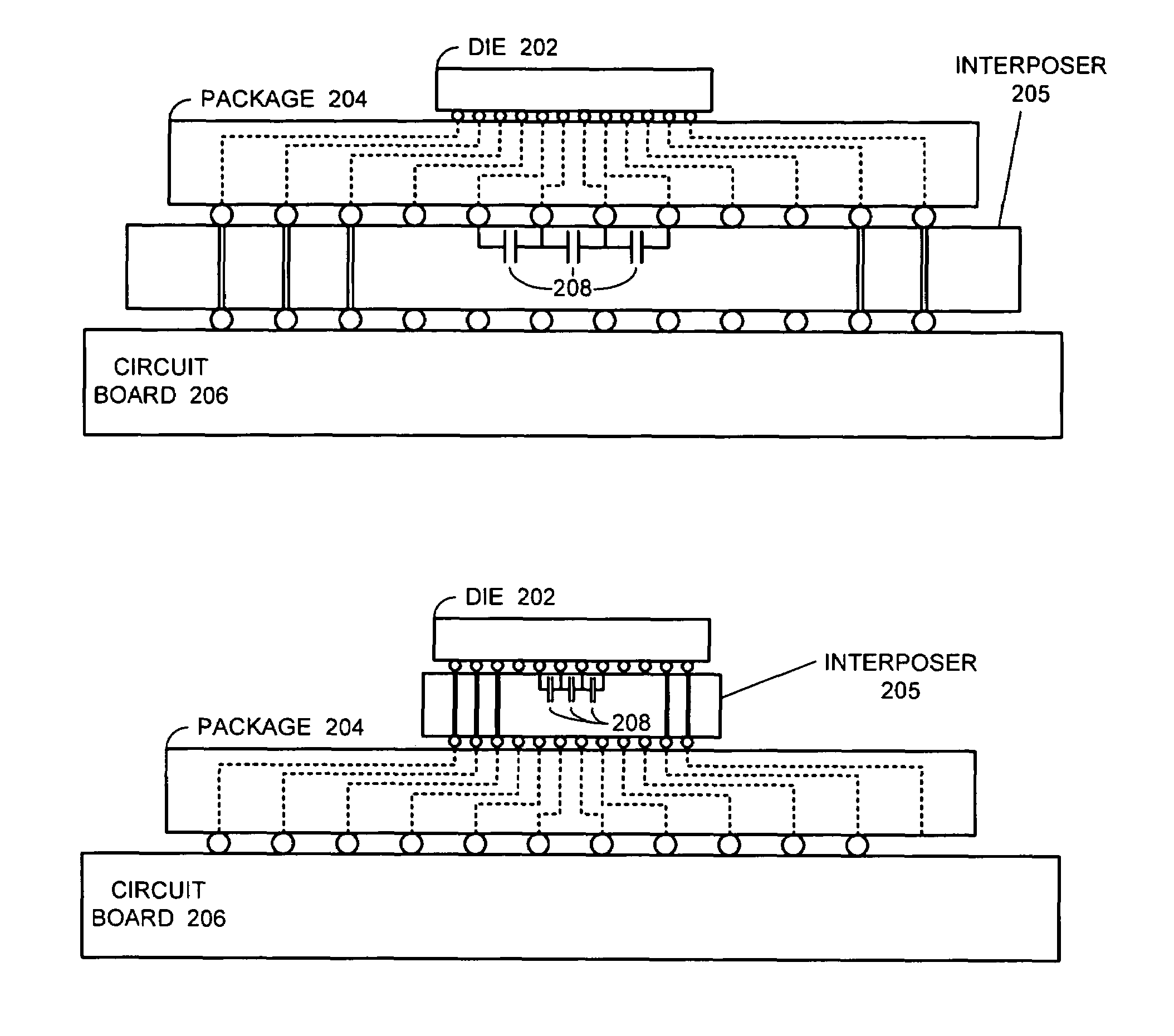

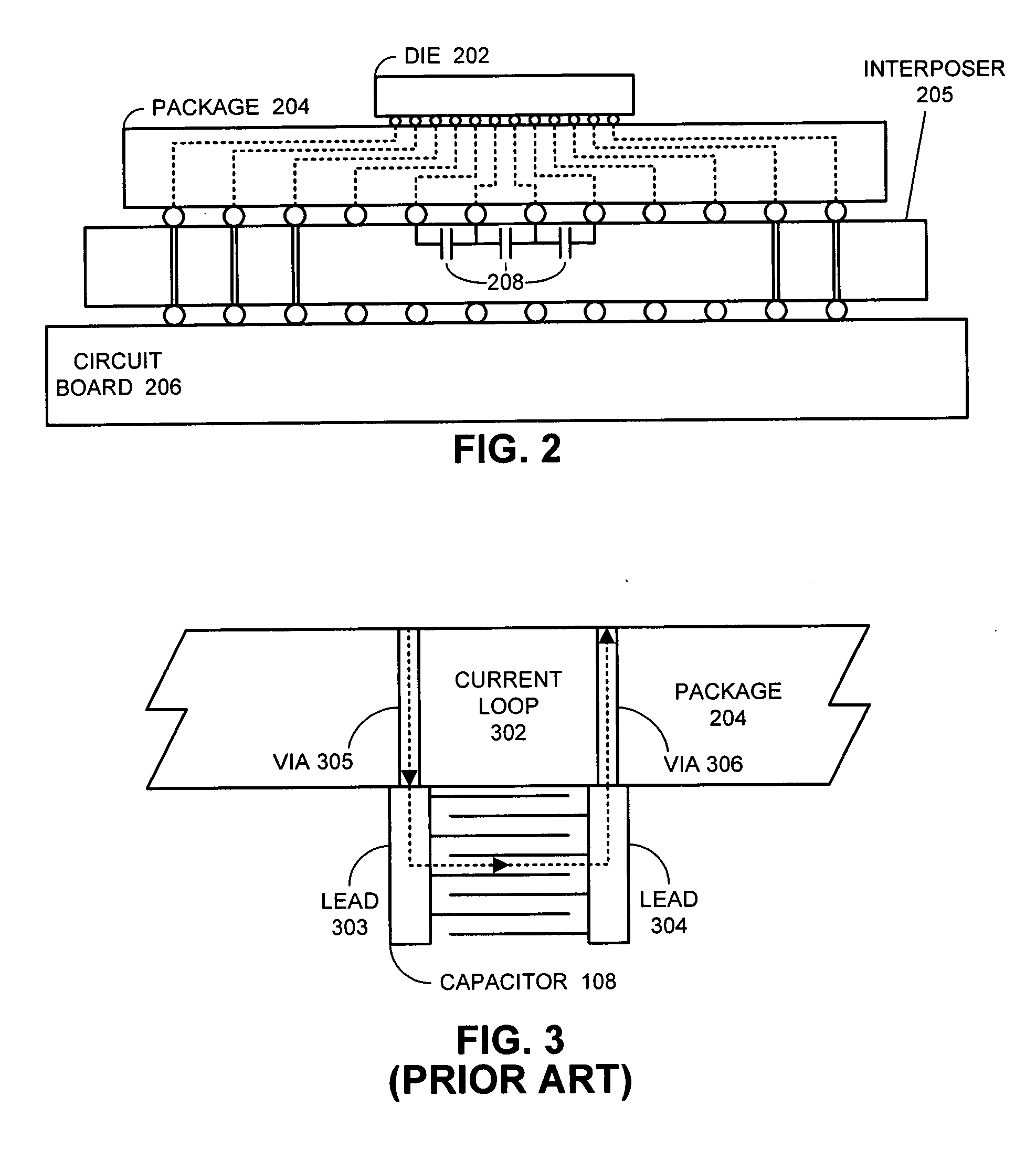

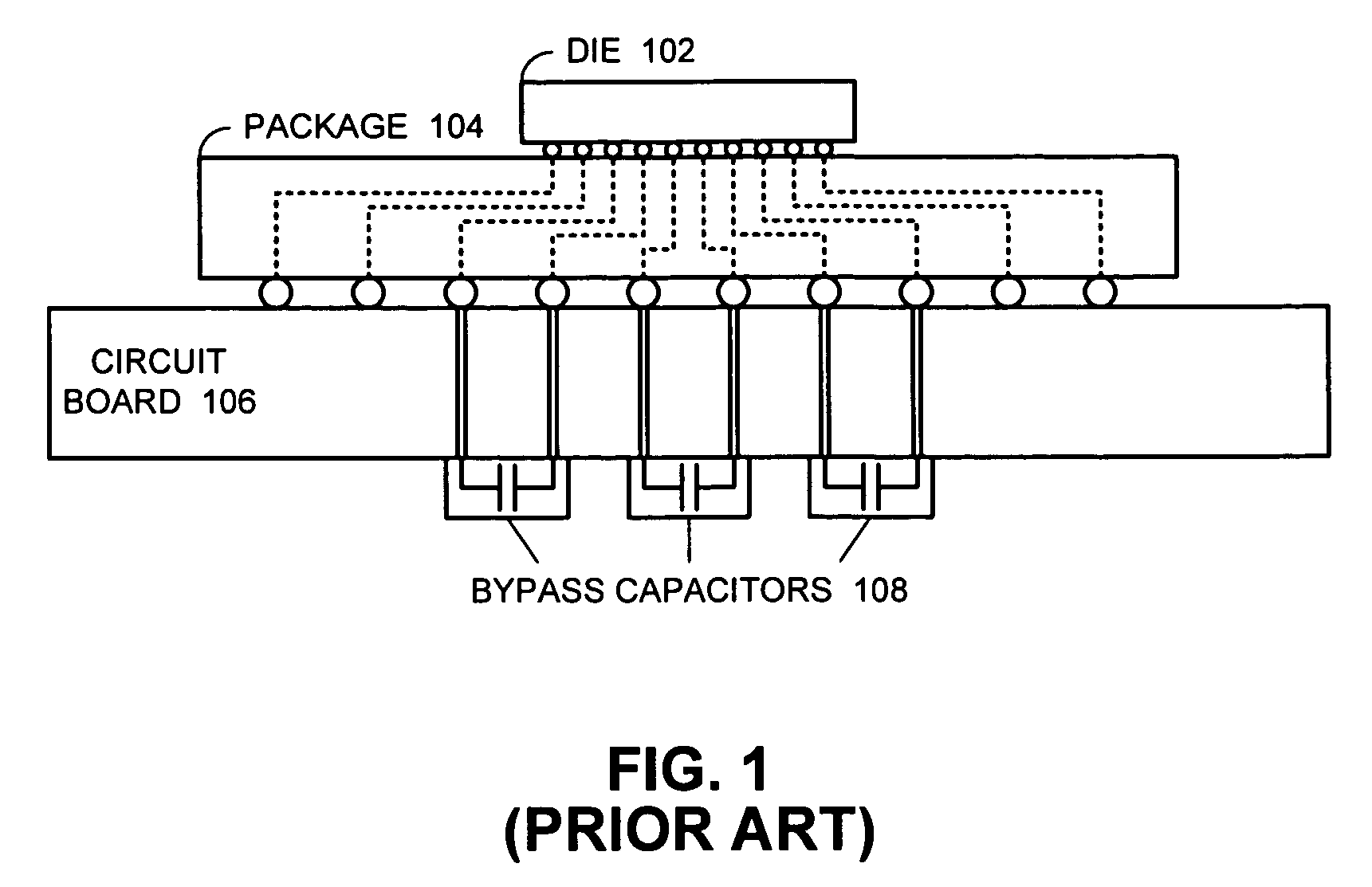

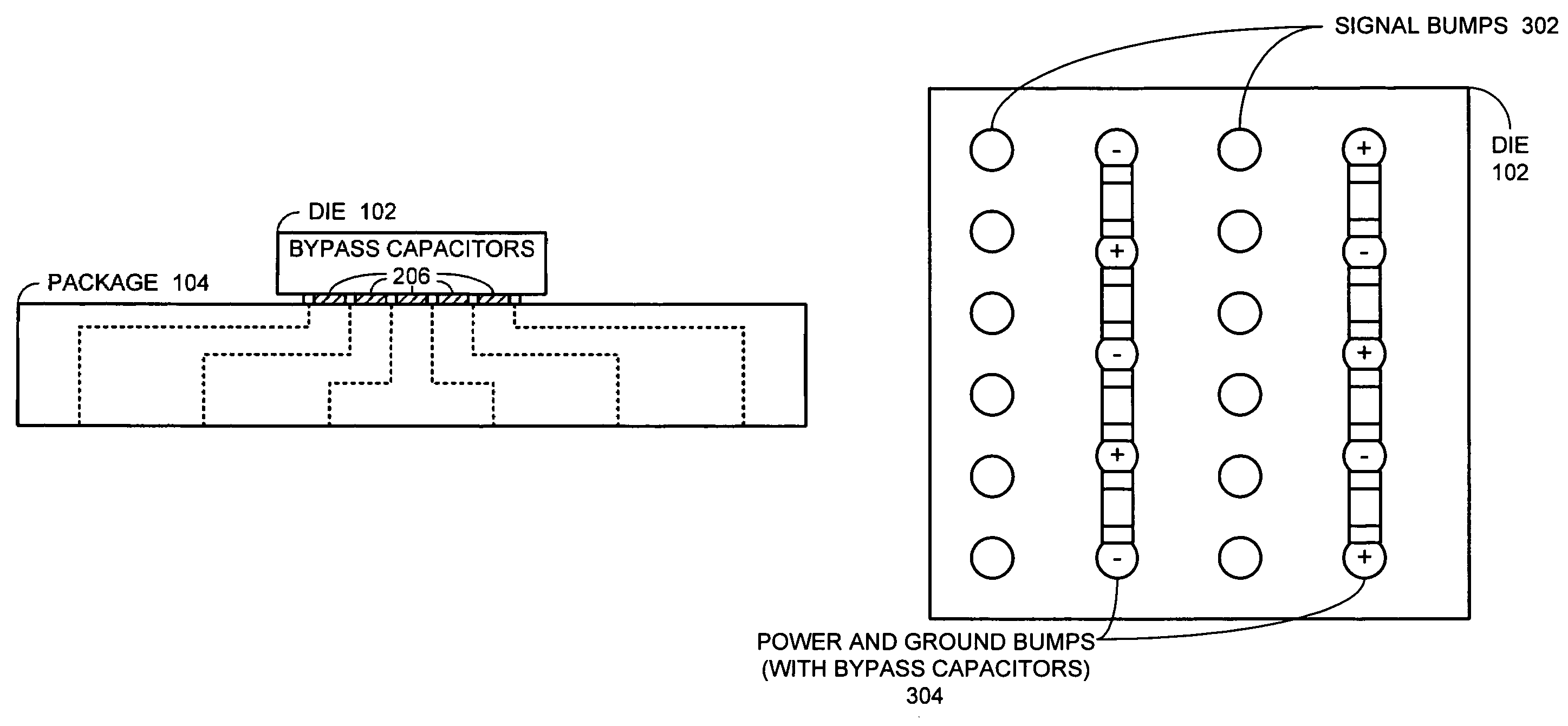

Interposer containing bypass capacitors for reducing voltage noise in an IC device

InactiveUS7268419B2Reduce voltageReduce noiseSemiconductor/solid-state device detailsSolid-state devicesElectricityElectrical connection

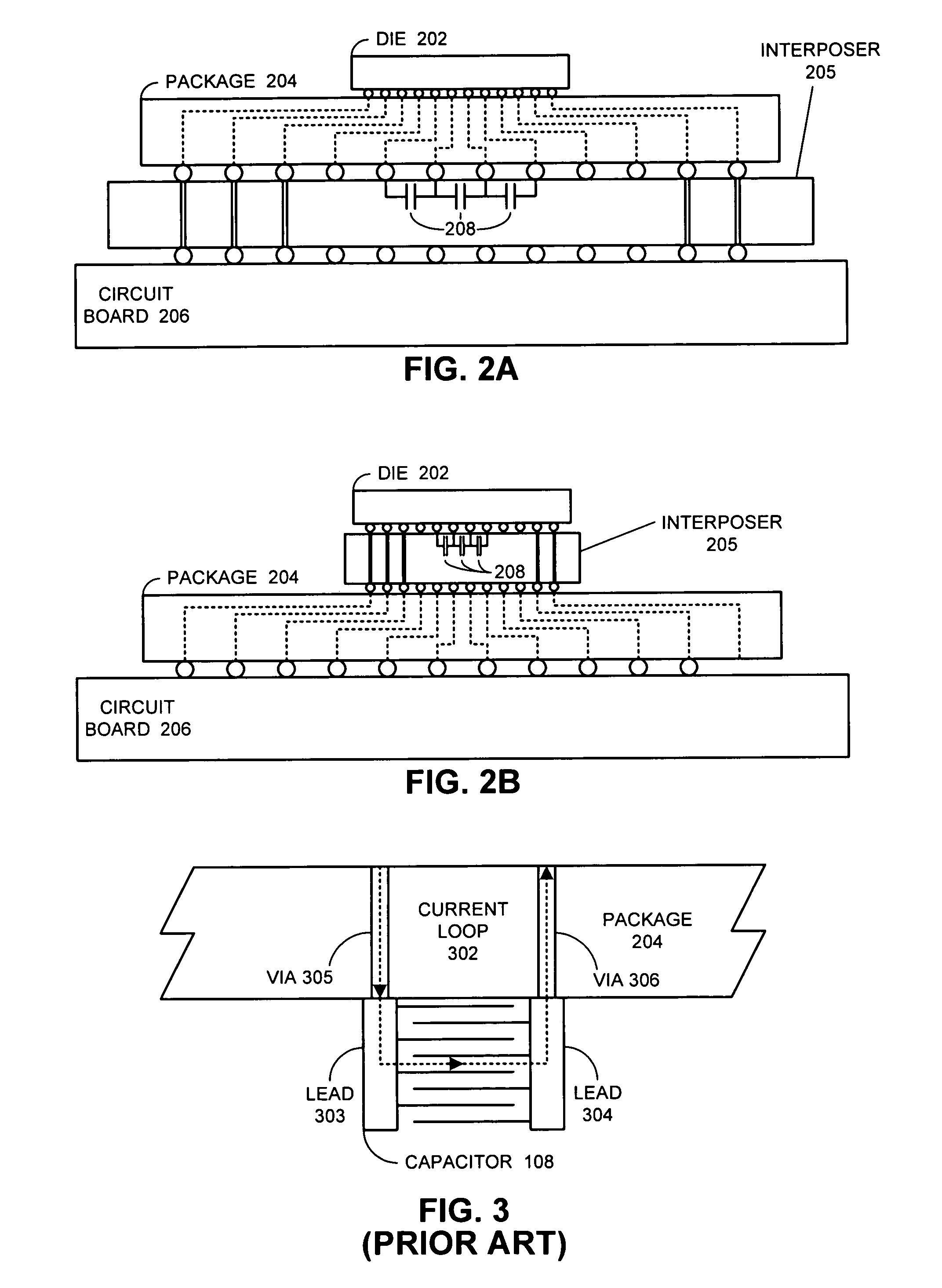

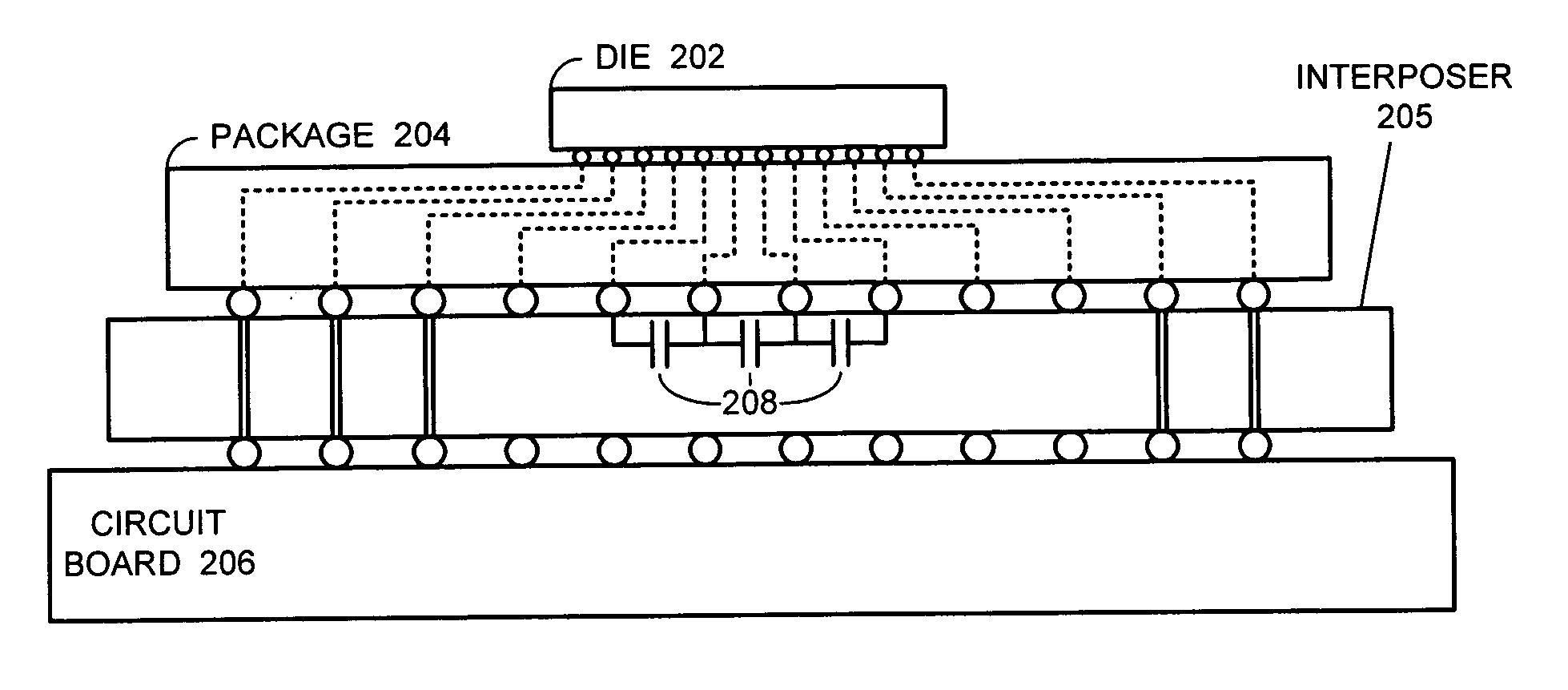

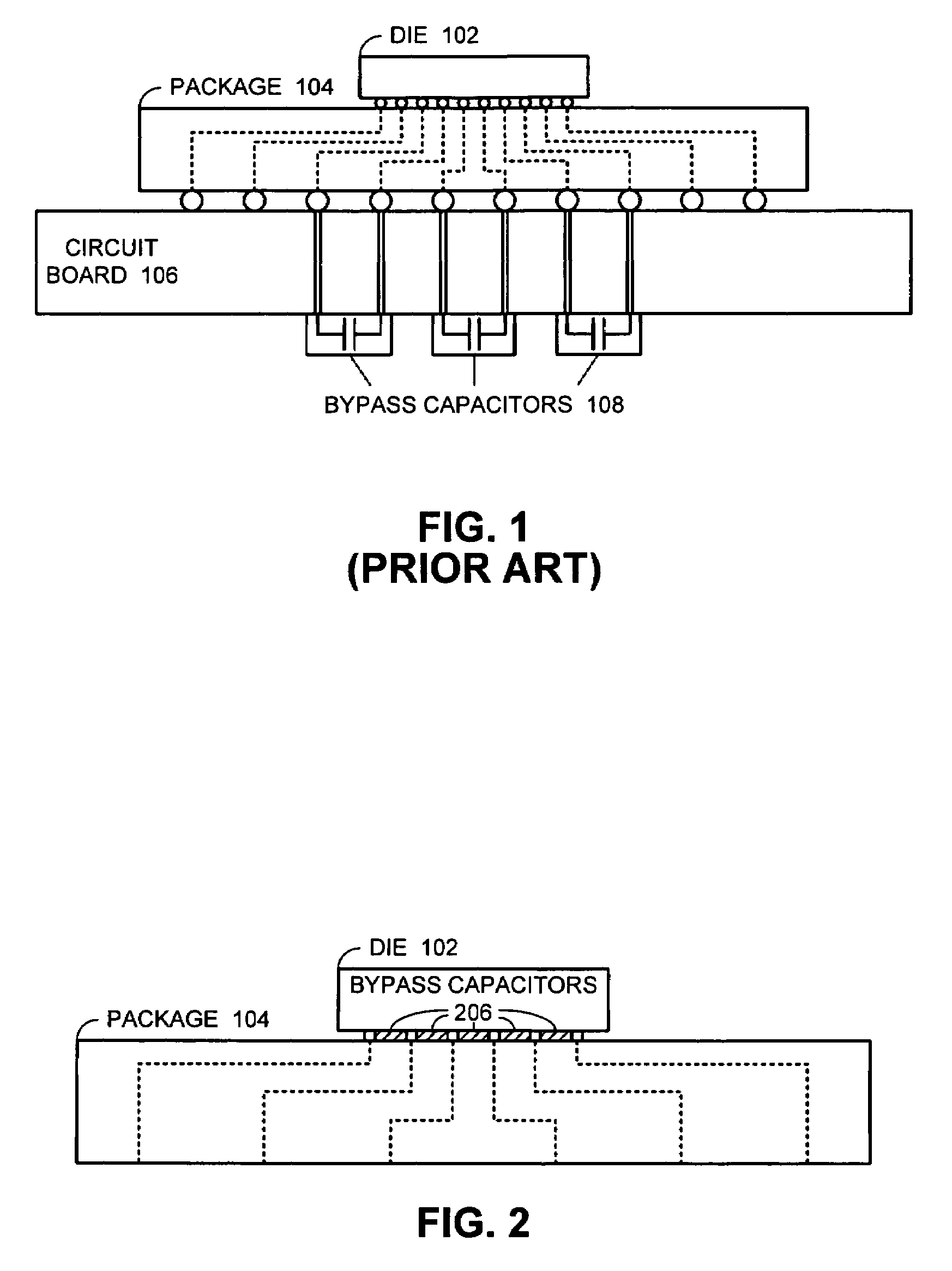

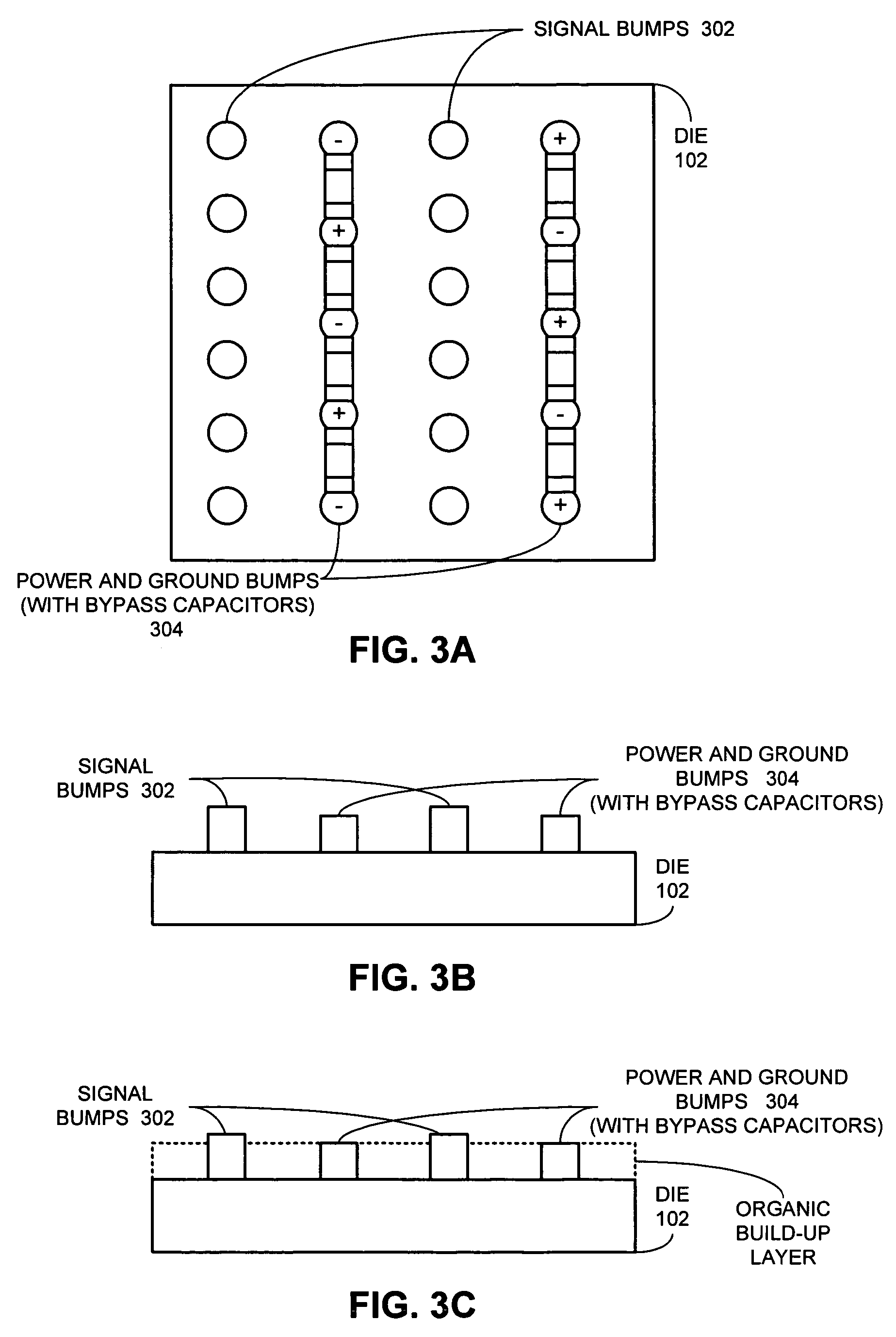

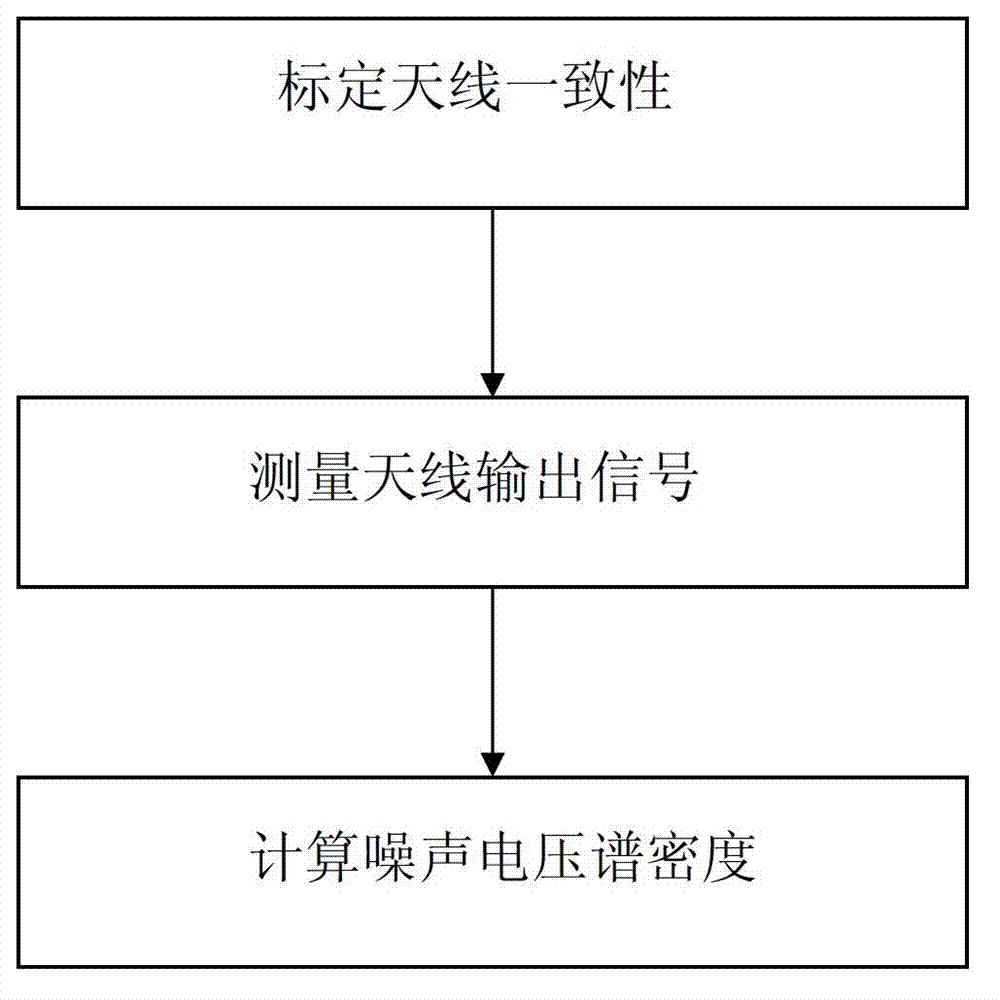

One embodiment of the present invention provides an apparatus that reduces voltage noise for an integrated circuit (IC) device. This apparatus includes an interposer, which is configured to be sandwiched between the IC device and a circuit board. This interposer has a bottom surface, which is configured to receive electrical connections for power, ground and other signals from the circuit board, and a top surface, which is configured to provide electrical connections for power, ground and the other signals to the IC device. A plurality of bypass capacitors are integrated into the interposer and are coupled between the power and ground connections for the IC device, so that the plurality of bypass capacitors reduce voltage noise between the power and ground connections for the IC device.

Owner:APPLE INC

Interposer containing bypass capacitors for reducing voltage noise in an IC device

InactiveUS20050280146A1Reduce voltage noiseReduce voltageSemiconductor/solid-state device detailsSolid-state devicesElectricityElectrical connection

One embodiment of the present invention provides an apparatus that reduces voltage noise for an integrated circuit (IC) device. This apparatus includes an interposer, which is configured to be sandwiched between the IC device and a circuit board. This interposer has a bottom surface, which is configured to receive electrical connections for power, ground and other signals from the circuit board, and a top surface, which is configured to provide electrical connections for power, ground and the other signals to the IC device. A plurality of bypass capacitors are integrated into the interposer and are coupled between the power and ground connections for the IC device, so that the plurality of bypass capacitors reduce voltage noise between the power and ground connections for the IC device.

Owner:APPLE INC

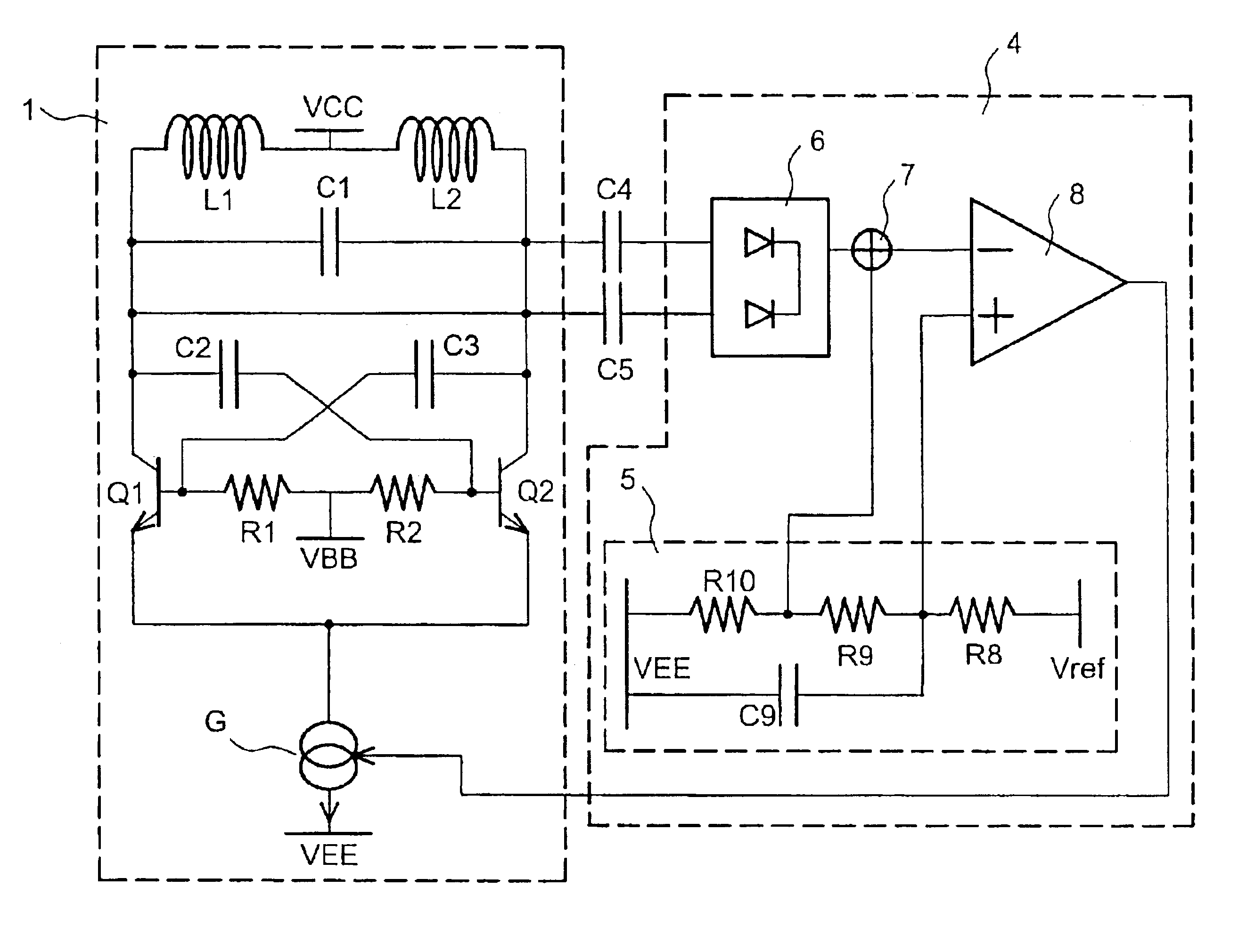

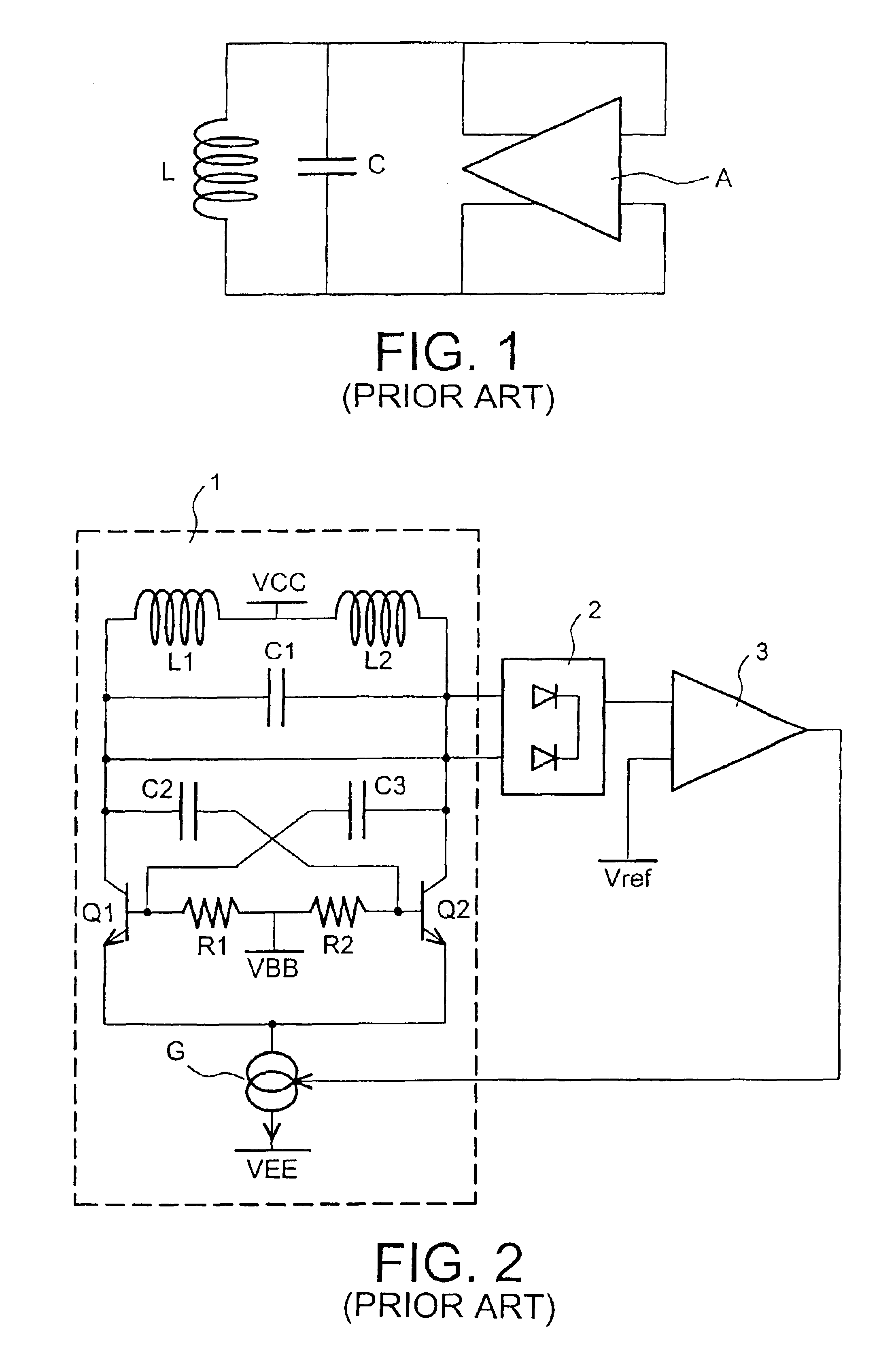

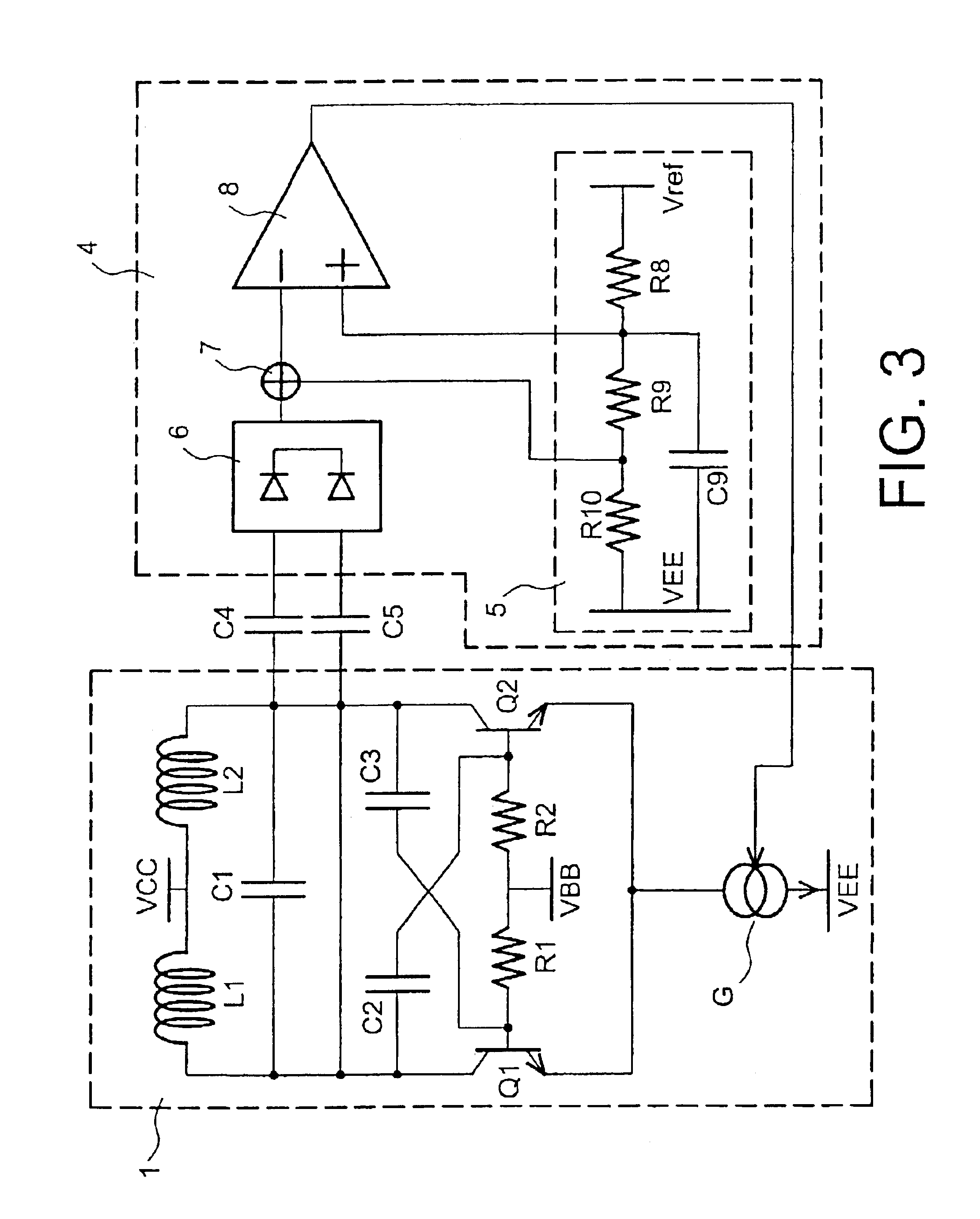

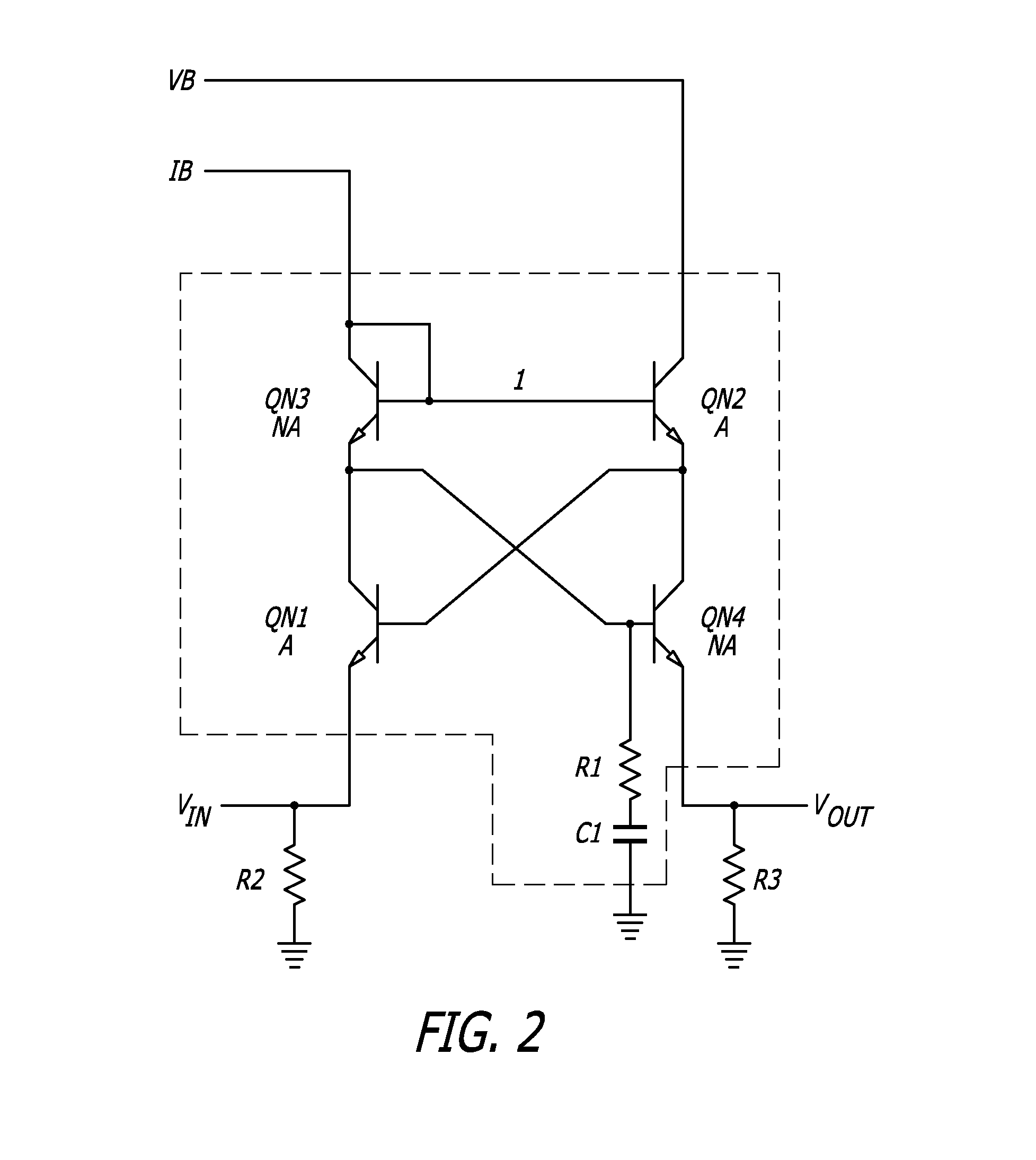

Amplitude control device for electrical oscillator and electrical oscillator comprising such a device

InactiveUS6838952B2Reduce contributionPulse automatic controlElectric pulse generatorControl signalAmplitude control

An amplitude control device for a signal output by an oscillator includes a rectification circuit for rectifying the output signal, and a differential amplification circuit for generating a biasing current control signal for the oscillator. The biasing current control signal is based upon the output signal from the rectification circuit and a reference voltage. A dividing bridge and an adder are designed so that only a fraction of the reference voltage is used to define the amplitude of the oscillations. The contribution made to the oscillator phase noise by the reference voltage noise is considerably reduced.

Owner:ST ERICSSON SA

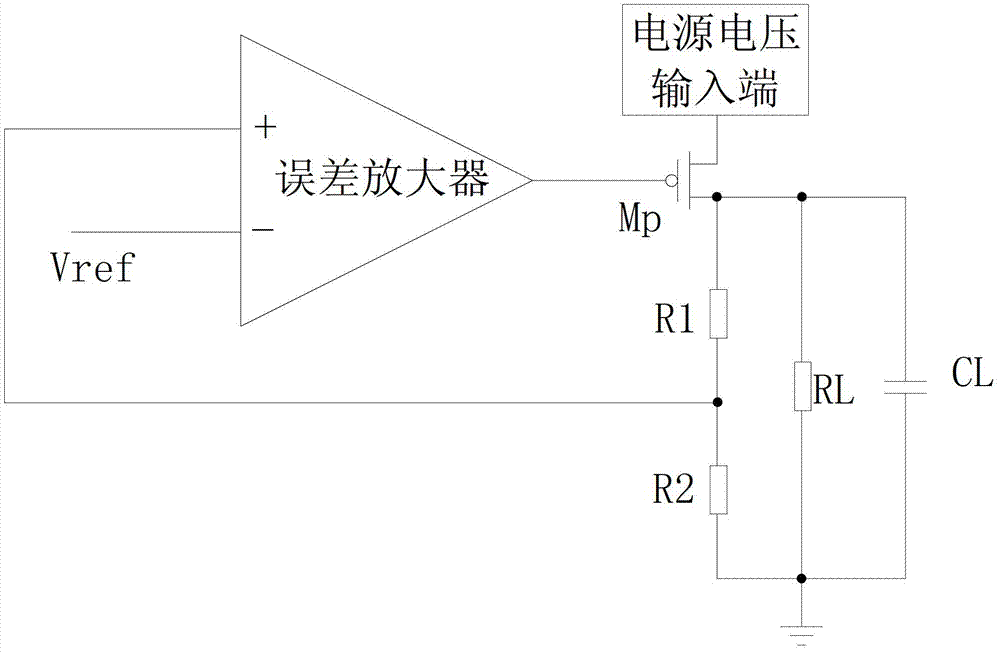

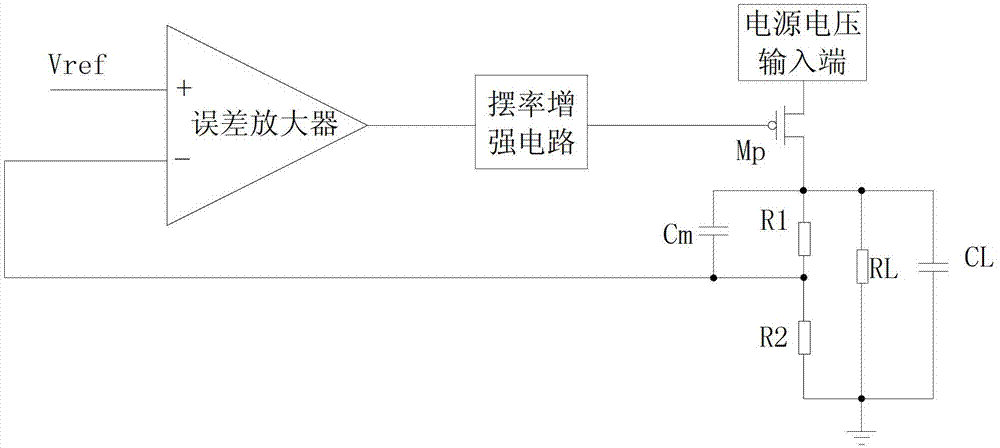

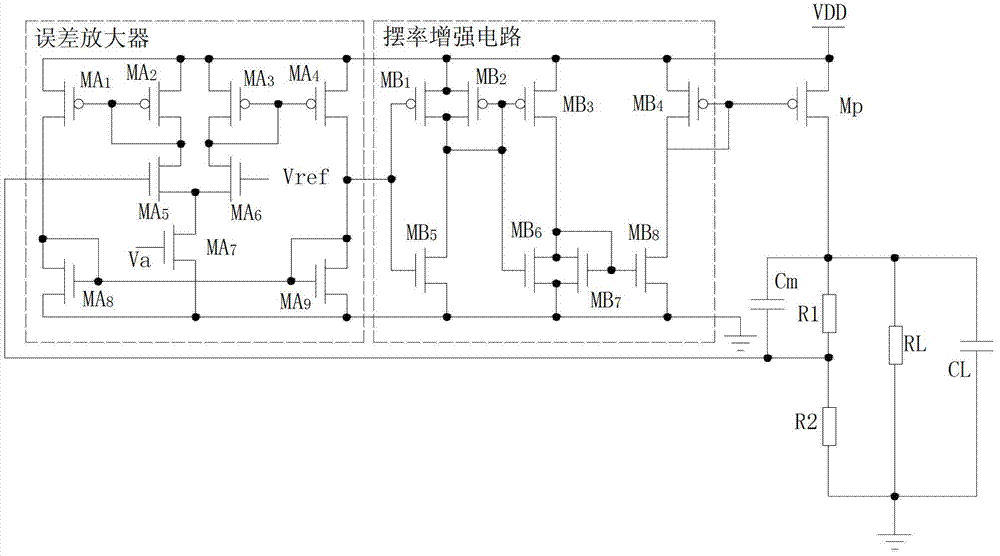

High-PSR (high power supply rejection) low-dropout regulator with slew rate enhancement circuit integrated thereto

ActiveCN103399607AIncrease slew rateImprove transient responseElectric variable regulationCircuit complexityCapacitance

The invention relates to power management technologies, solves the problem that generally voltage spike in output voltage is overcome for the existing low-dropout regulator at the costs of increased circuit complexity, decreased load capacity, increased output voltage noise and the like, and provides a High-PSR (high power supply rejection) low-dropout regulator with a slew rate enhancement circuit integrated thereto. According to the scheme, the regulator compared to the existing LDO regulators has the advantages that the slew rate enhancement circuit and a compensation capacitor are added, the positive phase input end of an error amplifier is connected with a reference voltage source, the negative phase input end of the error amplifier is connected with a resistance feedback circuit, the output end of the error amplifier is connected with the input end of the slew rate enhancement circuit, the output end of the slew rate enhancement circuit is connected with a gate of a pass transistor, one end of the compensation capacitor is connected with the negative phase input end of the error amplifier, and the other end of the compensation capacitor is connected with the output end of the error amplifier. The high-PSR low-dropout regulator has the advantages that transient response is enhanced and the scheme is applied to low-dropout regulators.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Method and system of characterizing a device under test

InactiveUS20050194981A1Correctly voltage noiseAccurate noiseResistance/reactance/impedenceTime domainEngineering

A system and method of characterizing a device under test wherein a signal is injected into the device under test, the response to the injected signal is measured to determine the impedance of the device under test in the frequency domain, the impedance is converted to the time domain, and the voltage noise of the device under test is calculated based on the impedance of the device under test in the time domain.

Owner:COLE J BRADFORD

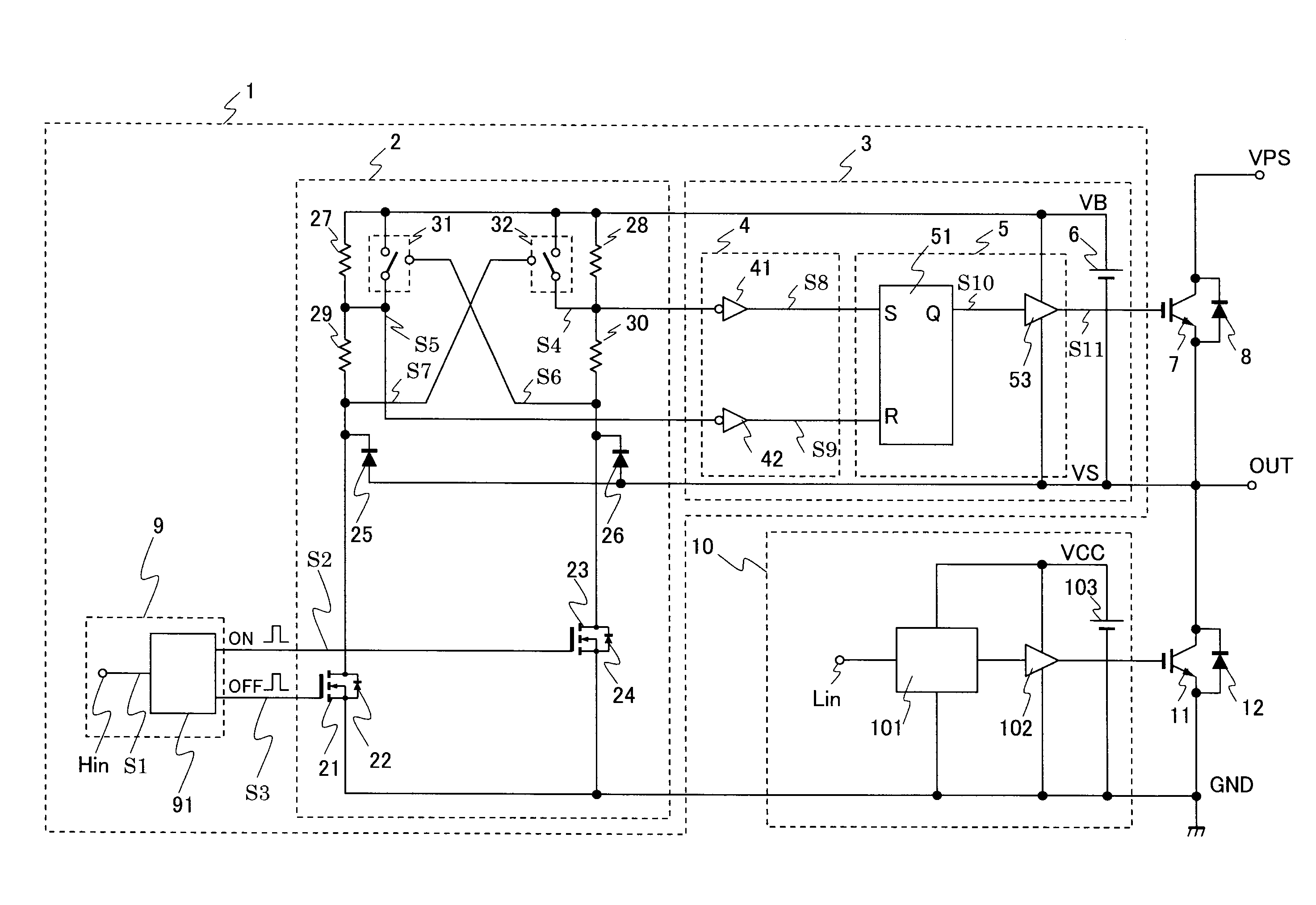

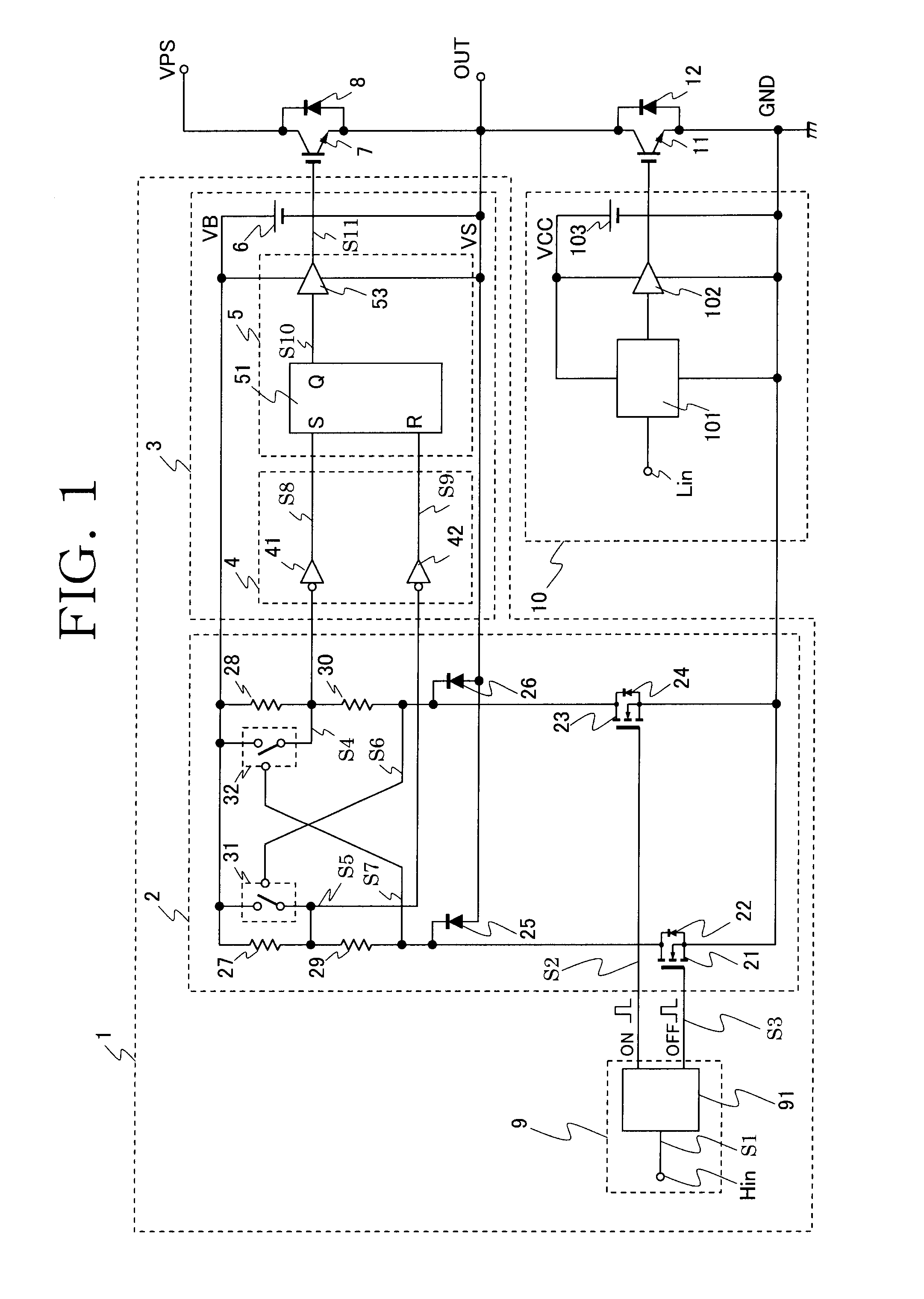

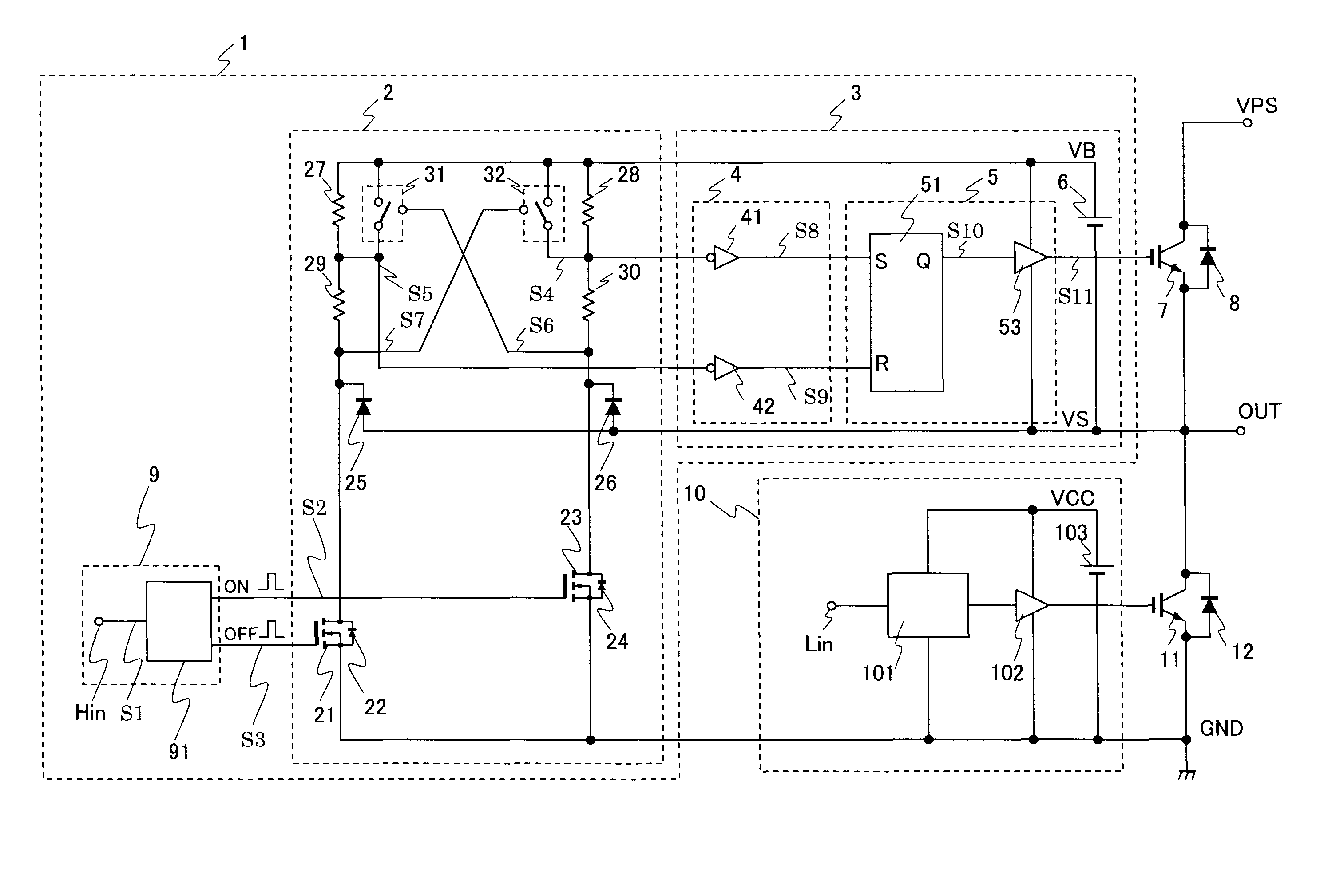

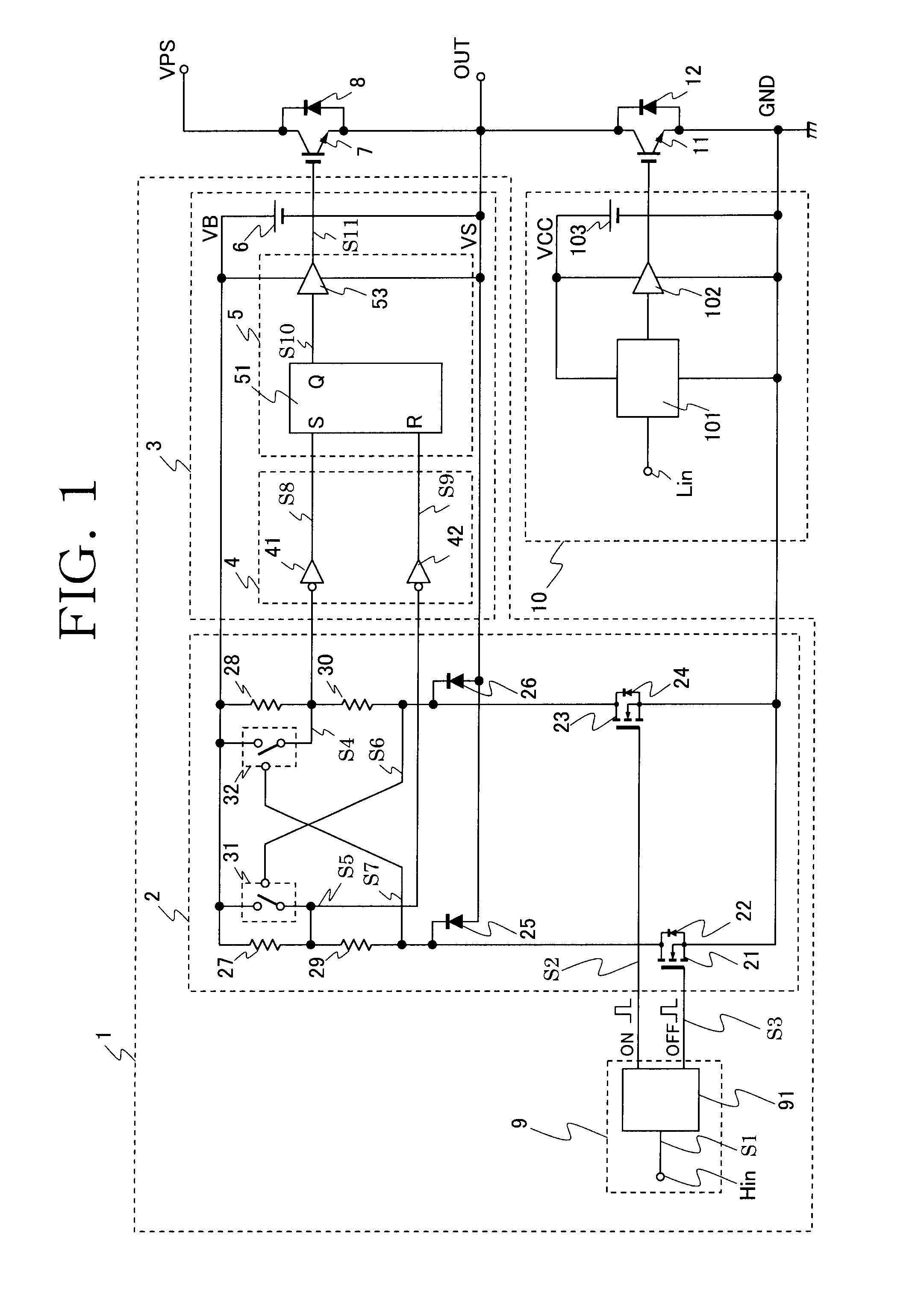

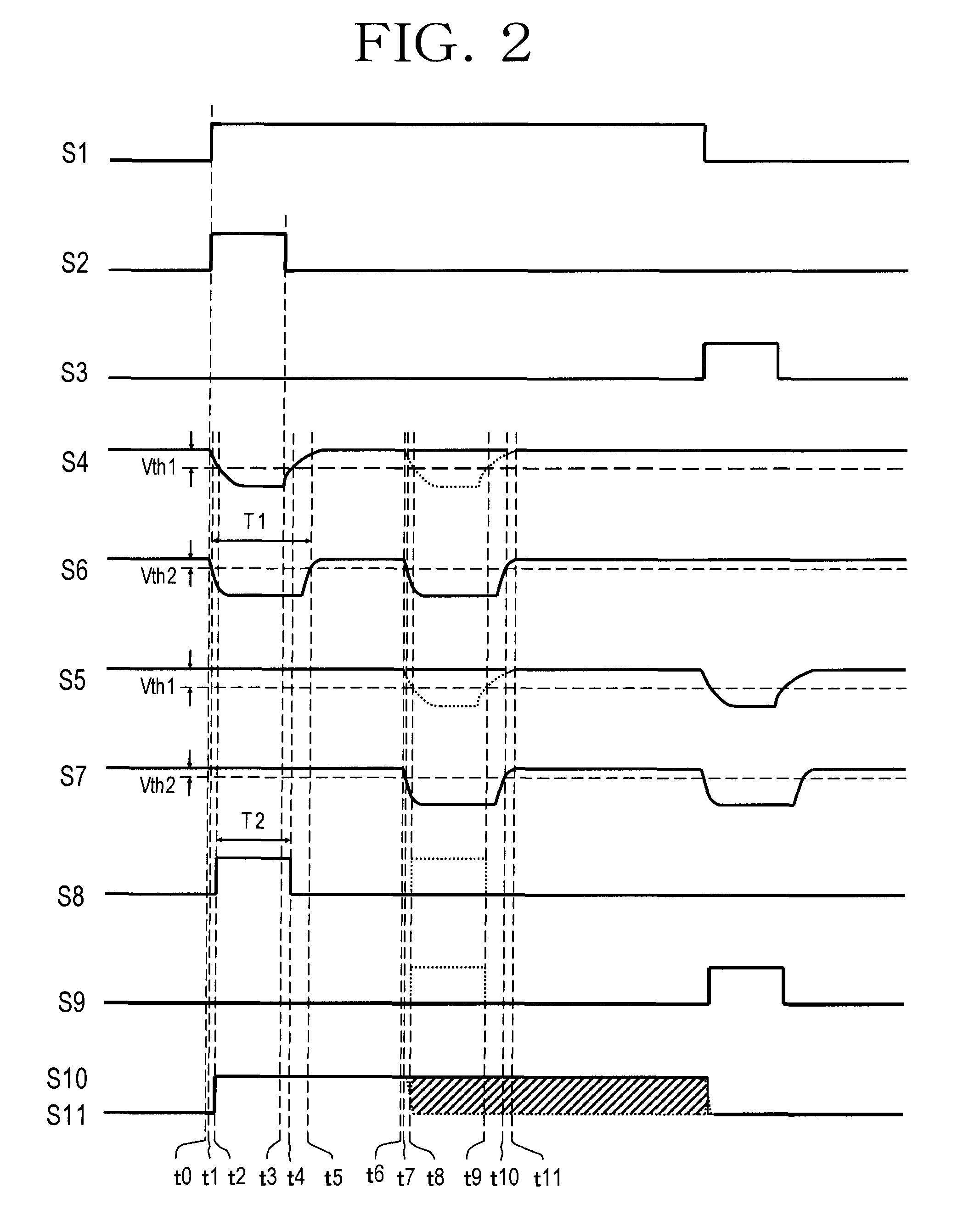

Semiconductor circuit

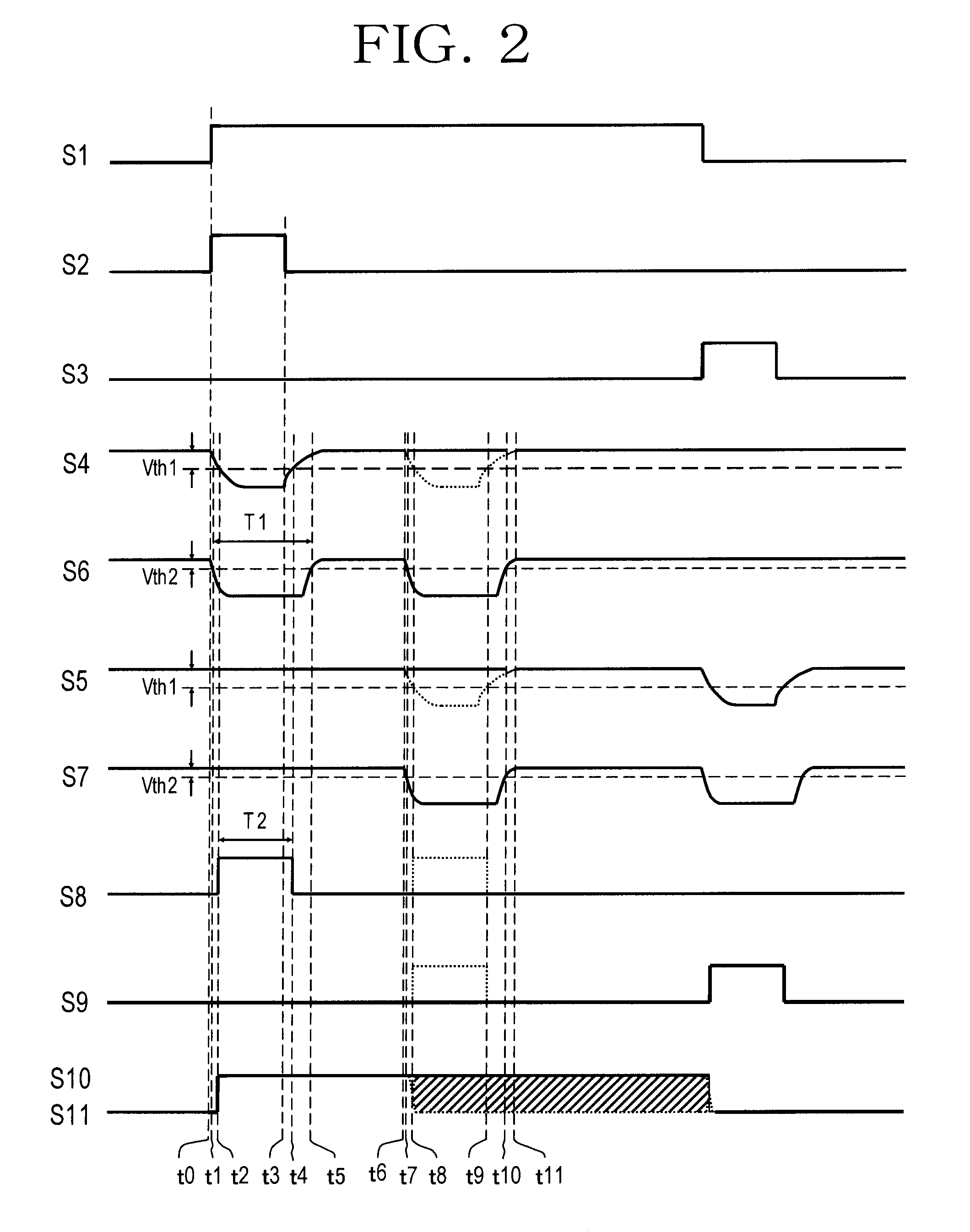

ActiveUS20110074485A1Avoid failureSimple circuit configurationPulse automatic controlElectronic switchingLoad resistanceSemiconductor

A semiconductor circuit is provided in which no error signal is generated even when the circuit is exposed to a transient voltage noise that occurs with a transition from a first state indicating a conduction of a high-potential side switching device to a second state indicating a non-conduction of the high potential side switching device, or vice versa. A high potential switching device drive circuit 1 includes short circuit devices 31 and 32 that are controlled by the second level shifted signals S6 and S7 simultaneously generated across the second load resistances 30 and 29, respectively, to thereby serving to prevent a signal from being generated at one of the output sections where the other one of the first level shifted signals S4 and S5 is to be generated, when either one of the first shifted signals S4 and S5 in level shift circuit ON and OFF sections is generated across first load resistance 28 or 27 in a level shift circuit 2.

Owner:MITSUBISHI ELECTRIC CORP

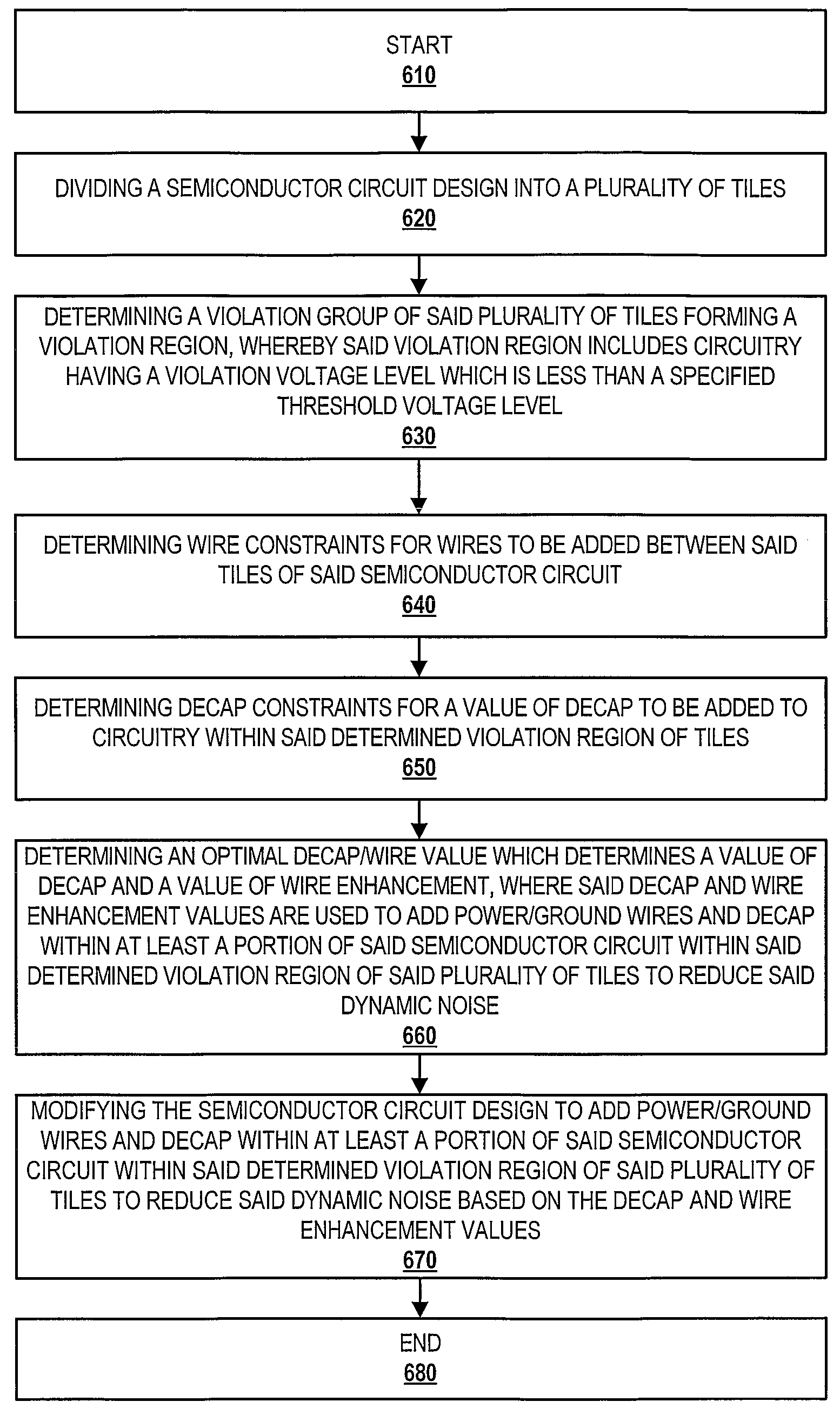

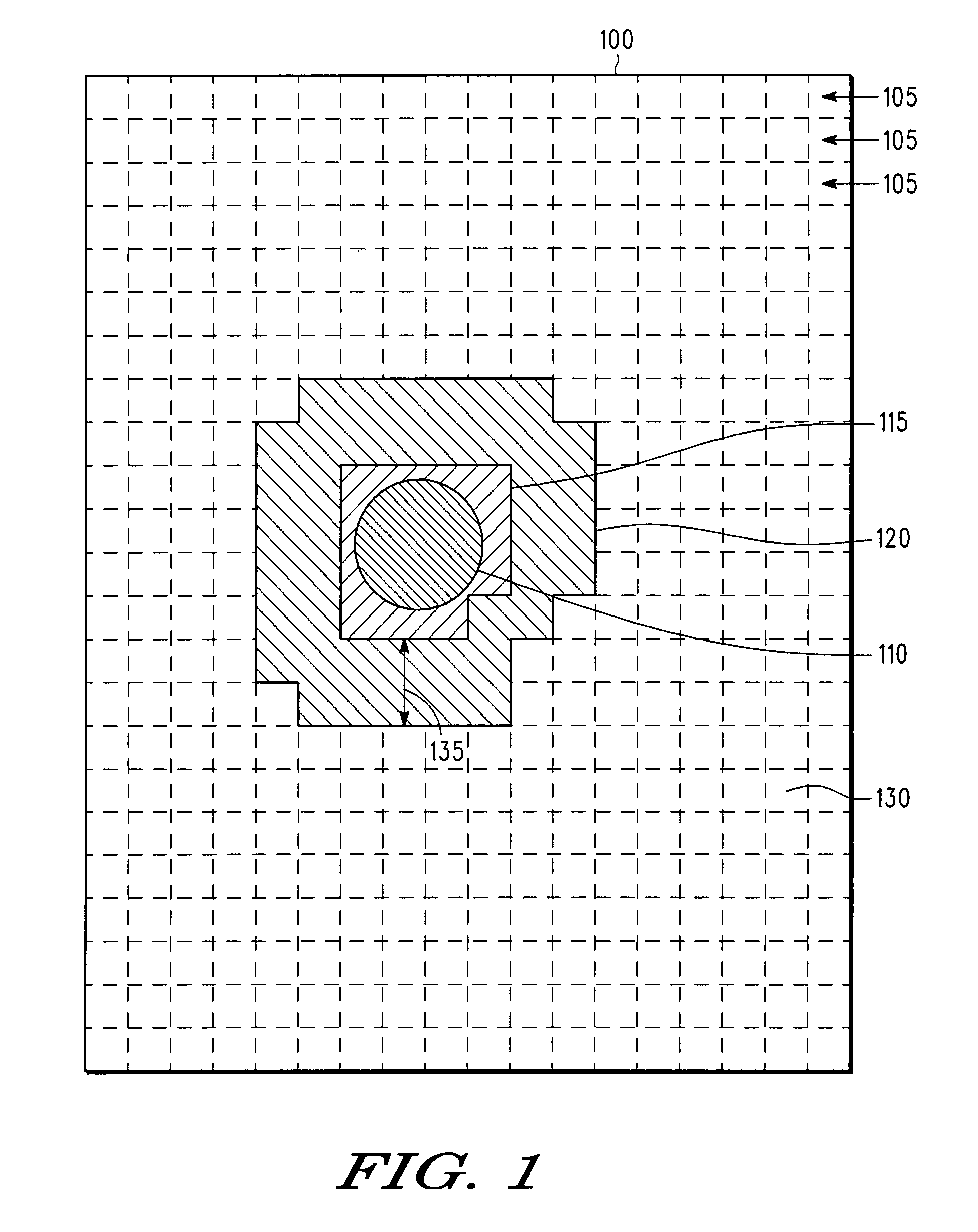

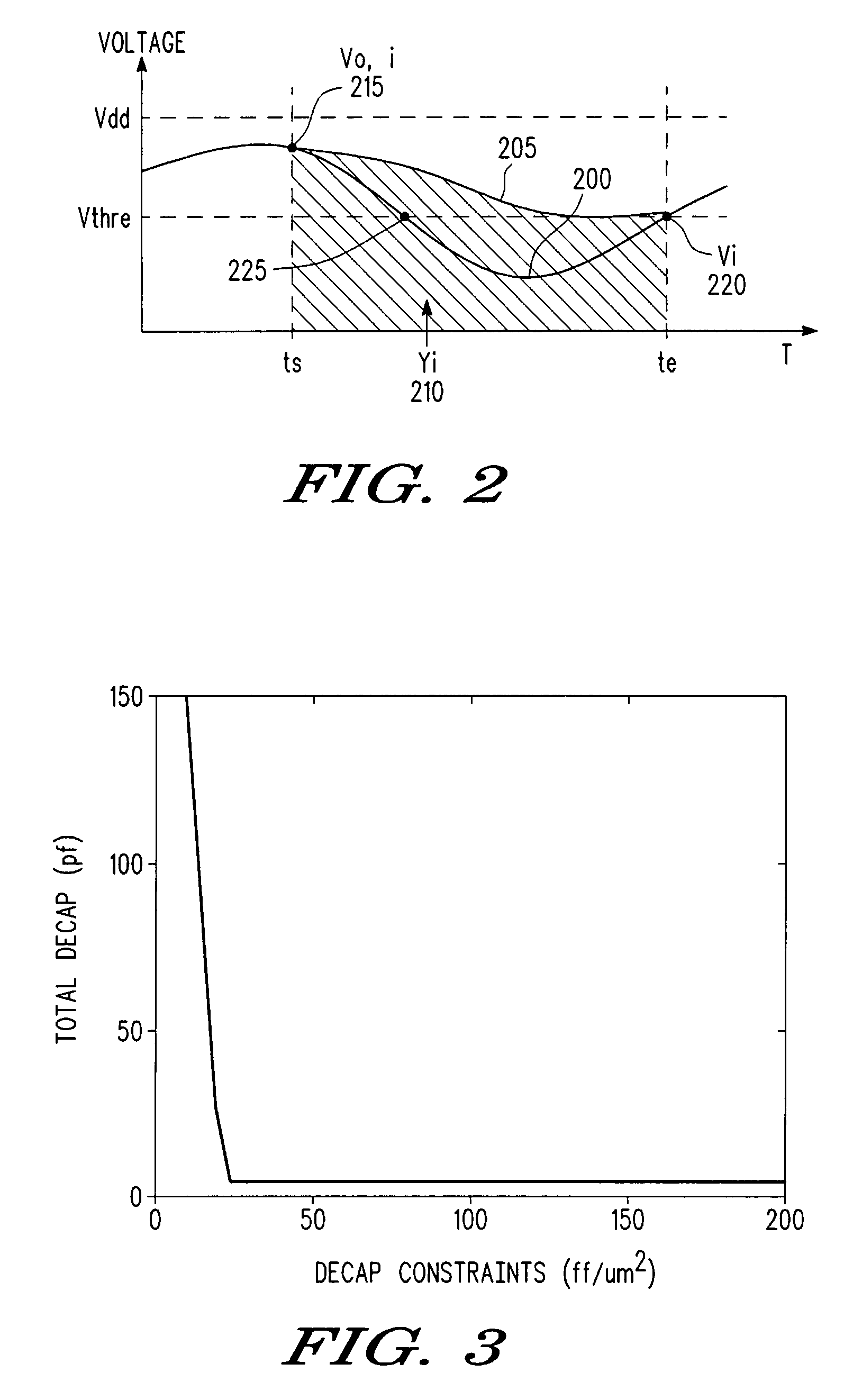

On-chip decoupling capacitance and power/ground network wire co-optimization to reduce dynamic noise

InactiveUS7698677B2Computer aided designSpecial data processing applicationsCapacitanceDynamic noise

A semiconductor power network (100) decoupling capacitance (decap) budgeting problem is co-optimized with a wiring enhancement problem, wherein the solution is formulated to minimize the total decap to be added or wiring changes (addition of wires (420)) to be made to the network (100). Voltage constraints, available white space and other constraints determine the amount of decap to be added. Wire enhancements and / or added decap can be distributed throughout a violation region (120) of the semiconductor circuit (100) design to reduce dynamic supply voltage noise so that dynamic network voltages are at all times maintained greater than a user-specified threshold voltage level (220).

Owner:NXP USA INC

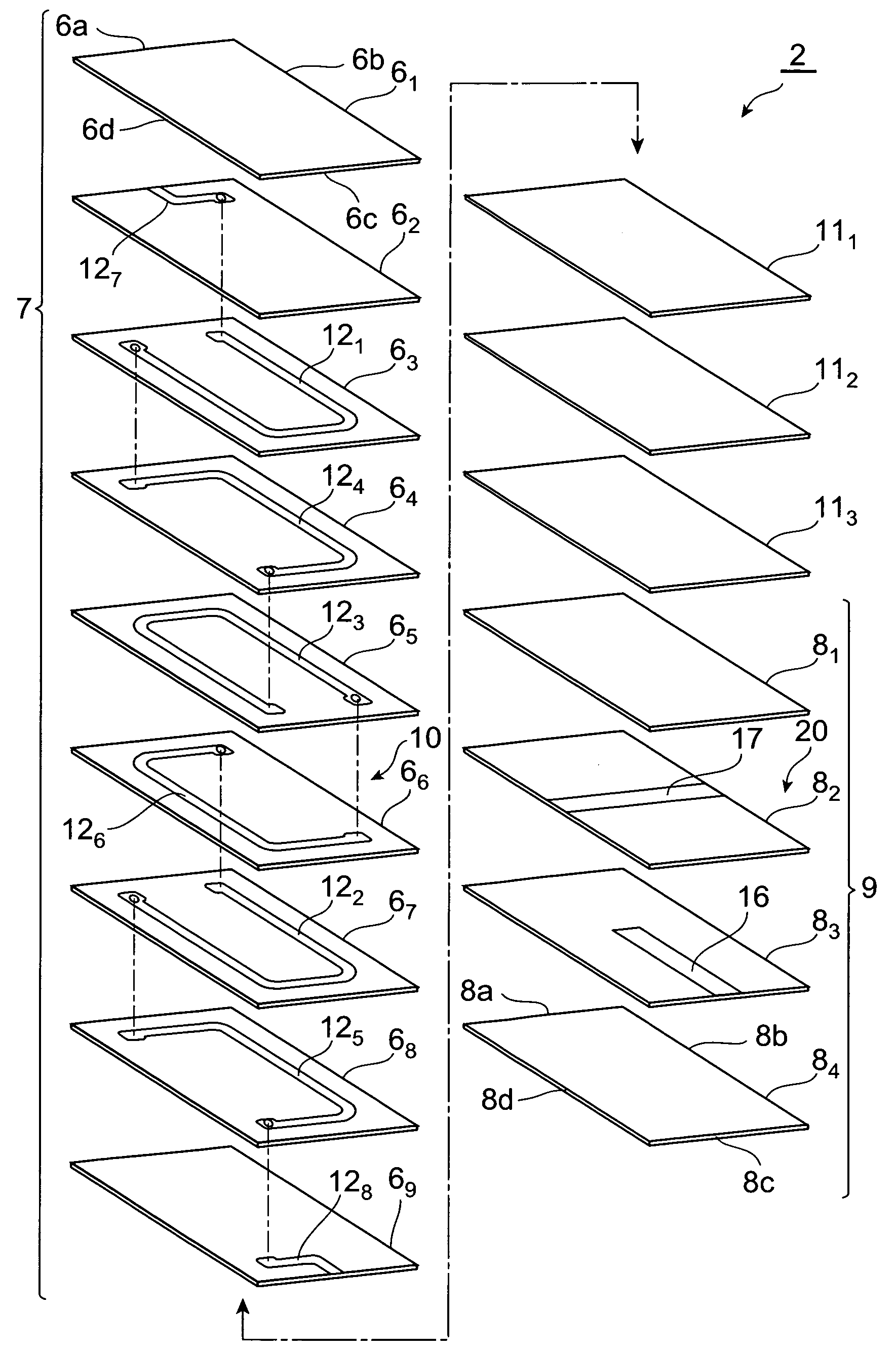

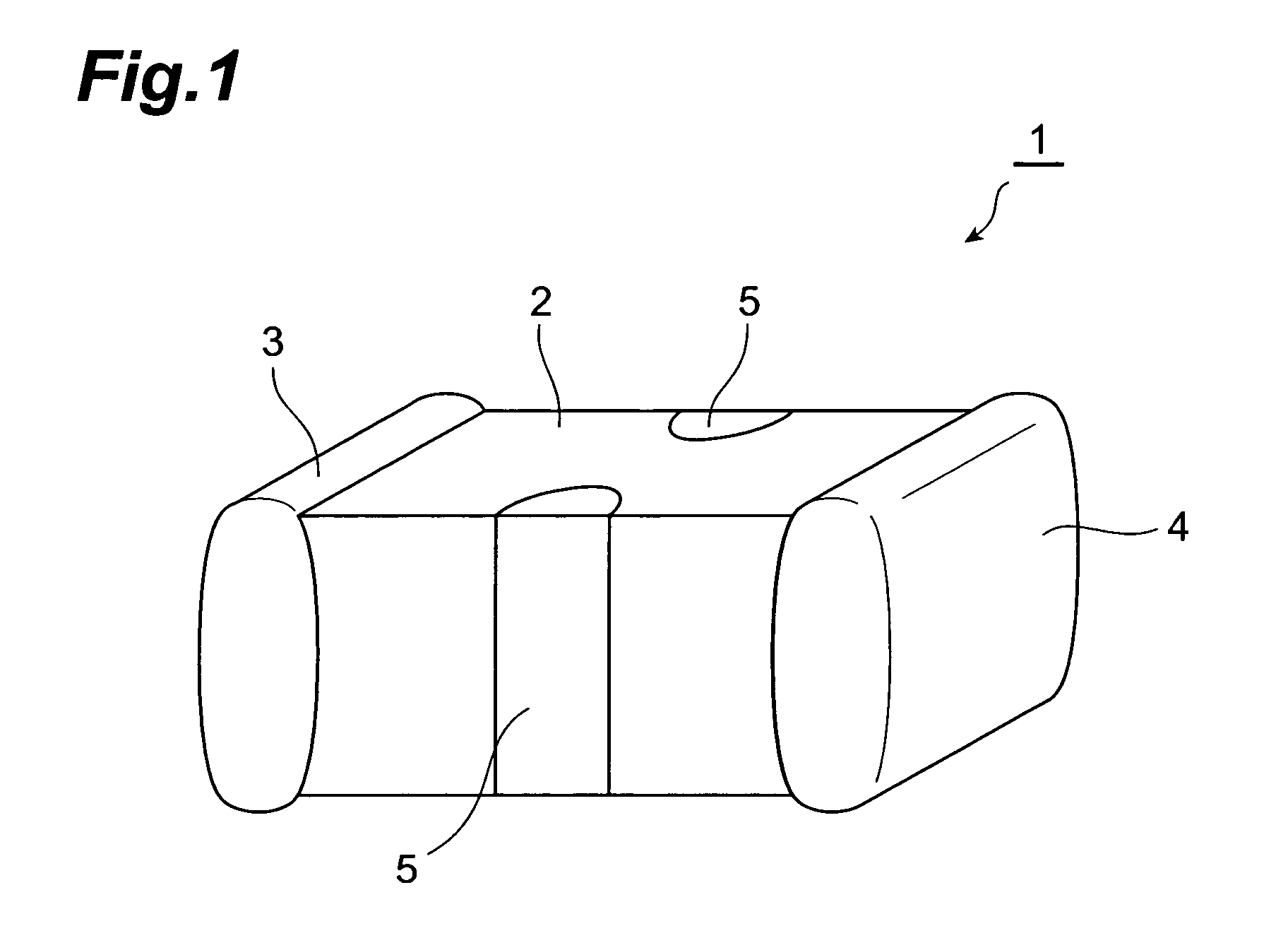

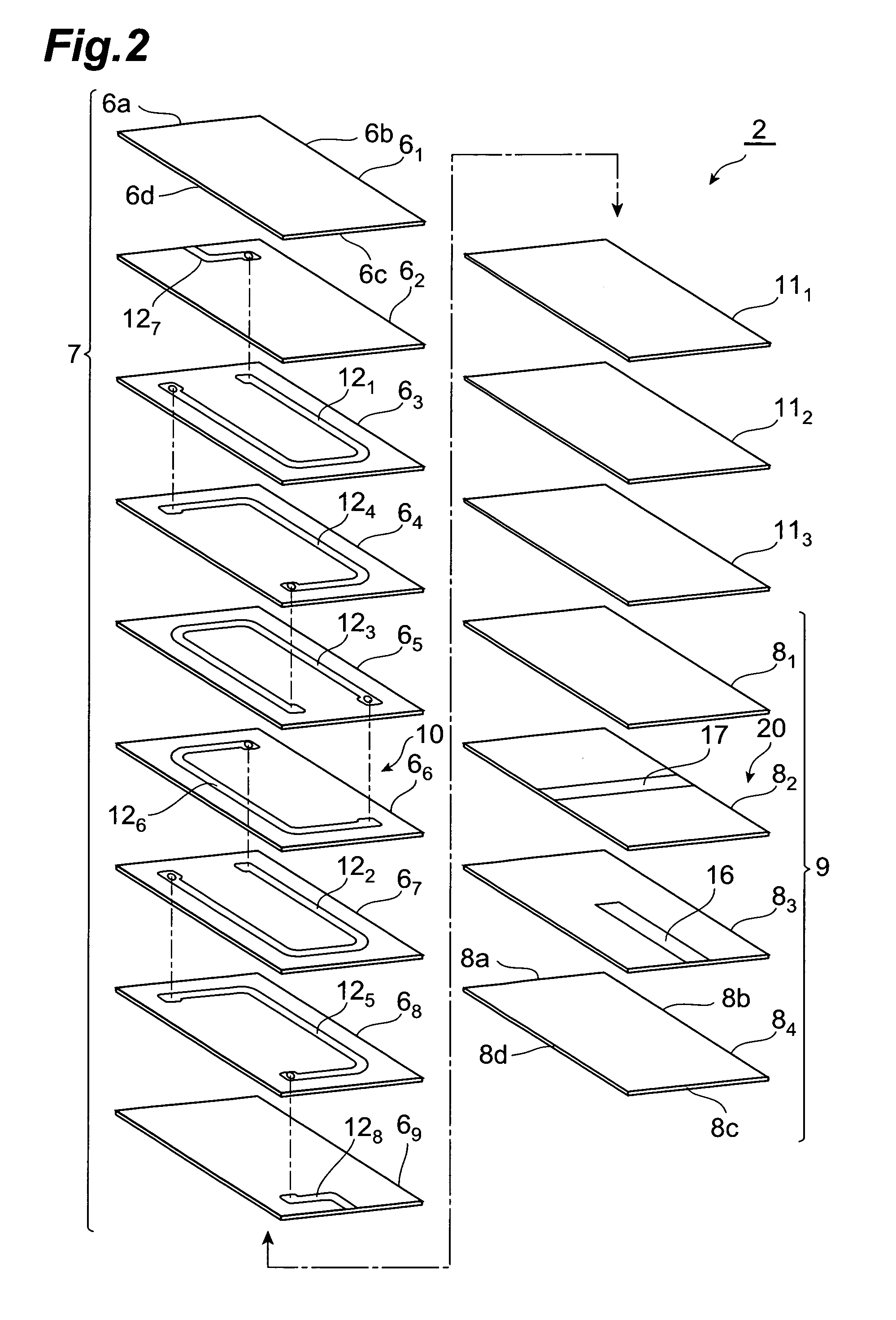

Multilayer filter

ActiveUS7277270B2Avoid flowIncrease resistanceMultiple-port networksFixed capacitor dielectricInductorHigh pressure

An objective is to provide a multilayer filter capable of preventing an electric current rapidly flowing by virtue of varistor effect, from passing as noise, upon application of noise of a high voltage over a varistor voltage to its input. A multilayer filter has an inductor part 10 and a varistor part 20 in a laminate 2, and the inductor part 10 has the DC resistance of 4 Ω-100 Ω. This prevents an electric current rapidly flowing by virtue of the varistor effect, from passing as noise, upon application of noise of a high voltage over the varistor voltage to the input.

Owner:TDK CORPARATION

Semiconductor circuit

ActiveUS8134400B2Simple configurationPulse automatic controlElectronic switchingLoad resistanceEngineering

A semiconductor circuit is provided in which no error signal is generated even when the circuit is exposed to a transient voltage noise that occurs with a transition from a first state indicating a conduction of a high-potential side switching device to a second state indicating a non-conduction of the high potential side switching device, or vice versa. A high potential switching device drive circuit 1 includes short circuit devices 31 and 32 that are controlled by the second level shifted signals S6 and S7 simultaneously generated across the second load resistances 30 and 29, respectively, to thereby serving to prevent a signal from being generated at one of the output sections where the other one of the first level shifted signals S4 and S5 is to be generated, when either one of the first shifted signals S4 and S5 in level shift circuit ON and OFF sections is generated across first load resistance 28 or 27 in a level shift circuit 2.

Owner:MITSUBISHI ELECTRIC CORP

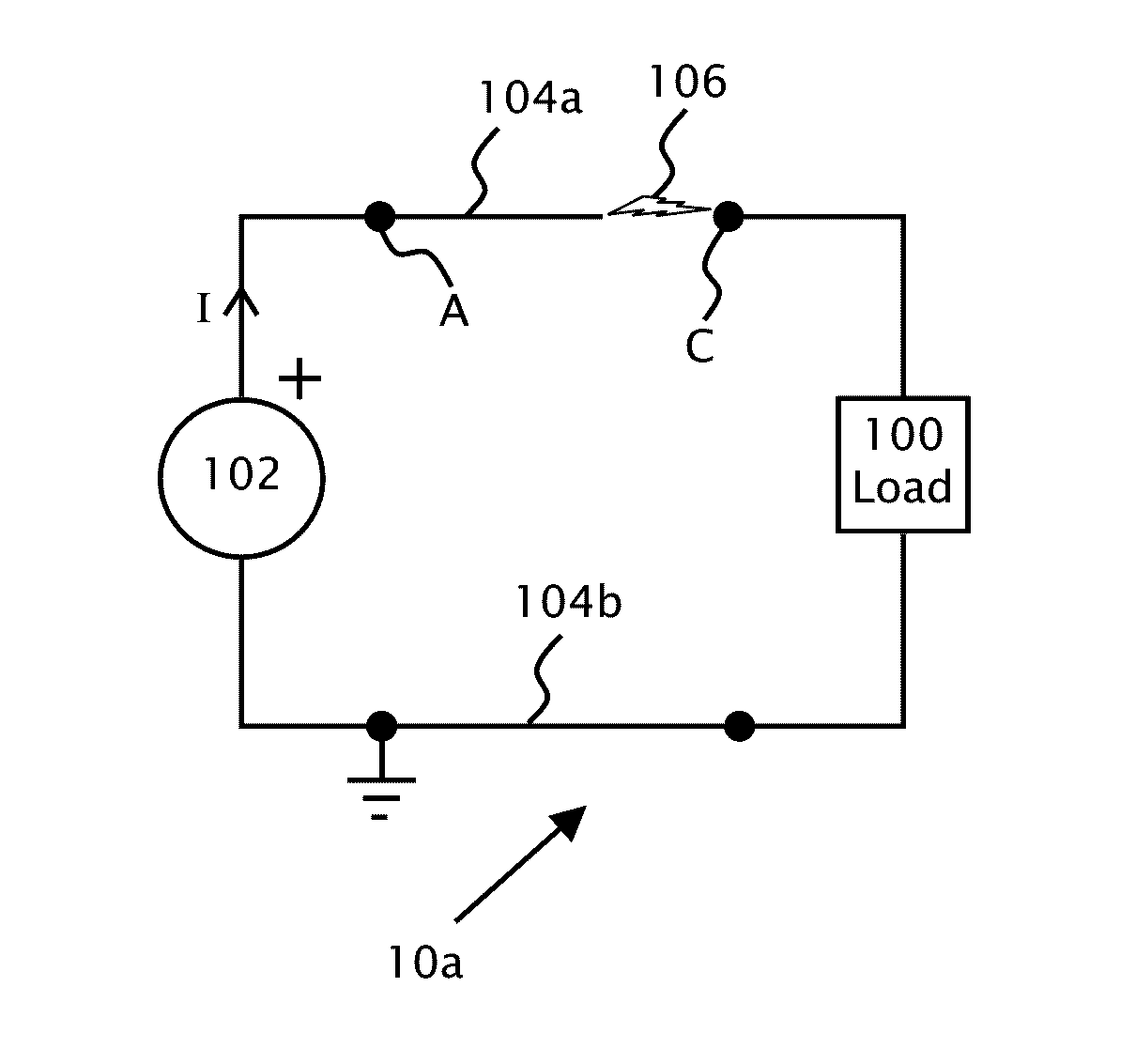

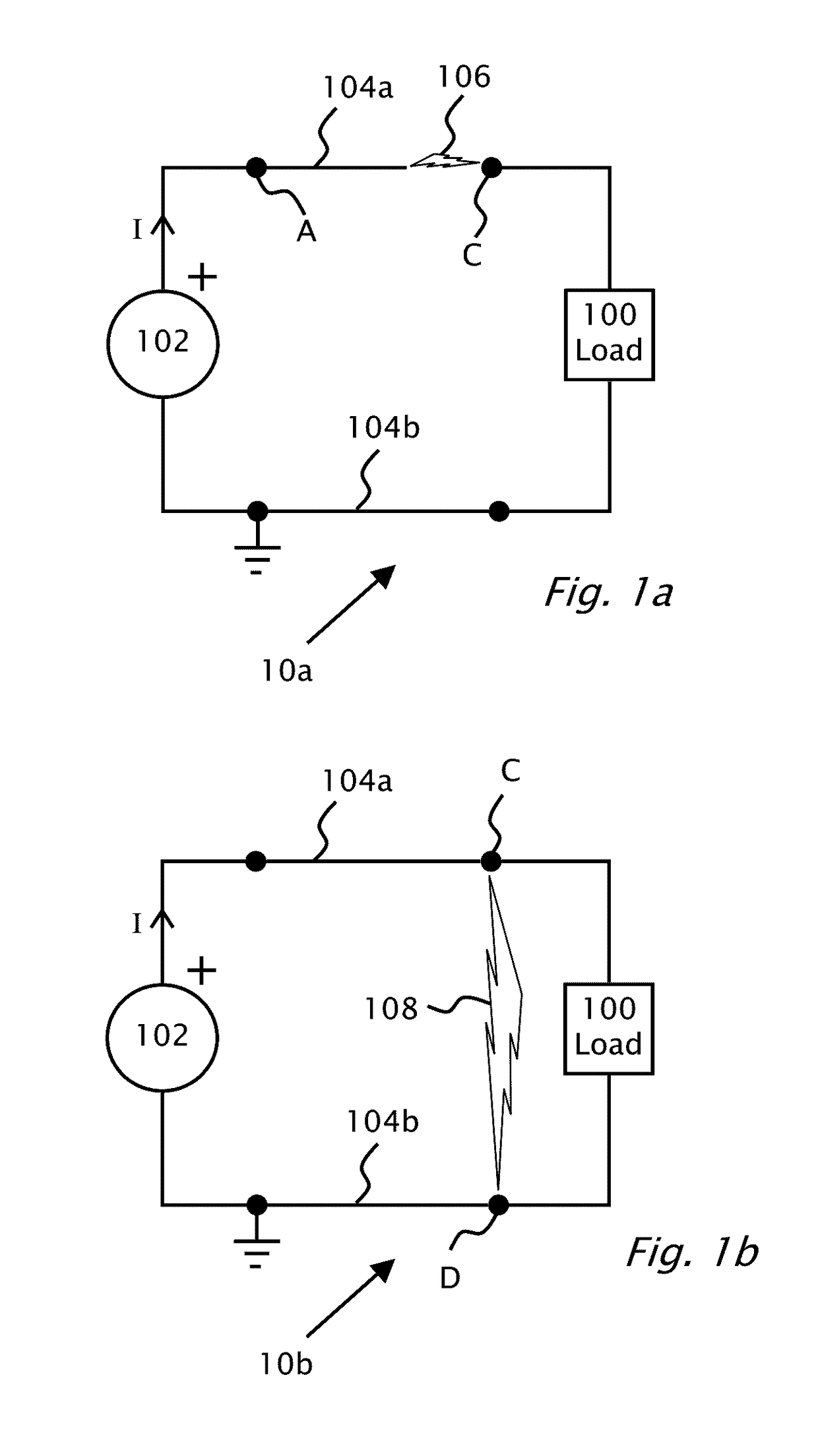

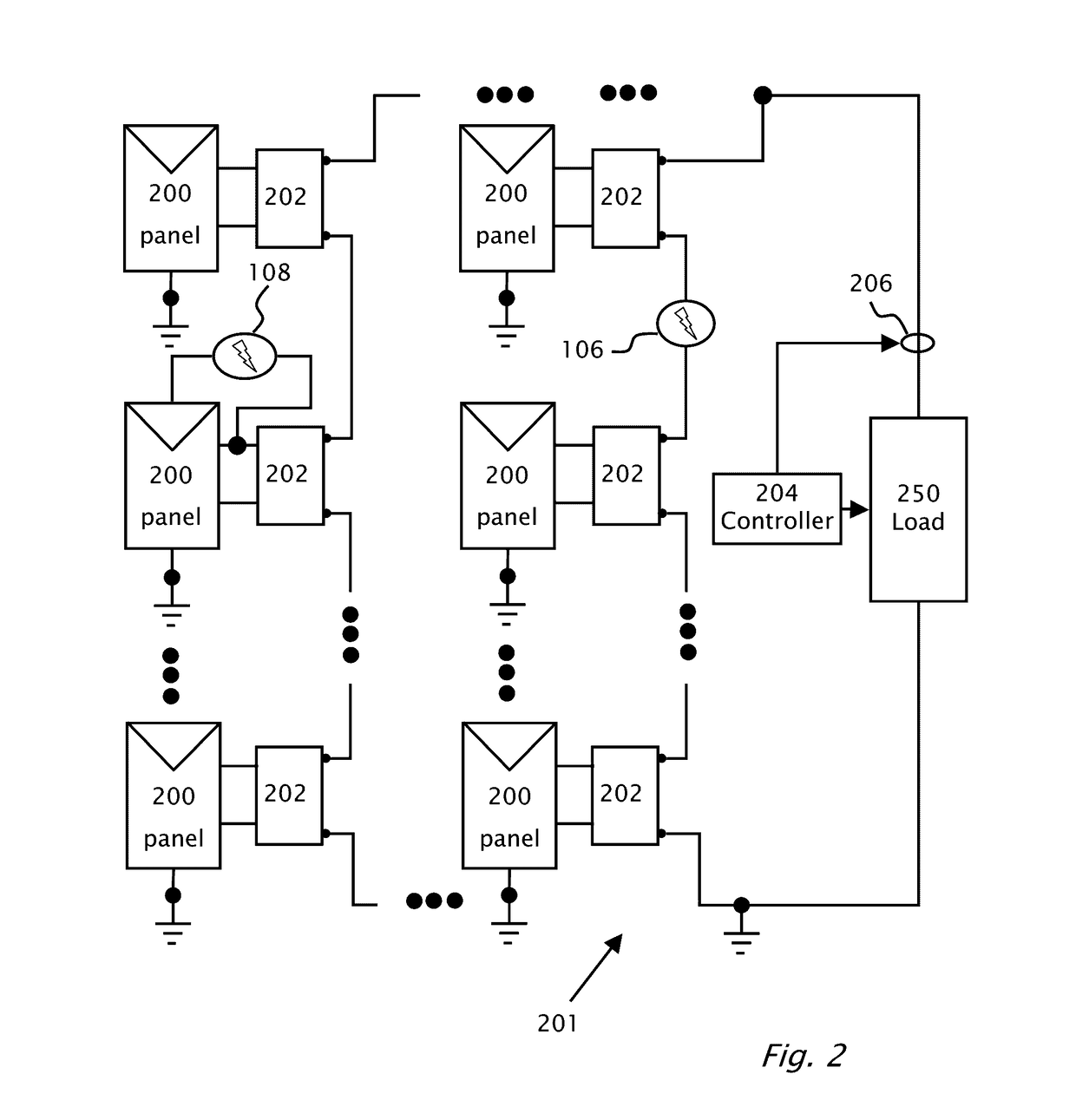

Arc Detection and Prevention in a Power Generation System

ActiveUS20170170782A1Improve abilitiesService lifePhotovoltaic monitoringEmergency protective arrangement detailsVoltage loopEngineering

Methods for arc detection in a system including one or more photovoltaic generators, one or more photovoltaic power devices and a system power device and / or a load connectible to the photovoltaic generators and / or the photovoltaic power devices. The methods measure voltage, voltage noise and / or power delivered to the load or system power device. The methods may compare one or more measurements, an aggregation of measurements and / or values estimated from the measurements to one or more thresholds, and upon a comparison indicating a potential arcing condition, an alarm condition may be set. Embodiments include an arrangement of photovoltaic generators and photovoltaic power devices for reduced-impedance voltage loops which may enhance arc-detection capabilities.

Owner:SOLAREDGE TECH LTD

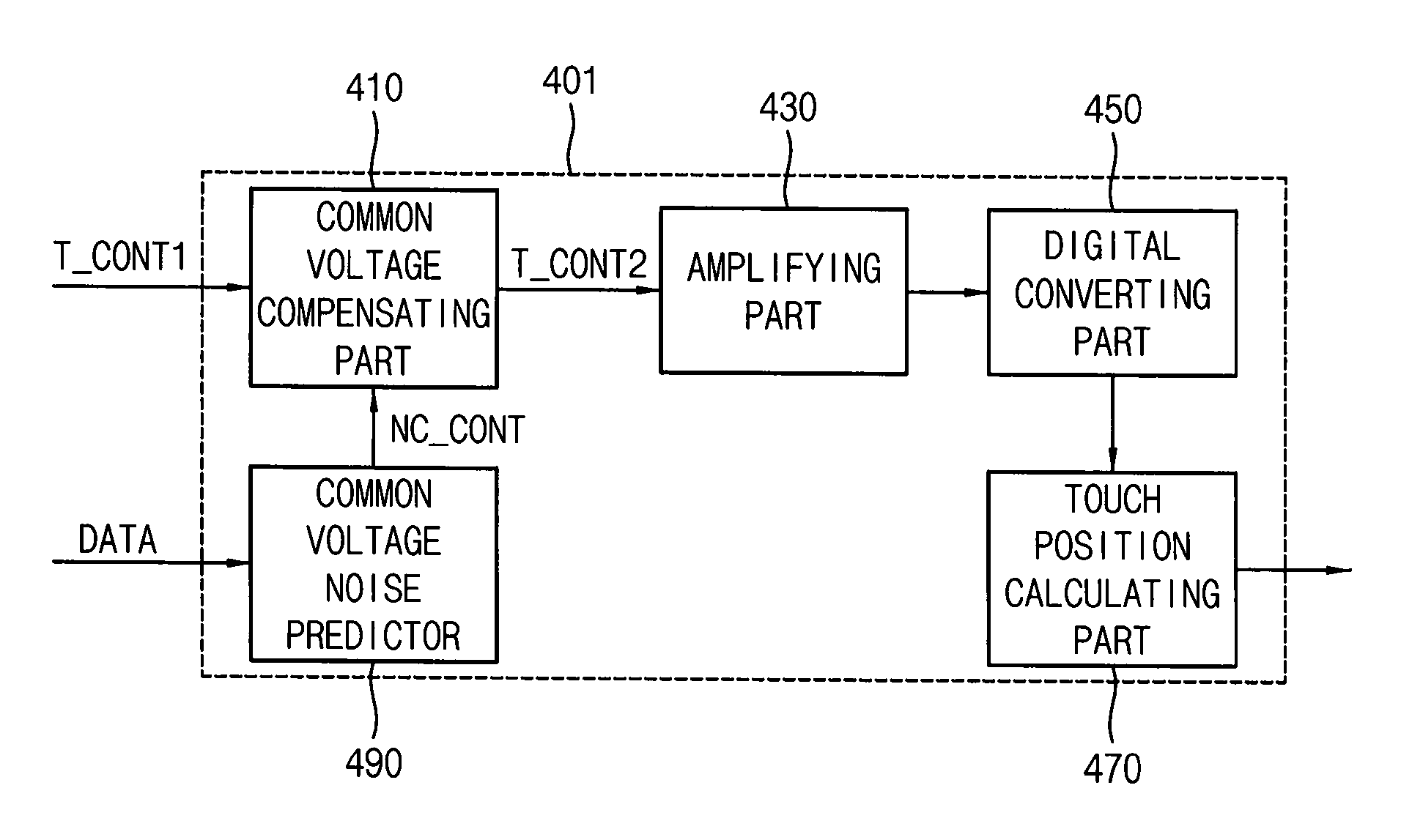

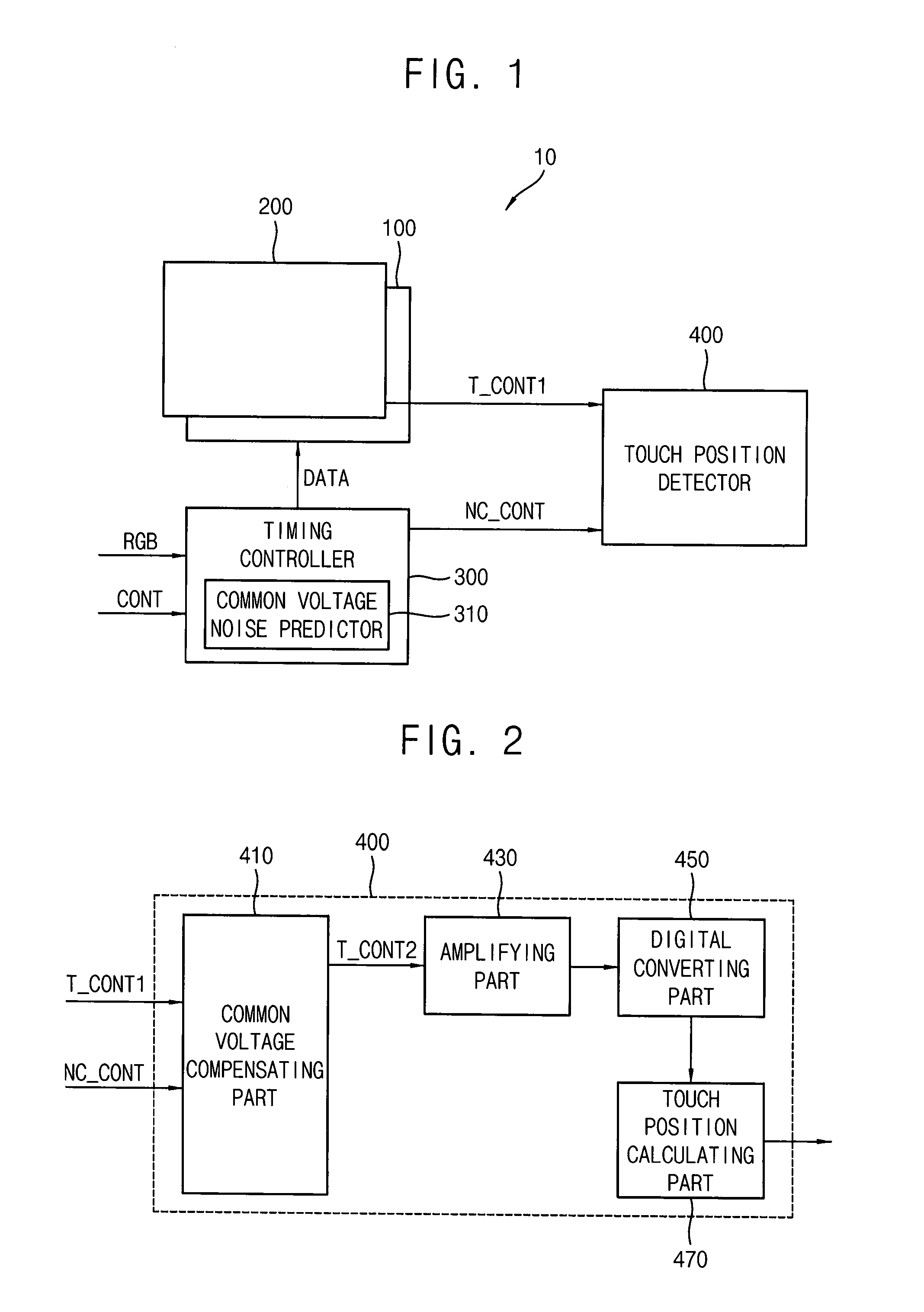

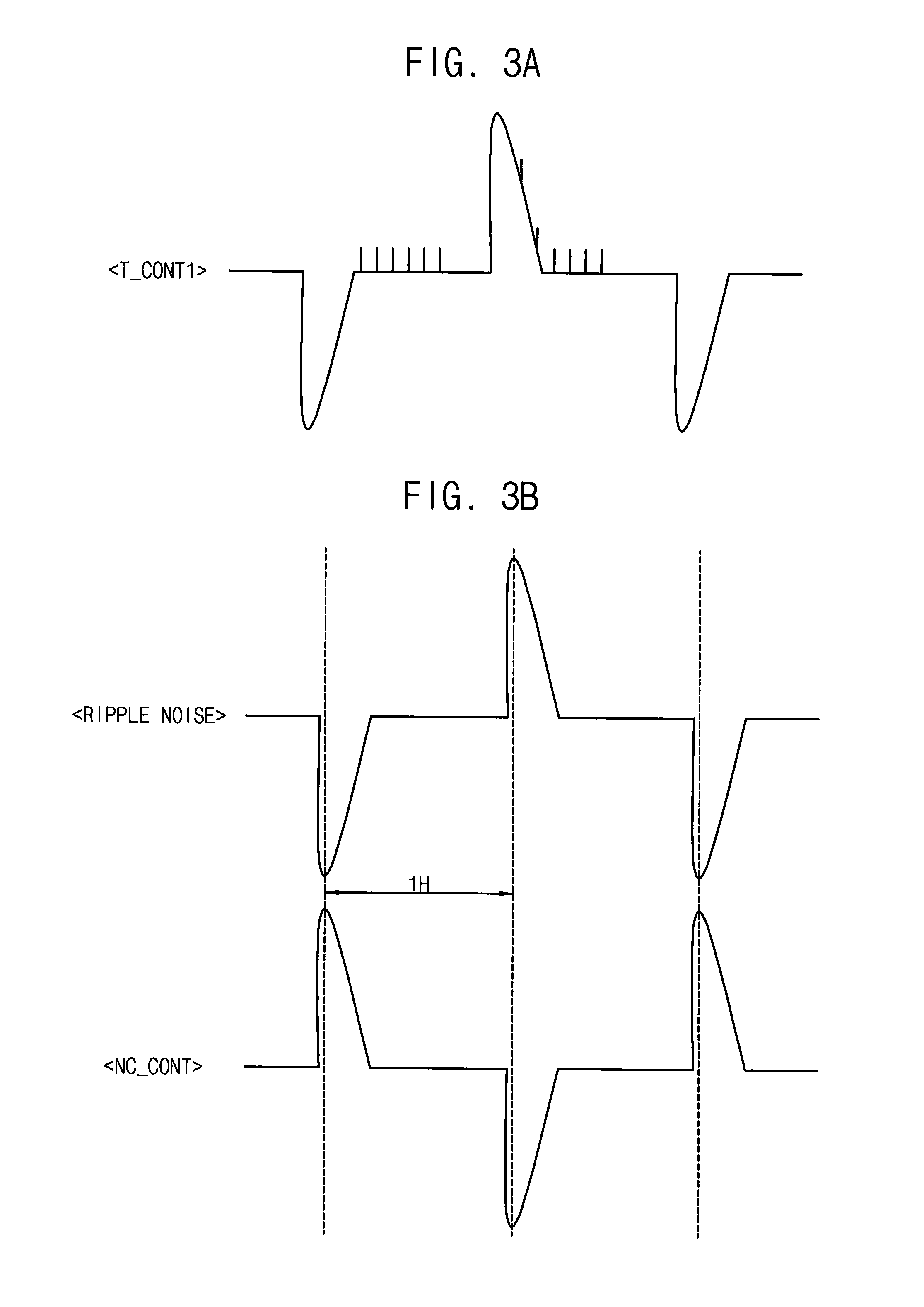

Display apparatus and method for driving the same

ActiveUS20150220177A1Improve touch recognition rateReduce ripple noiseNon-linear opticsInput/output processes for data processingData signalComputer science

A display apparatus including a display panel, a touch panel, a data driver, a common voltage noise predictor and a touch position detector. The display panel includes a plurality of data lines and a plurality of pixels. The pixels are electrically connected to the data lines, respectively. The touch panel is configured to output a first touch signal based on a touch event. The data driver is configured to output a data voltage to the data line based on a data signal. The common voltage noise predictor is configured to output a common voltage noise compensating signal based on the data signal. The touch position detector is configured to detect a touch position based on the common voltage noise compensating signal and the first touch signal.

Owner:SAMSUNG DISPLAY CO LTD

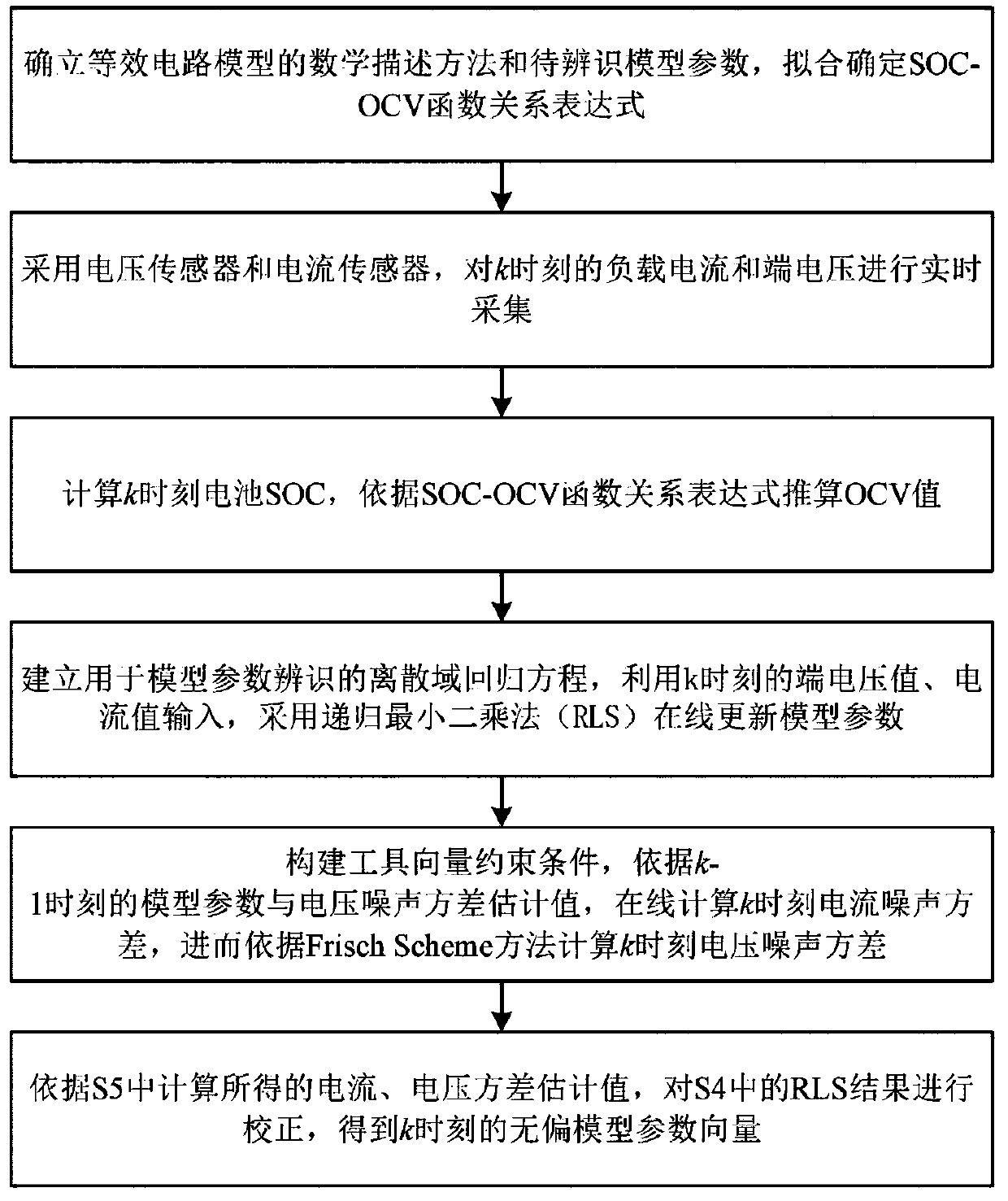

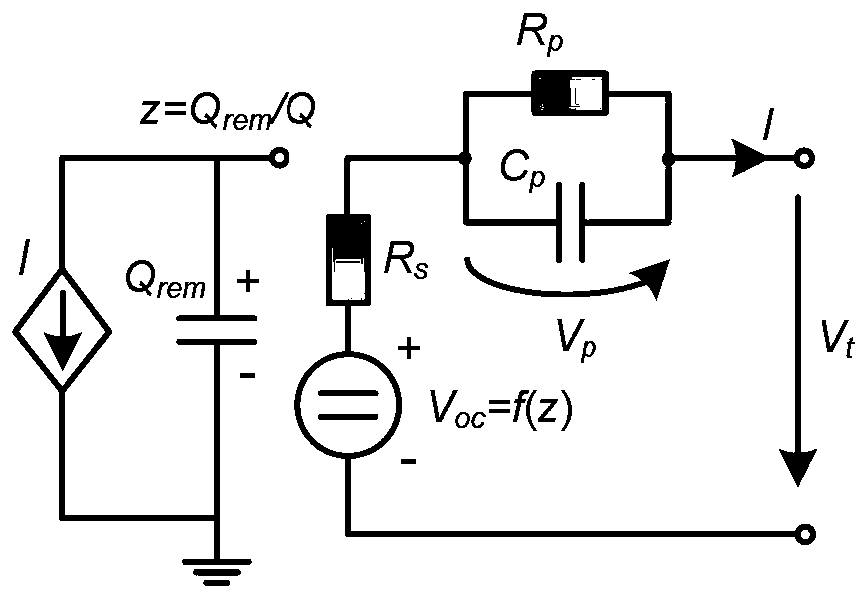

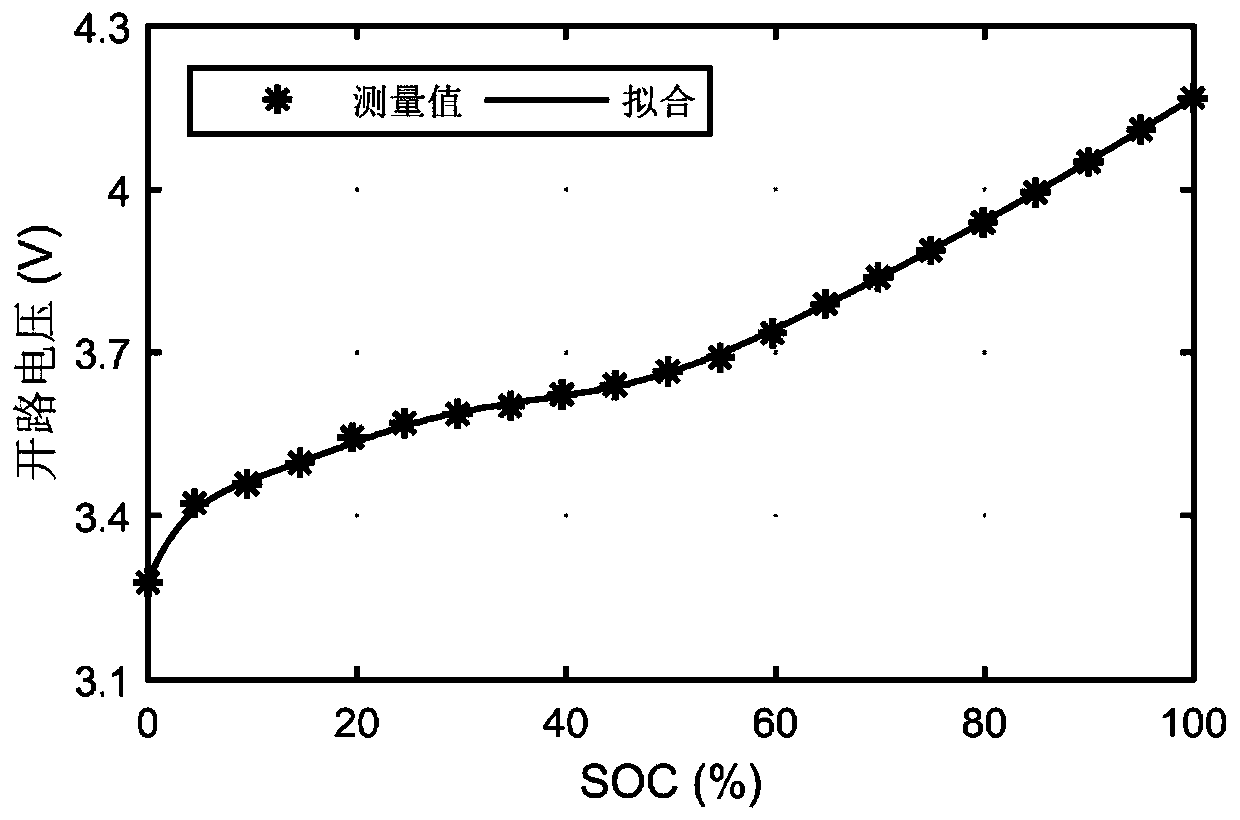

Anti-disturbance parameterization method for battery equivalent circuit model

ActiveCN111366855AReal-time acquisitionRealize identificationElectrical testingAlgorithmTerminal voltage

The invention discloses an anti-disturbance parameterization method for a battery equivalent circuit model. The method comprises the following steps: S1, establishing the equivalent circuit model of the battery, determining parameters of a model to be identified, and determining a relational expression of a state of charge (SOC) and an open-circuit voltage (OCV) through fitting; S2, carrying out real-time acquisition on the load current and the terminal voltage at the moment k; S3, calculating the SOC of the battery at the moment k, and calculating an OCV value; S4, establishing a discrete domain regression equation for model parameter identification, and updating model parameters online by adopting a recursive least square method (RLS); S5, constructing a tool vector constraint condition,calculating a current noise variance at the moment k on line, and further calculating a voltage noise variance at the moment k according to a FrischScheme method; and S6, correcting the RLS result inthe step S4 according to the estimated values of the current and voltage variances to obtain an unbiased model parameter vector at the moment k. According to the method, current and voltage measurement noise statistical characteristics can be estimated on line, so that model identification deviation in a noise interference environment is compensated, and unbiased model parameter identification isrealized.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

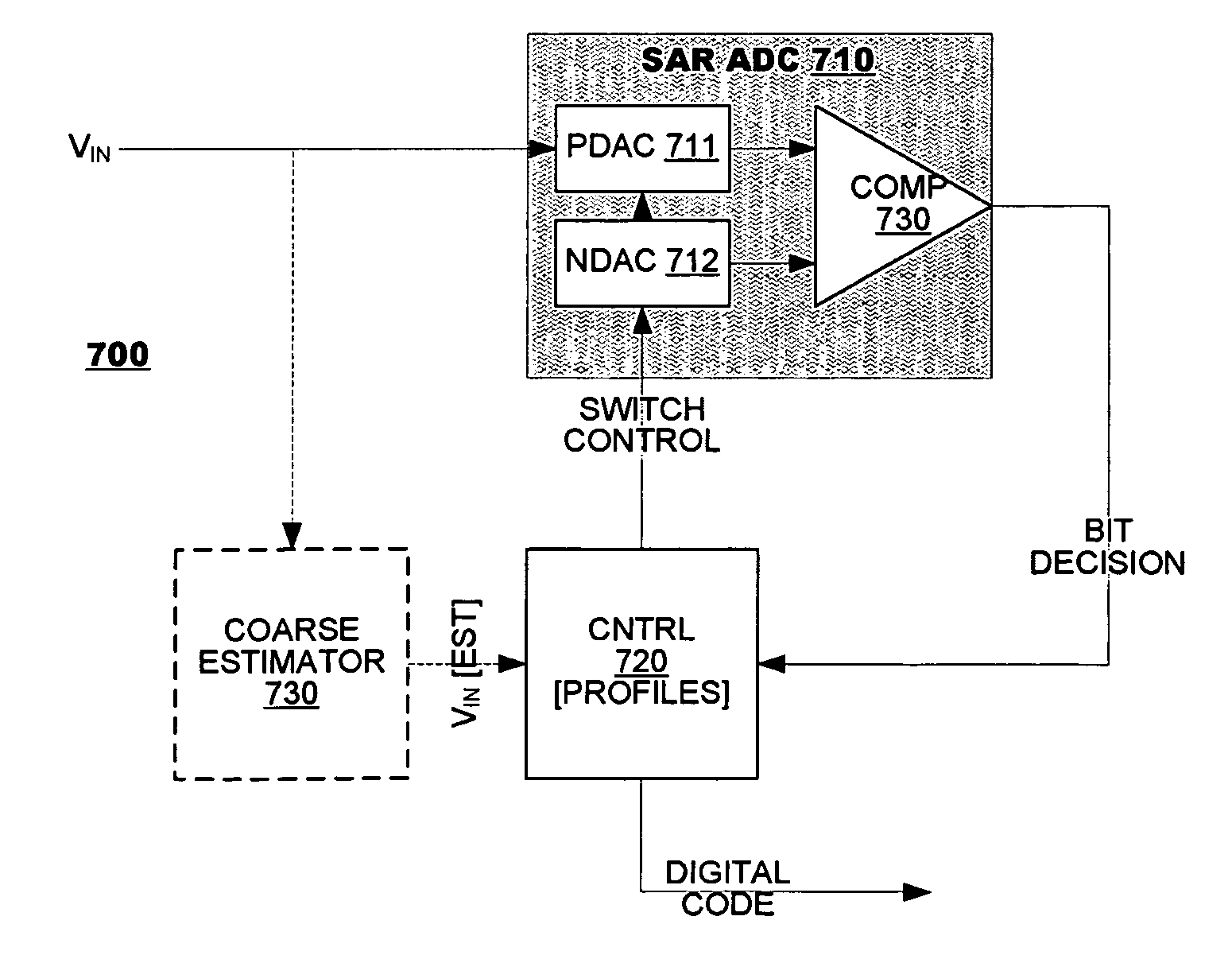

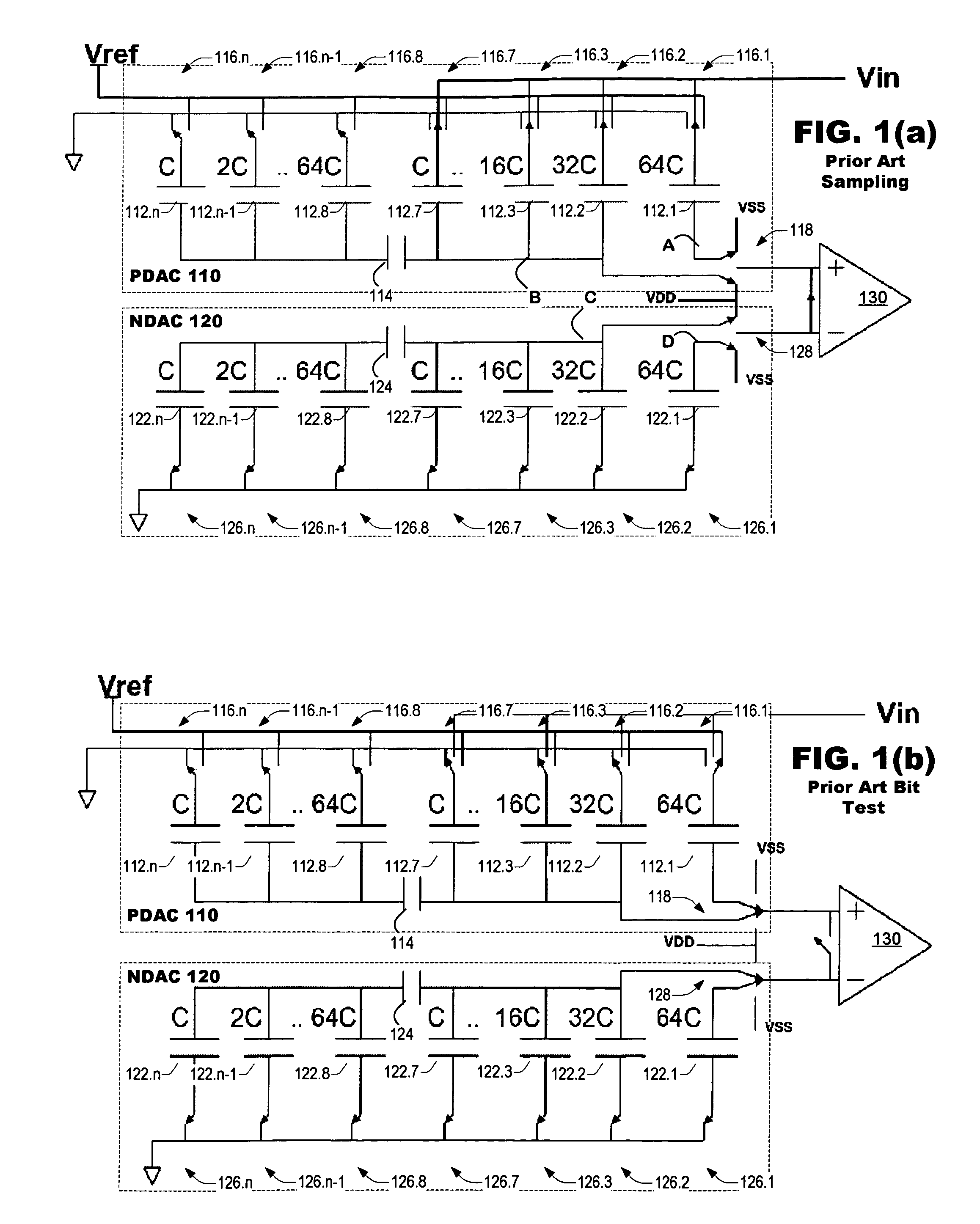

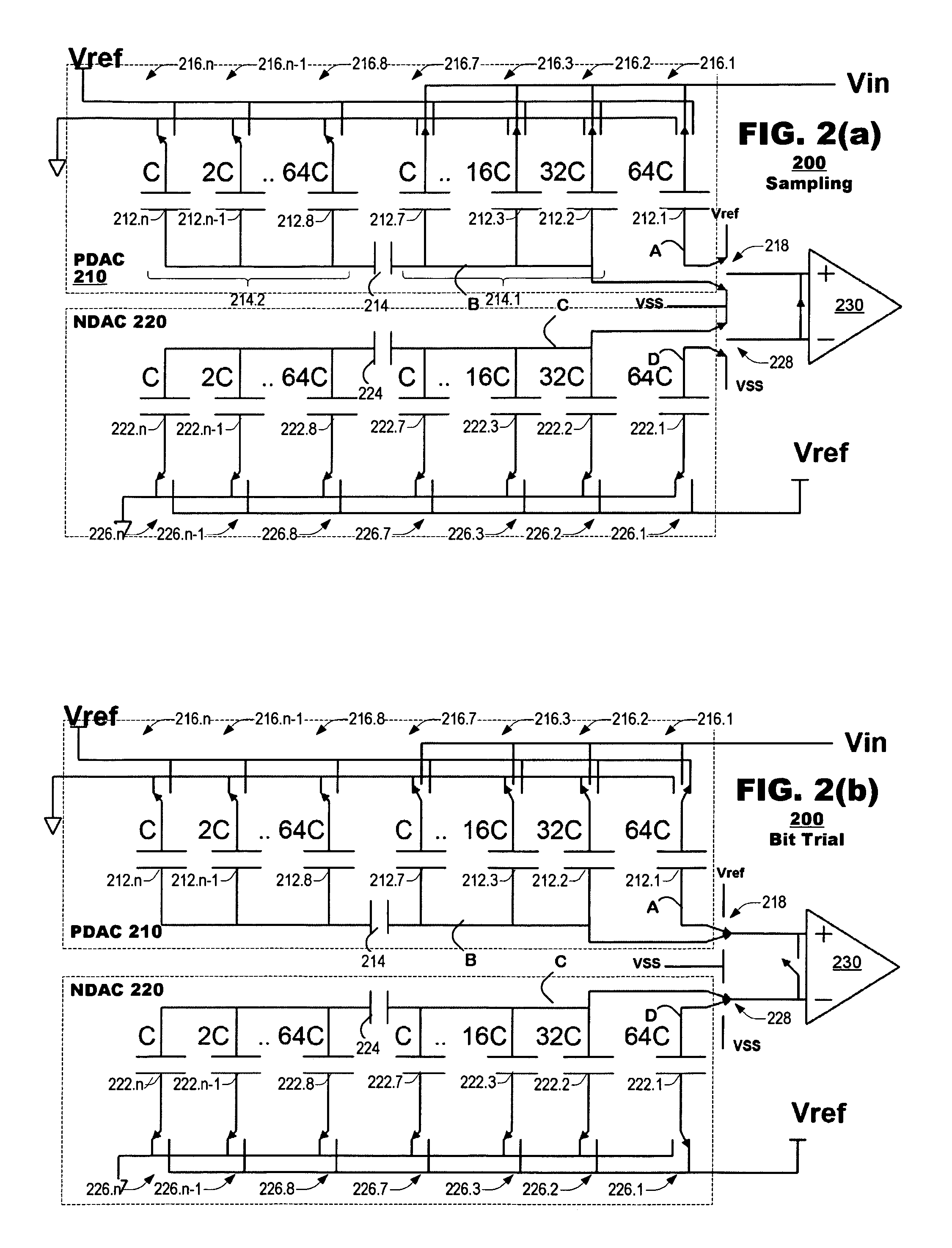

Successive approximation register analog to digital converter with improved immunity to time varying noise

ActiveUS7675452B2Electric signal transmission systemsAnalogue-digital convertersVoltage referenceEngineering

An SAR ADC provides increased immunity to noise introduced by time varying noise components provided on reference potentials (VREF). Reference voltage noise contributions are canceled by introducing a reference voltage component to a pair of binary weighted capacitor arrays (NDAC and PDAC) during bit trials, which are presented to a differential comparator as a common mode signal and rejected. During sampling, select elements in either the PDAC or the NDAC also obtain a reference voltage contribution. Although the sampled VREF signal may have a noise contribution, the noise is fixed at the time of bit trials, which can improve performance. Generally, the scheme provides a 50% reduction in noise errors over the prior art for the same VREF noise. Additional embodiments described herein can reduce noise errors to 25% or even 12.5% over prior art systems.

Owner:ANALOG DEVICES INC

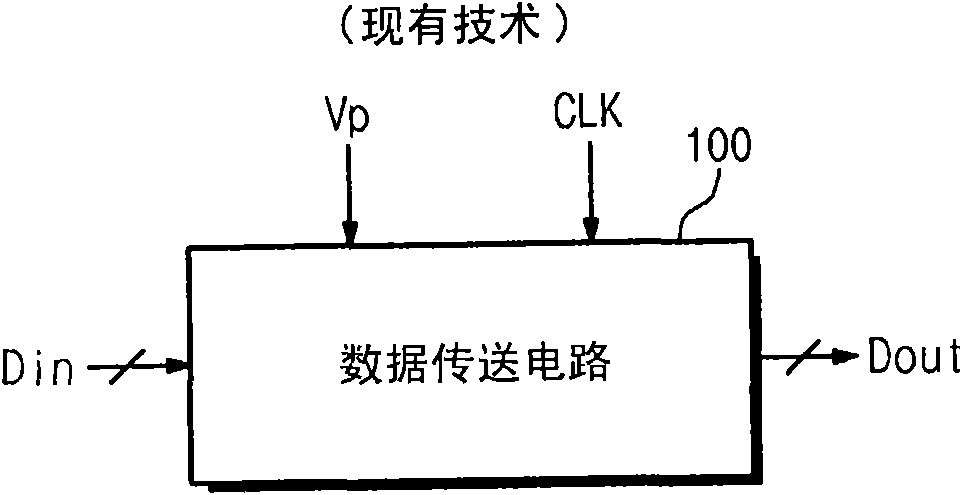

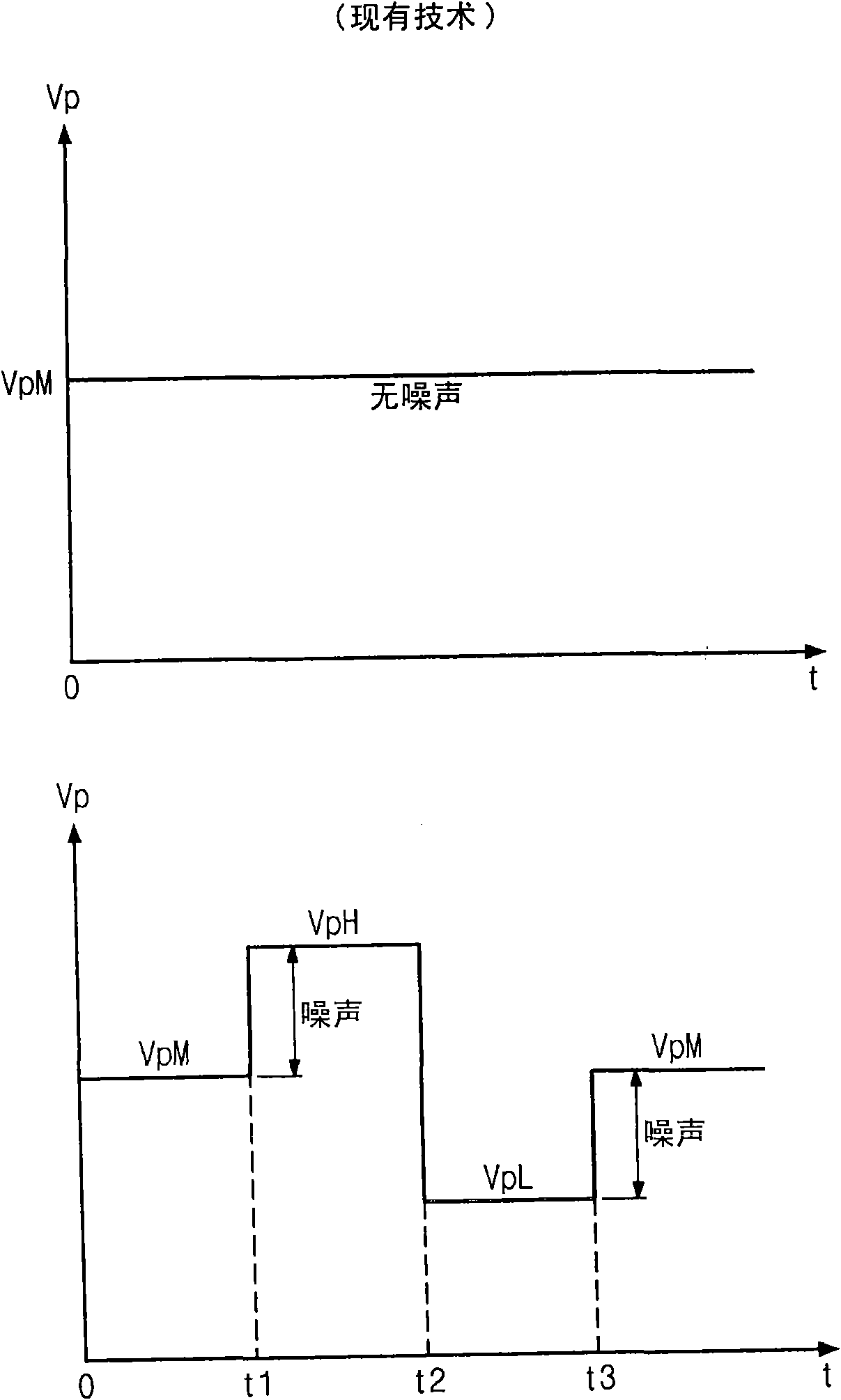

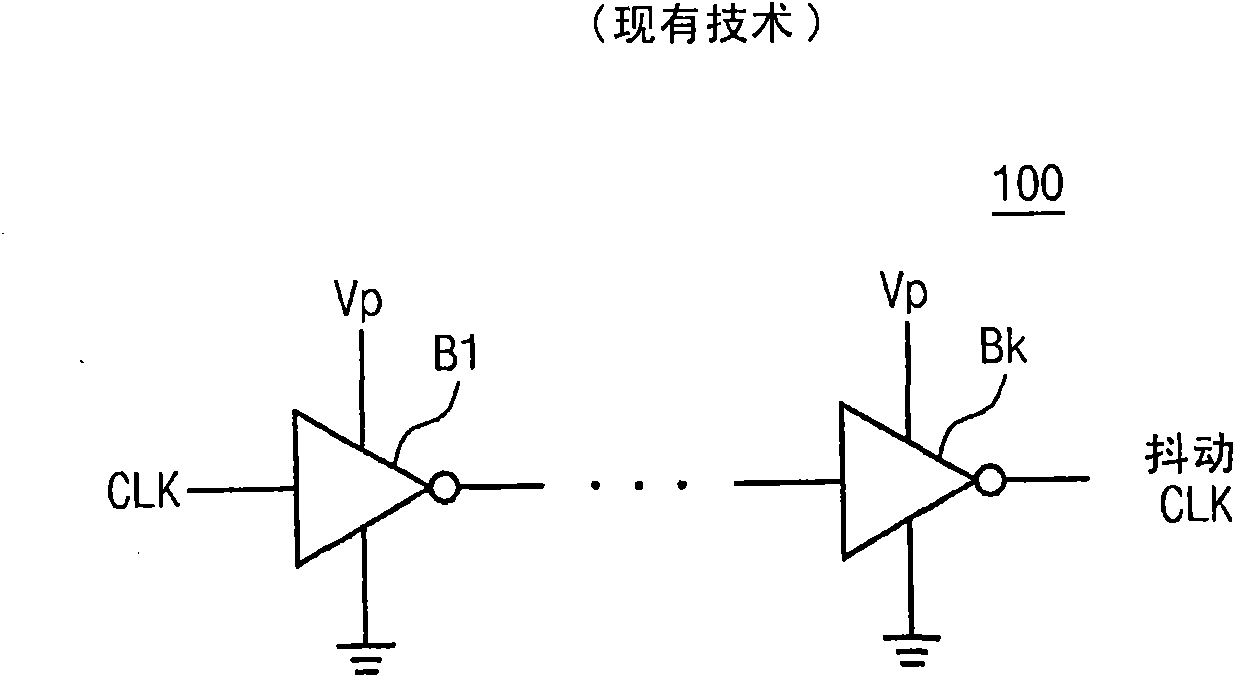

Semiconductor integrated circuit compensating jitter and jitter compensation method

The invention relates to a semiconductor integrated circuit compensating jitter and a jitter compensation method. A data I / O interface for an integrated circuit device includes a noise detector receiving a power supply voltage, detecting a power supply voltage noise component, and providing a clock delay control signal in response to detected power supply voltage noise component. The data I / O interface also includes a clock delay circuit providing a delayed clock signal in response to the clock delay control signal, and a data transfer circuit powered by the power supply voltage and providing output data synchronously with the delayed clock signal.

Owner:SAMSUNG ELECTRONICS CO LTD

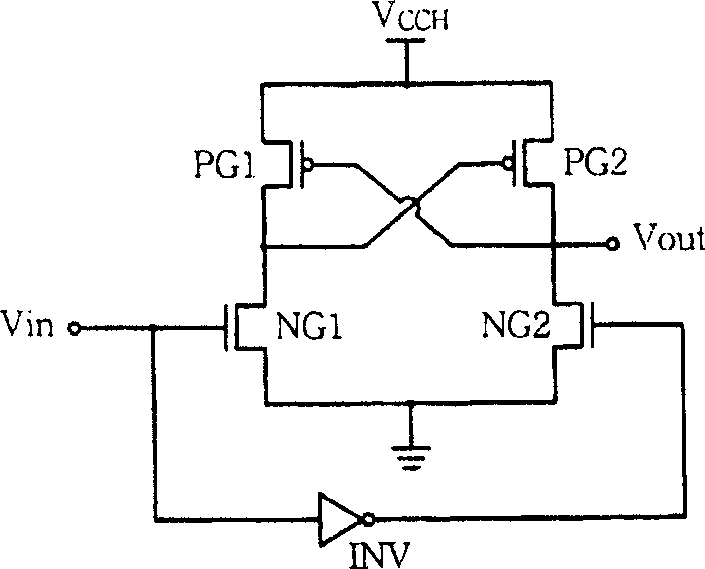

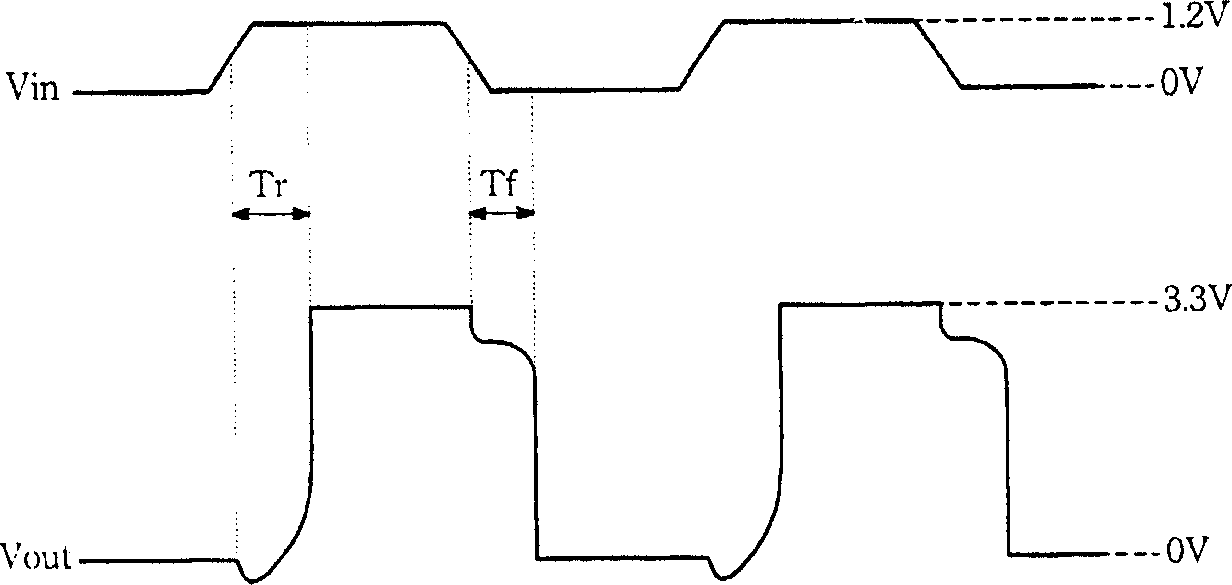

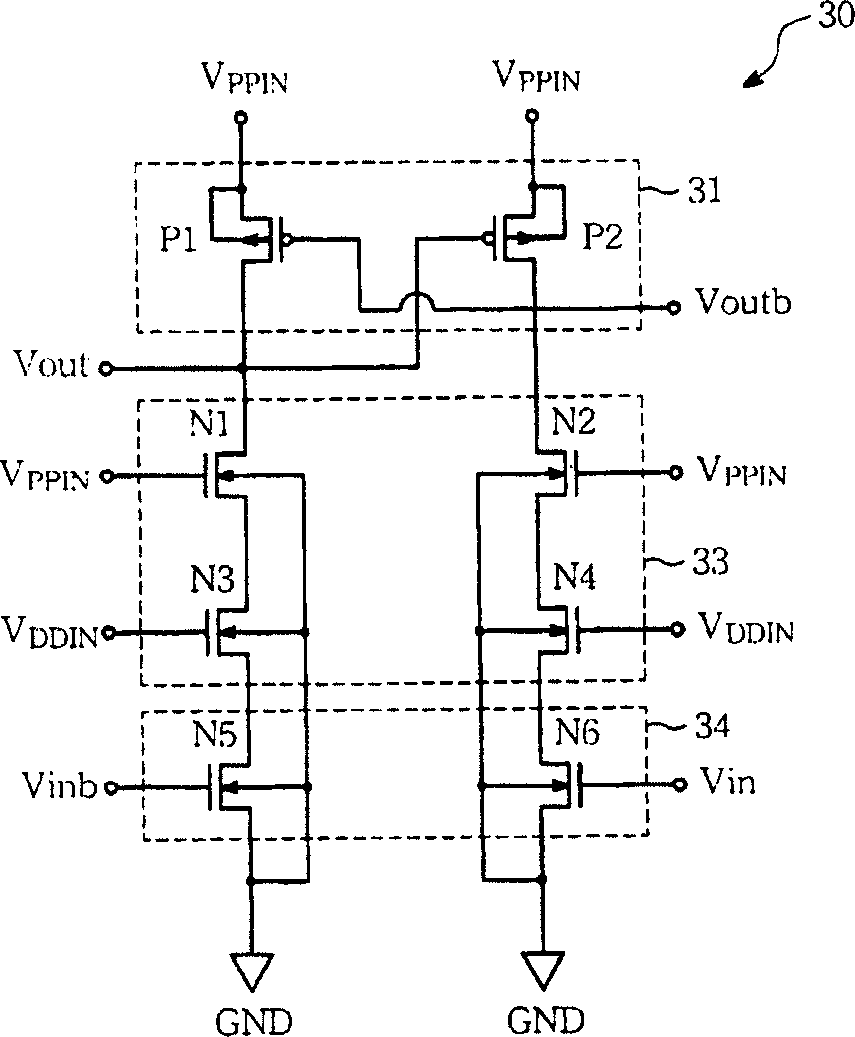

Voltage level converter

ActiveCN1764069AReduce noiseReduce jitterLogic circuits coupling/interface using field-effect transistorsVoltage dropEngineering

The disclosed voltage-level translator, which comprises a draw-up circuit, a path cutting circuit to separate the draw-up / down circuits when translating, a voltage drop circuit, and a draw-down circuit constructed by thin-grid transistor for the low received voltage to improve switch speed. This invention avoids the competition between draw-up and down circuits, and reduces output voltage noise and jitter.

Owner:VIA TECH INC

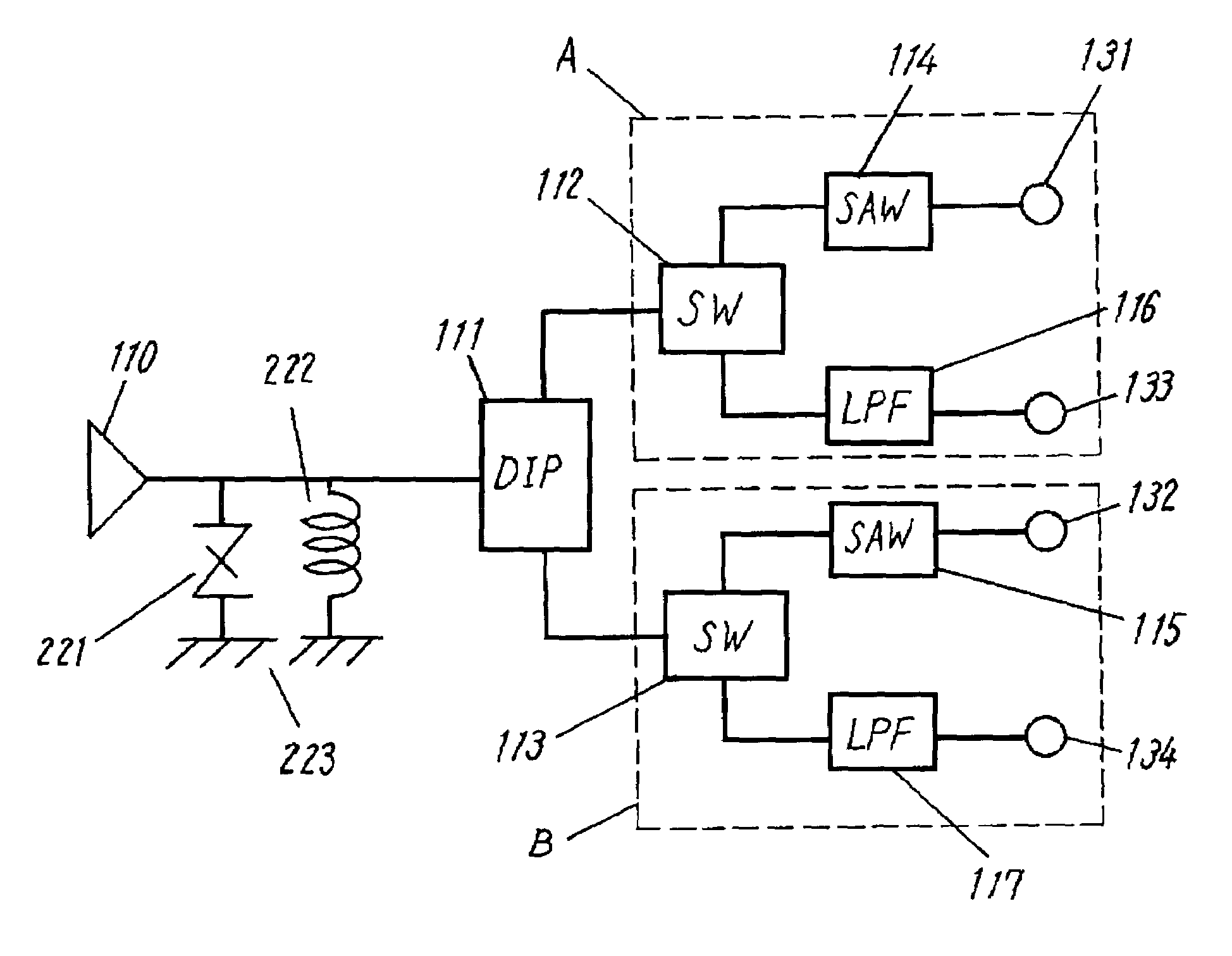

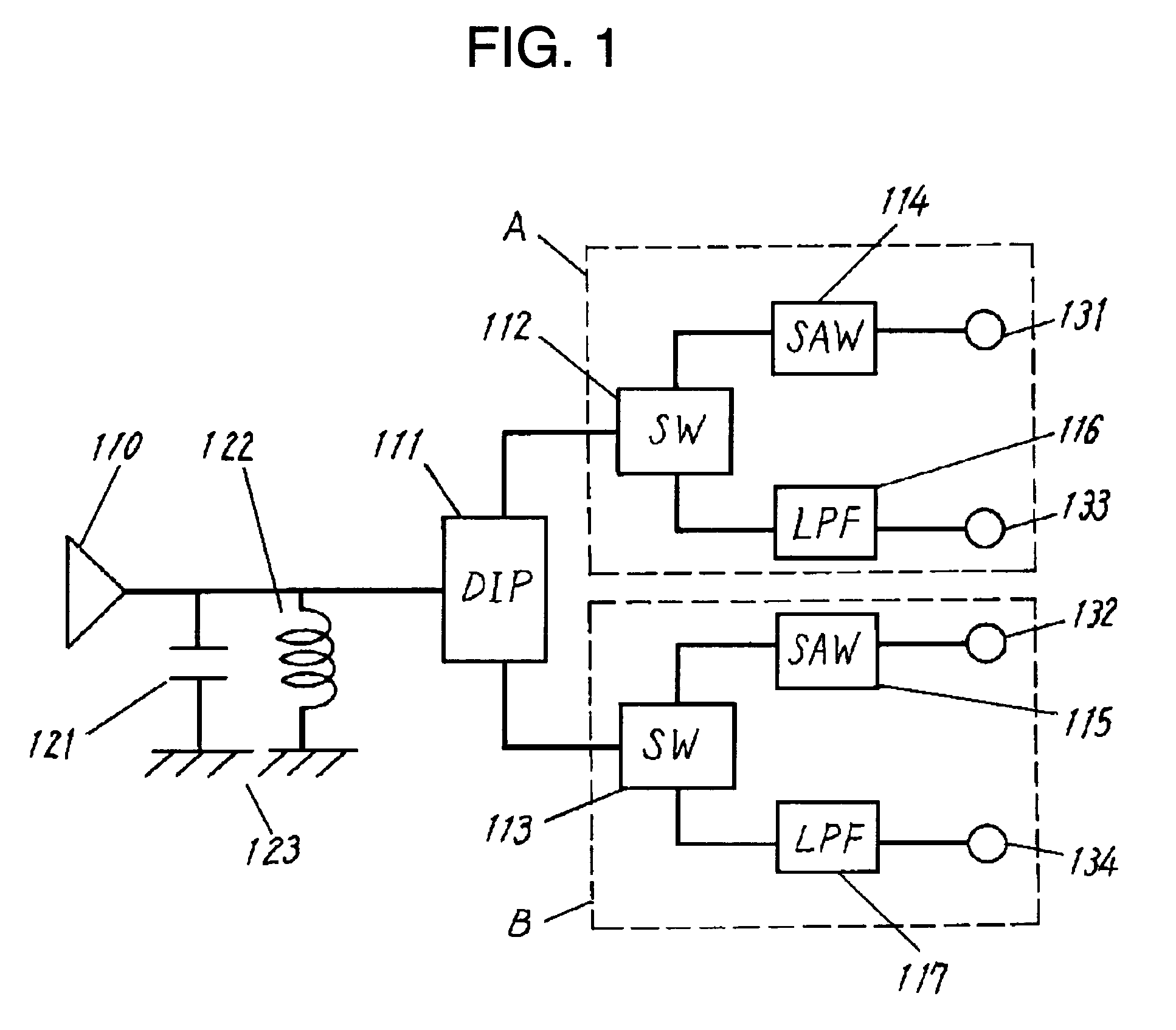

High-frequency device

A high-frequency device includes an antenna terminal, a signal line connected to the antenna terminal, a high-frequency signal processing circuit connected to the signal line, a capacitance element having one end connected to the signal line and other end grounded, and an inductor having one end connected to the signal line and other end grounded. The high-frequency device can protect the high-frequency signal processing circuit from a high voltage noise, such as a static electricity, having a frequency close to a signal pass band.

Owner:PANASONIC CORP

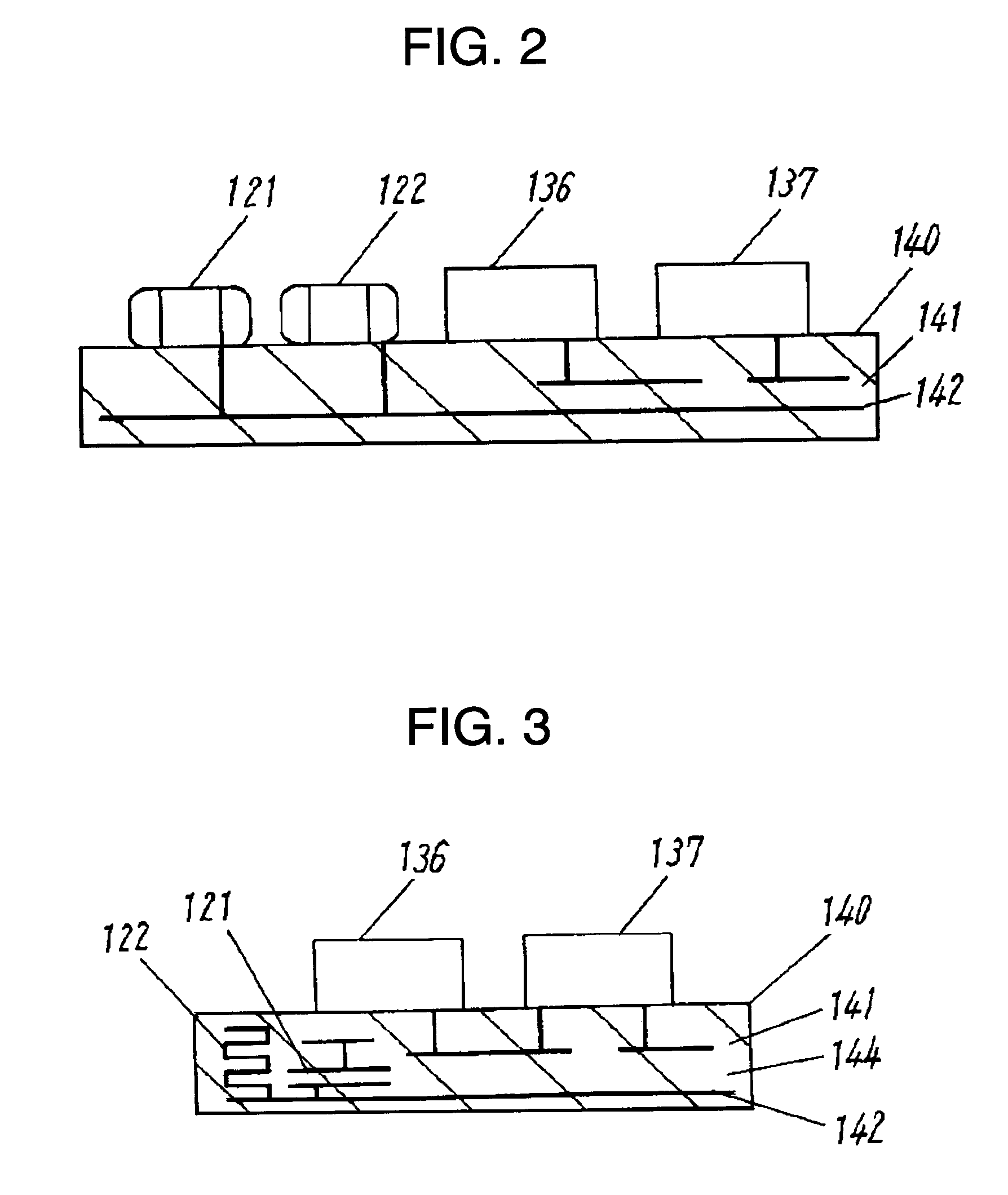

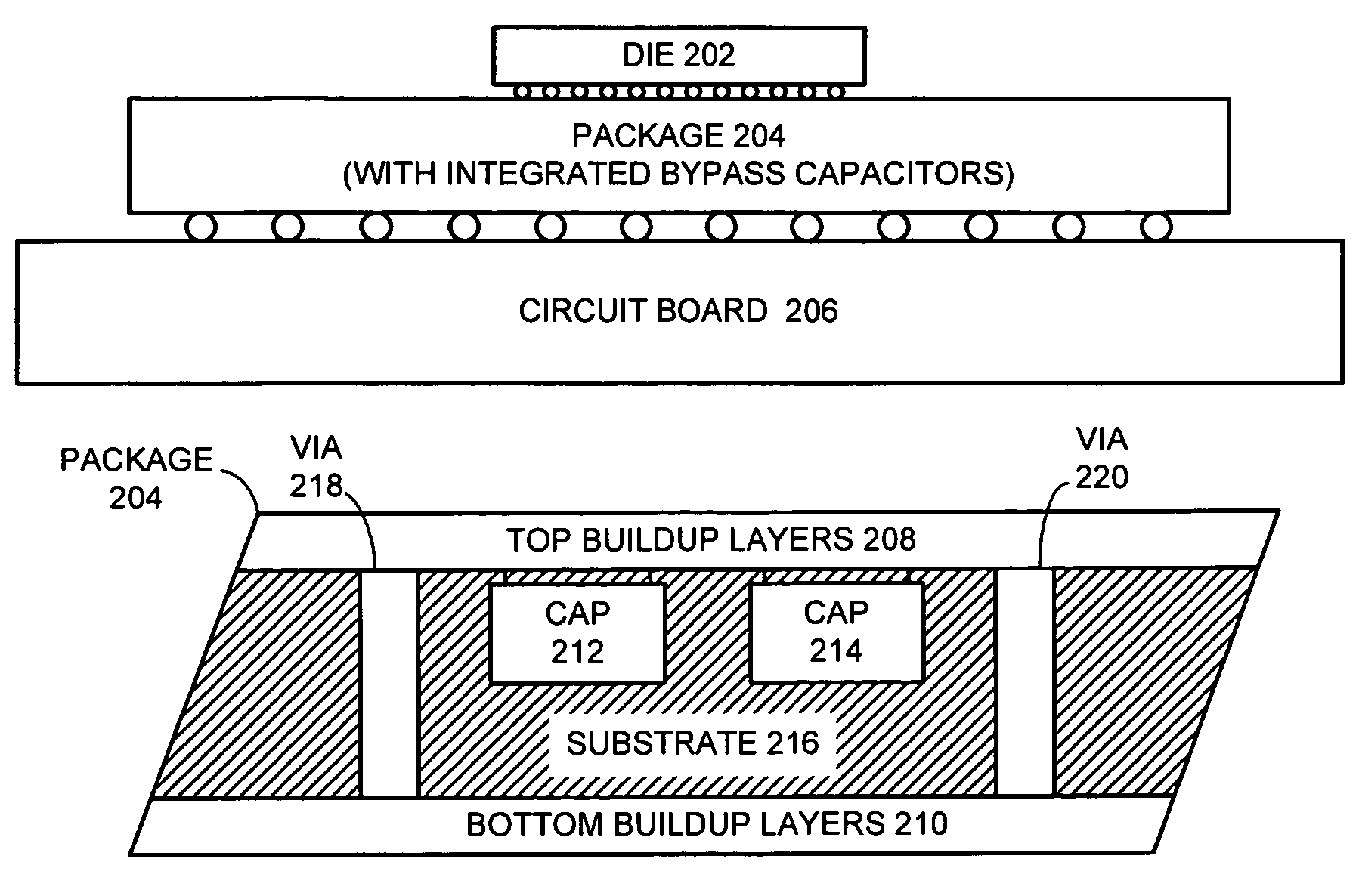

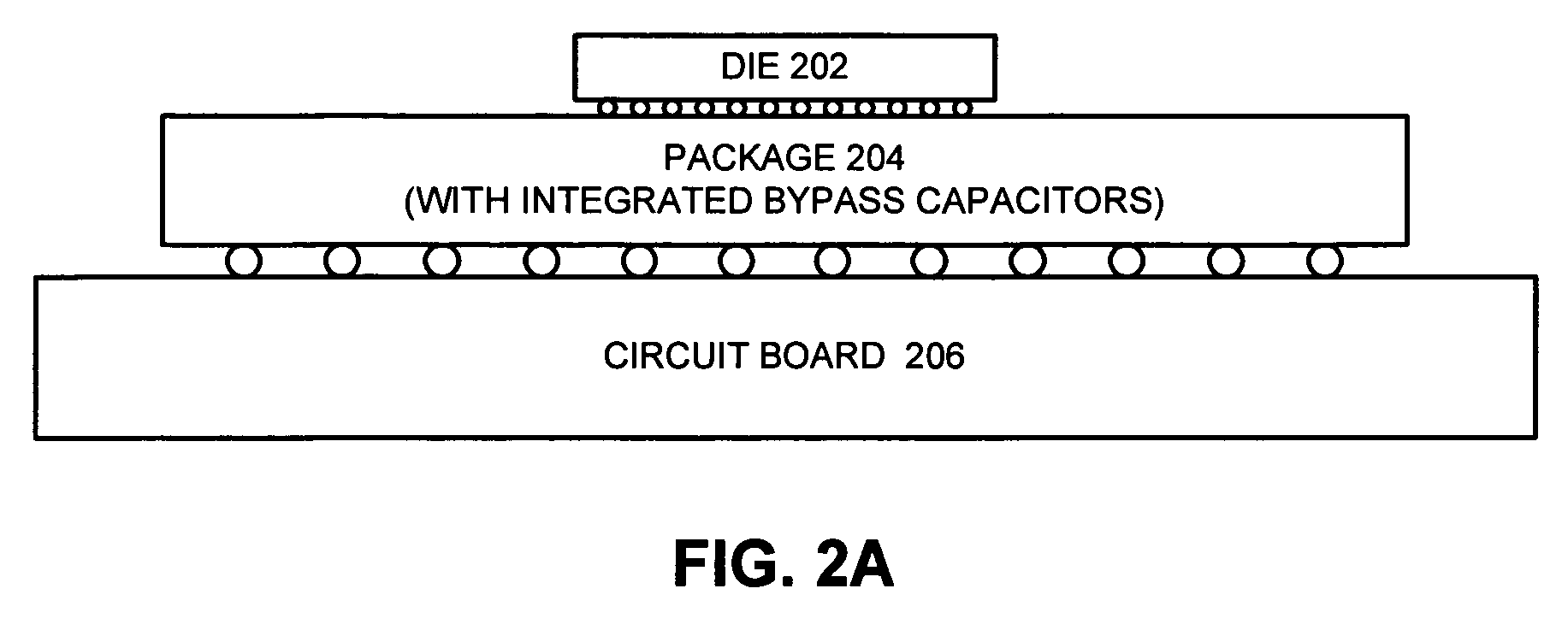

Semiconductor die package with internal bypass capacitors

InactiveUS7446389B2Reduce voltageReduce noiseSemiconductor/solid-state device detailsSolid-state devicesElectricityCapacitance

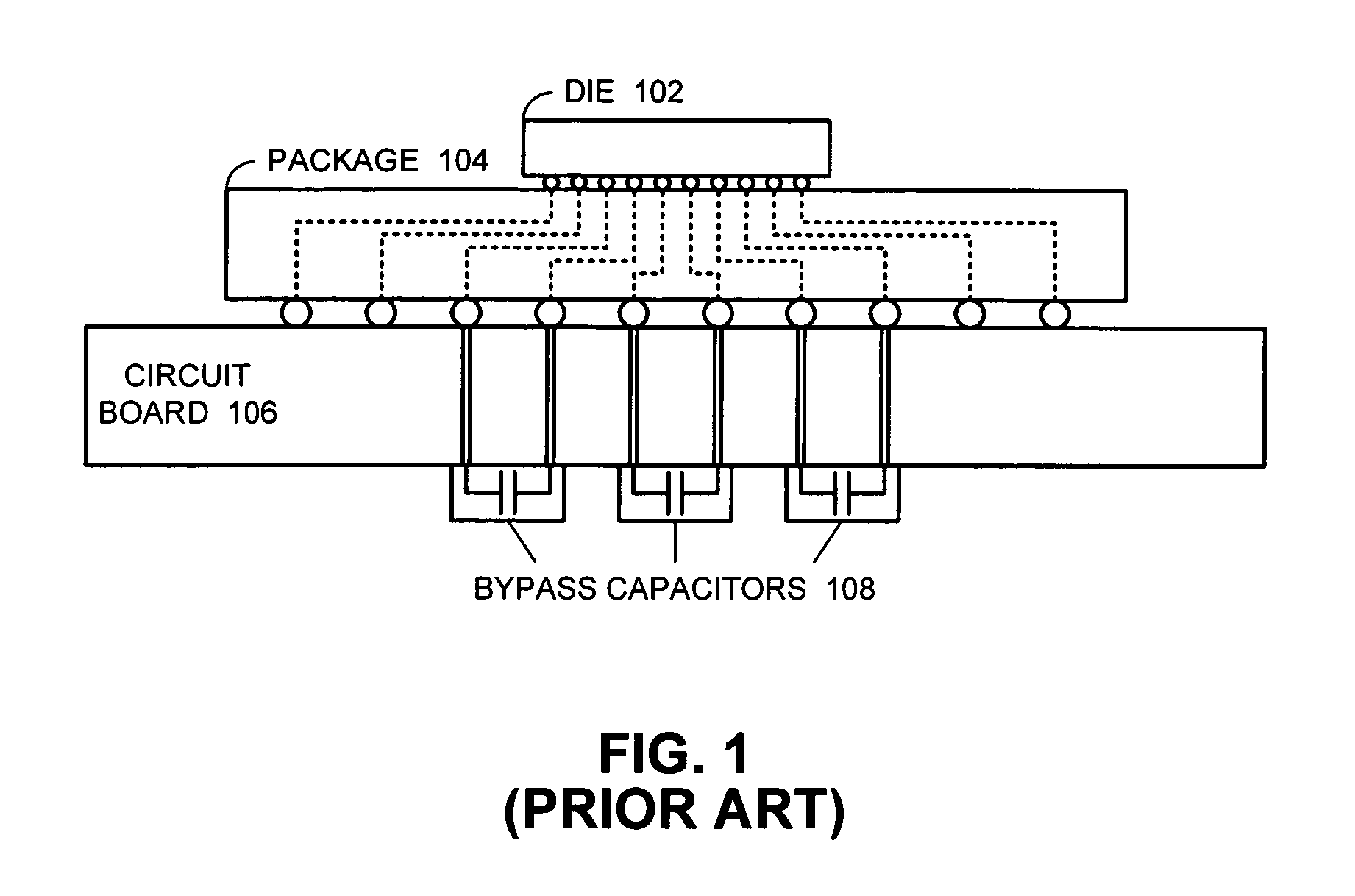

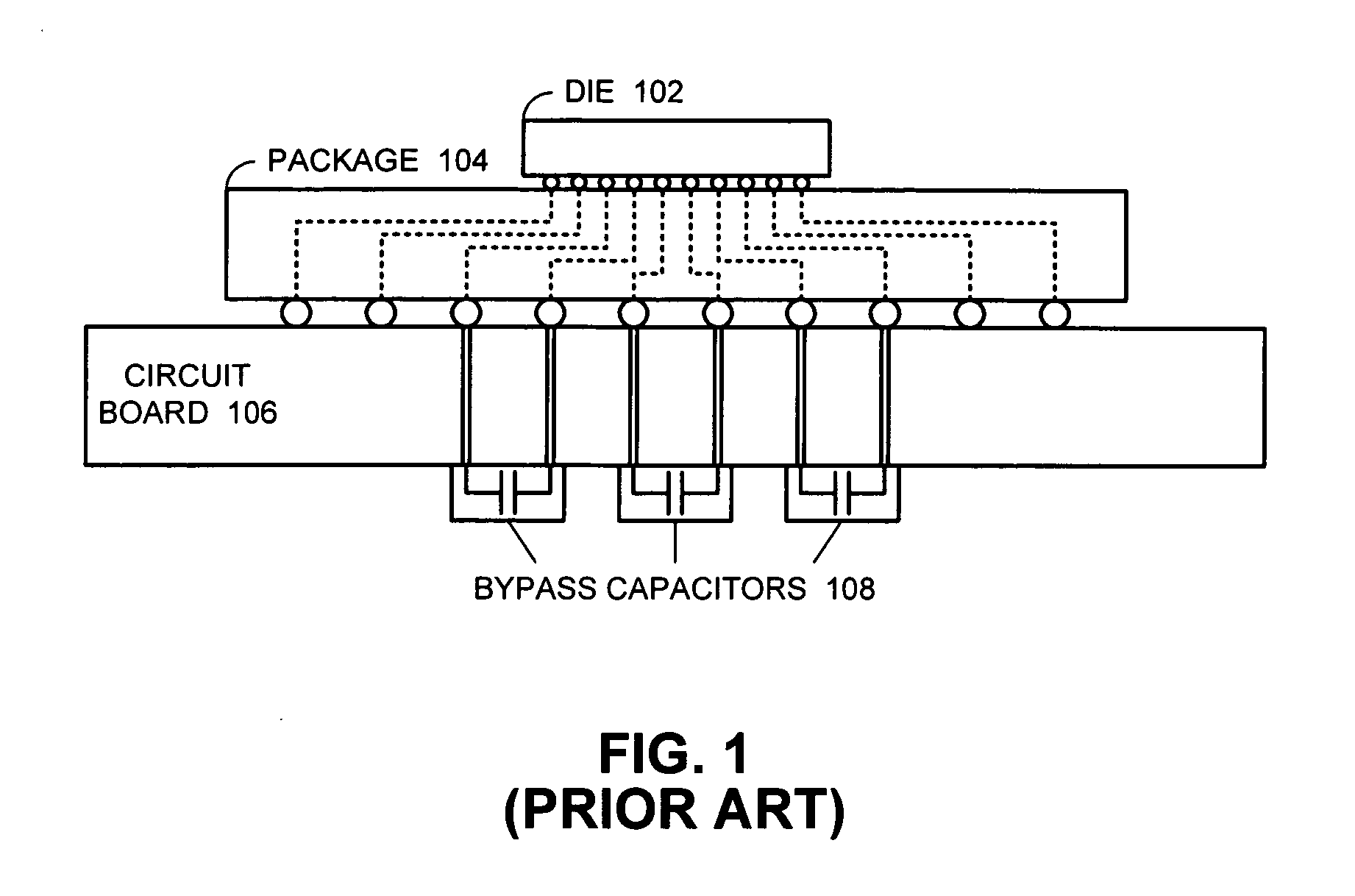

One embodiment of the present invention provides an apparatus that reduces voltage noise for an integrated circuit (IC) device. This apparatus includes a package which is configured to be sandwiched between the IC device and a circuit board. This package has a bottom surface, which is configured to receive electrical connections for power, ground and other signals from the circuit board, and a top surface, which is configured to provide electrical connections for power, ground and the other signals to the IC device. A plurality of bypass capacitors are integrated into the package and are coupled between the power and ground connections for the IC device, so that the plurality of bypass capacitors reduce voltage noise between the power and ground connections for the IC device.

Owner:APPLE INC

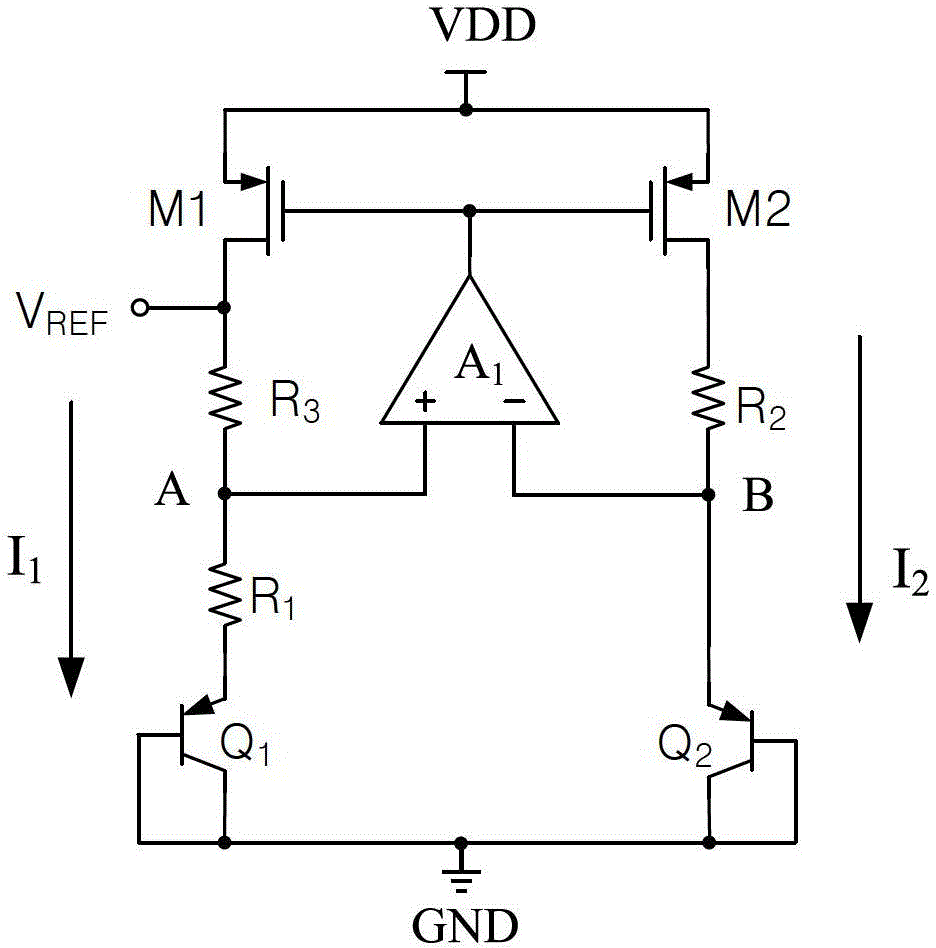

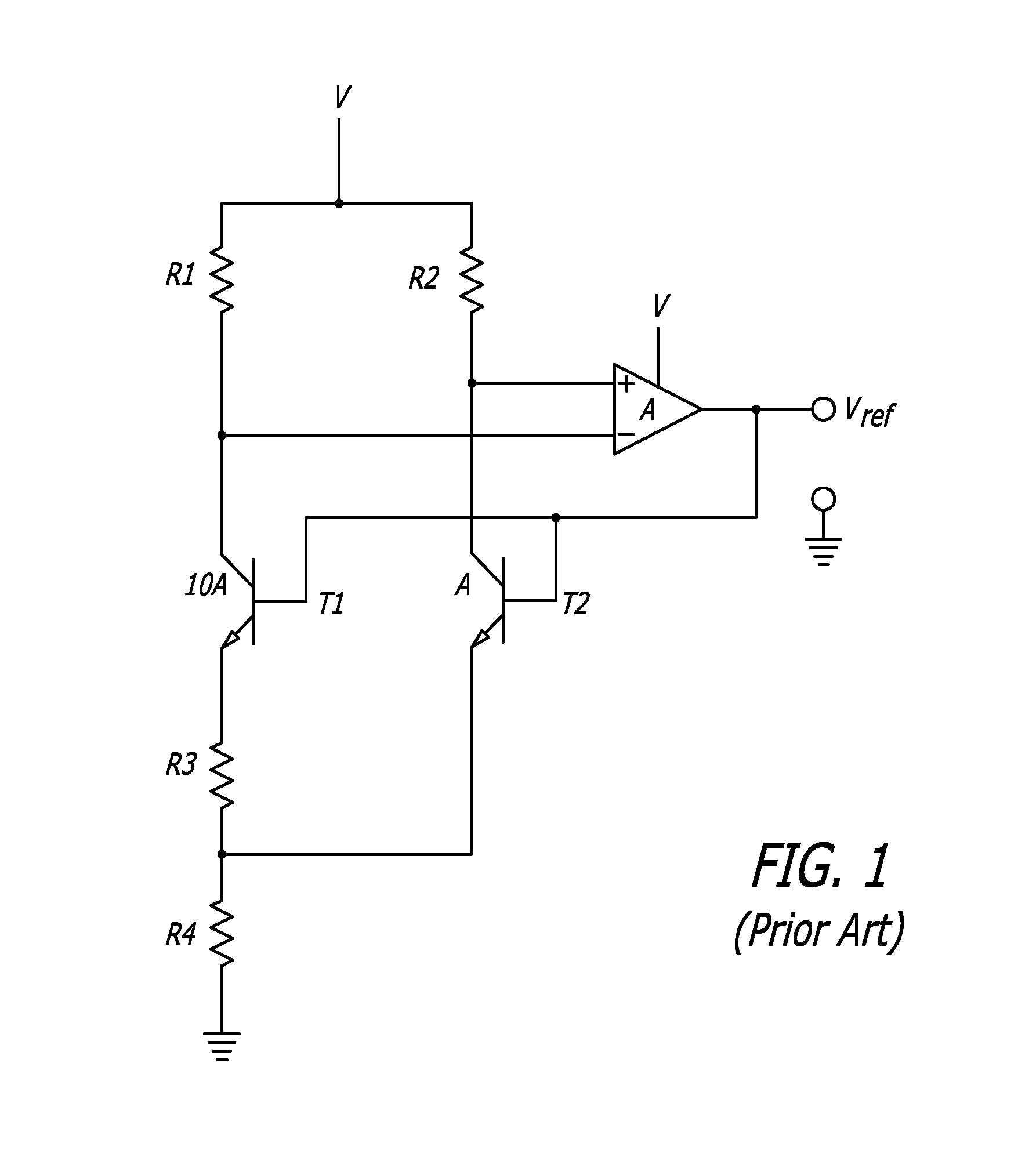

Band gap voltage reference circuit

ActiveCN103941792ALittle changeReduce noiseElectric variable regulationAudio power amplifierLocal oscillator

The invention provides a band gap voltage reference circuit, and belongs to the field of analog circuits. The band gap reference circuit comprises a first PMOS transistor, a second NMOS transistor, a third NMOS transistor, a fourth PMOS transistor, a fifth PMOS transistor, a sixth PMOS transistor, a first PNP audion, a second PNP audion, a capacitor C, a first resistor, a second resistor, a third resistor, a fourth resistor, a fifth resistor and an operational amplifier. According to the technical scheme, the influence of local oscillator noise and voltage noise on output voltages can be lowered, the precision of a reference voltage is improved, meanwhile, the area of a chip is considered, and the design complexity of the circuit is reduced.

Owner:北京森海晨阳科技有限责任公司

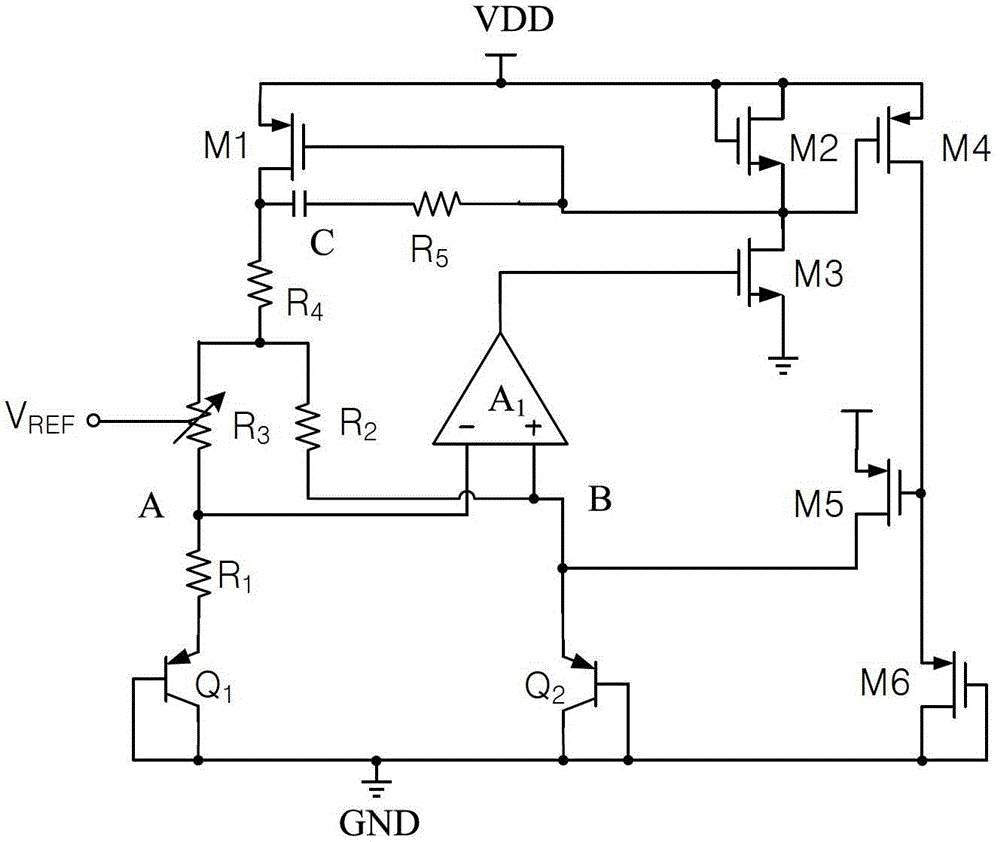

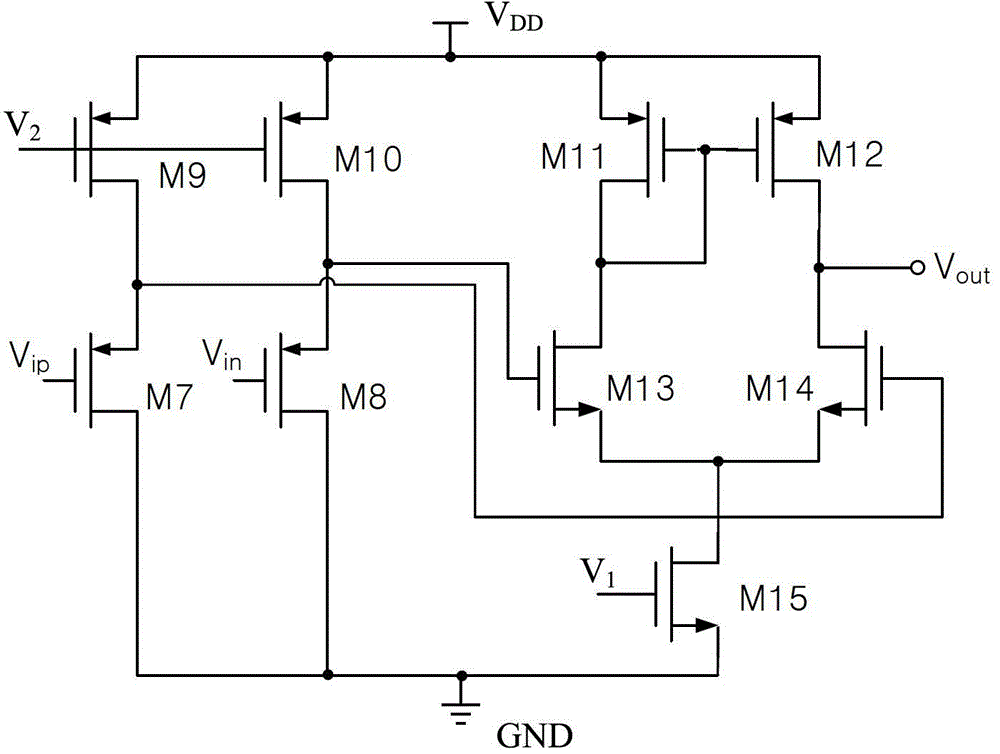

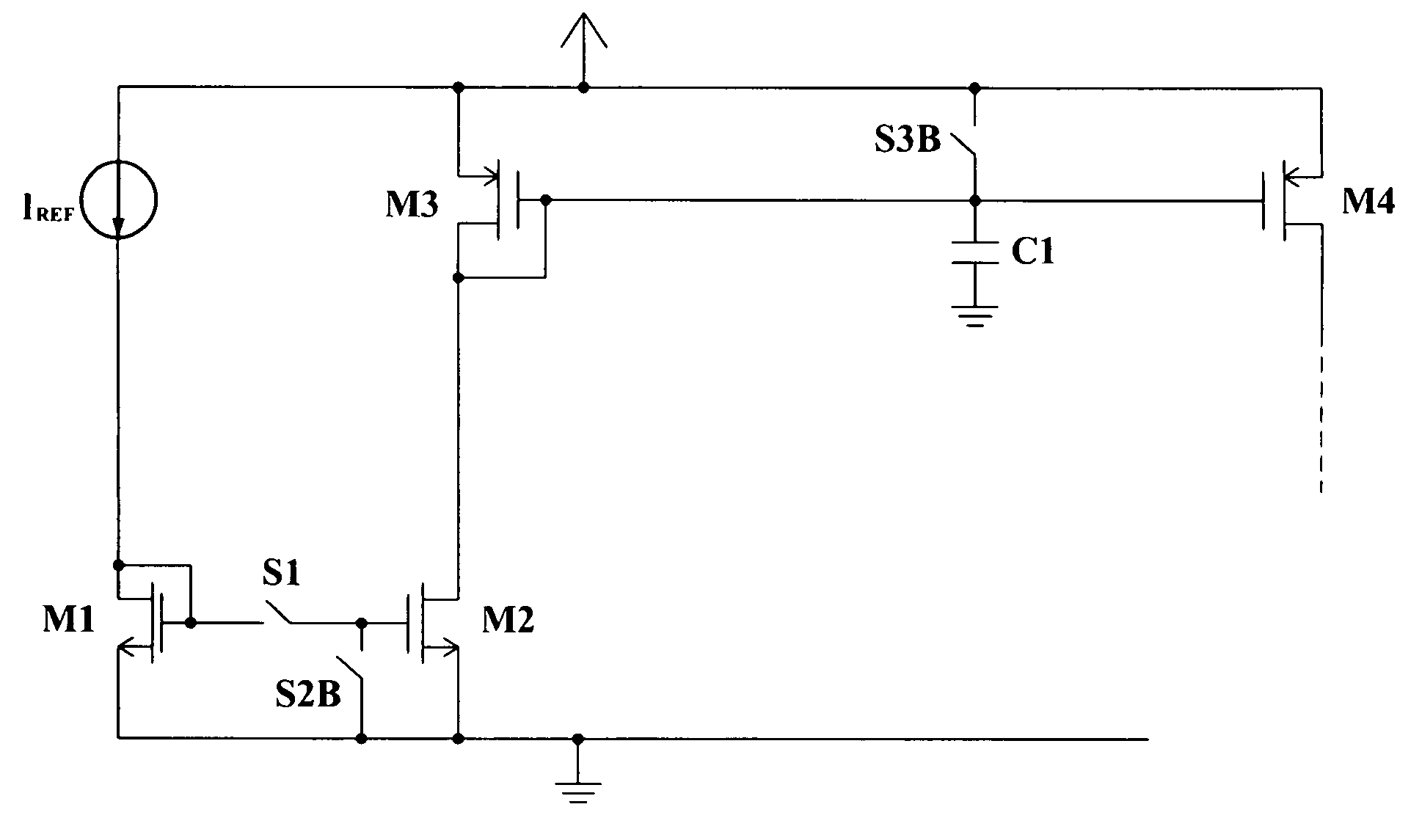

Device for voltage-noise rejection and fast start-up

InactiveUS20070115061A1Reduce reference noiseReduce the impact of noiseInterconnection arrangementsGain controlCapacitanceReference current

Owner:IND TECH RES INST

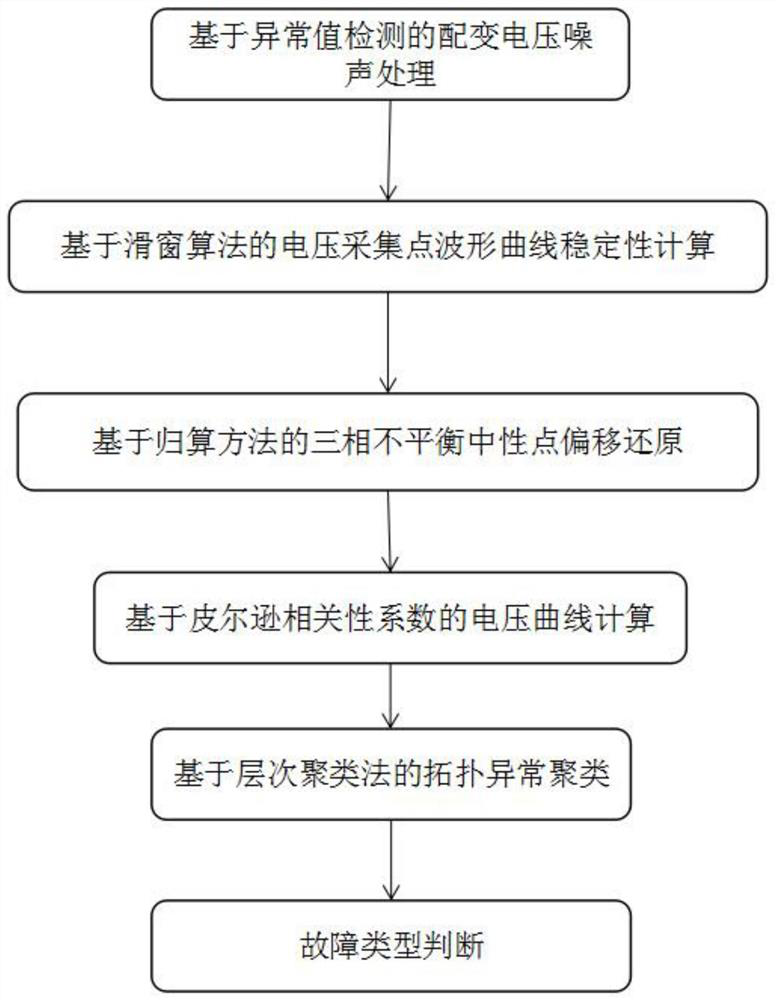

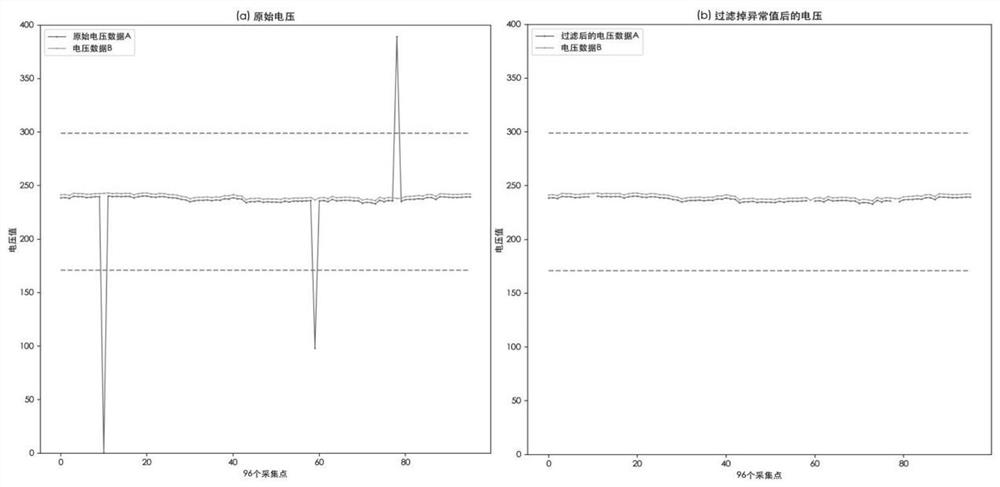

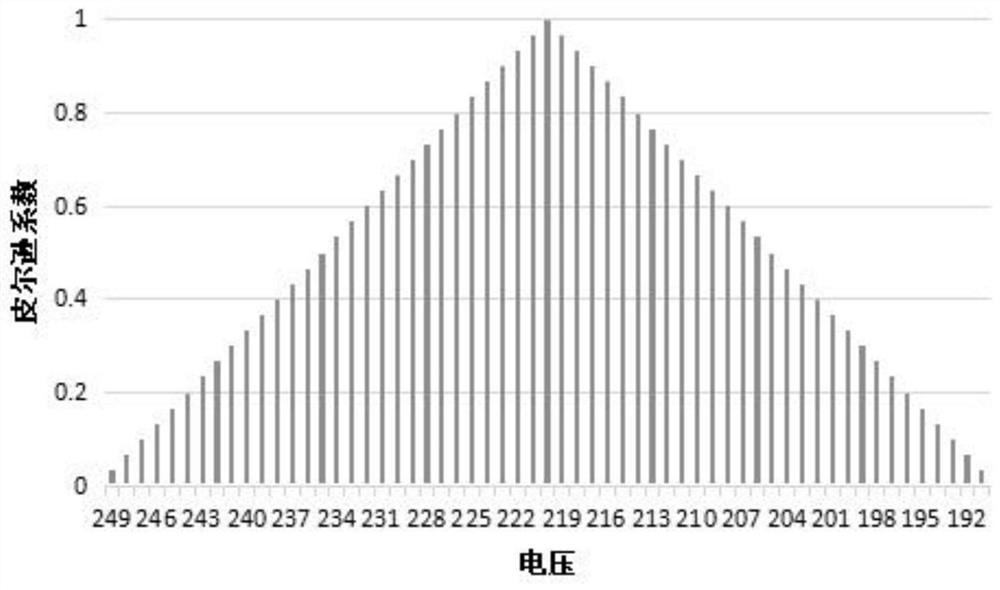

Power distribution network line-transformer relationship anomaly identification and judgment method

InactiveCN112098772AAccurate identificationImprove accuracyFault location by conductor typesDistribution transformerAlgorithm

The invention discloses a power distribution network line-transformer relationship anomaly identification and judgment method, which comprises the following steps of distribution transformer voltage noise processing based on abnormal value detection, voltage acquisition point waveform curve stability calculation based on a sliding window algorithm, three-phase imbalance neutral point offset reduction based on a reduction method, a Pearson-correlation-coefficient-based voltage curve calculation method for judging the similarity degree of voltage curves, topological anomaly clustering based on ahierarchical clustering method, and fault determination. On the basis of massive operation data of a centralized power grid, the operation situation of a topological structure is reflected by researching and utilizing service characteristics of voltage waveform similarity through a distribution transformer voltage waveform hierarchical clustering method, and a standing book and power grid topological data are accurately identified; on the basis of a voltage curve waveform correlation coefficient, hierarchical clustering is used to realize accurate identification of the topological structure,and the accuracy and authenticity of the topological structure of the power distribution network are comprehensively improved; and through secondary comparison, the fault type is quickly determined.

Owner:TONGLING POWER SUPPLY CO OF STATE GRID ANHUI ELECTRIC POWER CO

Apparatus for providing capacitive decoupling between on-die power and ground conductors

InactiveUS7391110B2Reduce noiseReduce inductanceSemiconductor/solid-state device detailsSolid-state devicesCapacitanceElectrical conductor

Owner:APPLE INC

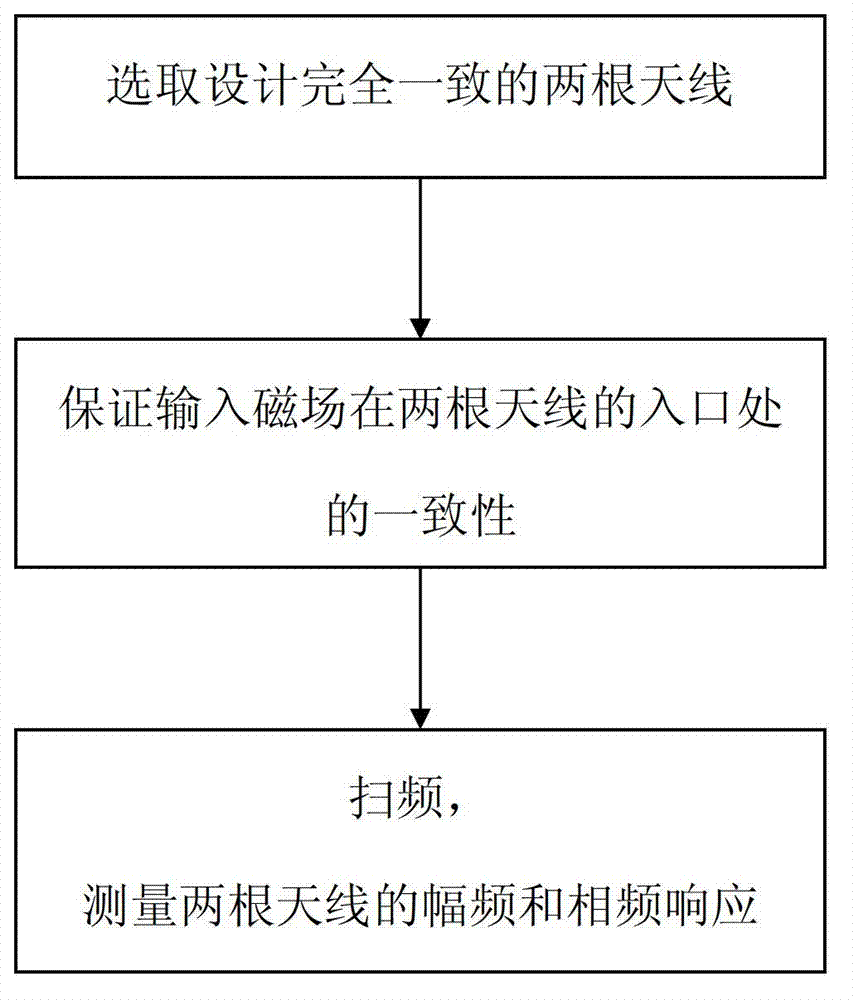

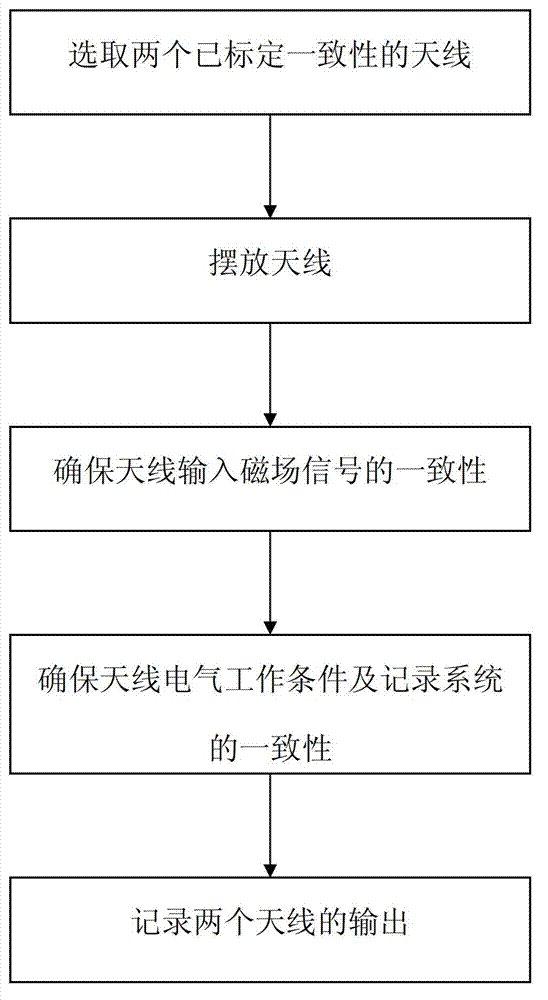

Background noise measuring method of magnetic antennas

ActiveCN102928713AOvercome shieldingOvercome accuracyElectrical testingMeasuring instrumentBackground noise

The invention discloses a background noise measuring method of magnetic antennas. A method combining measuring and mathematical calculation is adopted, and the two antennas good in consistency and a spectrum density calculating method are used to obtain equivalent antenna output voltage noise signals. The background noise measuring method is characterized by comprising the steps of calibrating antenna consistency, measuring antenna output signals and calculating antenna voltage noise spectrum density. By means of the background noise measuring method, additional measuring instruments and shielding measures are not needed, the shortcomings of poor magnetic shielding effect and inaccurate measuring results in direct background noise measuring of the antennas can be overcome, and simultaneously the background noise measuring method is suitable for antennas with different sensitivity and particularly suitable for background noise measuring of magnetic antennas high in accuracy.

Owner:BEIJING MILESTONE SCI & TECH DEV +1

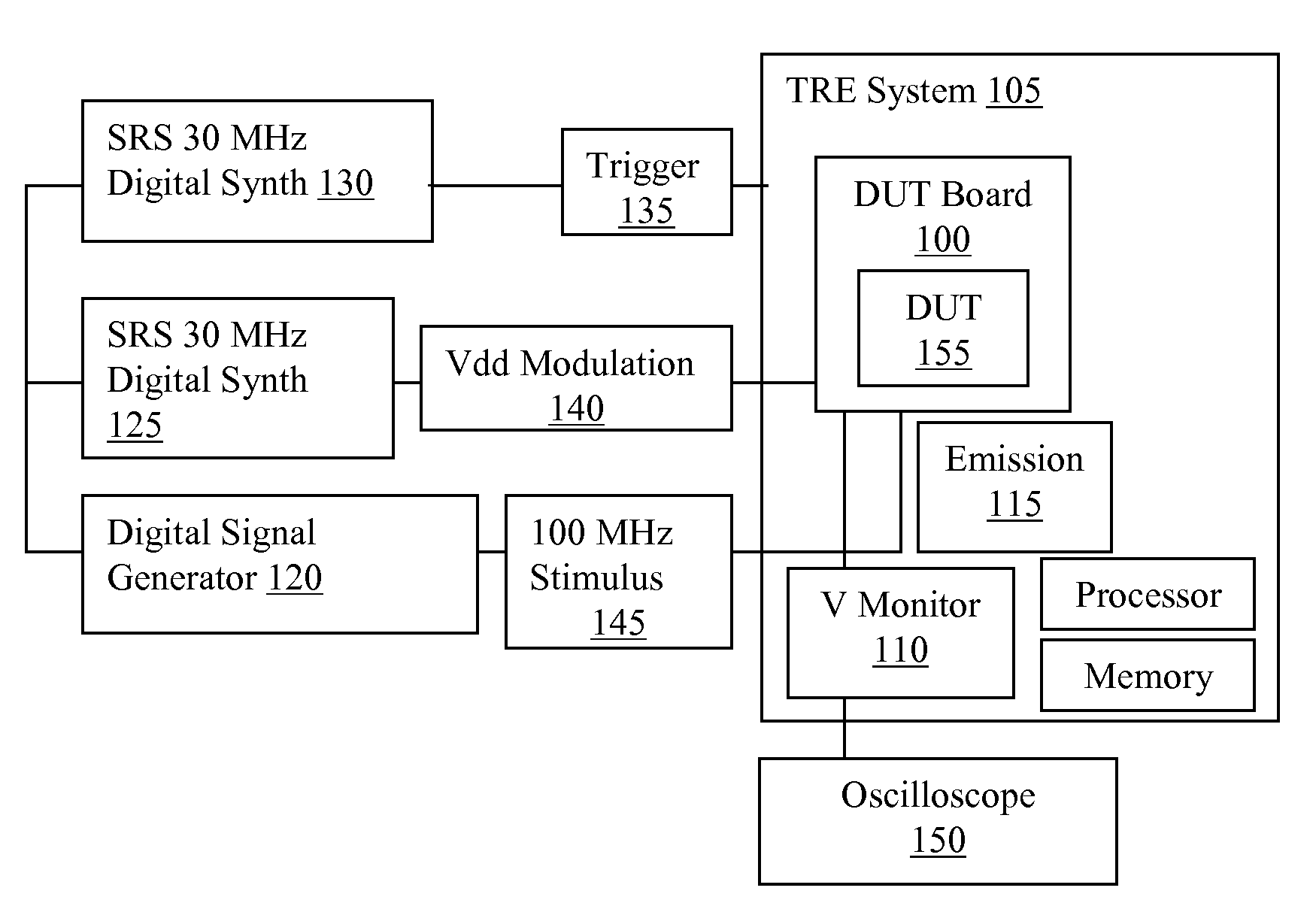

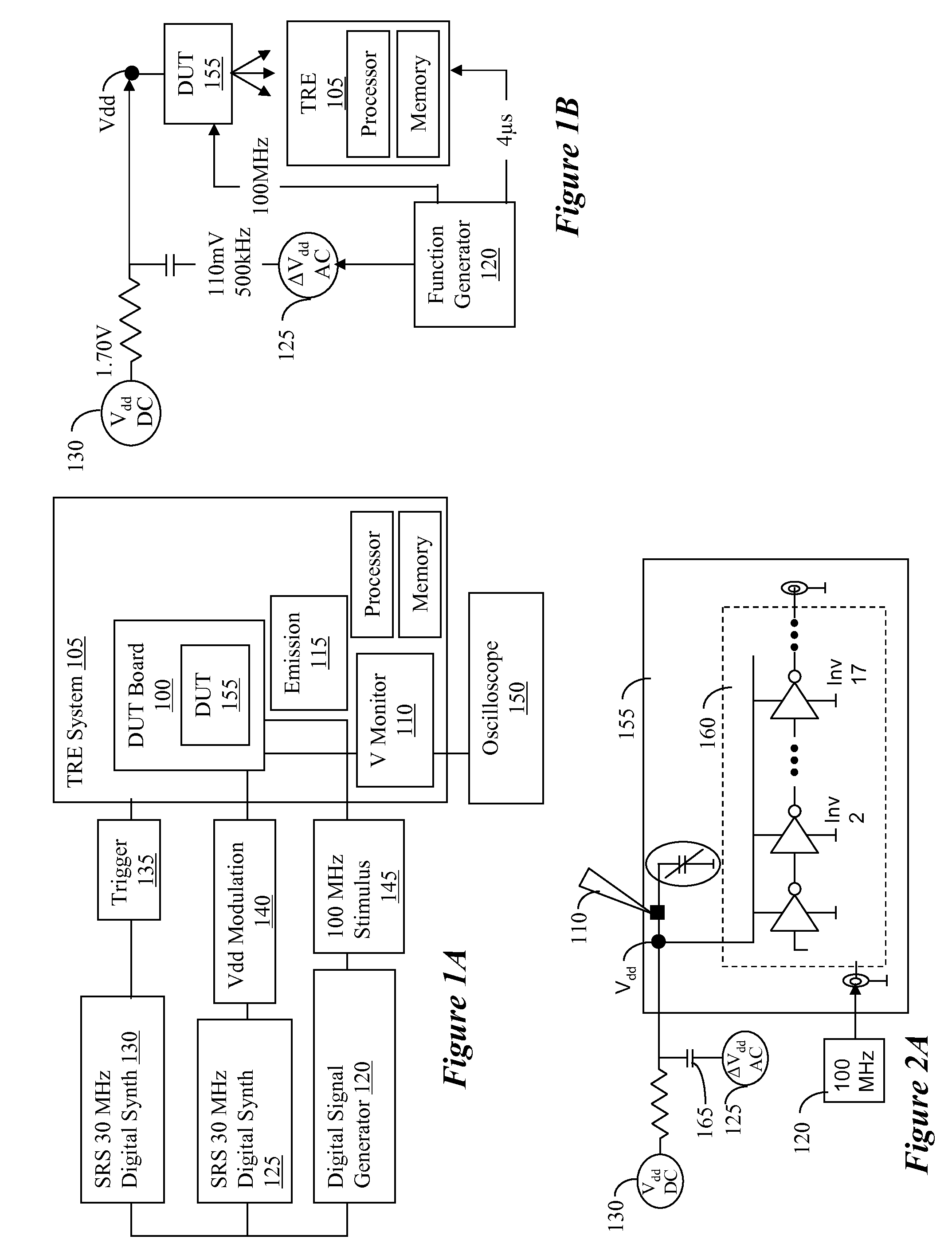

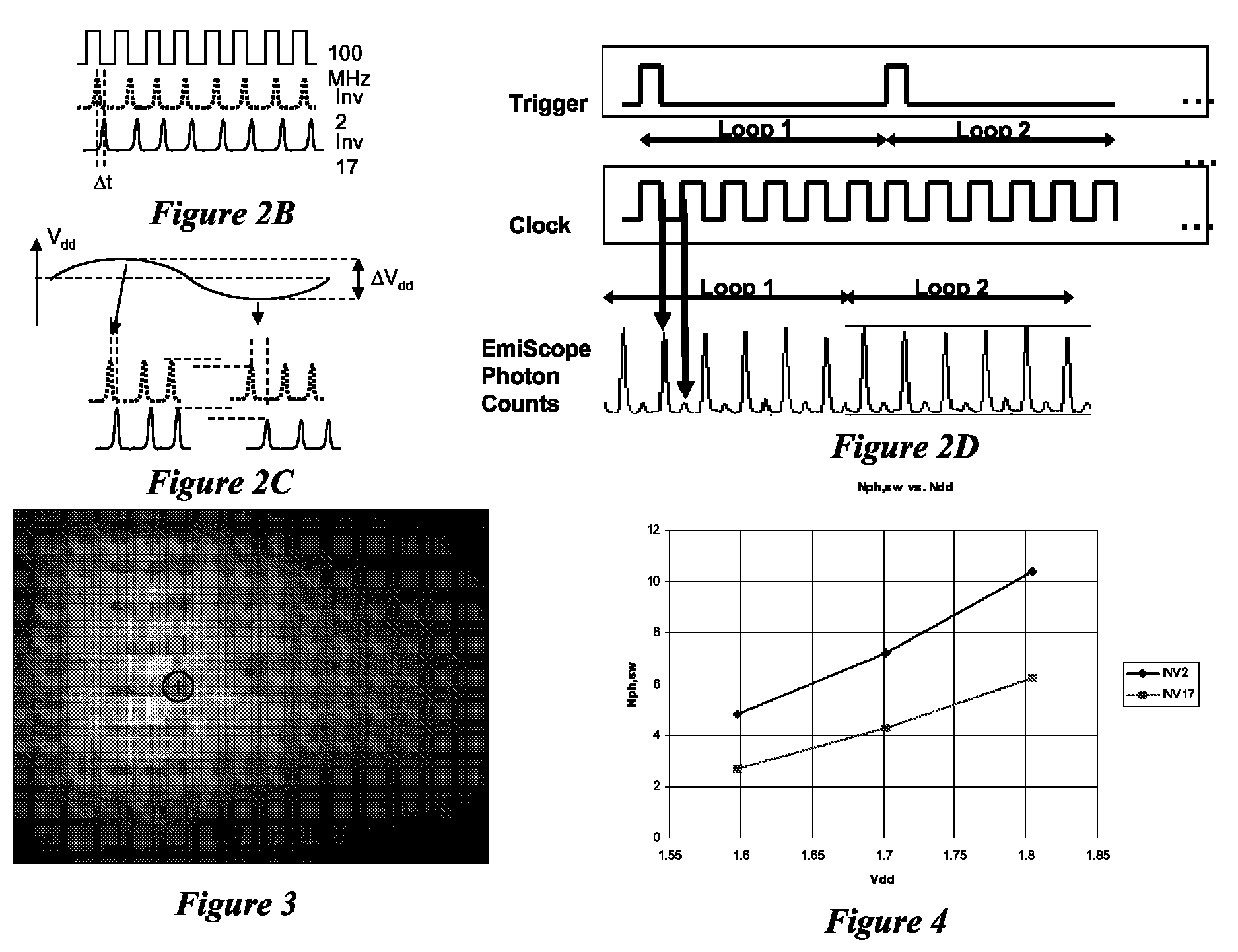

System and method for voltage noise and jitter measurement using time-resolved emission

ActiveUS7679358B2Spectral/fourier analysisNoise figure or signal-to-noise ratio measurementPropagation delayEngineering

Time-resolved emission can be used to measure loop-synchronous, small-signal voltage perturbation in integrated circuits. In this technique the measurements are completely non-invasive and so reflect the true device behavior. The time-dependant propagation delay caused by Vdd modulation also shows the expected qualitative signature. This technique should find applications in circuits with relatively fast clock-like circuits where loop-synchronous voltage pickup is limiting circuit behavior.

Owner:DCG SYST

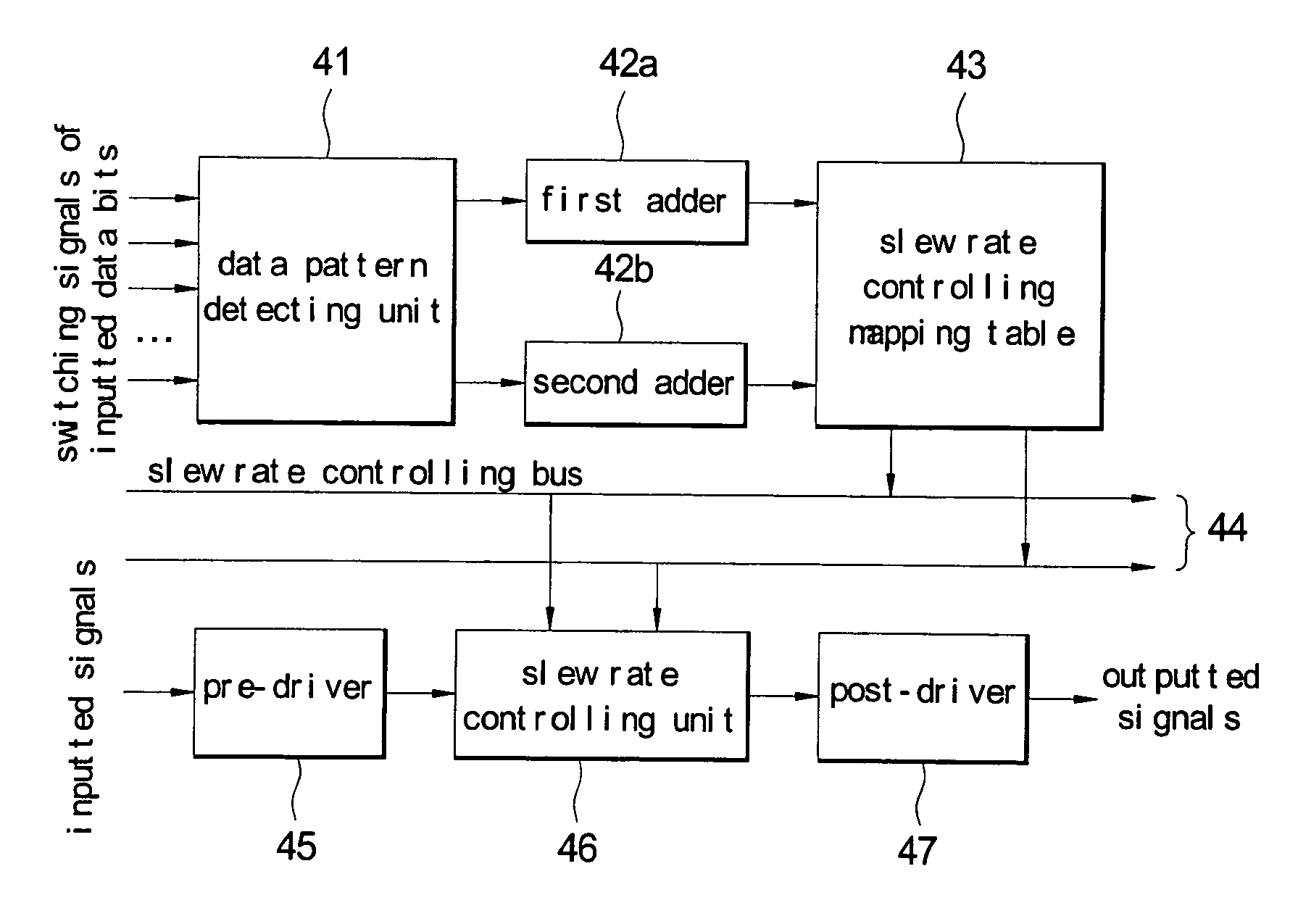

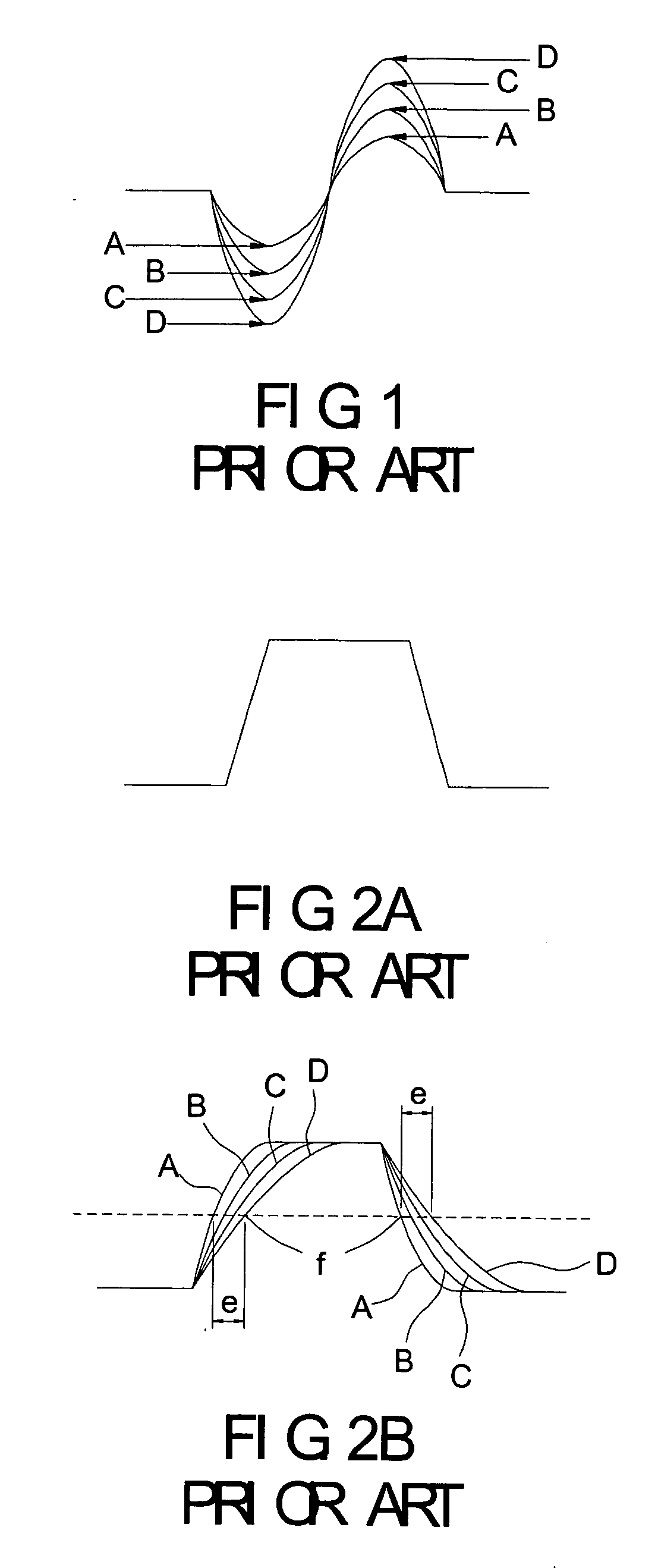

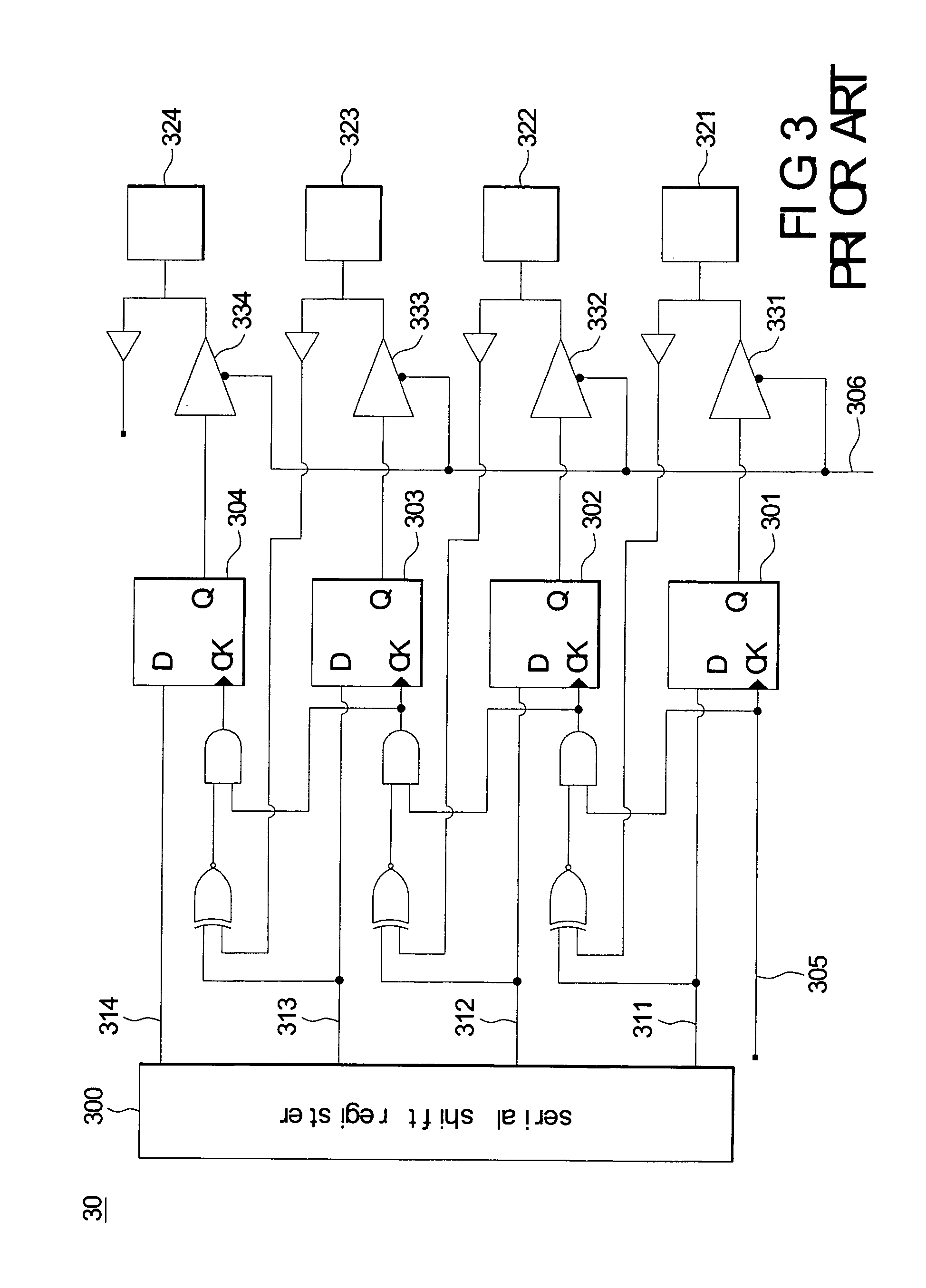

Dynamic slew rate controlling method and device for reducing variance in simultaneous switching output

InactiveUS20050283749A1Reduce varianceVoltage noise then increasesRecord information storageElectronic switchingControl setAnalysis data

A dynamic slew rate controlling method and a device is provided to reduce SSO variance generated from voltage noises, which is as a result of a plurality of data bits switching to the same state simultaneously while the I / O bus transmits these data bits. The device and method at first analyzes data patterns, then determines the slew rate controlling setting value based on the slew rate controlling mapping table corresponding to different data patterns, and then transmits the setting value to the I / O buffer with the same voltage level in order to reduce the SSO variance.

Owner:ALICORP

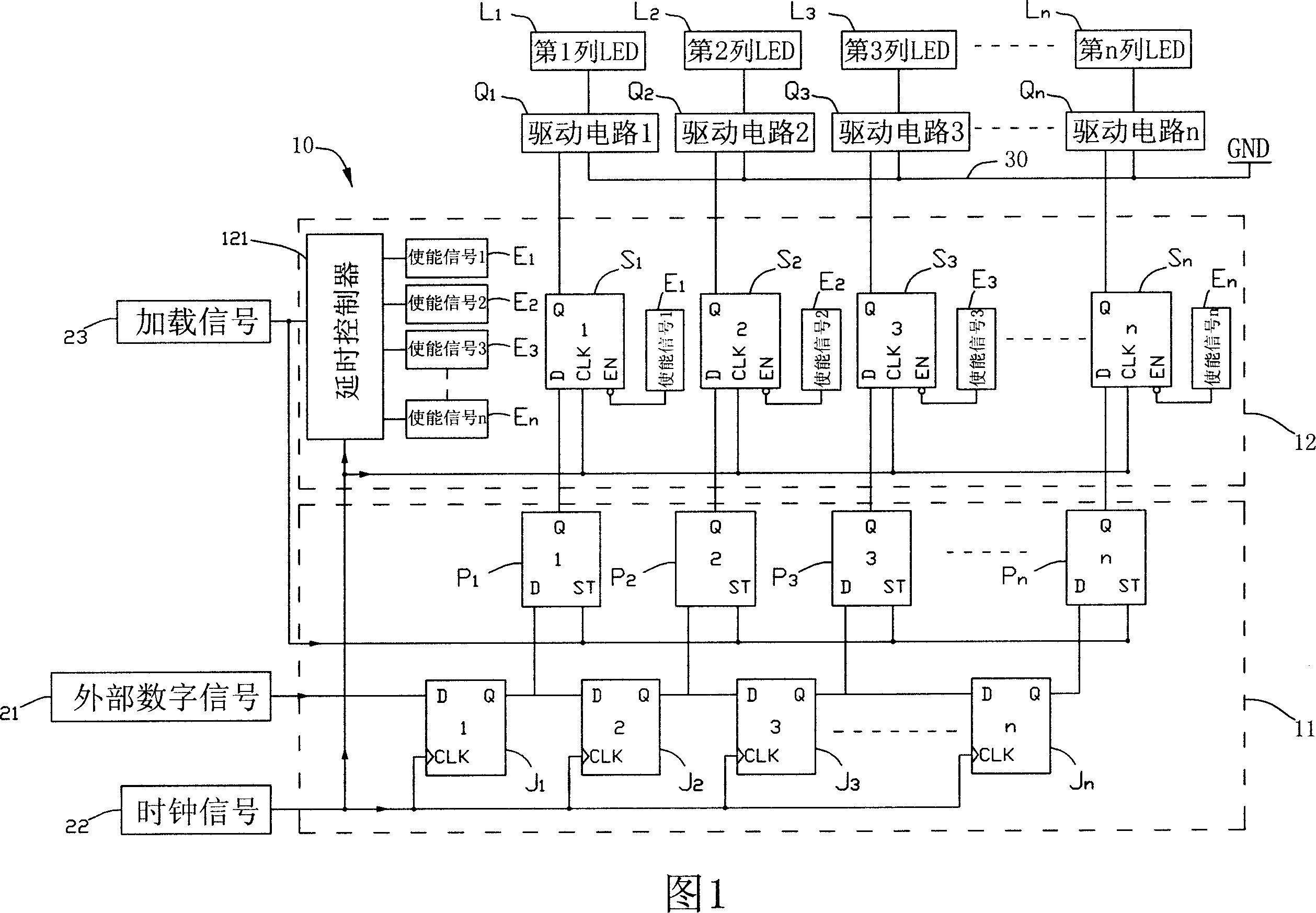

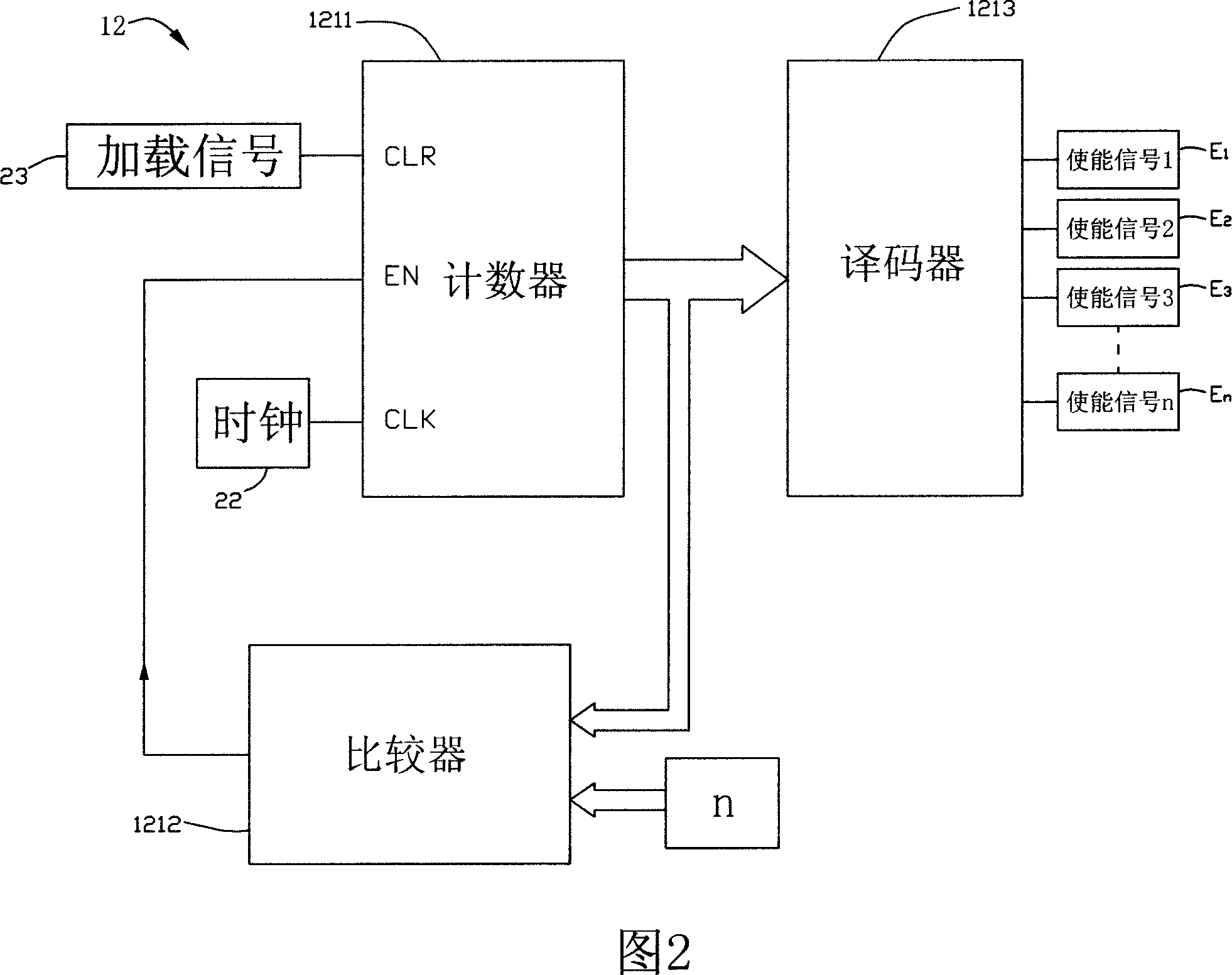

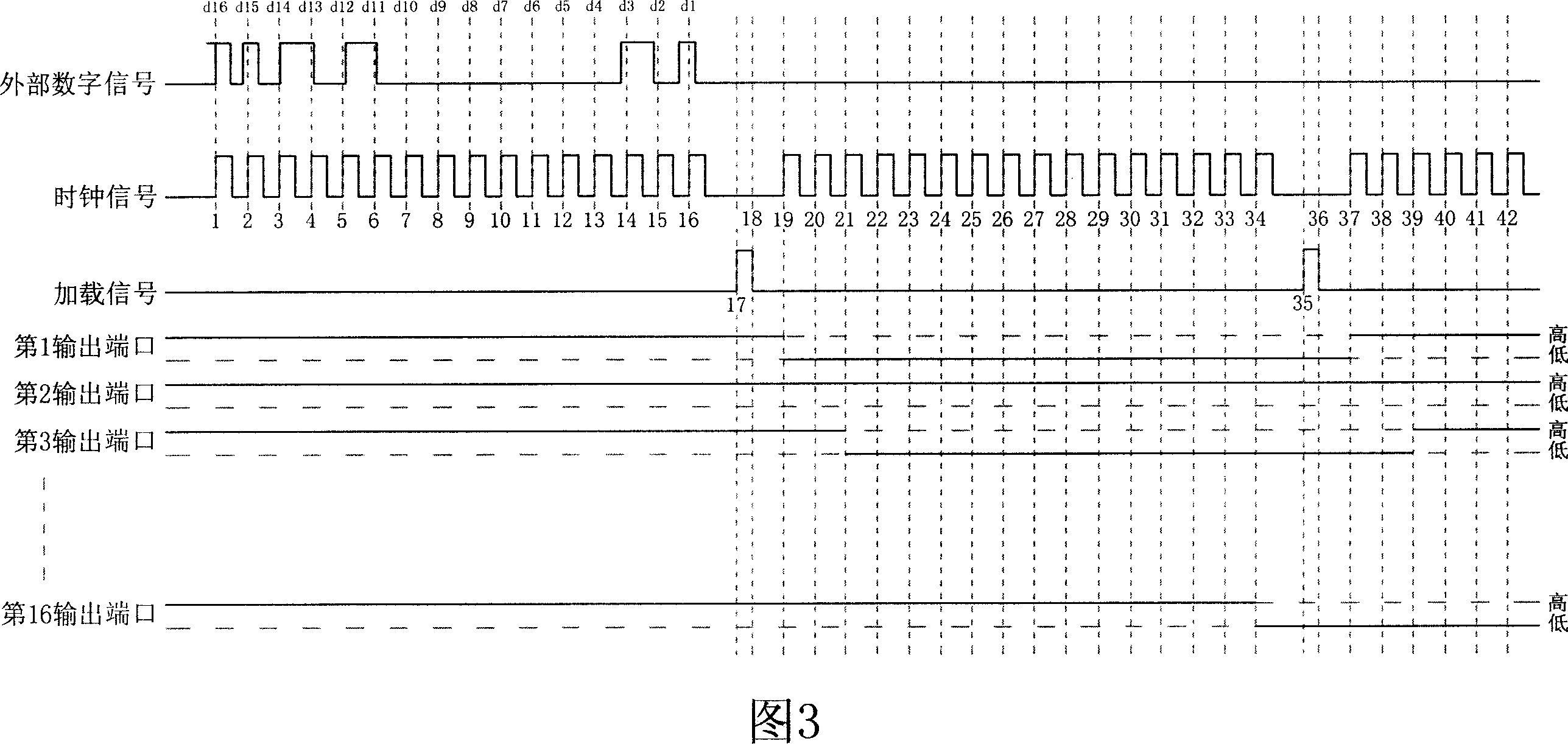

Driving control system for overturn row-by-row and its method and LED display screen

ActiveCN1963906AReduce the magnitude of instantaneous change in currentGuaranteed to workStatic indicating devicesElectroluminescent light sourcesCycle controlLED display

Owner:深圳市中庆微科技开发有限公司

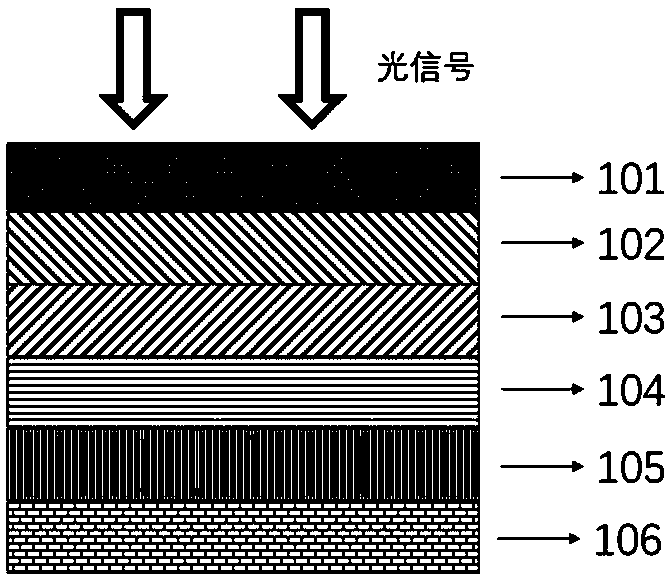

High-performance perovskite/organic semiconductor heterojunction type photoelectric detector

InactiveCN108365099AInhibition effectImprove photoelectric responseSolid-state devicesSemiconductor/solid-state device manufacturingHeterojunctionPhotovoltaic detectors

The invention relates to a high-performance perovskite / organic semiconductor heterojunction type photoelectric detector, and belongs to the technical field of semiconductor photoelectric devices. Thephotoelectric detector prepared via a lamination technology structurally comprises a transparent bottom electrode layer, an organic semiconductor and perovskite function layer and a top electrode layer successively from bottom to top; the organic semiconductor and perovskite function layer includes a cavity type organic semiconductor, perovskite and another cavity type organic semiconductor, or anelectronic type organic semiconductor, perovskite and another electronic organic semiconductor successively from bottom to to; the perovskite and organic semiconductor layer form two heterojunctions;and the top electrode is made of gold or silver. The photoelectric detector is wide in response spectrum and simple in structure, can make response to visible spectrums in full waveband, and has a voltage saturation characteristic, the working voltage is 0.7V, and influence of voltage noise on performance of the detector can be inhibited effectively.

Owner:FUDAN UNIV

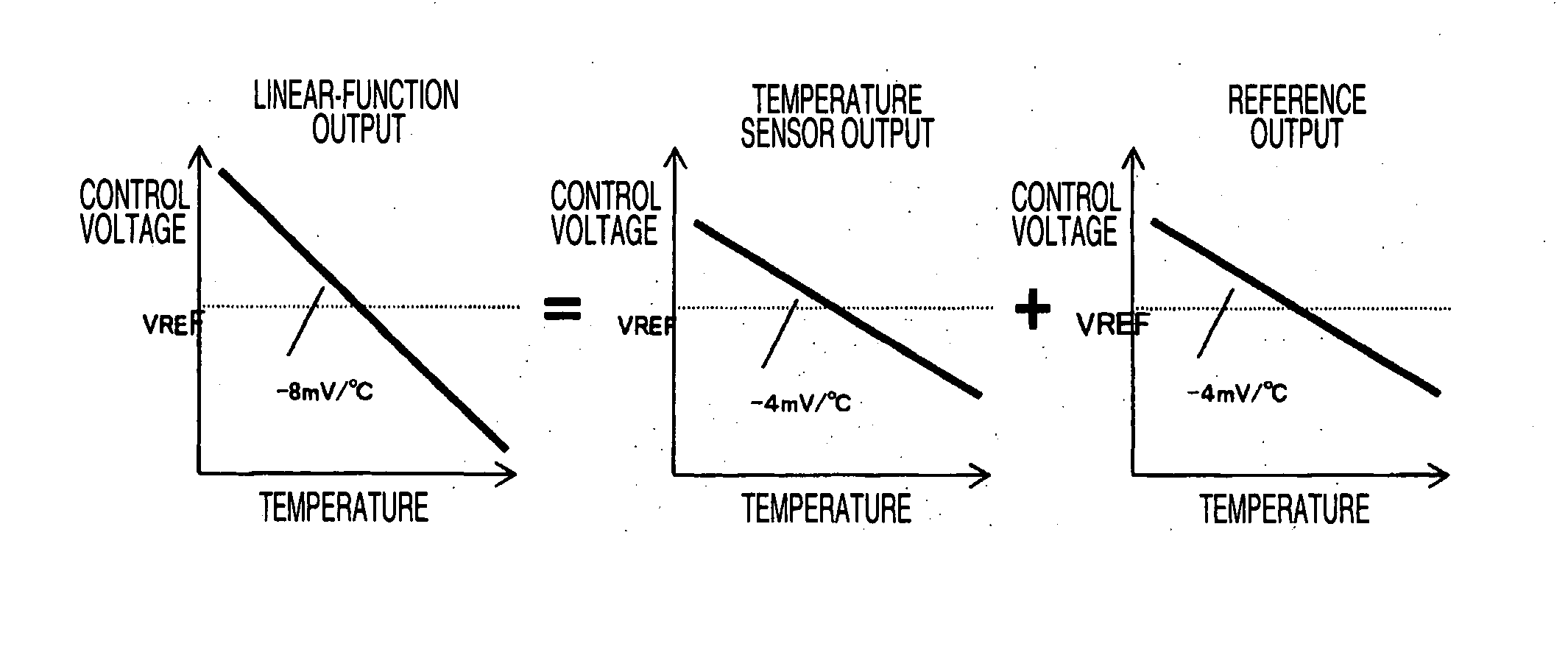

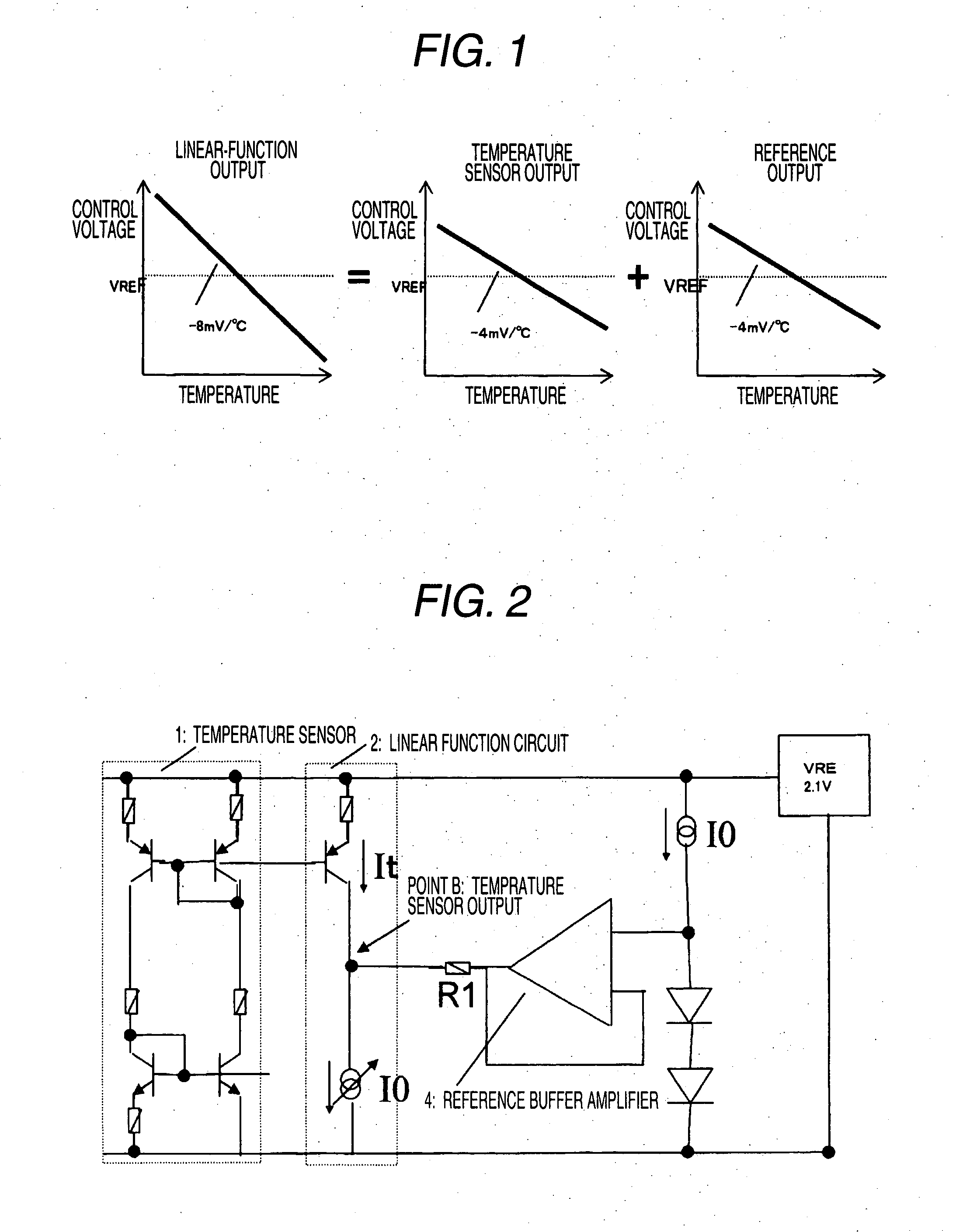

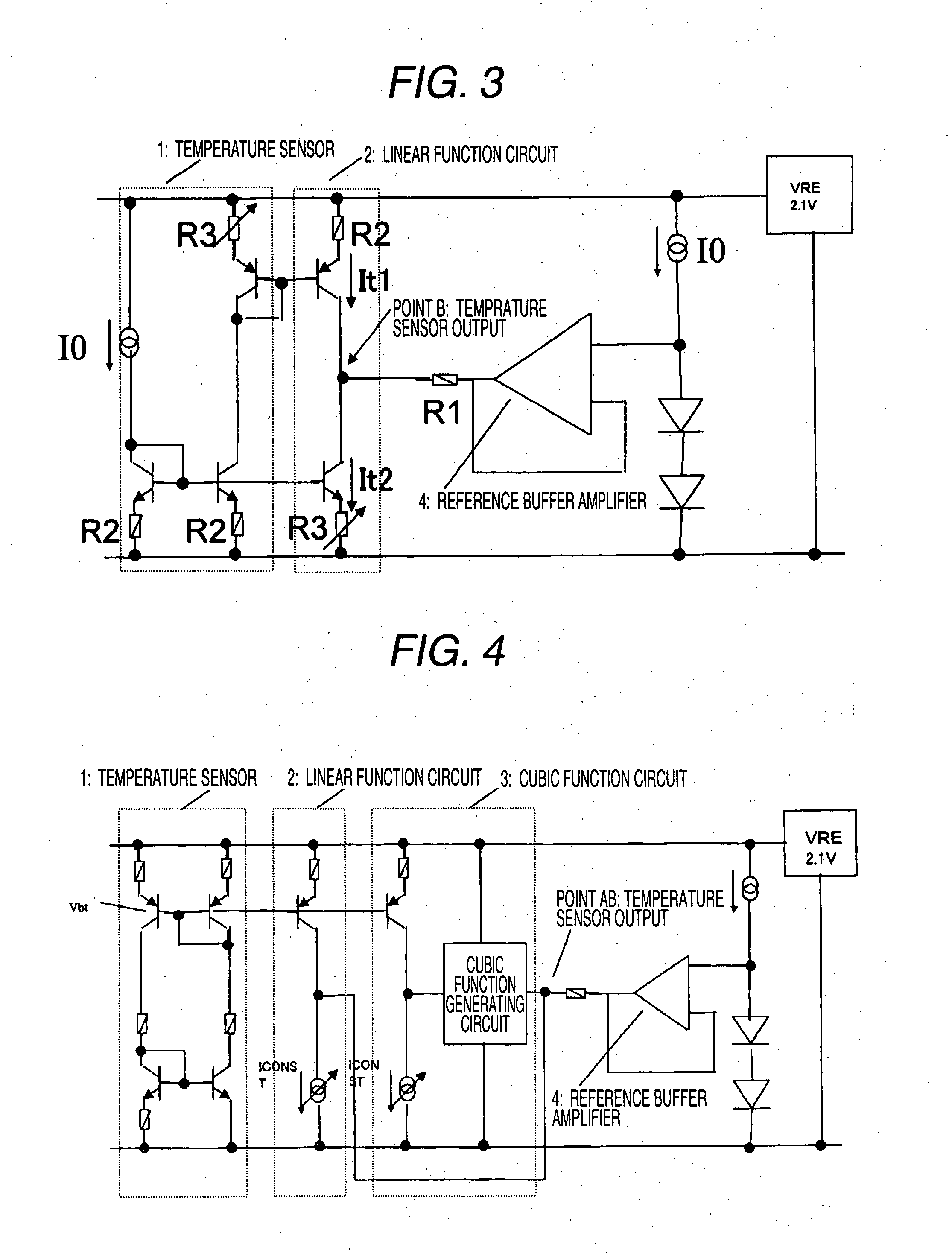

Temperature-compensated crystal oscillator

InactiveUS20070222532A1Reduce noiseReduce vibration noiseGenerator stabilizationOscillations generatorsAudio power amplifierVoltage reference

There is provided a temperature-compensated crystal oscillator for reducing a voltage noise of a cubic function control voltage controlling an output frequency of an oscillation circuit.A temperature-compensated crystal oscillator includes a quartz vibrator, an amplifier having an oscillation frequency controller, and a temperature compensation circuit of a crystal oscillation frequency, wherein a reference voltage for a compensation voltage of the temperature compensation circuit is generated using a forward voltage of a diode.

Owner:PANASONIC CORP

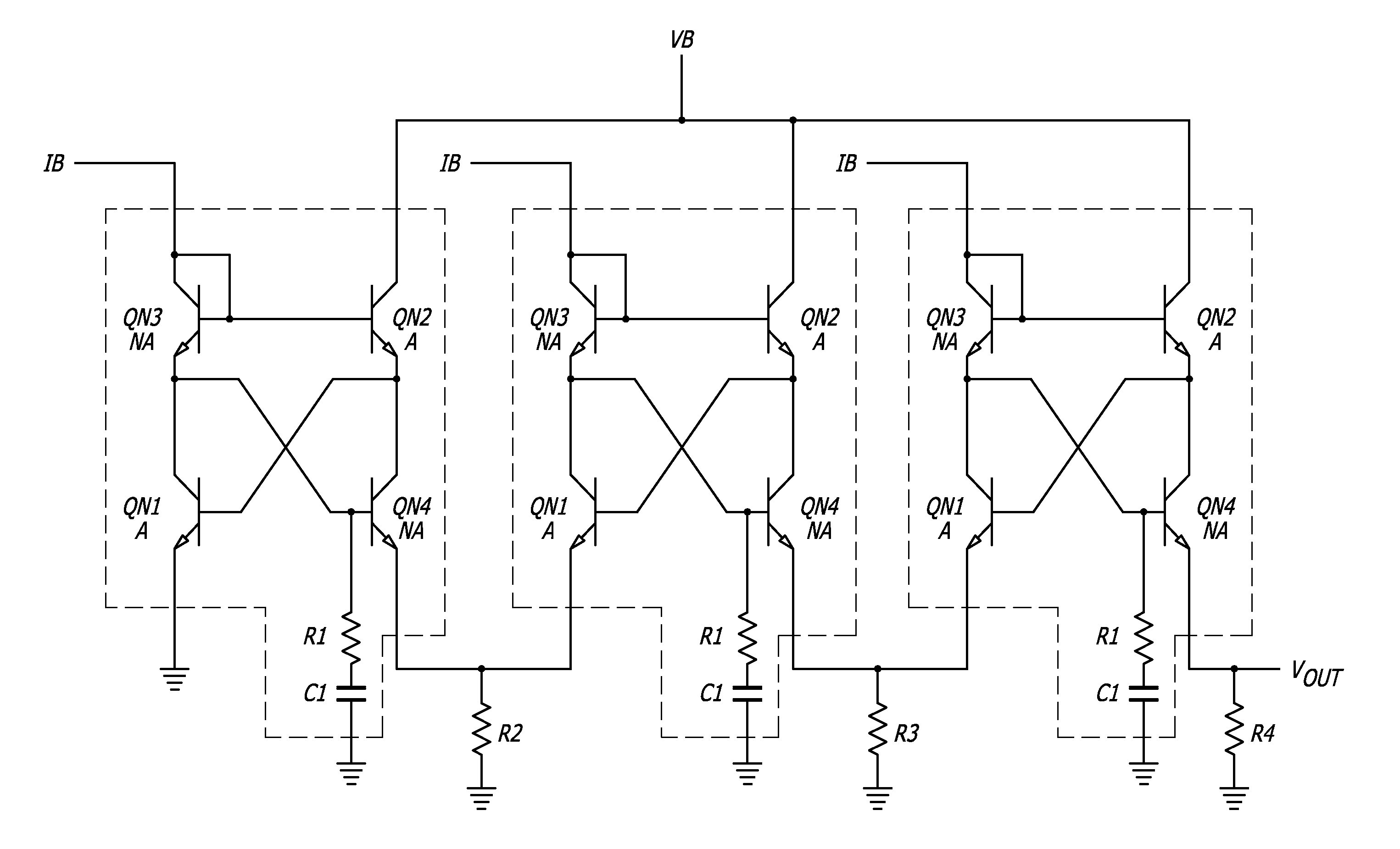

Low Noise Bandgap References

ActiveUS20110241646A1Computing operations for integral formationComputing operations for integration/differentiationLow noisePower flow

Low noise bandgap voltage references using a cascaded sum of bipolar transistor cross coupled loops. These loops are designed to provide the total PTAT voltage necessary for one and two bandgap voltage references. The PTAT voltage noise is the square root of the sum of the squares of the noise voltage of each transistor in the loops. The total noise of the reference can be much lower than approaches using two or 4 bipolar devices to get a PTAT voltage and then gaining this PTAT voltage to the required total PTAT voltage. The cross coupled loops also reject noise in the current that bias them. Alternate embodiments are disclosed.

Owner:MAXIM INTEGRATED PROD INC

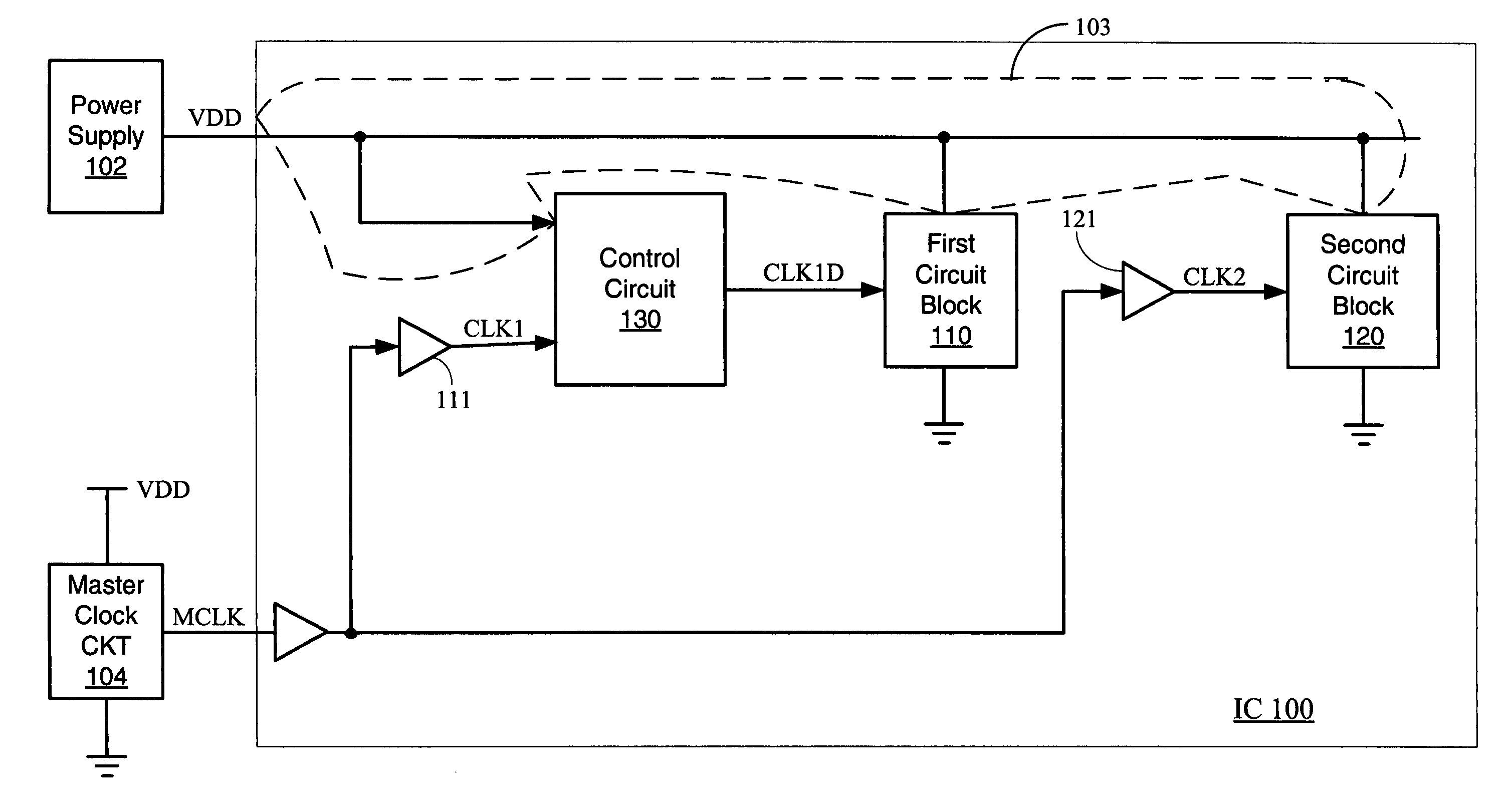

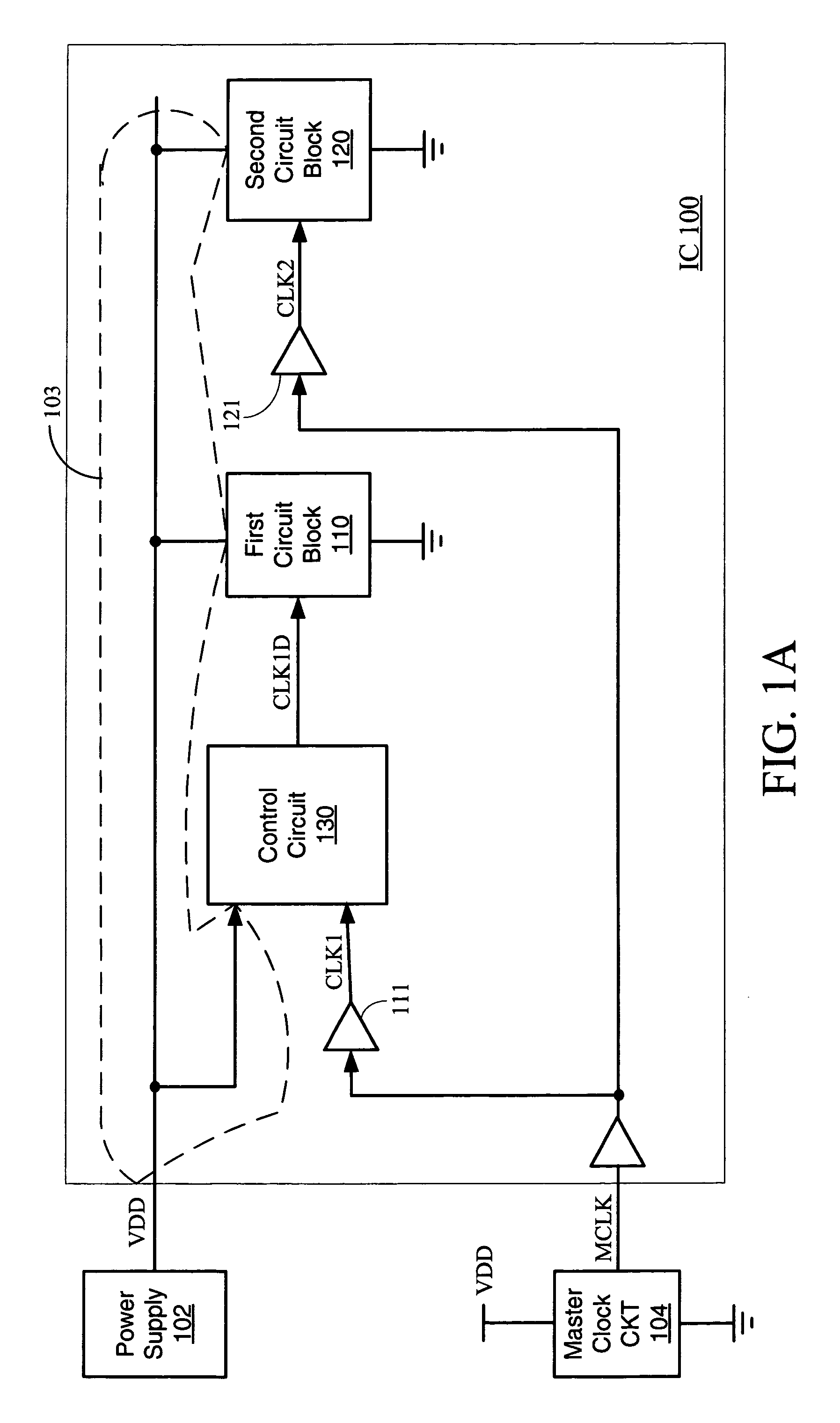

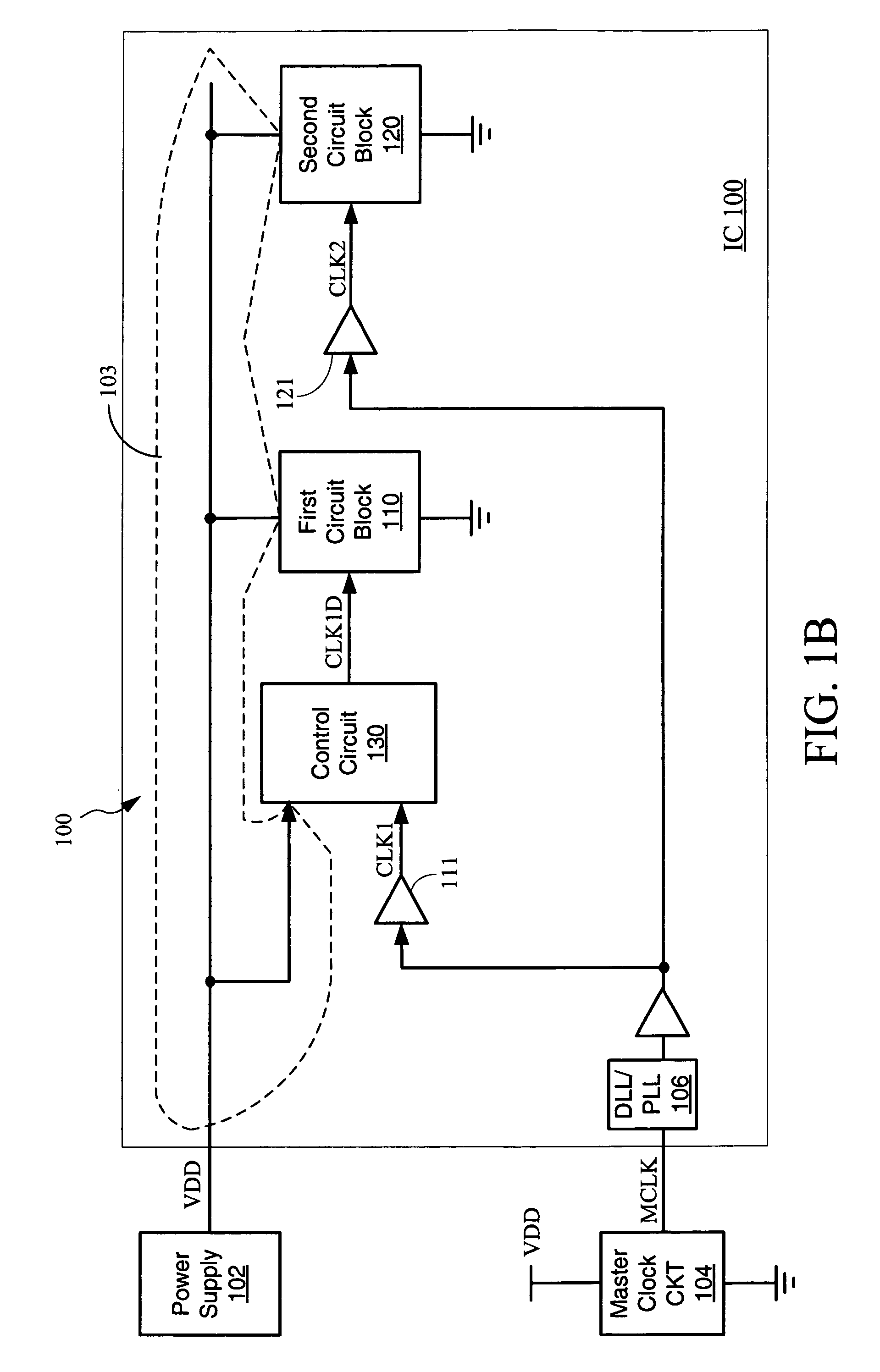

Clock auto-phasing for reduced jitter

ActiveUS8258845B1Reduce clock jitterMinimize clock jitterPower supply for data processingElectric pulse generatorPhase shiftedControl circuit

The relative timing of triggering switching events in a circuit block of an IC device is dynamically adjusted in response to fluctuations in device's supply voltage to minimize clock jitter caused by supply voltage noise. A control circuit monitors supply voltage fluctuations, and in response thereto dynamically phase-shifts a clock signal that triggers the switching events so that the switching events occur during relatively quiet time intervals in which fluctuations in the supply voltage are minimal.

Owner:XILINX INC