Semiconductor integrated circuit compensating jitter and jitter compensation method

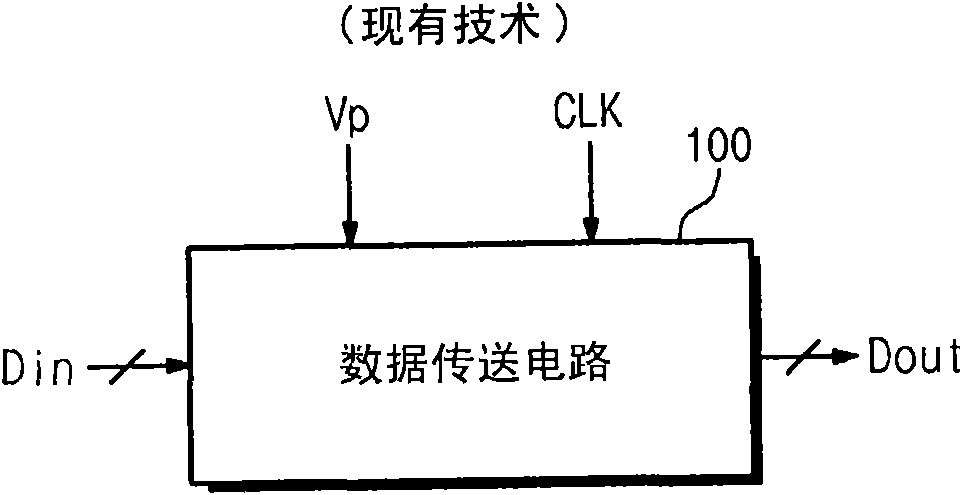

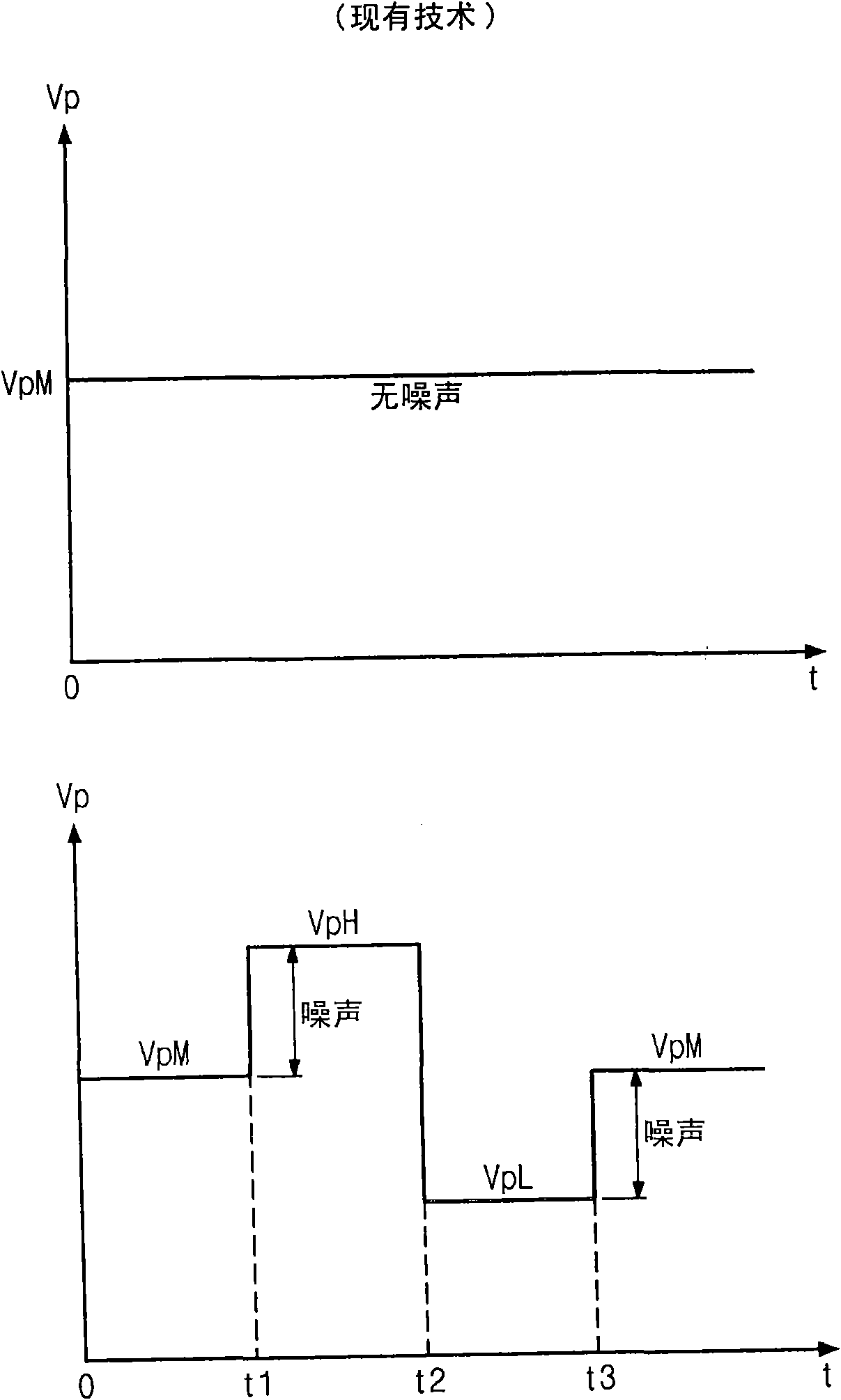

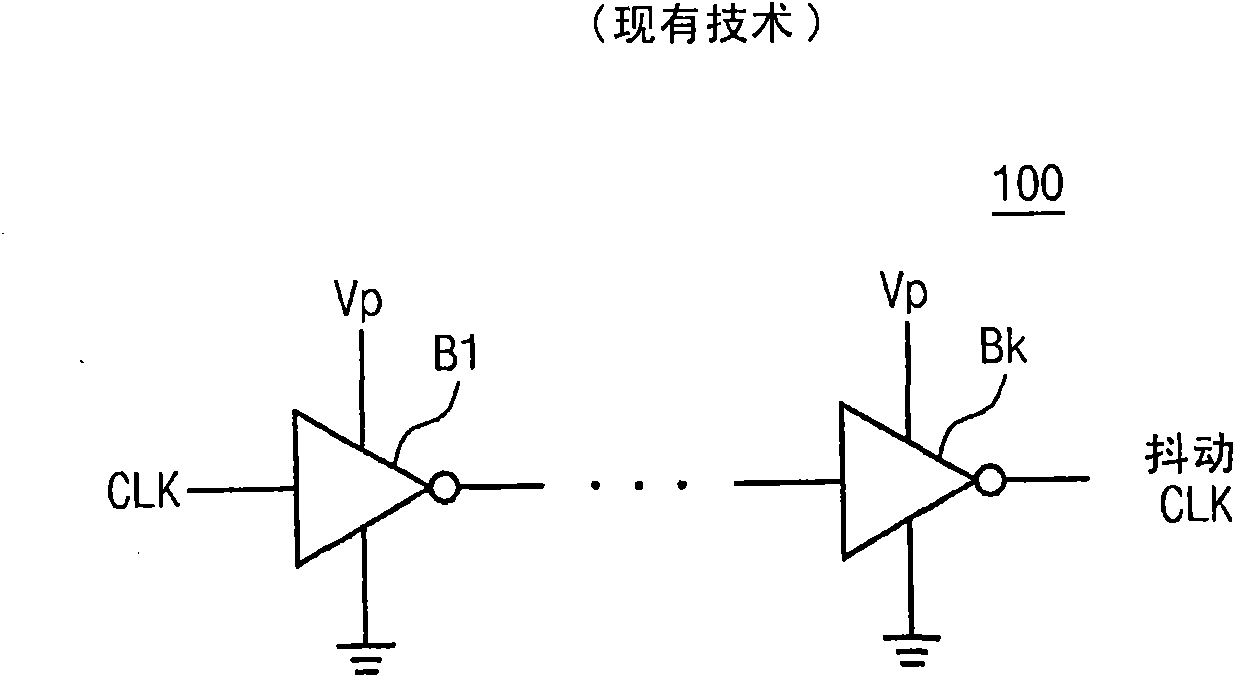

A data transmission and circuit technology, applied in electrical components, digital memory information, static memory, etc., can solve problems such as uneven clock cycle, wrong output data, wrong input data gating operation, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] Reference will now be made to specific embodiments of the inventive concepts illustrated in the accompanying drawings. Throughout the drawings and written description, the same reference numbers and labels are used to refer to the same or similar elements, signals and features.

[0042] It should be noted that the inventive concept can be embodied in many different ways. Accordingly, the inventive concept should not be construed as limited to the illustrated embodiments. Rather, these embodiments are presented as illustrative examples only.

[0043] Those skilled in the art will appreciate that recitation terms (eg, first, second, etc.) are only used to distinguish different elements. These terms should not define a certain numerical limitation for such elements.

[0044] As used herein, the term "and / or" includes any and all combinations of one or more of the associated listed items. It will also be understood that when an element is referred to as being "connected...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More