Semiconductor device and fabrication method thereof

A semiconductor and device technology, applied in the field of semiconductor devices and their manufacturing process, can solve the problem of increased hole mobility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

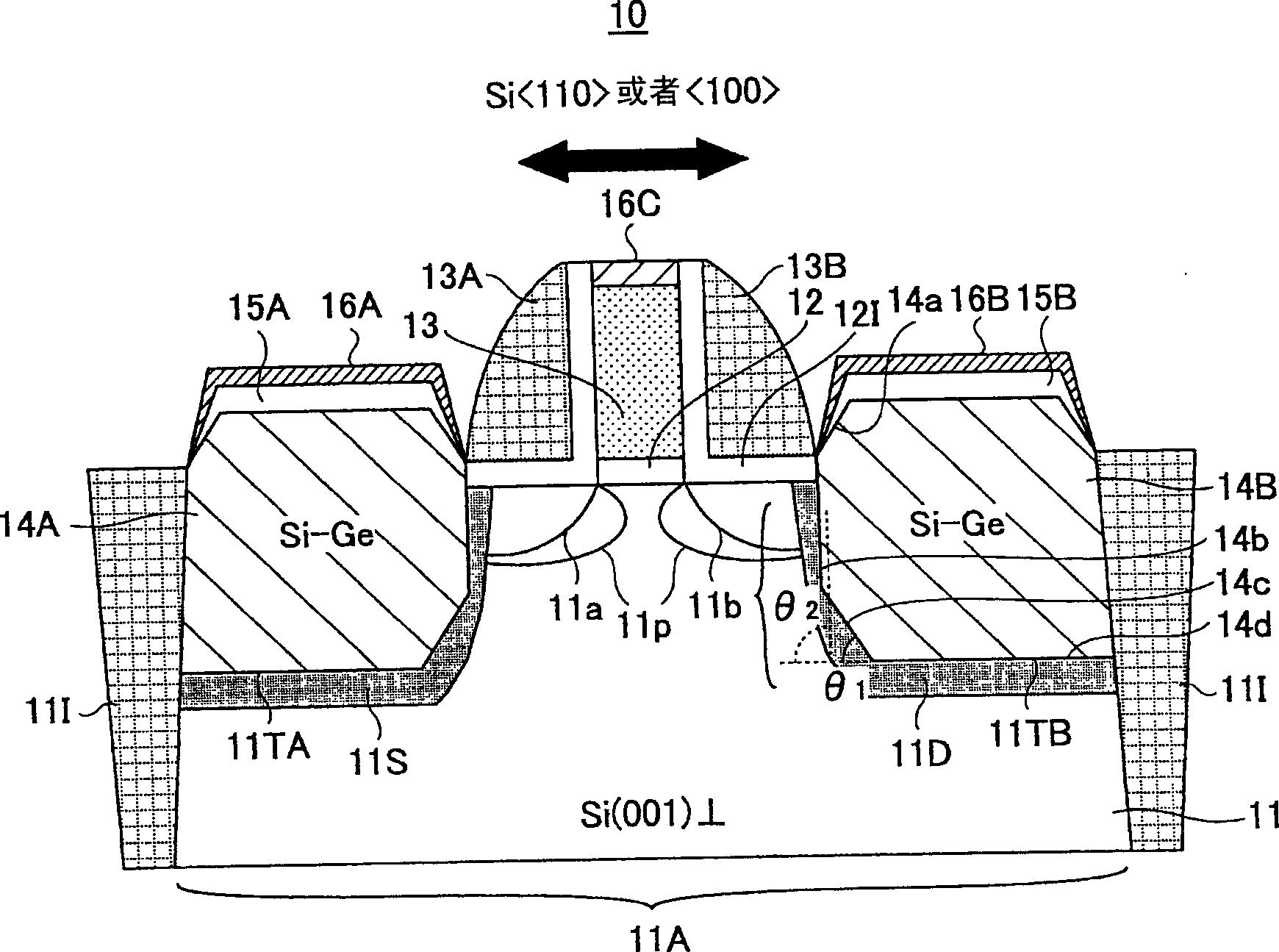

[0081] image 3 The structure of the P-channel MOS transistor 10 according to the first embodiment of the present invention is shown.

[0082] refer to image 3 , the P-channel MOS transistor 10 is formed on the n-type device region 11A defined by the STI device isolation region 11I on the silicon substrate in the (001) plane direction, wherein the high-quality gate insulating film of a thermal oxide film or a SiON film 12 is formed on the silicon substrate 11 corresponding to the channel region in the device region 11A, and has a thickness of about 1.2 nm.

[0083] In the above-mentioned device region 11A, a p-type doped polysilicon gate electrode 13 is formed on the gate insulating film 11 , wherein the silicon substrate surface exposed at lateral sides of the gate electrode 13 is covered by a CVD oxide film 12I. Therefore, it should be noted that each CVD oxide film 12I extends continuously, and covers the side wall surface of gate electrode 13 . Further, sidewall insula...

no. 2 example

[0118] will later refer to Figure 8A to Figure 8E explained Figure 4D The fabrication process of p-channel MOS transistors.

[0119] refer to Figure 8A , the device region 11A is defined on the surface of the p-type silicon substrate 11 by the STI-type device isolation structure 11I, and an n-type well is formed in the device region 11A by implanting n-type impurity elements into the device region 11A.

[0120] and, in Figure 8B In the step of , since the SiON film and polysilicon film patterned uniformly formed on the silicon substrate 11, a gate insulating film 12 and a polysilicon gate electrode 13 are formed on the silicon substrate 11 corresponding to the device region 11A, and by implanting p Type impurity elements such as B + , while using the polysilicon gate electrode 13 as a mask, a p-type source extension region 11a and a p-type drain extension region 11b are formed in the device region 11A.

[0121] In addition, after the sidewall insulating films 13A and ...

no. 3 example

[0148] Figure 10A is an illustration of performing the process of FIG. 8D in a low-pressure CVD apparatus as a third embodiment of the present invention, summarizing the above-explained.

[0149] refer to Figure 10A , first, the substrate to be processed is introduced into a low-pressure CVD apparatus at a temperature of 400° C. or lower, and the temperature is raised to a predetermined processing temperature of 400-550° C. in a hydrogen atmosphere (heating).

[0150] Subsequently, in the same hydrogen atmosphere, at the same processing temperature, the substrate to be processed is kept for a maximum of 5 minutes, and a hydrogen heat treatment process (H 2 - baking).

[0151] Next, at the same process temperature, the process gas introduced into the low-pressure CVD apparatus was changed, and as described above, epitaxial growth (SiGe deposition) of p-type SiGe mixed crystal regions 14A and 14B was performed in trenches 11TA and 11TB .

[0152] and, in Figure 10A In th...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More