Automatic fault-testing of logic blocks using internal at-speed logic-bist

A logic module and logic technology, applied in the field of automatic real-speed fault testing, can solve the problems of ATE interface not allowed, not testing digital logic macro interface, connection failure not being detected, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0011] In the following description, numerous specific details are set forth in order to provide a thorough understanding of the present invention. It will be understood, however, to one skilled in the art that the present invention may be practiced without some or all of these specific details. In other instances, well-known hardware designs, operations and testing procedures have not been described in detail so as not to obscure the present invention.

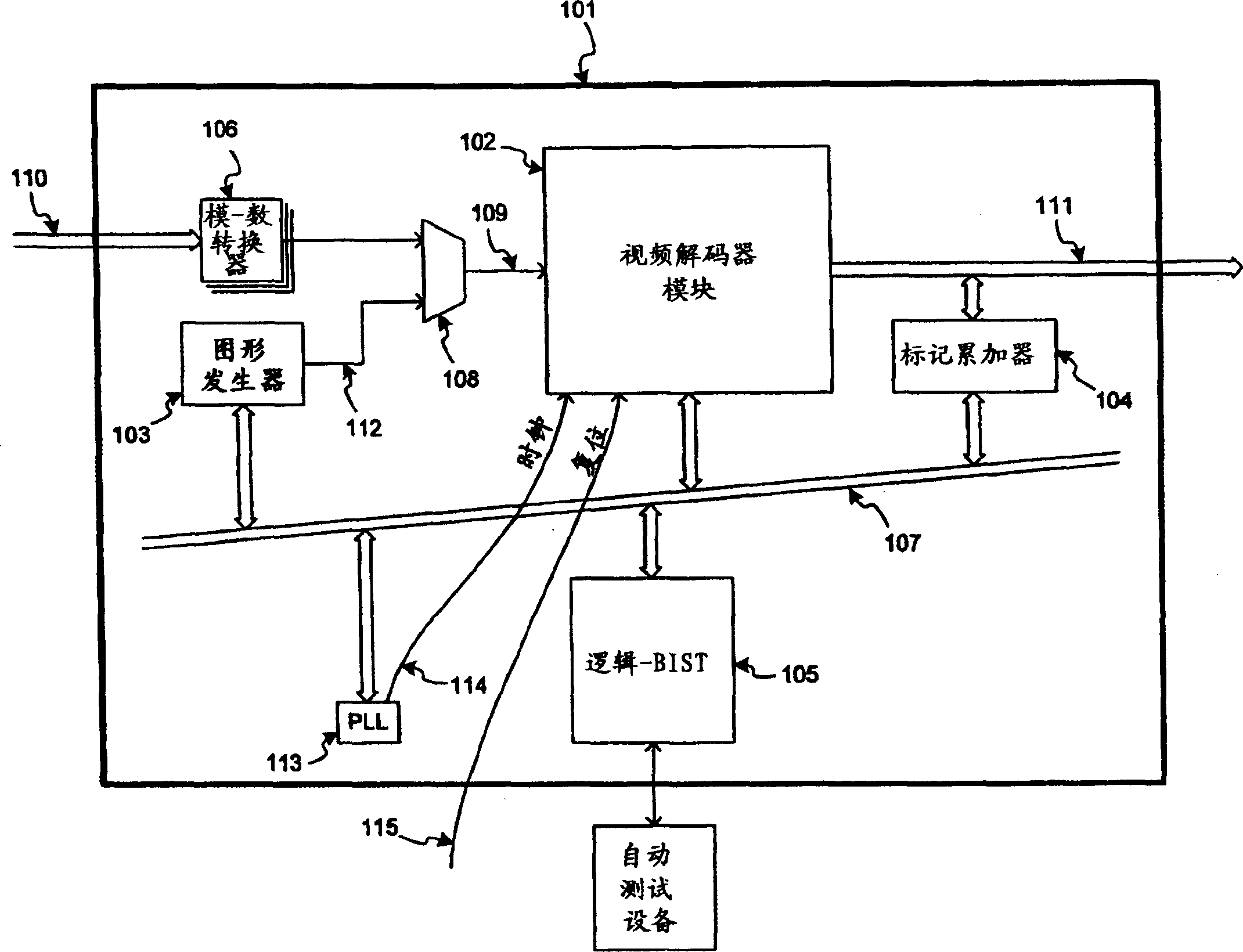

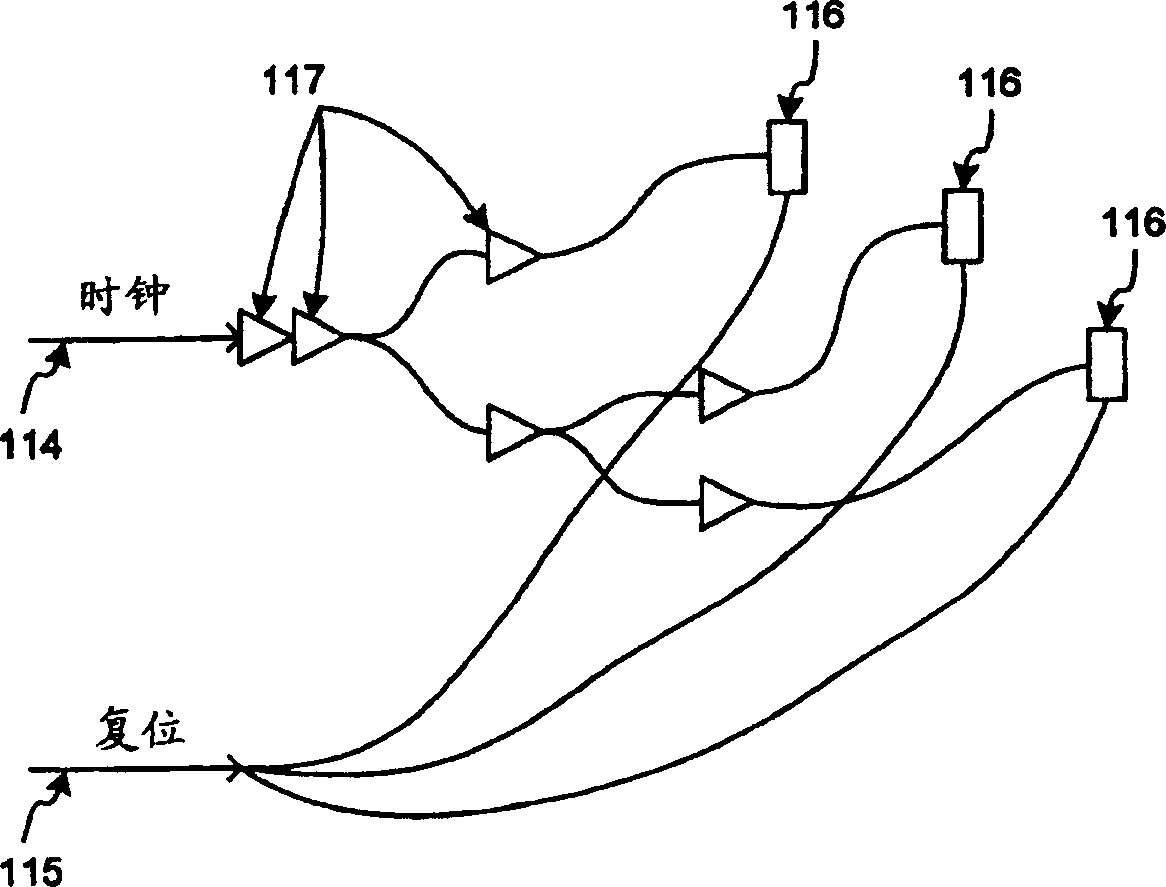

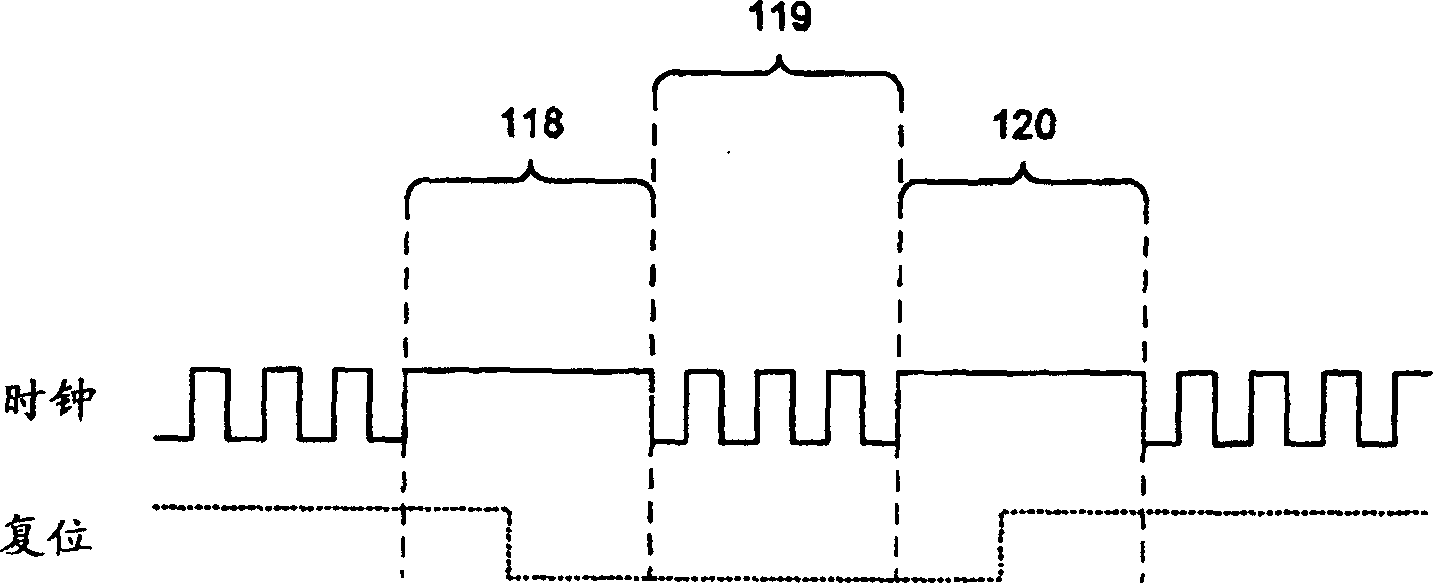

[0012] Accordingly, what is provided is a system and method for automatic failure testing of logic and interfaces of a semiconductor device (chip) using a real-speed logic-BIST (built-in self-test) circuit built into the chip. The invention allows testing to be performed on the ATE using simple test vectors. It also allows field engineers to perform system-level tests on actual panels, regardless of the impact on chip functionality. The ATE vector is simple because it only needs to trigger the logic-BIST circuit and does no...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com