Multiple-CPU system and its control method

A control method and control logic technology, applied in the fields of electronic equipment and communication, can solve the problems of poor system reliability, inability to control the main CPU, and inability to communicate with the CPU, achieving reliable performance, saving design and programming time, and strong anti-interference performance. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

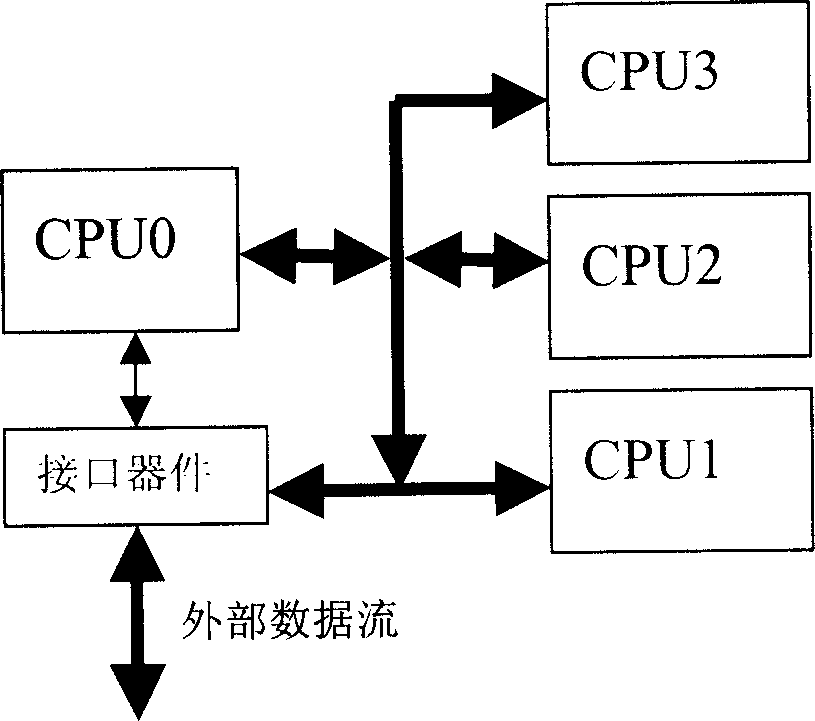

[0048] refer to Figure 4 , Figure 4 It is the functional block diagram of the first embodiment of the system of the present invention:

[0049] The control logic unit S11 is respectively connected with the main processor CPU0 and each slave processor, and is used to reset each slave processor according to the command of the main processor CPU0;

[0050] The watchdog and the reset circuit S12 are respectively connected with the main processor CPU0 and the control logic unit S11, and are used to reset the main processor CPU0 and each slave processor, and the reset of each slave processor is completed through the control logic unit S11 The specific operation is to execute the reset operation on each slave CPU according to the reset signal provided by the watchdog and reset circuit S12.

[0051] The main processor CPU0 communicates with the control logic unit S11 through the MPI (microprocessor interface) interface, and completes the management operation of the running status ...

no. 2 example

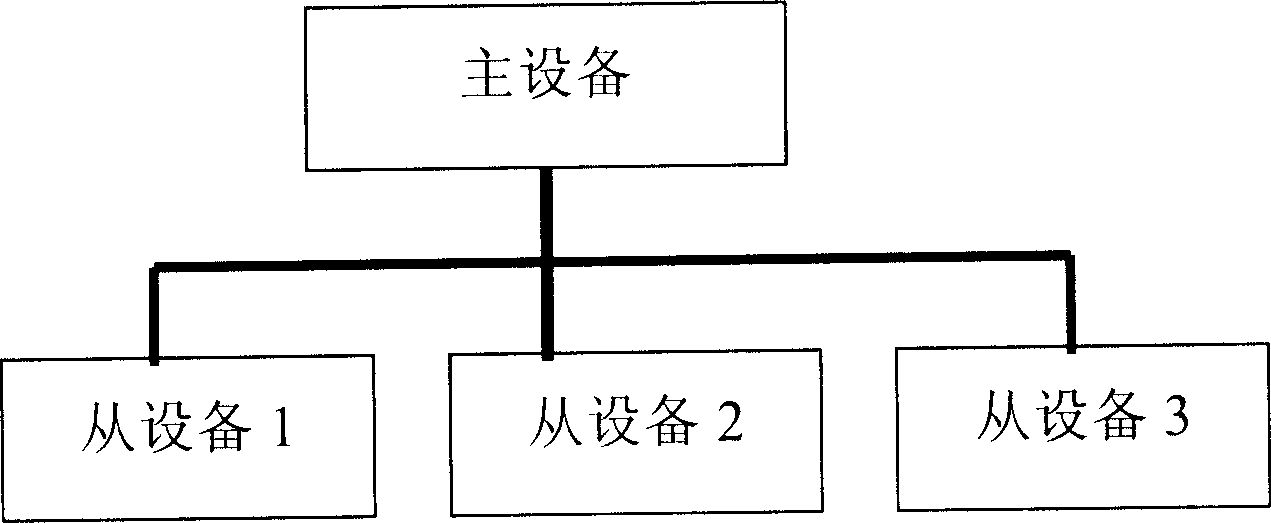

[0061] refer to Figure 5 , Figure 5 It is the functional block diagram of the second embodiment of the system of the present invention:

[0062] The communication logic unit S21 is respectively connected with the main processor CPU0 and each slave processor, and is used to control the working state of each slave CPU according to the command of the main processor CPU0. The watchdog and reset circuit S12 is respectively connected with the main processor CPU0 and each slave processor. The processors are connected to reset the main processor CPU0 and each slave processor separately, that is, the reset signals between the processors are independent.

[0063] The main processor CPU0 communicates with the communication logic unit S21 through the MPI interface to complete the management operation of the running status of each slave processor. Similarly, the communication between the communication logic unit S21 and each slave processor is also performed through the MPI interface. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More