Methods and systems for improving microelectronic

A technology for packaging components and semiconductors, which is applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., and can solve problems such as not meeting the current demand

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

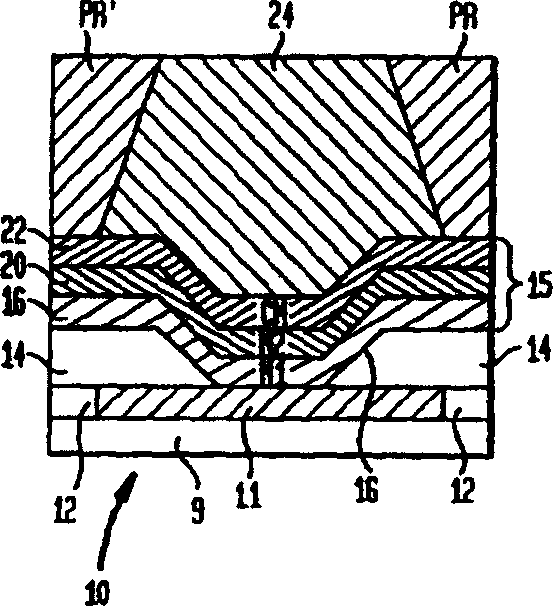

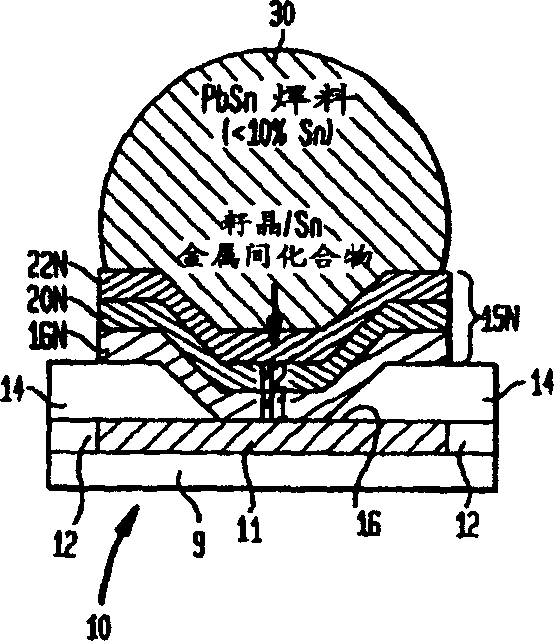

[0026] figure 1 with 2 Description is used to form one or more C4 solder bumps 24 above the metal contact 11 formed on the semiconductor device 10 on the formed conformal seed layer 15 and form one or more C4 solder balls 30 therefrom. There are technical processes. The seed layer 15 is composed of at least one bottom layer of a metal bonding layer 16. Such as figure 1 with 2 As shown, the device 10 includes a bottom layer of two metal layers 16 and 20. In order to complete the seed stack, the metal bottom layers 16 and 20 are covered by a conductive metal (CM) layer 22 composed of copper (Cu). A part of the semiconductor device 10 is shown to illustrate an example of a C4 bump formation process sequence in which the seed stack 15 is used during processing. As will be explained below, after processing, only a part of the copper originally included in the CM layer 22 remains in the CM layer 22N as figure 2 Part of the seed layer 15 of the middle layers 16N, 20N, and 22N.

[0027...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More