Adding-up apparatus and digital circuit unit of its direct digit frequency synthesizing apparatus

A technology of digital circuits and adding units, applied in the field of direct digital frequency synthesis, can solve problems such as the number of bits and operating frequency limitations, and achieve the effect of improving accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

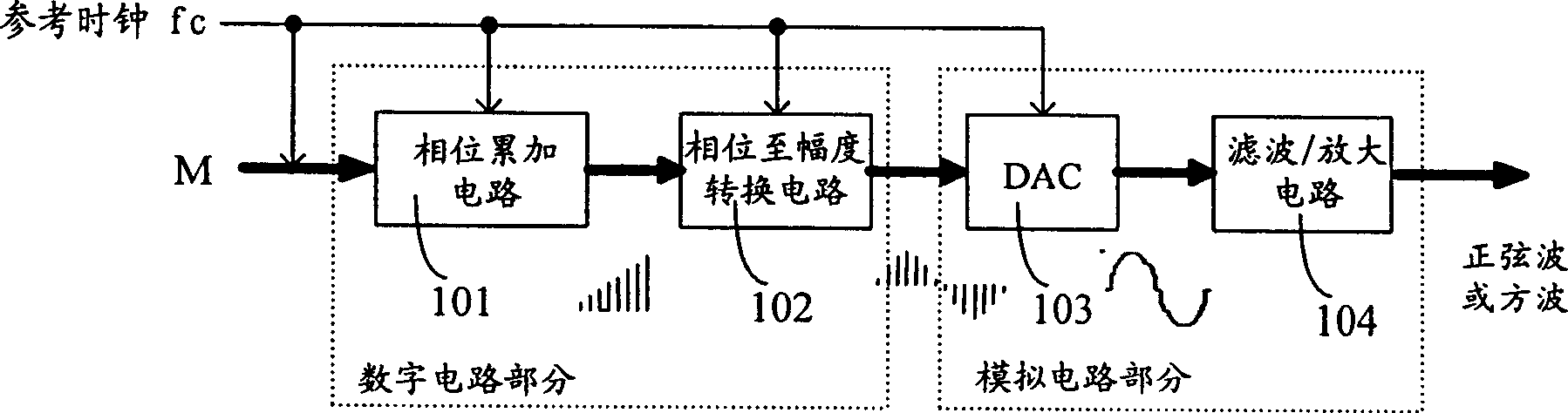

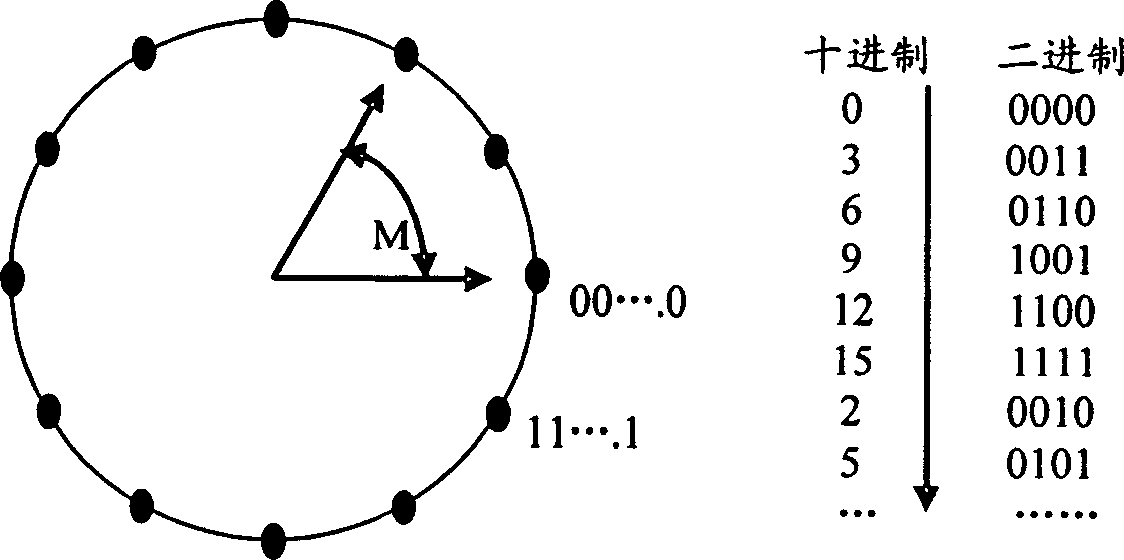

AI Technical Summary

Problems solved by technology

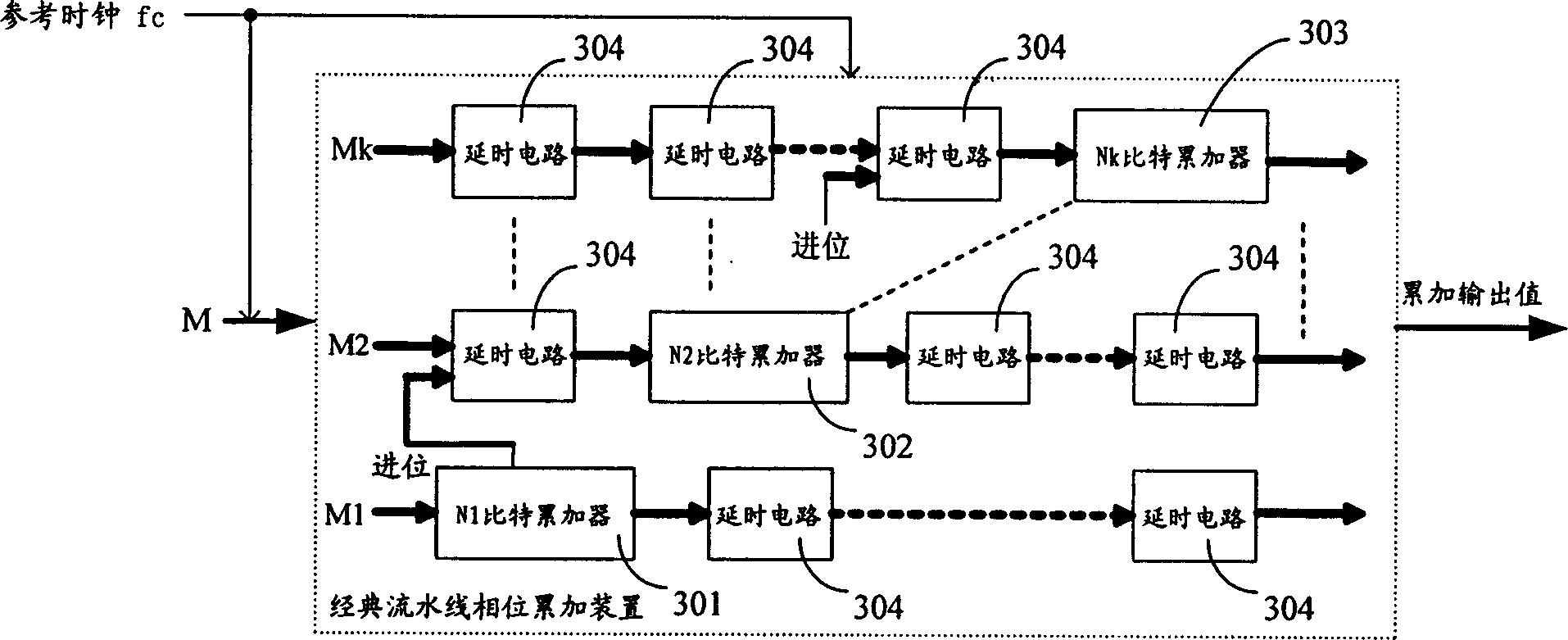

Method used

Image

Examples

Embodiment 1

[0064] Embodiment 1: frequency reduction accumulating device.

[0065] See Figure 5 , Figure 5 It is a schematic diagram of the down-frequency accumulating device in Embodiment 1 of the present invention. Figure 5The frequency reduction and accumulation device shown includes an increment multiplier unit 501 , an accumulator 502 , a delay circuit 503 , and an addition unit 504 . Wherein, the increment multiplier unit 501 includes k-1 multipliers and one M transmission line. Coefficients of the k-1 multipliers are 2, 3, 4...k respectively, and k is a natural number greater than 1. The multiplier and the M transmission line respectively receive the input delta M. Among them, the multiplier whose coefficient is less than or equal to k-1 multiplies the increment M and the coefficient, and generates the multiple value of the increment respectively: M×2, M×3..., M×(K-1) are respectively output to the addition unit 504 . The multiplier with a coefficient equal to k multiplies...

Embodiment 2

[0080] Embodiment 2: The output of the accumulation device is directly input to the digital circuit part of the high-speed DDS device of the phase-to-amplitude conversion circuit.

[0081] See Figure 6 , Figure 6 It is a partial schematic diagram of the digital circuit of the high-speed DDS device in Embodiment 2 of the present invention, which includes a down-frequency phase accumulation circuit 601 and a phase-to-amplitude conversion unit 602 . Down-frequency phase accumulation circuit 601 such as Figure 5 The accumulating device shown in the figure receives a phase increment M with a frequency of fc, and outputs a set of k-channels of phase data every k / fc time: P1, P2, ..., Pk.

[0082] The phase-to-amplitude conversion unit 602 includes k phase-to-amplitude conversion circuits 603, and each phase-to-amplitude conversion circuit 603 receives one of the k output phase data P1, P2, ..., Pk of the down-frequency accumulation circuit 601. Convert it in k / fc time. The ph...

Embodiment 3

[0084] Embodiment 3: The digital circuit part of a high-speed DDS device including a frequency adjustment circuit.

[0085] See Figure 7 , Figure 7 It is a partial schematic diagram of the digital circuit of the high-speed DDS device in Embodiment 3 of the present invention, which includes a down-frequency phase accumulation circuit 701 , a frequency adjustment circuit 702 , and a phase-to-amplitude conversion unit 703 . Down-frequency phase accumulation circuit 701 such as Figure 5 The accumulating device shown receives a phase increment M with a frequency of fc, and outputs a set of k-channel phase data every k / fc time: P1, P2, ..., Pk.

[0086] The frequency adjustment circuit 702 is arranged between the down-frequency phase accumulating circuit 701 and the phase-to-amplitude conversion unit 703, receives a group of k-channel phase data output by the down-frequency phase accumulating circuit 701, outputs a group of i-channel phase data, and sends them to a The phase-t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More