Amplitude adjusting system for full-duplex multi-level pulse wave and blind activation receiver

A receiver, multi-level technology, applied in the direction of AM carrier system, etc., can solve the problem of complex implementation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

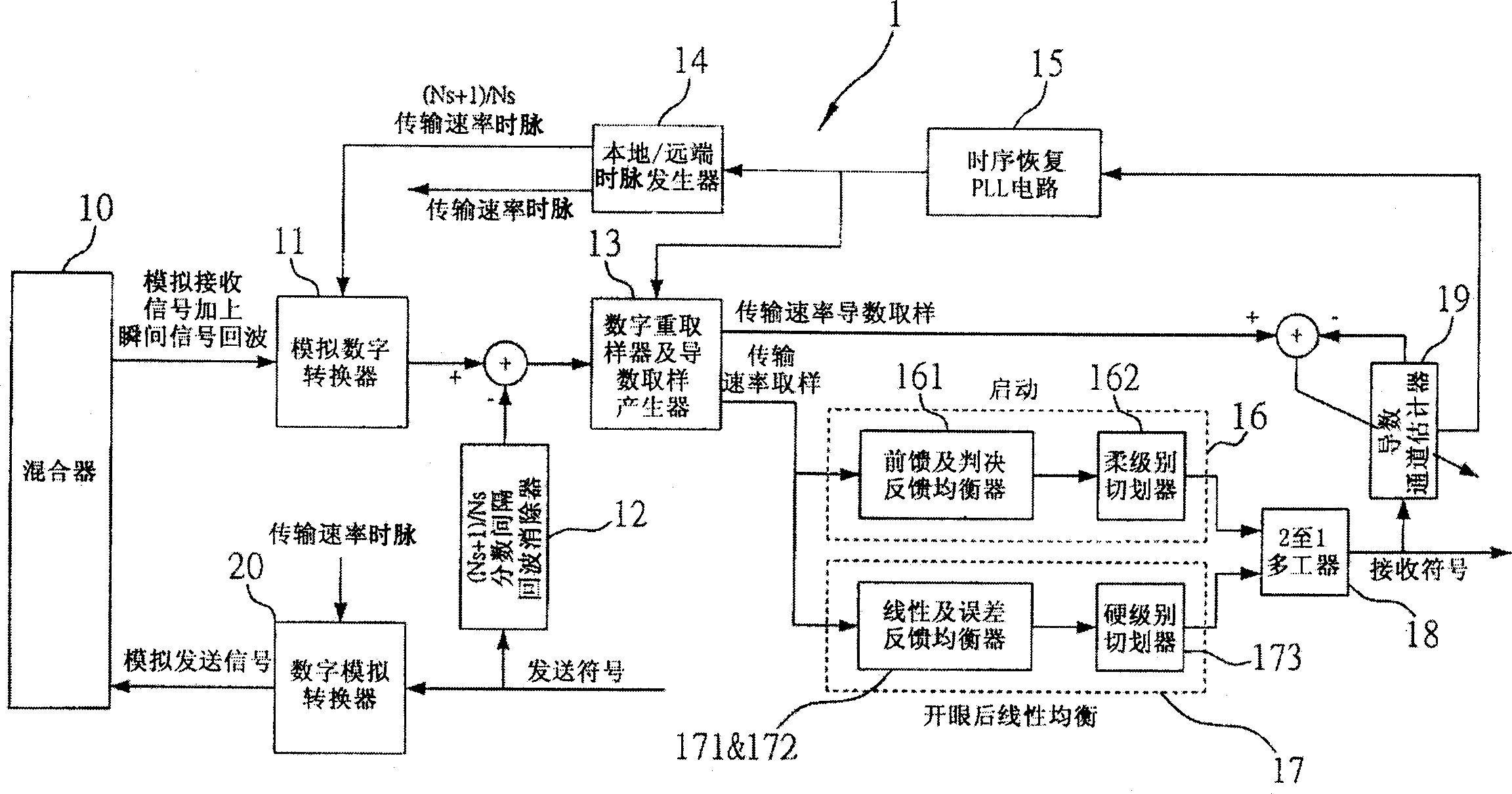

[0024] like figure 1As shown, the receiver structure 1 of the present invention includes a mixer 10, an analog-to-digital converter (ADC) 11, a fractionally spaced echo canceller 12, a digital resampler 13, a local / remote clock generator 14, a timing recovery PLL A circuit 15 , a blind equalization (BEQ) branch 16 , a linear equalization (LEQ) branch 17 and a 2-to-1 multiplexer (Mux) 18 and a derivative inversion estimator 19 .

[0025] The BEQ branch 16 includes a decision feedback equalizer 161 and a soft level slicer 162 , wherein the LEQ branch 17 includes a linear equalizer 171 , an error feedback equalizer 172 , a hard level slicer 173 and an error level hard limiter 174 . See below for descriptions of these two branches.

[0026] The sampling rate of ADC 11 is flexibly set as (N s +1) / N s multiplied by the transfer rate, where N s is an integer equal to or greater than 1. Therefore, when choosing N s When it is 1, the sampling rate is equal to 2 times the transmis...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More