Postponing circuit with high electrical-magnetic compatibility

A technology of electromagnetic compatibility and delay circuit, applied in electrical components, pulse processing, single output arrangement, etc., can solve problems such as weak driving ability, failure of subsequent functional circuits to operate normally, circuit malfunction, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

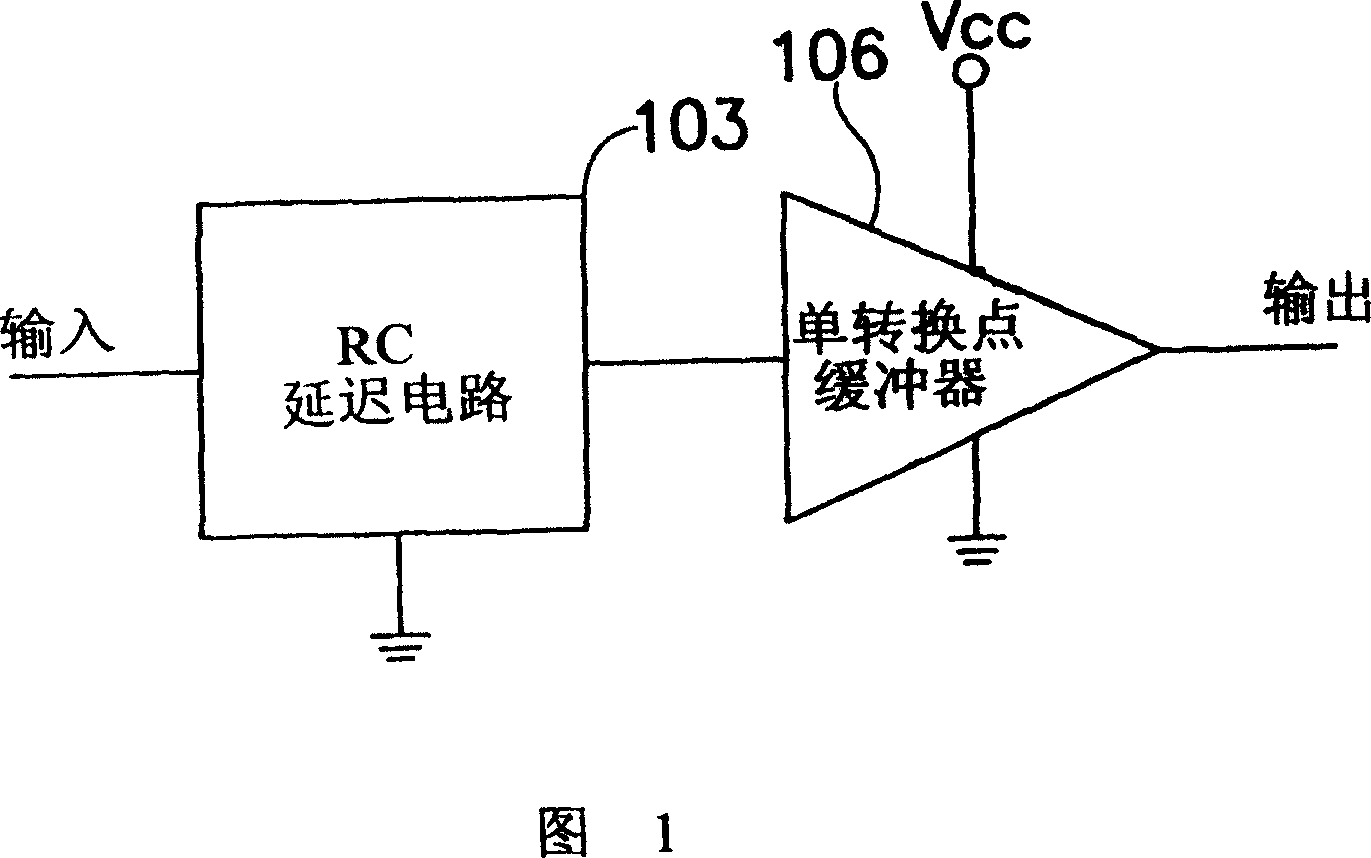

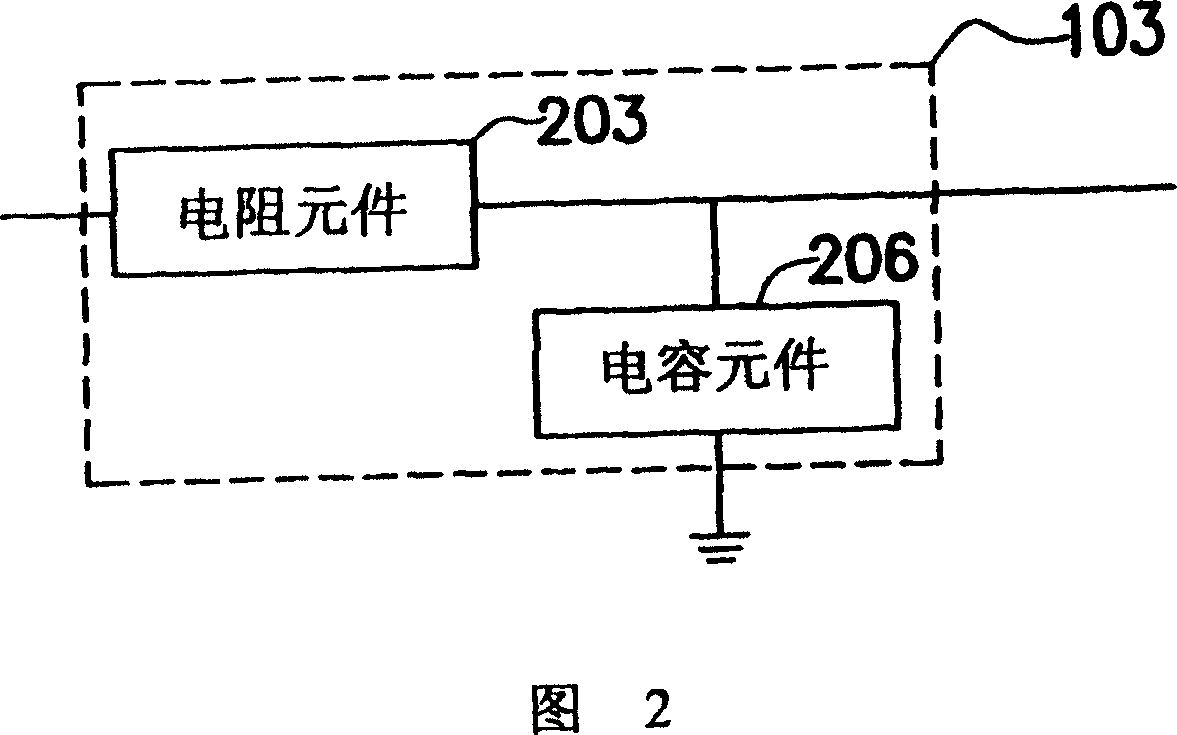

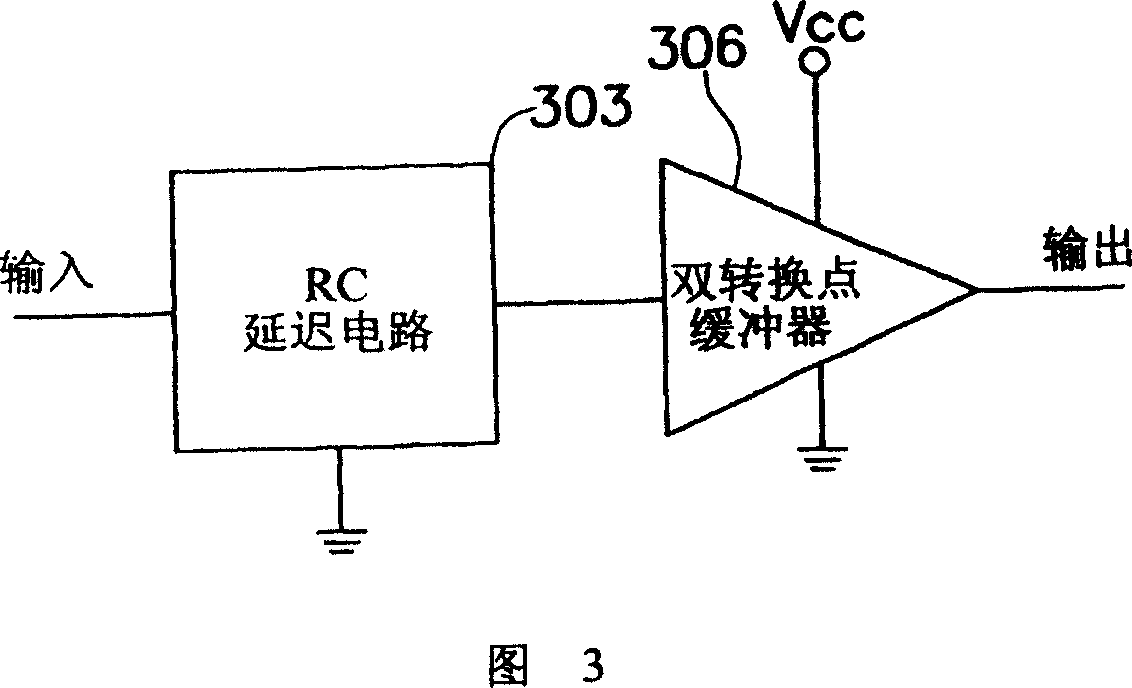

[0037] Please refer to FIG. 3 , which shows a schematic block diagram of a delay circuit according to a first preferred embodiment of the present invention. This delay circuit includes an RC delay circuit 303 and a double conversion point buffer 306, wherein the internal device of the RC delay circuit 303 is the same as the block diagram of the RC delay circuit shown in FIG. The composed RC delay circuit 303. Its action is that the input signal will be transformed into a delayed signal with a delay time through the RC delay circuit 303 composed of the resistance component 203 and the capacitor component 206, and the delay time of the delay signal is the RC time constant.

[0038]The next double switching point buffer 306 provides two level voltages, which can enhance the tolerance to noise. In a preferred embodiment of the present invention, the double switching point buffer 306 can be a Schmitt Trigger Circuit (Schmitt Trigger Circuit). Those skilled in the art will know tha...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More