Electrically alterable non-volatile memory with n-bits per cell

a non-volatile memory, electric altering technology, applied in static storage, digital storage, instruments, etc., can solve the problems of unstable reference voltage level, complex sensing scheme of multi-level memory devices, and requiring 2.sup.n-1 voltage references

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

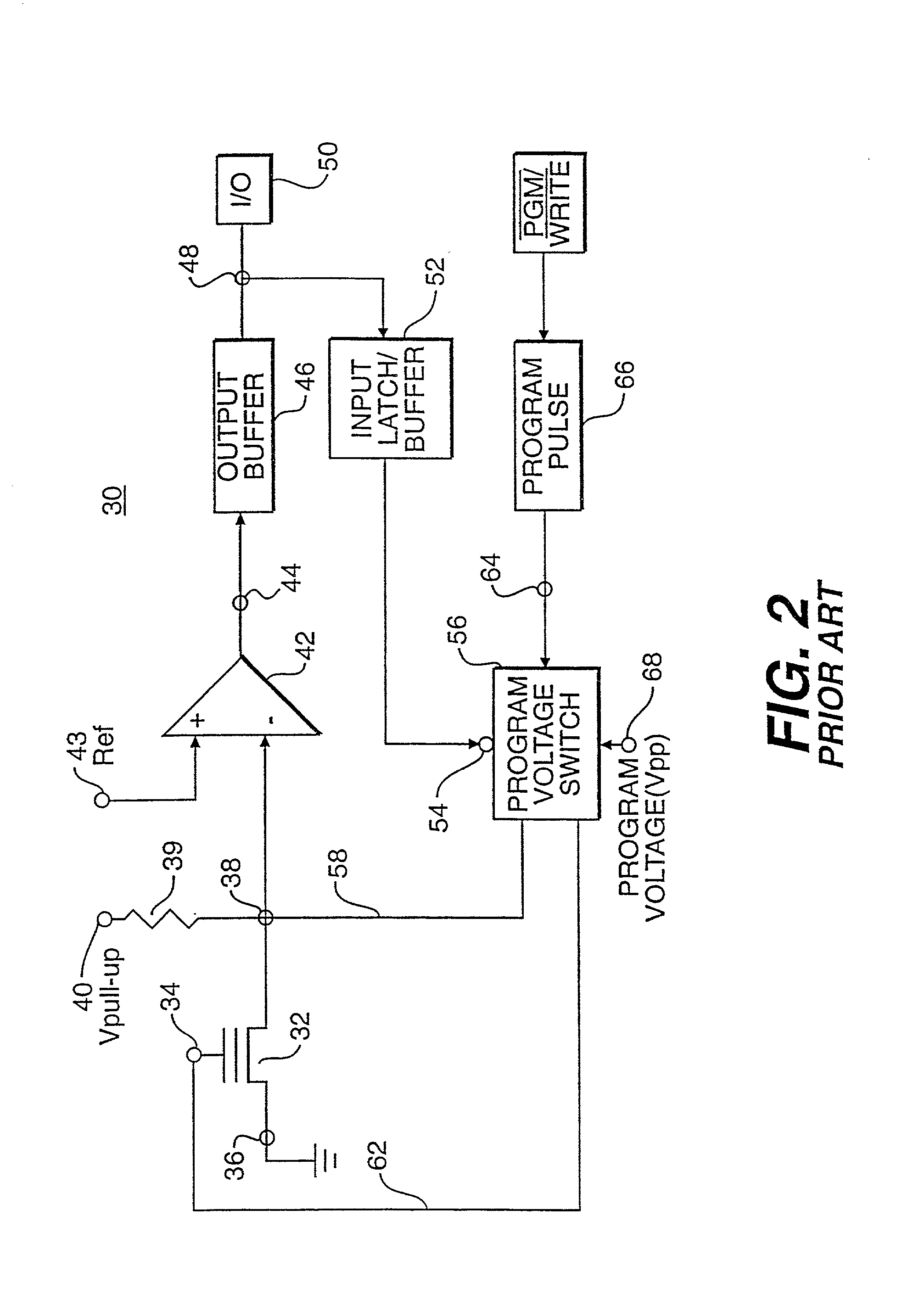

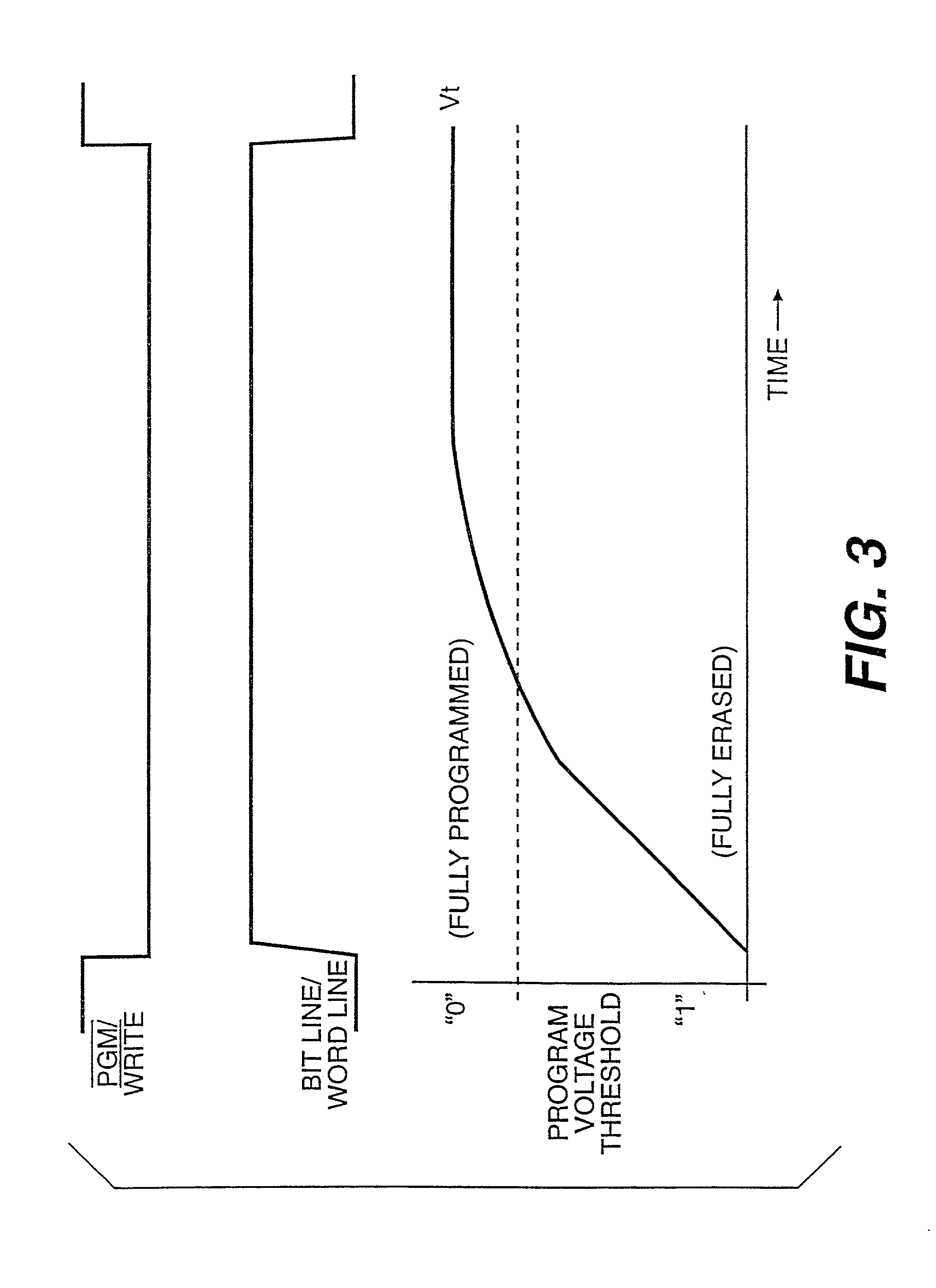

[0065] A multi-level (or multi-bit) memory device which contains more than one bit of information per memory cell needs accurate and stable reference voltages. The reference voltages allow a multi-level memory cell to be correctly read over various process, voltage, and temperature ranges. The reference voltages must be implemented into the integrated circuit which can accurately sense the multi-level voltage levels of the memory cells as well as track each memory array voltage level as it drifts with the process, voltage, and temperature variations. An unstable or inaccurate reference voltage tends to cause problems such as an improper voltage level read of a bit line, and the like from a memory cell.

[0066] In a 2-bit per memory cell embodiment, the memory cell includes four voltage levels V0, V1, V2, and V3 at each of the bit lines as illustrated by FIG. 15. To uniquely detect each of the four voltage levels, it is necessary to generate at least three reference voltages, each of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More