Semiconductor integrated circuit and printed wiring substrate provided with the same

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

[0016] (First Embodiment)

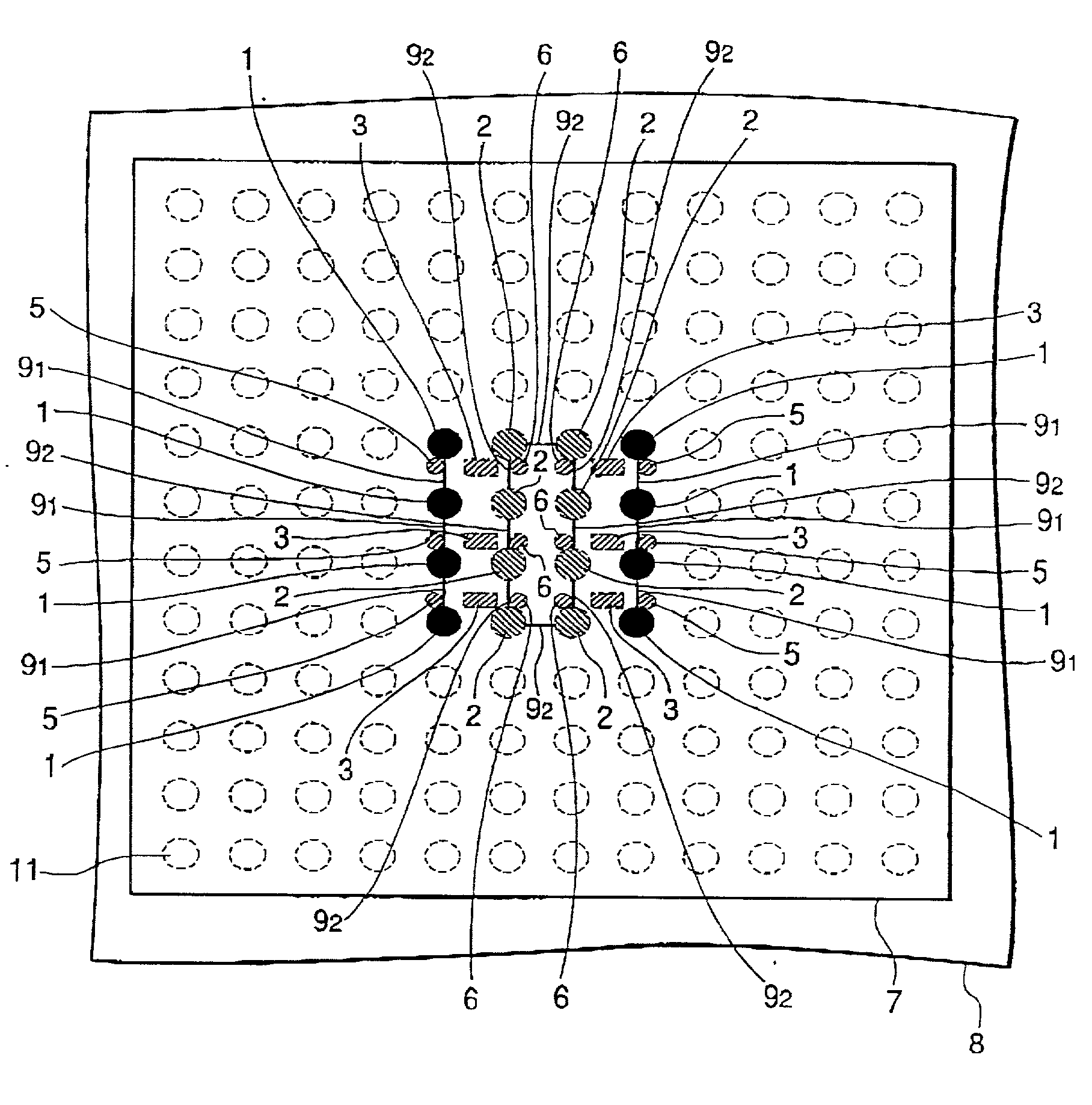

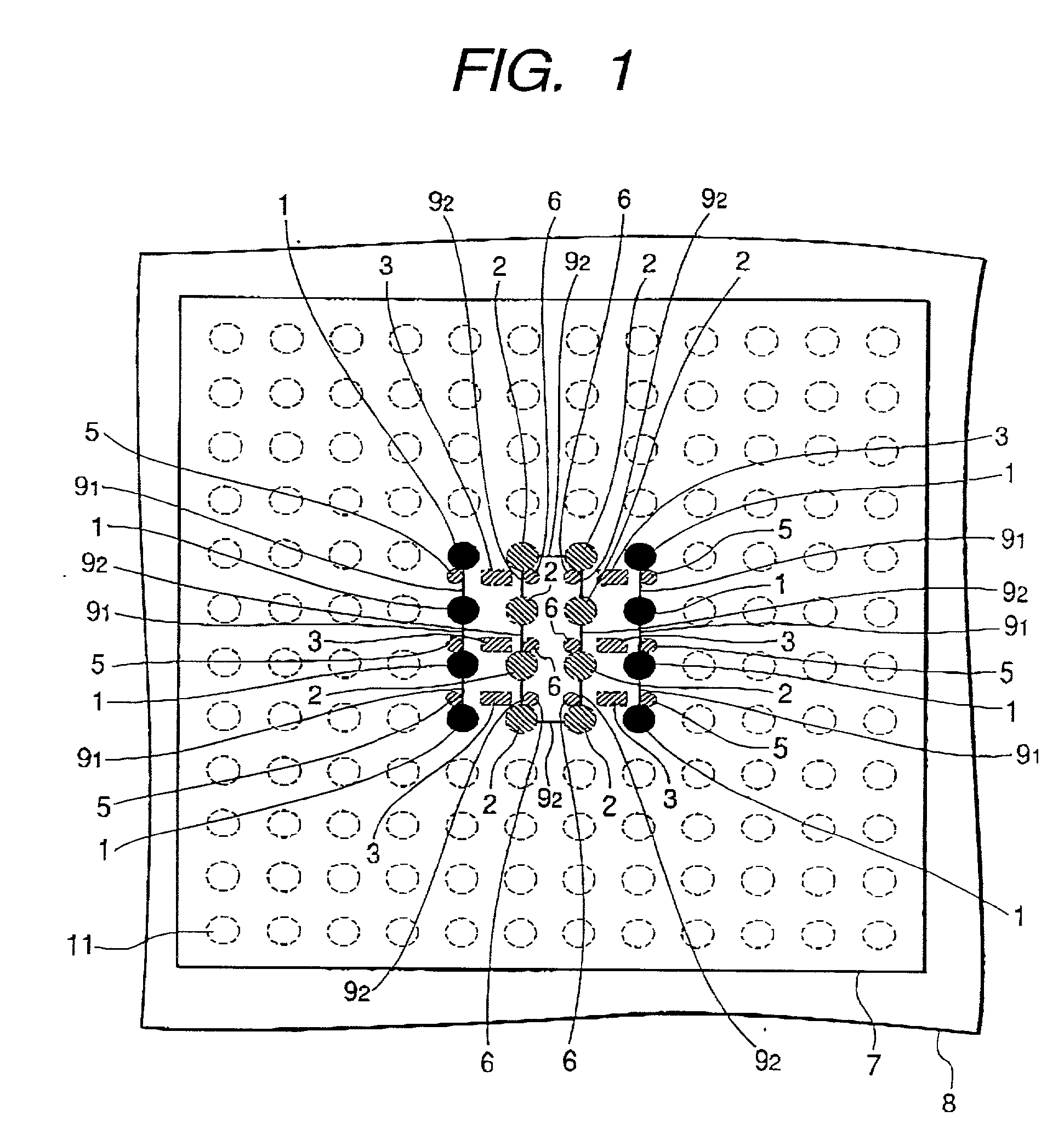

[0017] FIG. 1 is a plan view of a printed wiring substrate carrying thereon a semiconductor integrated circuit according to a first embodiment of the present invention, and FIG. 2 is a longitudinal cross-sectional view of the printed wiring substrate of FIG. 1. FIG. 1 shows the printed wiring substrate 8 carrying thereon the semiconductor integrated circuit 7 having array-like electrode pads as it is seen from a surface on which the semiconductor integrated circuit 7 is mounted.

[0018] In the bottom surface 10 of the package of the semiconductor integrated circuit 7, a plurality of connecting electrode pads 11 (in FIG. 1, indicated by dotted circles) for making the electrical connection between the semiconductor integrated circuit 7 and an external circuit are regularly arranged at a full grid in a grid-like fashion. Of the connecting electrode pads 11, electrode pads 1 for ground (indicated by black painted-out circles) are connecting electrode pads for grou...

second embodiment

[0023] (Second Embodiment)

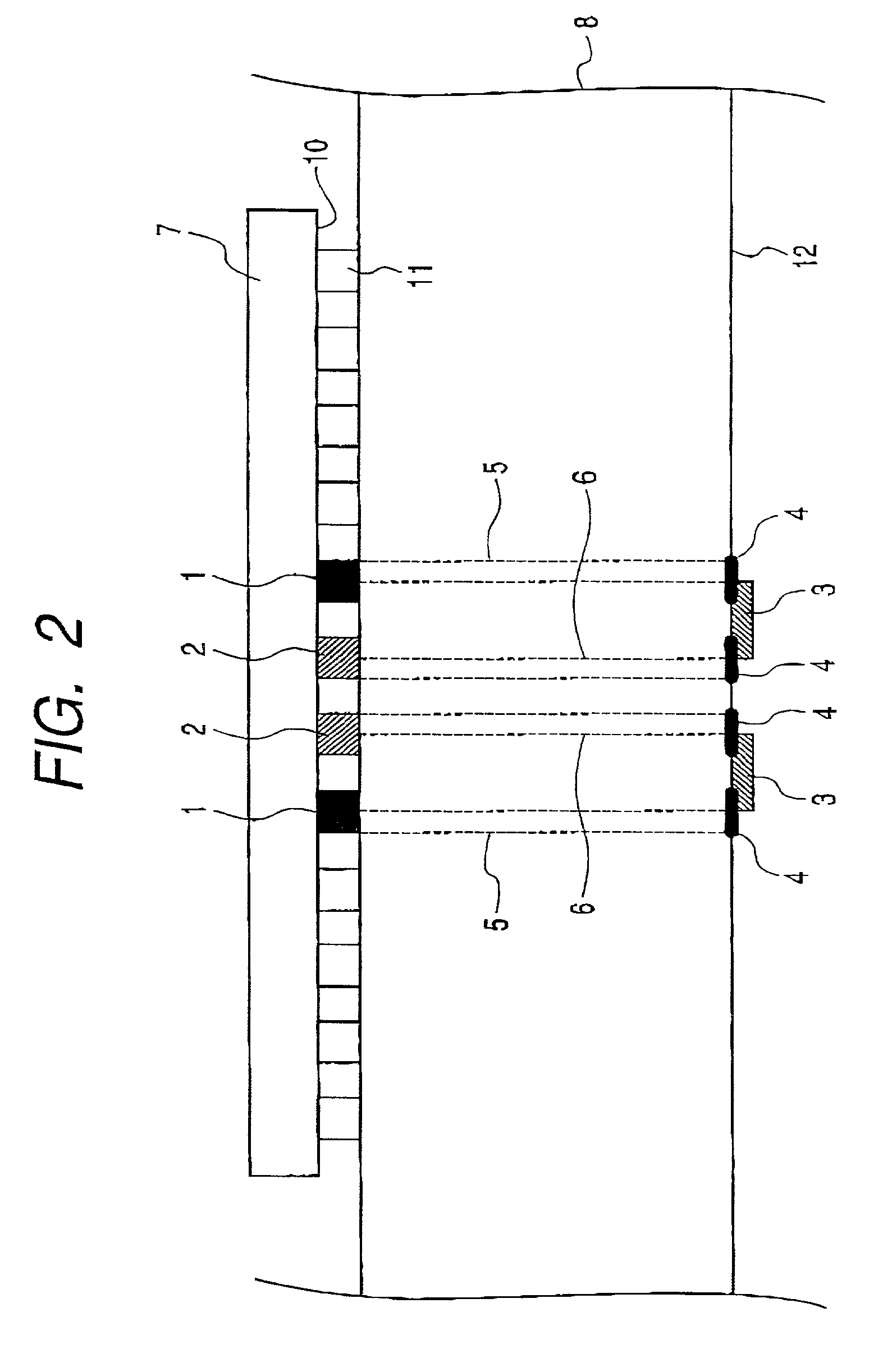

[0024] FIG. 3 is a plan view of a printed wiring substrate carrying thereon a semiconductor integrated circuit according to a second embodiment of the present invention. In this embodiment, as shown in FIG. 3, the power supply electrode pads 2 of the semiconductor integrated circuit 7 of FIGS. 1 and 2 are disposed on the innermost side and the electrode pads 1 for ground are disposed so as to surround the power supply electrode pads 2, and all of the power supply electrode pads 2 and all of the electrode pads 1 for ground are connected by a wiring pattern 9.sub.2 and a wiring pattern 9.sub.1, respectively. In the other points, the construction of the present embodiment is the same as that of the first embodiment.

[0025] Again in such a construction, as in the first embodiment, the radiation noise of electromagnetic waves from the printed wiring substrate 8 is reduced and the drawing-out of the wiring from the electrode pads for signals to the surrounding par...

third embodiment

[0026] (Third Embodiment)

[0027] FIG. 4 is a plan view of a printed wiring substrate carrying thereon a semiconductor integrated circuit according to a third embodiment of the present invention. This embodiment is such that in the first embodiment, the electrode pads 1 for ground and the power supply electrode pads 2 are disposed in spirally opposed relationship with each other and in the other points, the construction of the present embodiment is the same as that of the first embodiment.

[0028] Again in such a construction, as in the first embodiment, the radiation noise of electromagnetic waves from the printed wiring substrate 8 is reduced and the drawing-out of the wiring from the electrode pads for signals to the surrounding parts becomes easy, and this is also effective for the higher density of the printed wiring substrate.

PUM

| Property | Measurement | Unit |

|---|---|---|

| Density | aaaaa | aaaaa |

| Shape | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More