Testing of integrated circuits using boundary scan

a technology for integrated circuits and boundary scans, applied in digital circuit testing, electronic circuit testing, measurement devices, etc., can solve the problems of difficult testing of difficult to write test software for jtag testing, and difficult to test the connection between the bga chip and its board. achieve the effect of facilitating the creation of test scripts

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

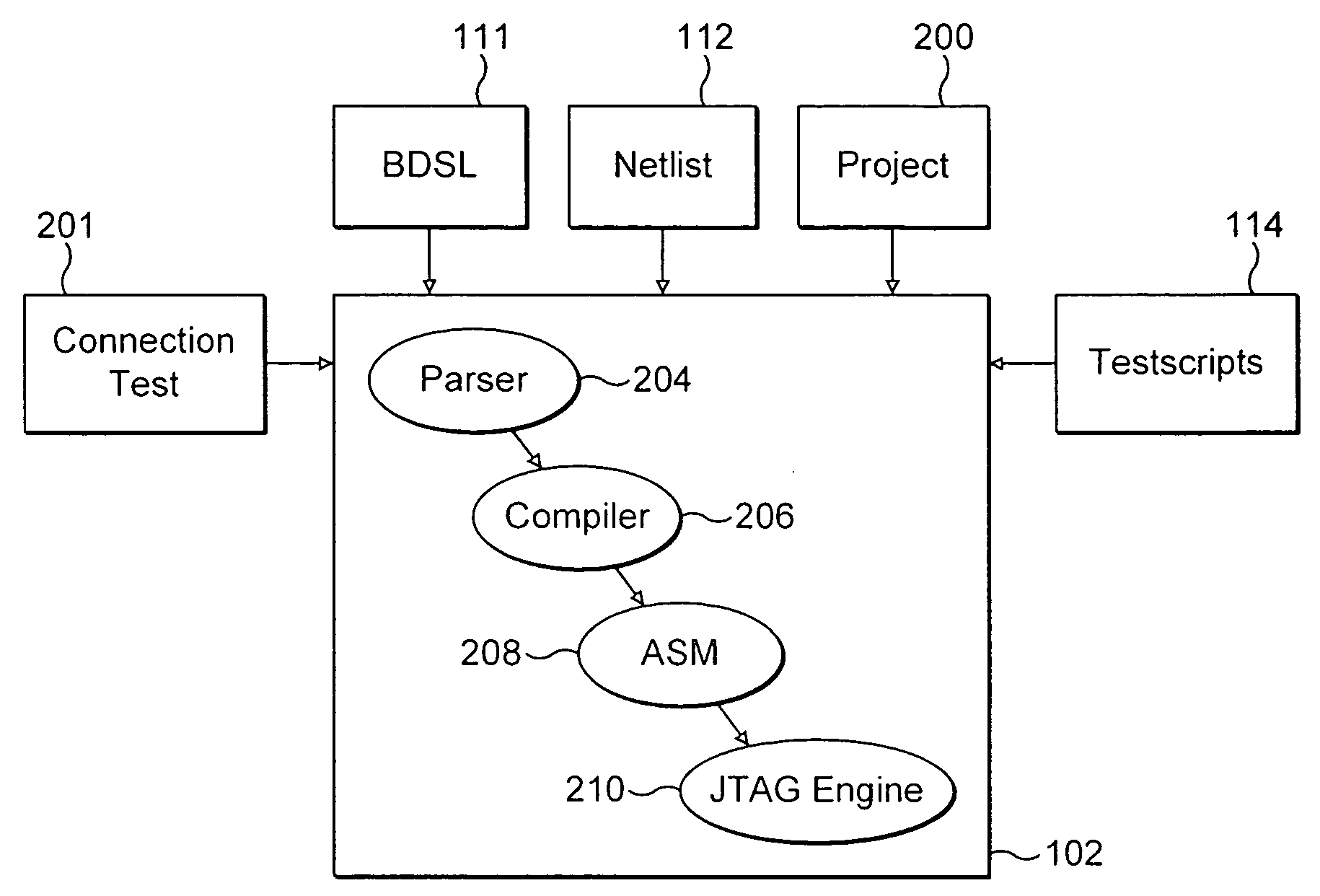

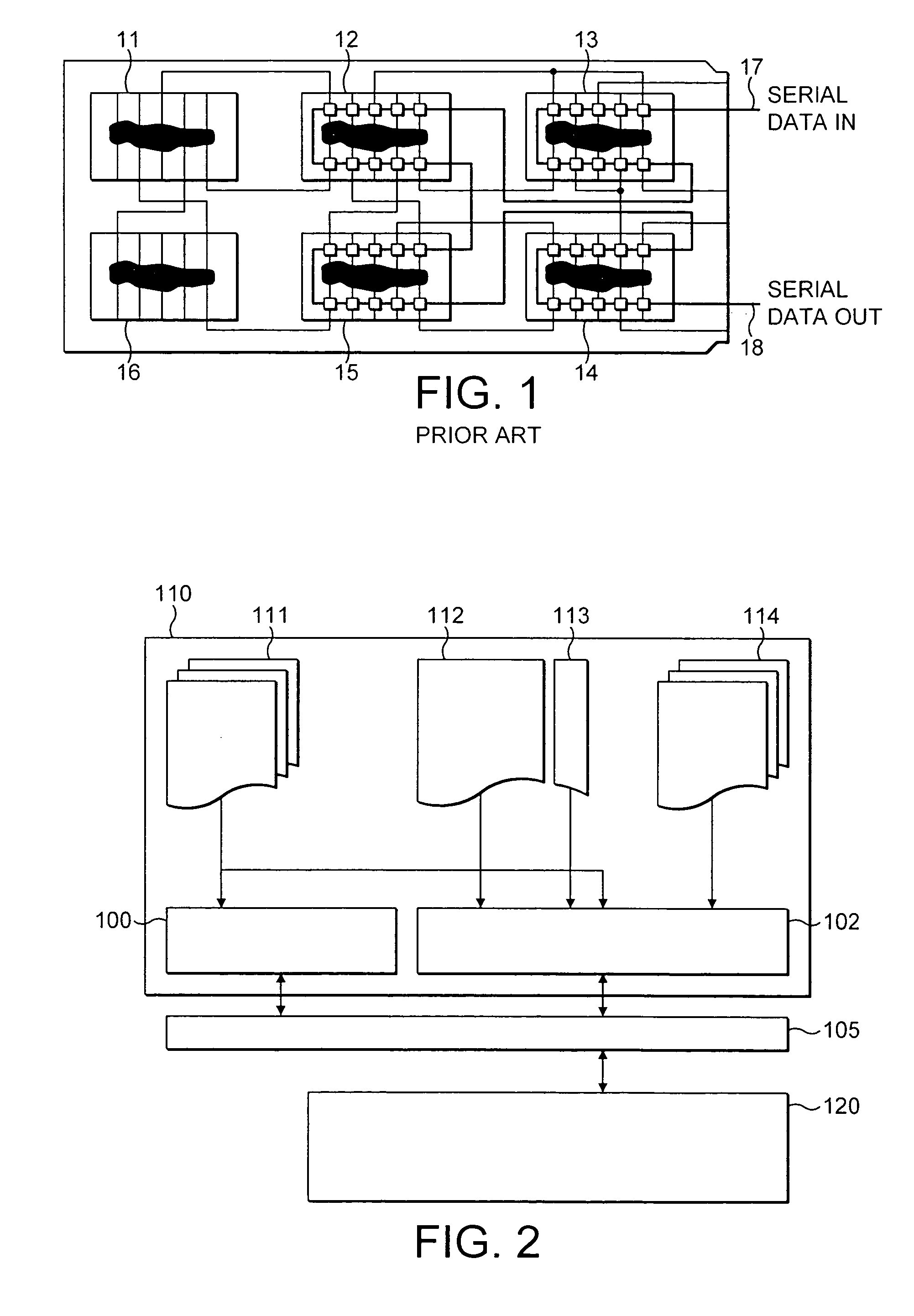

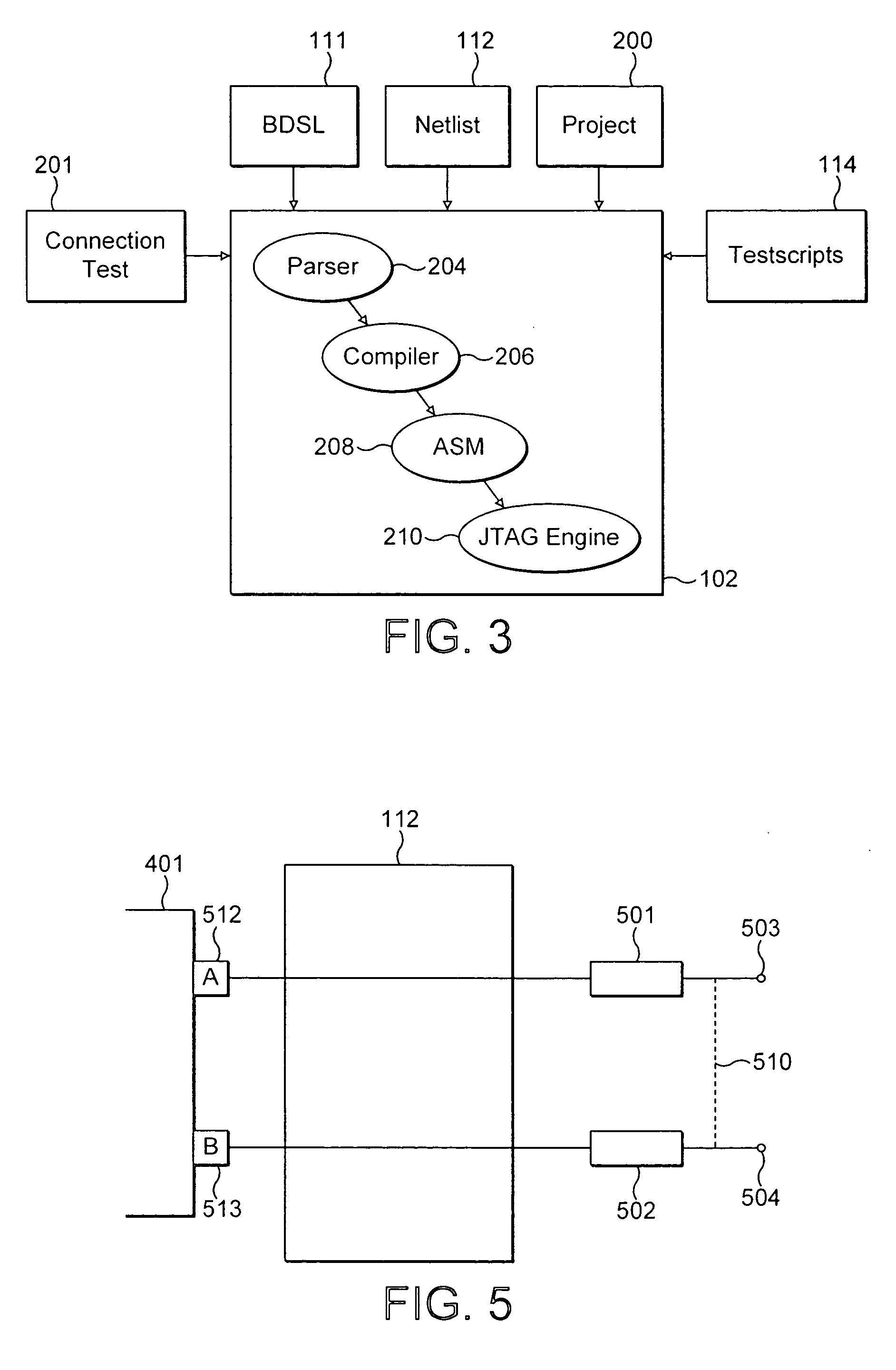

[0020] Referring to FIG. 2, the equipment of the present invention comprises analyser software 100 and test software 102, which are run on a computer 110 that is connected via an adapter 112 to a board 120 that is to be tested. The test software 102 is stored in a high level language as described below. Loaded into the computer 100 are boundary-scan description language (BSDL) files 111, a netlist 112 and a set of test scripts 114. Beside the netlist 112 is shown a connections list 113.

[0021] Each BSDL file 111 is supplied by the manufacturer of a particular IC and defines, for that IC the manner in which JTAG is implemented. BSDL files contain the following elements: [0022] Entity Description: Statements naming the device or a section of its functionality. [0023] Generic Parameter: A value such as a package type. The value may come from outside the current entity. [0024] Port Description: Describes the nature of the pins on the device (input, output, bidirectional, linkage). [0025...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More