Memory technology test apparatus

a memory technology and test apparatus technology, applied in the field of memory devices, can solve the problems of spurious data to be used during read or write operations, adversely affecting data and address eyes, and other high-speed memory devices currently being developed, and achieve the effects of quick, flexible, efficient and inexpensive manner, inexpensive and timely, and cheap and convenient us

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] In the following detailed description, reference is made to various specific embodiments in which the invention may be practiced. These embodiments are described with sufficient detail to enable those skilled in the art to practice the invention, and it is to be understood that other embodiments may be employed, and that structural and electrical changes may be made without departing from the spirit or scope of the present invention.

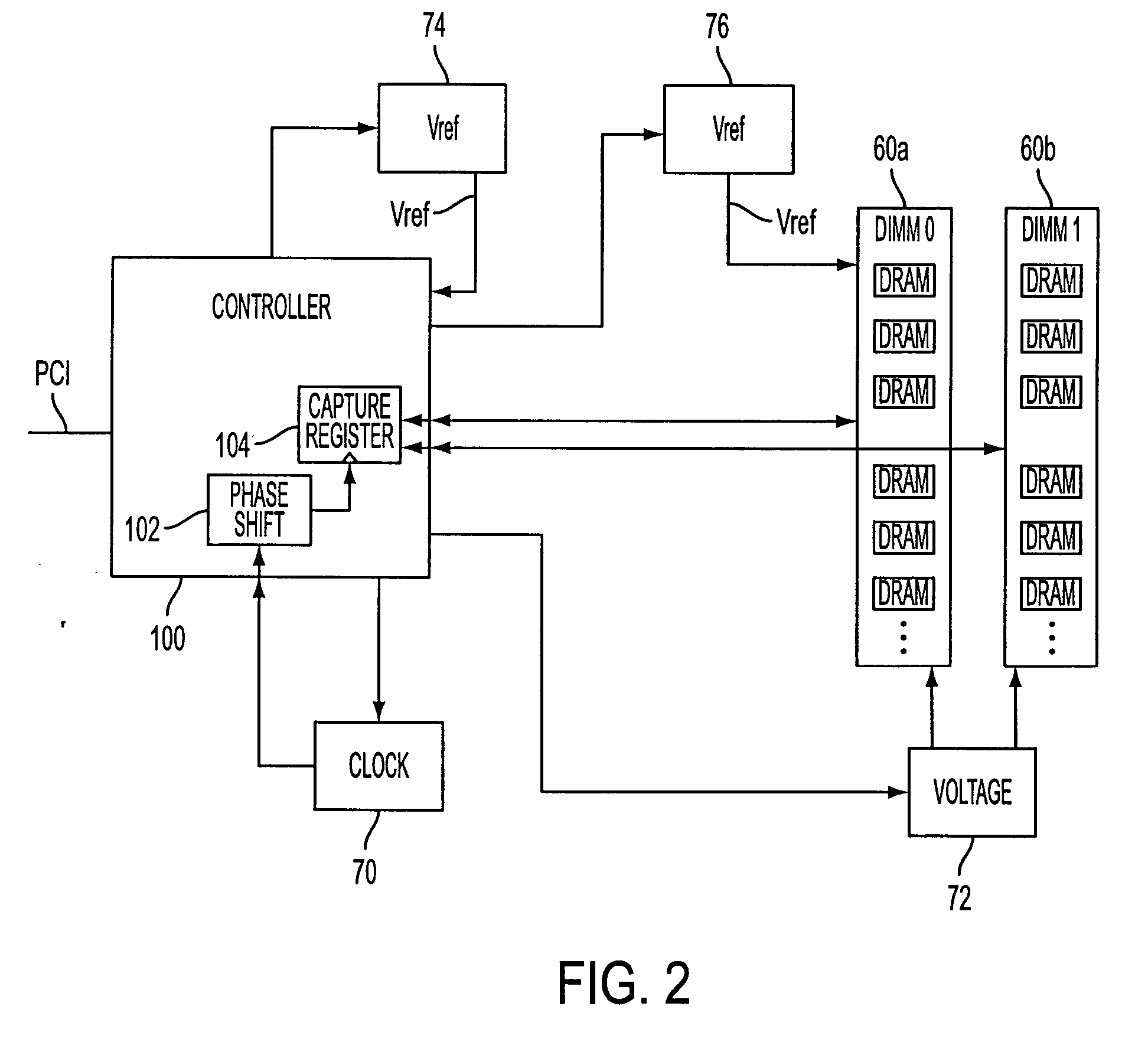

[0017] The following description is made with reference to DDR SDRAM technology. It should be appreciated, however, that the test board and control device of the present invention may be utilized with any current and future memory technology and that the invention is not to be limited to any specific form of memory (such as a DDR SDRAM). In fact, one of the objectives of the invention is to aid in the development of new technology by simplifying the testing, evaluation and prototyping of new memory devices.

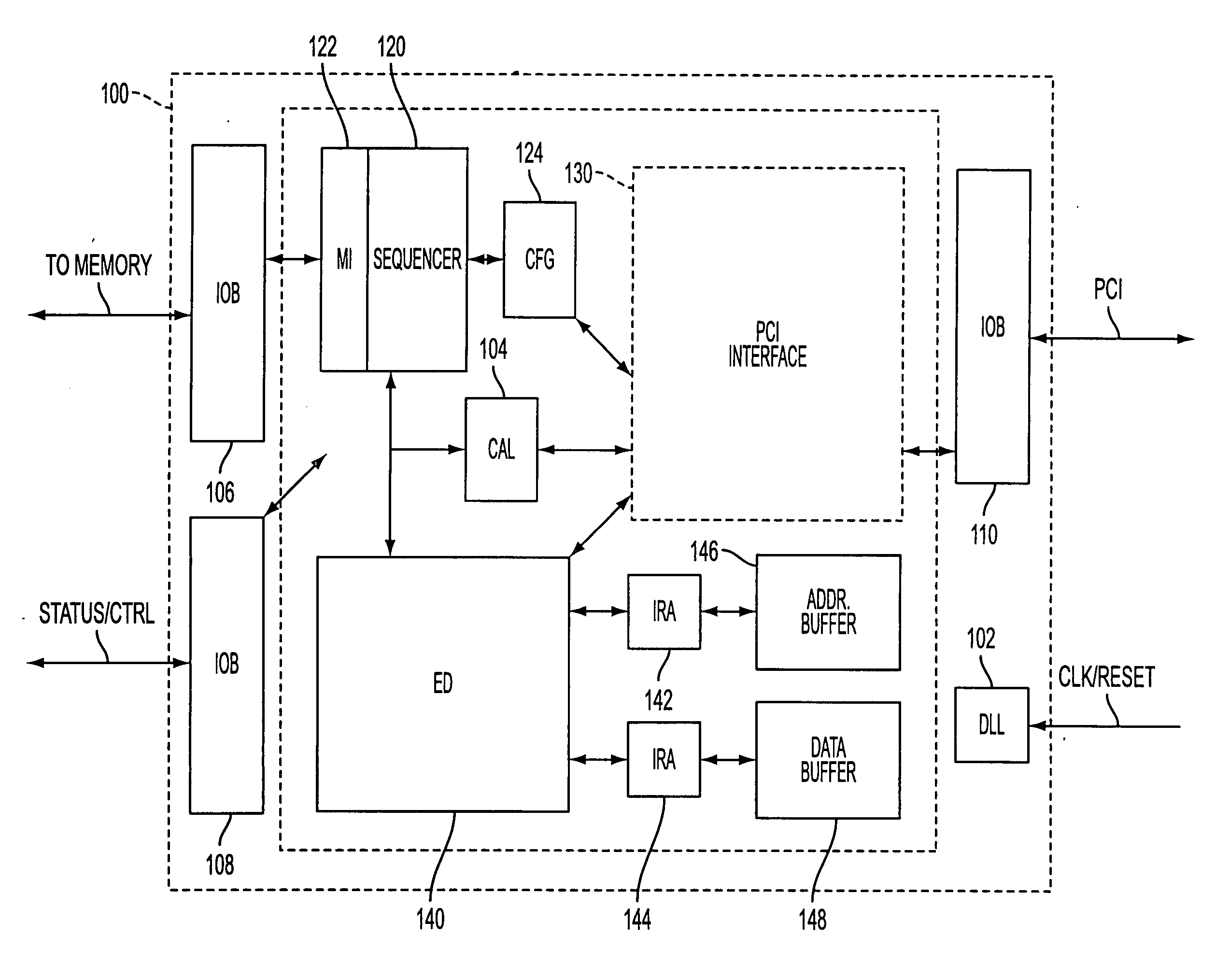

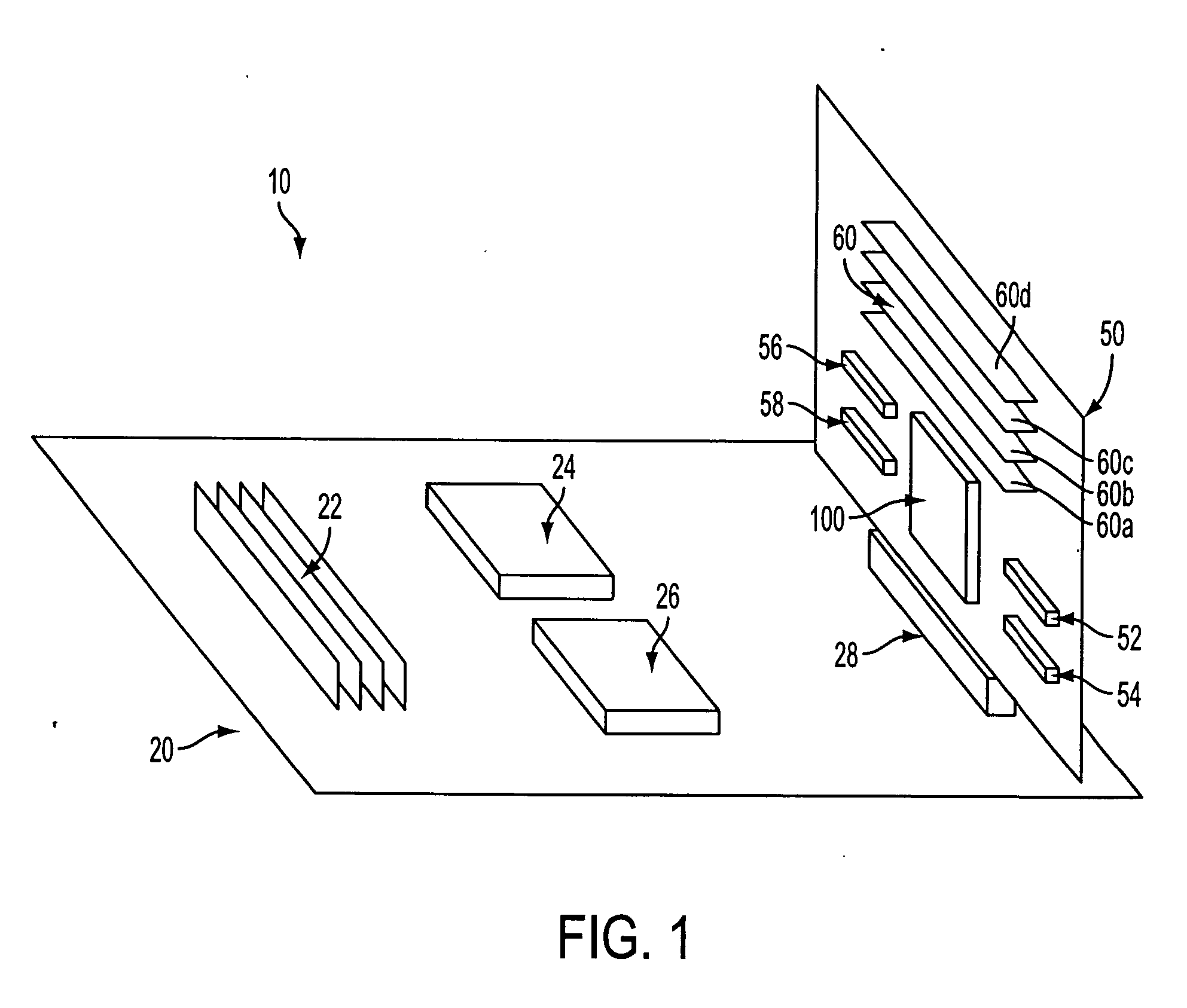

[0018]FIG. 1 illustrates an exemplary t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More