Mixed-scale electronic interface

a technology of electronic interface and mixed-scale, applied in the direction of electrical equipment, semiconductor devices, instruments, etc., can solve the problems of high cost, design and fabrication overhead, and inability to meet the needs of mixing-scale microelectronic devices, and achieve the effect of improving reliability, cost and reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

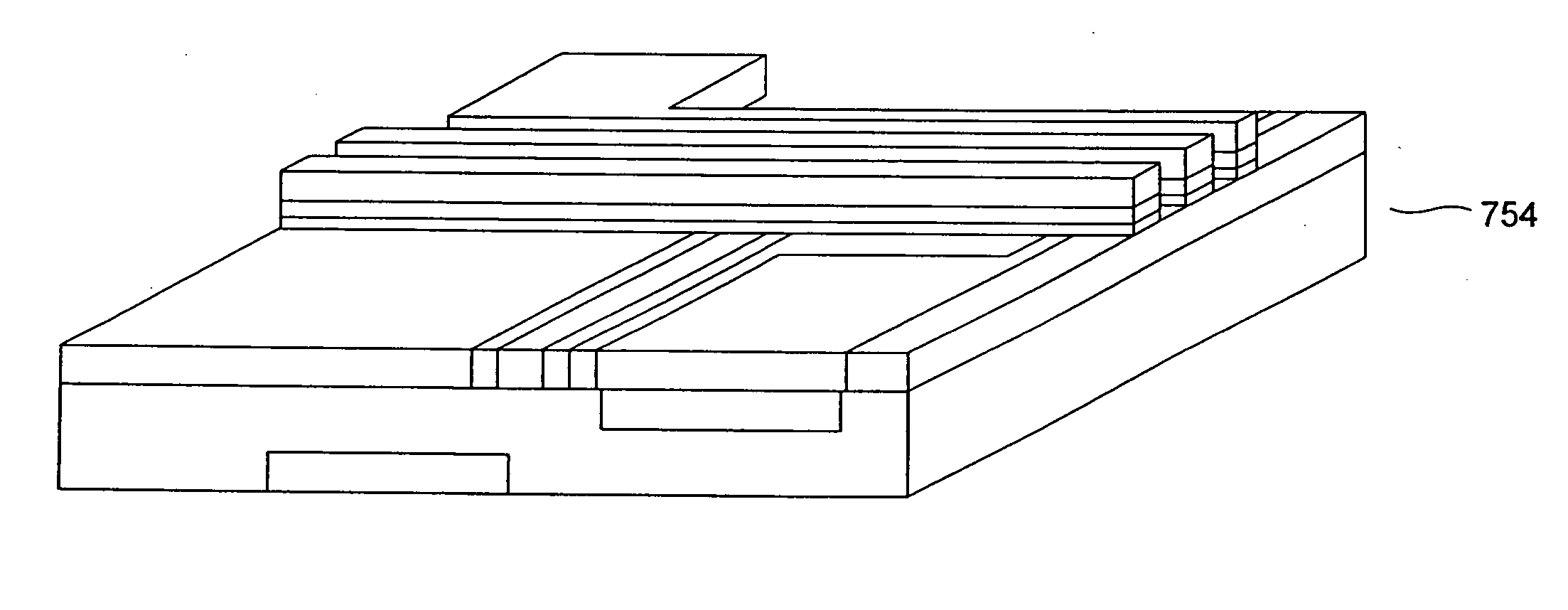

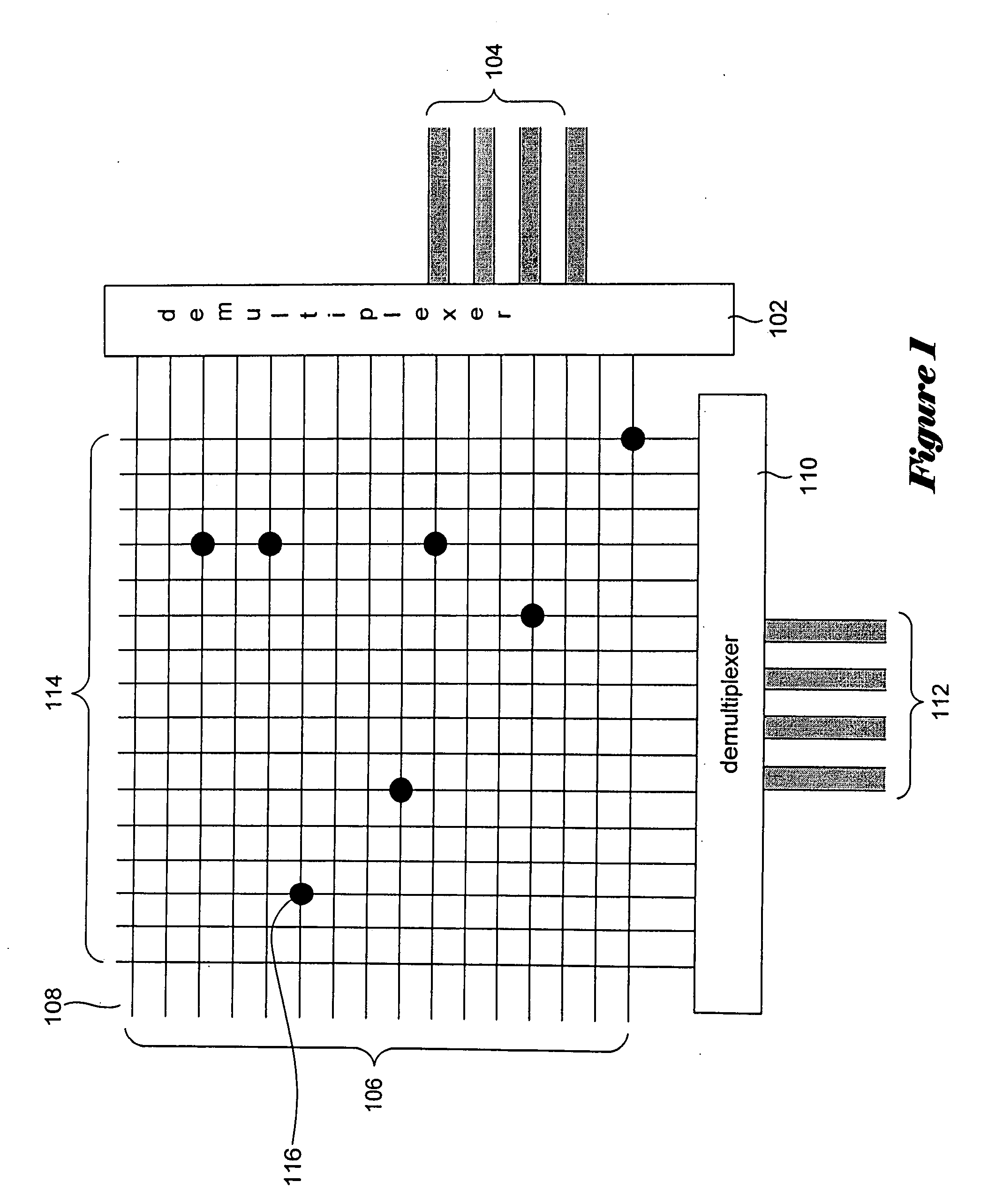

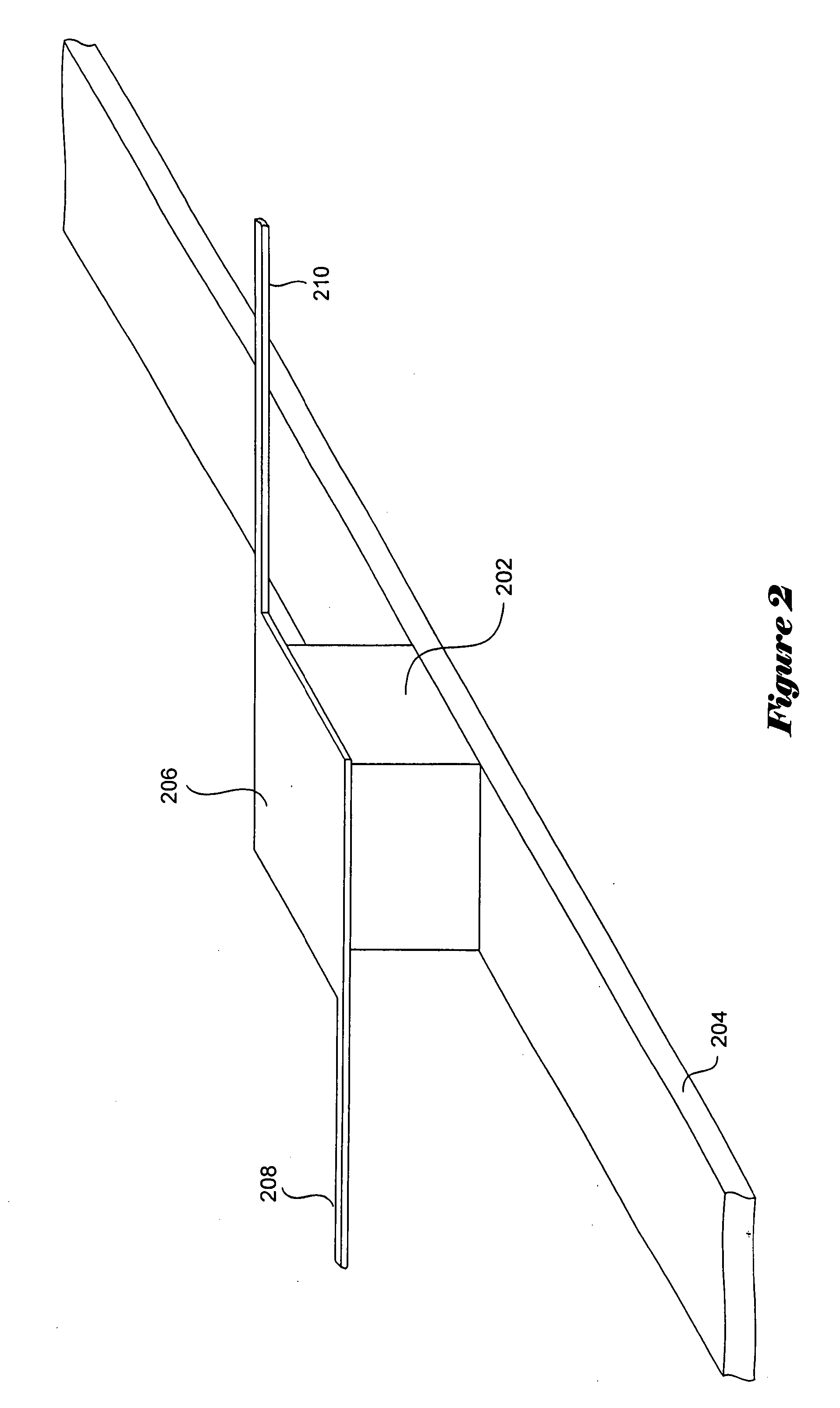

[0029] Embodiments of the present invention are directed to nanoscale / microscale interfaces that permit dense interconnections between microscale and submicroscale features and logic and nanoscale features and logic within an integrated circuit or other electronic device. In the current discussion, the term “nanoscale” refers to features and components with a least one dimension smaller than 100 nanometers. Alternatively, the term “nanoscale” may refer to features and components with at least one dimension smaller than 50 nanometers, and, in certain cases, less than 10 nanometers. The term “submicroscale” generally refers to features and components with at least on dimension smaller than 1 micron, and the term “microscale” refers to features and components with dimensions equal to, or greater than, 1 micron. In general, microscale and submicroscale features and components can be fabricated by conventional photolithographic techniques, but nanoscale components and features can genera...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More