Semiconductor integrated circuit

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

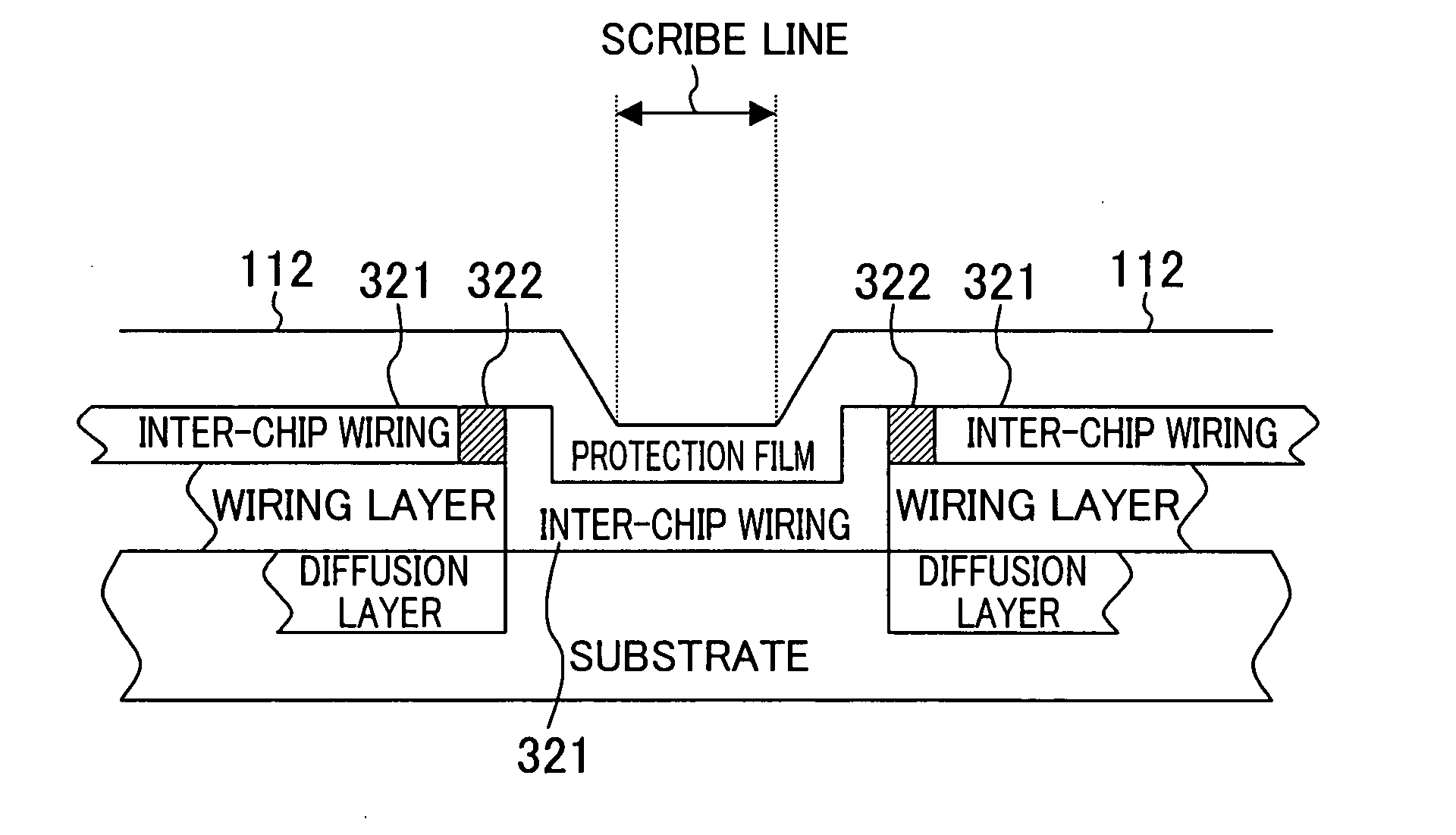

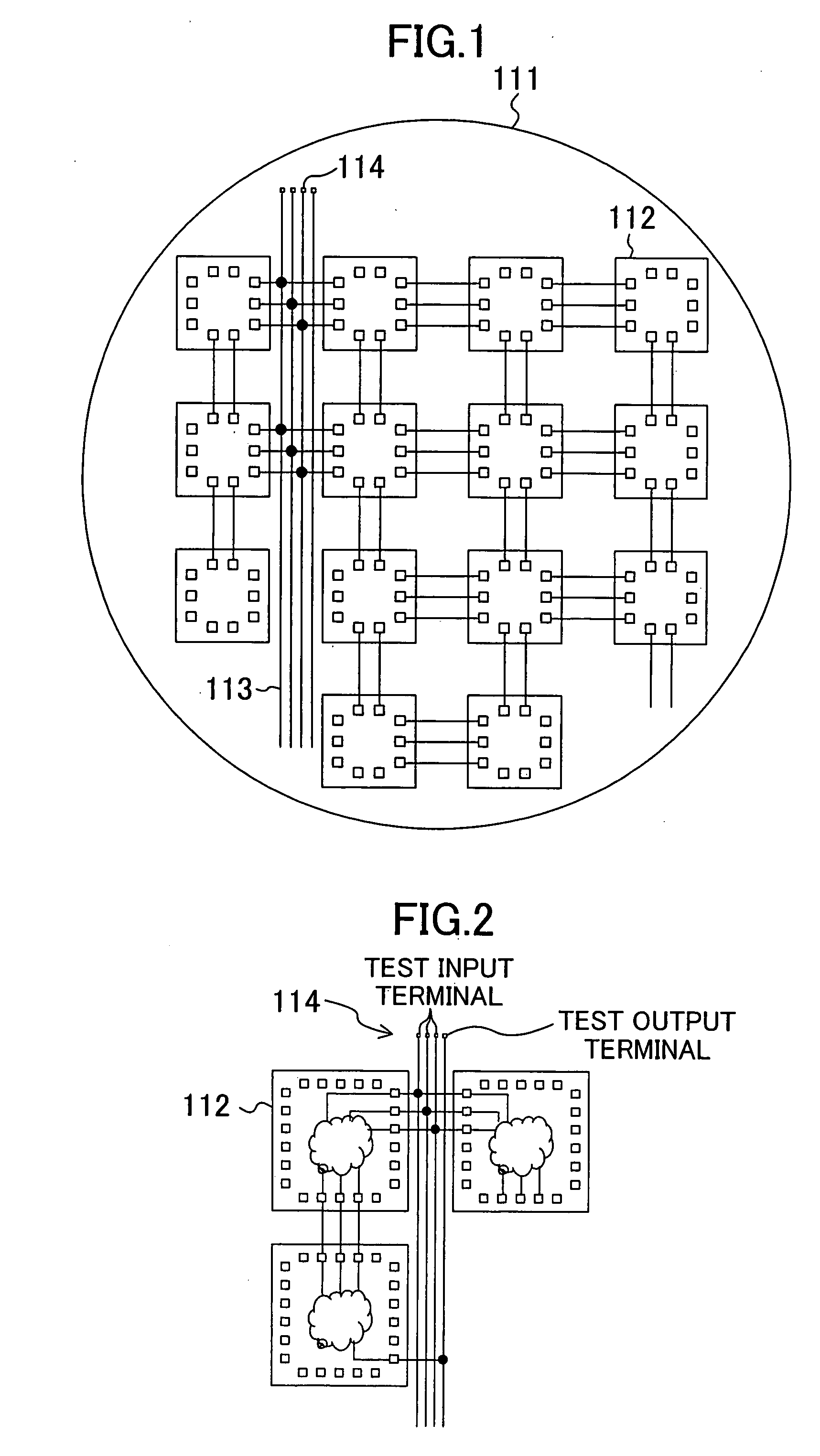

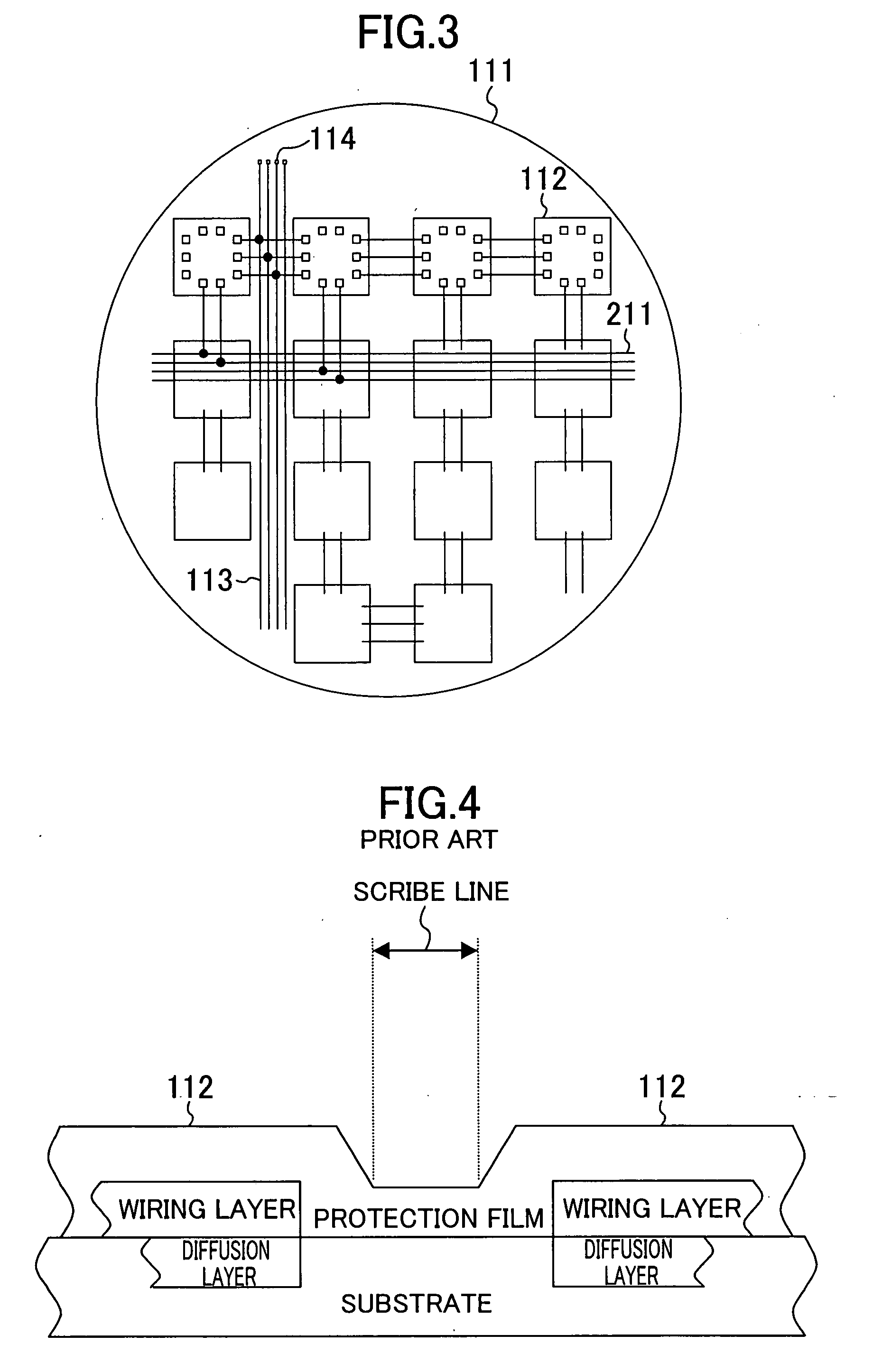

[0052]Embodiments of the present invention will be described below with reference to the accompanying drawings.

[0053]FIG. 1 is a plan view of a wafer of a semiconductor integrated circuit in one embodiment of the present invention. Wirings, which are led out from test terminals of a plurality of chips 112 formed on a semiconductor wafer 111 to the outside of the chips, are all connected to the wafer 111. A test signal wiring group 113, which is formed along a scribe line, is connected to a test terminal group 114 provided in the peripheral part of the wafer 111.

[0054]FIG. 2 shows a connection of one 112 of the chips to other adjacent chips. Test input terminals (for example, a clock input terminal, a scan enable input terminal, a scan-in terminal) in the test terminal group 114 are connected to test input terminals of a plurality of chips 112. Test output terminals (for example, a clock output terminal, a scan enable output terminal, a scan-out terminal) of the chip 112 are connecte...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More