Computer processing system employing an instruction reorder buffer

a computer processing system and instruction reordering technology, applied in the field of instruction reorder buffers, can solve the problems of cumbersome mapping of ilp applications on one or more tlp cores, requiring highly complex microprocessors that consume a significant amount of power, and consuming a large amount of power

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

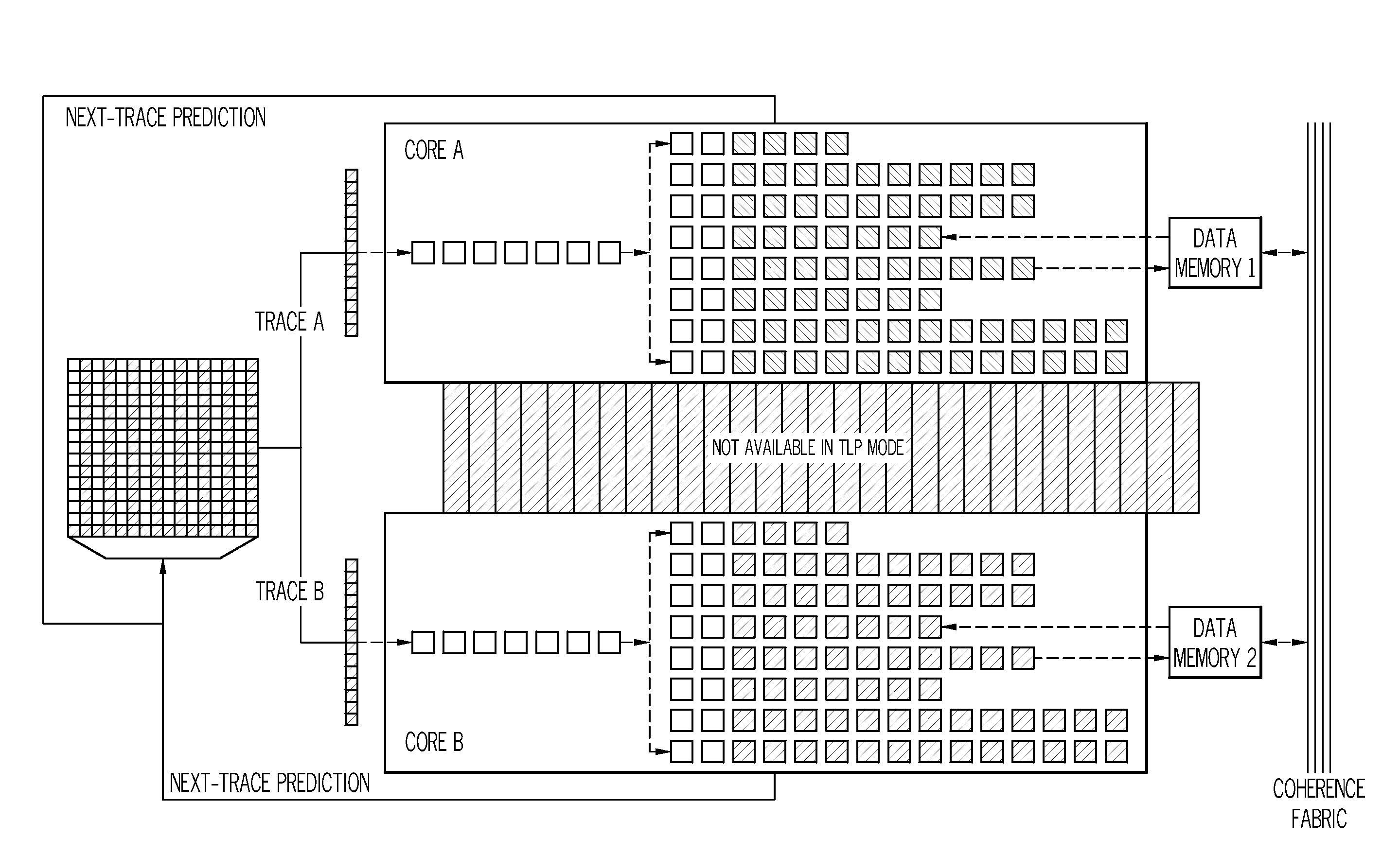

[0027]One aspect of the exemplary embodiments is a superstructure called SuperROB (Super Re-Order Buffer) that operates across a plurality of TLP cores. Another aspect of the exemplary embodiments is a method of mapping ILP applications on a TLP core by providing for ILP extraction on demand.

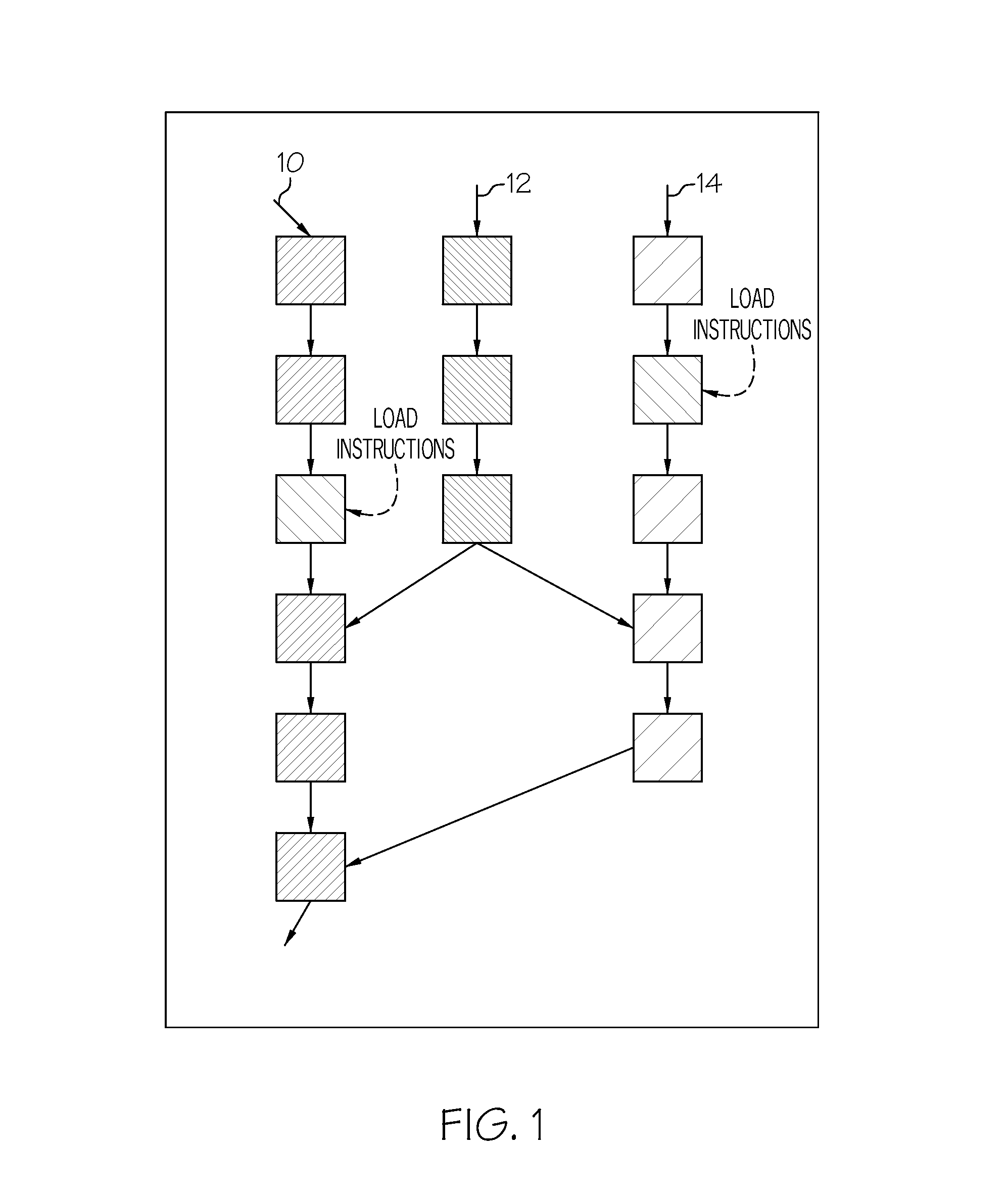

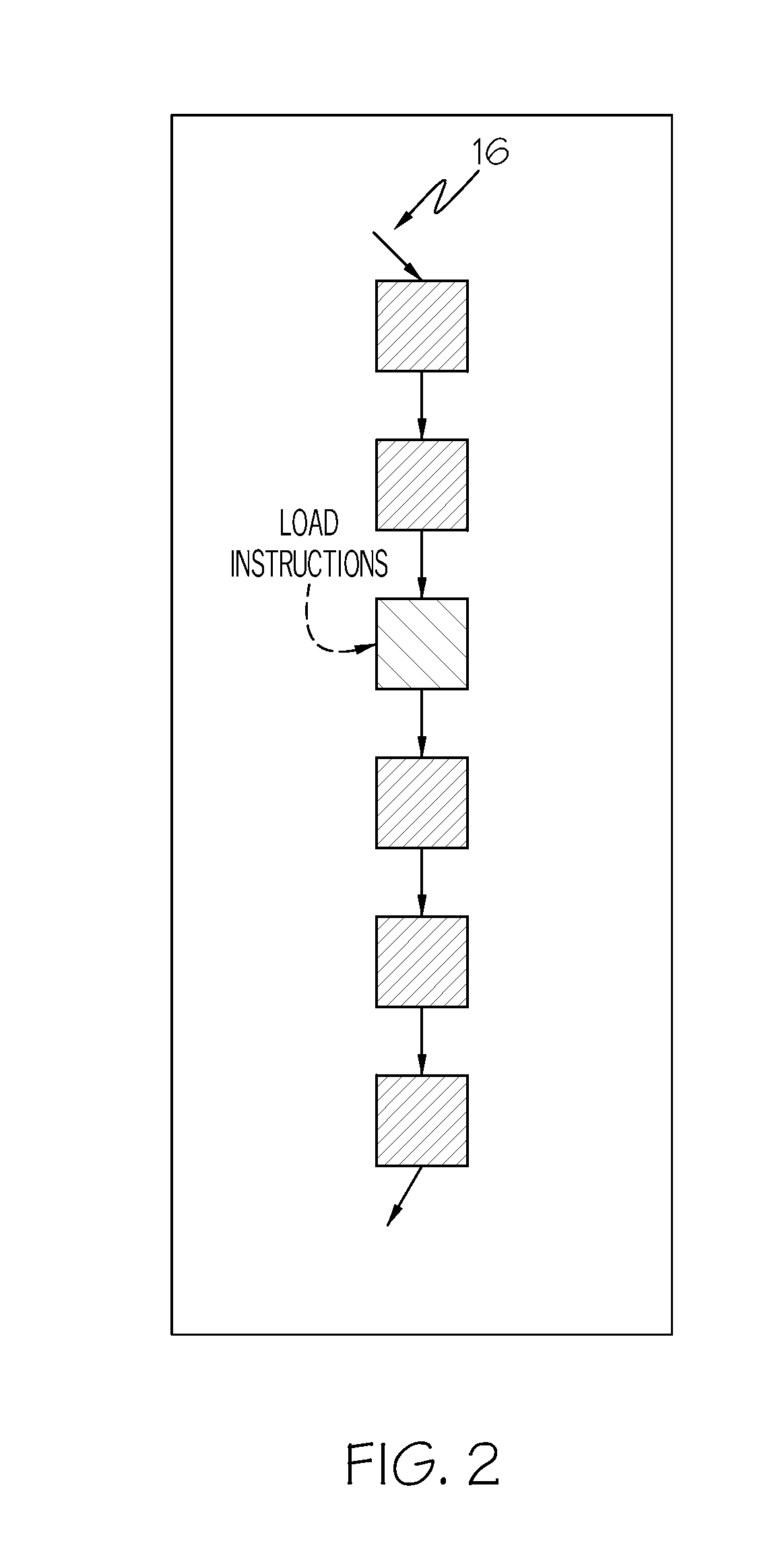

[0028]For a long time, the secret to more performance was to execute more instructions per cycle, otherwise known as ILP, or decreasing the effective latency of instructions. To execute more instructions each cycle, more functional units (e.g., integer, floating point, load / store units, etc.) had to be added. In order to more consistently execute multiple instructions, a processing paradigm called out-of-order processing (OOP) may be used. FIG. 1 illustrates one example of an ILP workload using such processing paradigm.

[0029]In FIG. 1, there are three semi-independent chains of dependences that contain load instructions. Key data dependence paths that the processor optimizes are compute-compute ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More