Patents

Literature

39 results about "Re-order buffer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A re-order buffer (ROB) is used in a Tomasulo algorithm for out-of-order instruction execution. It allows instructions to be committed in-order. Normally, there are three stages of instructions: "Issue", "Execute", "Write Result". In Tomasulo algorithm, there is an additional stage "Commit". In this stage, the results of instructions will be stored in a register or memory. In the "Write Result" stage, the results are just put in the re-order buffer. All contents in this buffer can then be used when executing other instructions depending on these.

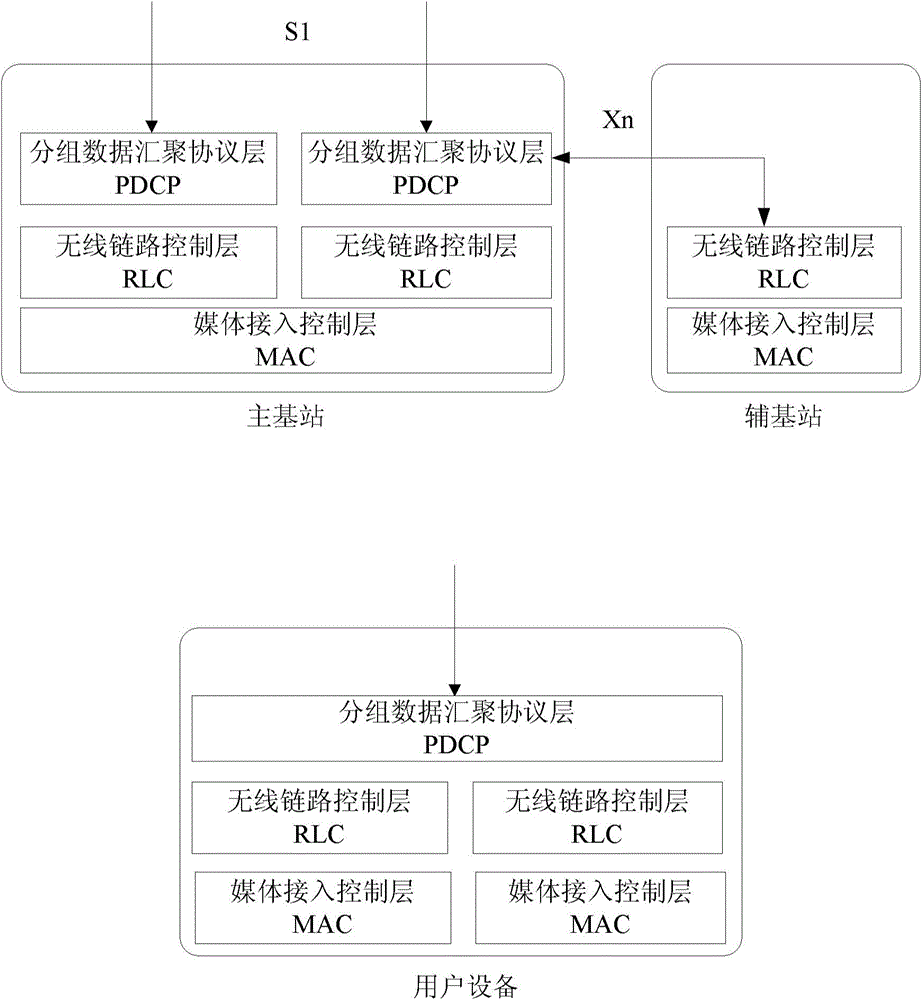

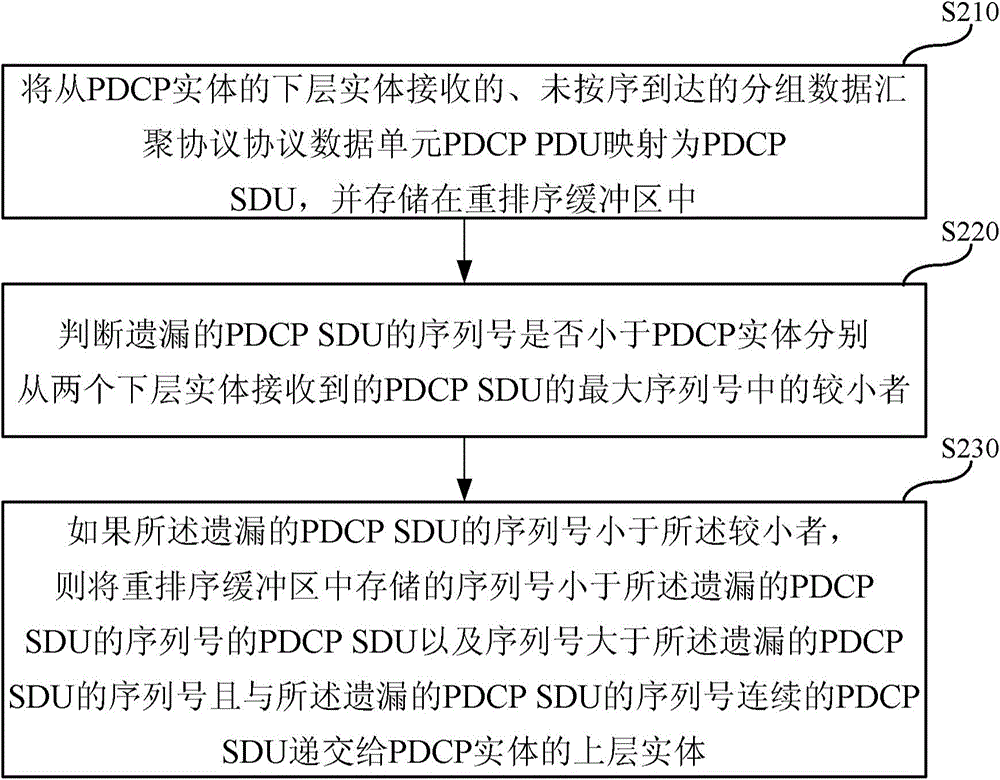

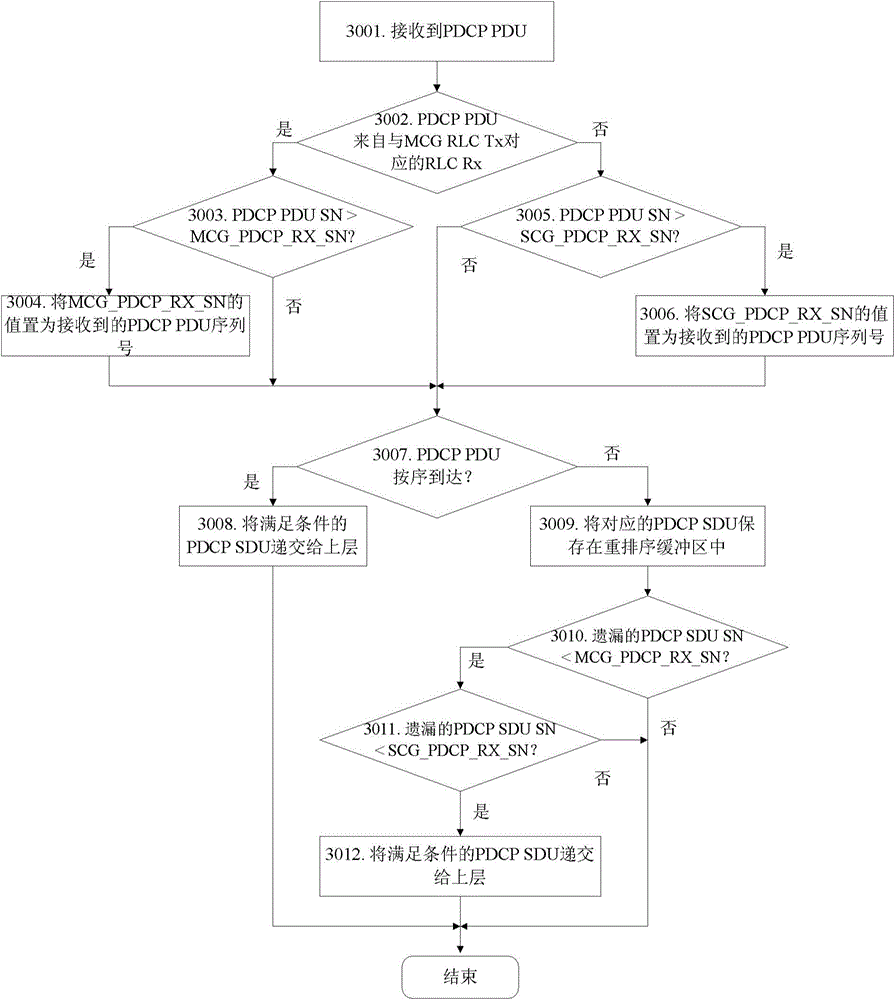

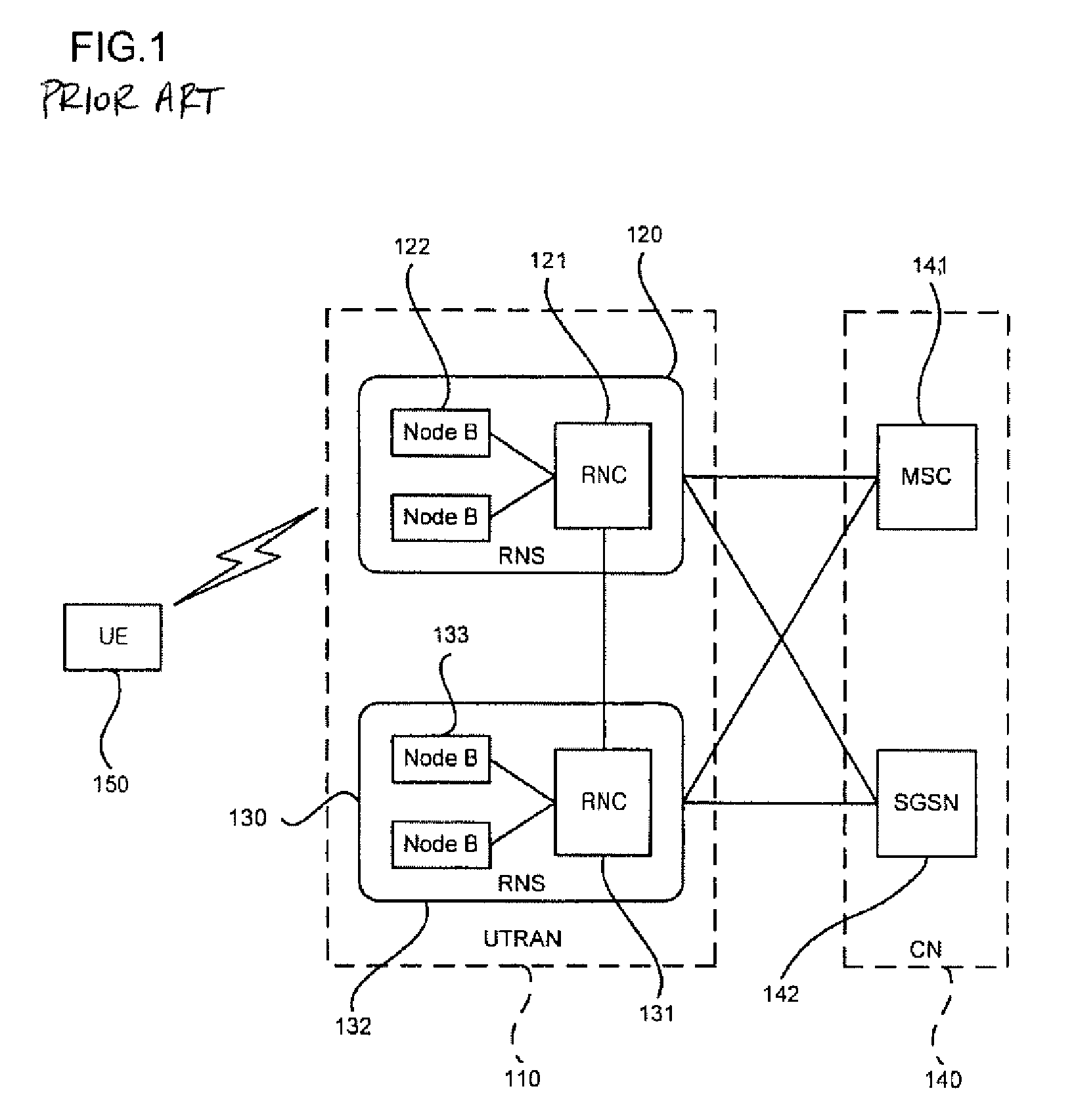

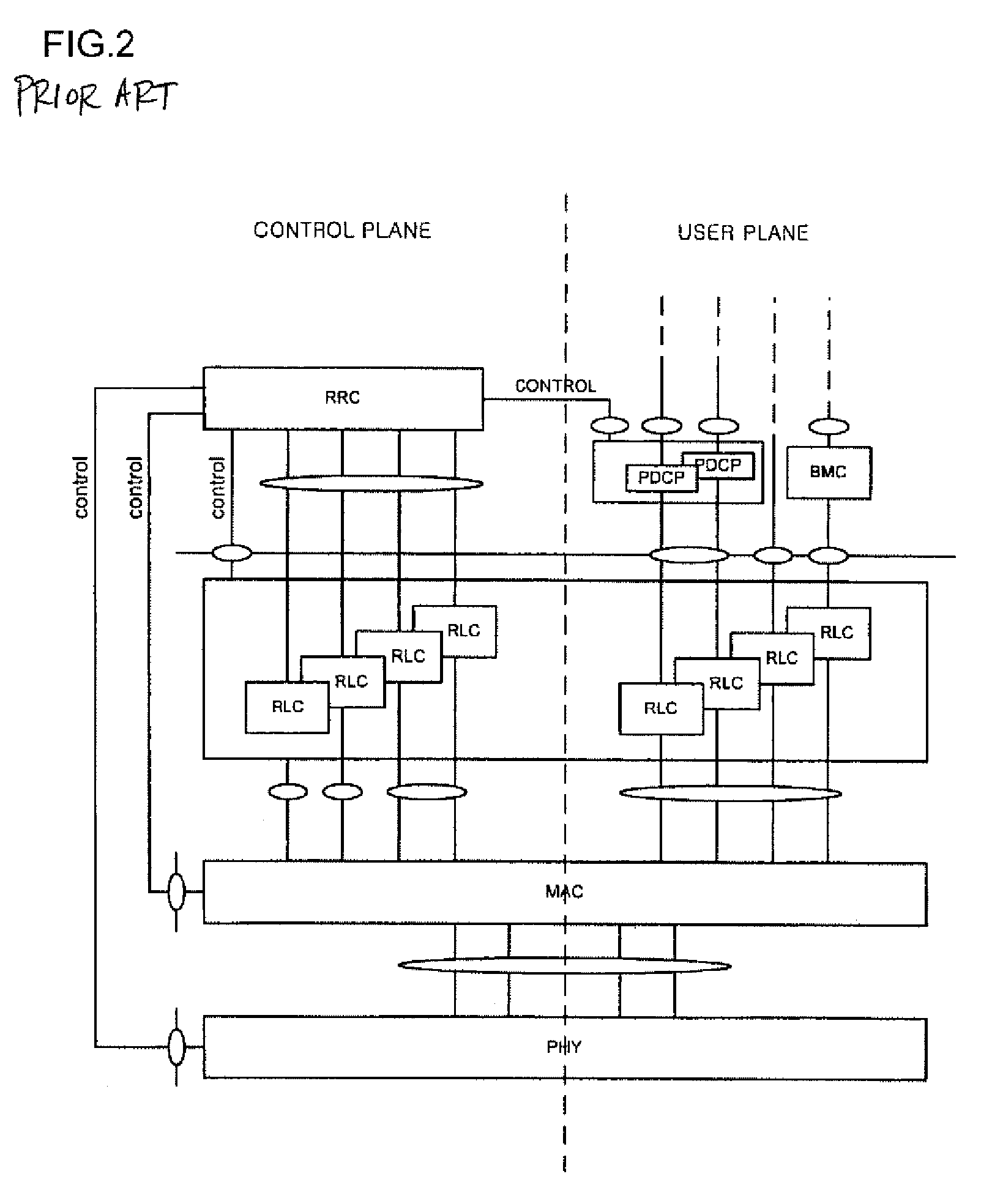

Packet data convergence protocol PDCP entity and execution method thereof

InactiveCN104935413AReduce latencyImprove reliabilityError prevention/detection by using return channelNetwork traffic/resource managementPDCPSerial code

Disclosed are an execution method of a Packet Data Convergence Protocol (PDCP) entity and a corresponding entity apparatus. The method includes: mapping a PDCP Protocol Data Unit (PDCP PDU) which is received from a lower entity of a PCDP entity and arrives in disorder onto a PDCP Service Data Unit (PDCP SDU) and storing PDCP SDU in a reorder buffer; judging whether the serial number of a missing PDCP SDU is smaller than the smaller one of the biggest serial number of the PDCP SDUs respectively received from two lower entities by the PDCP entity; and if the serial number of the missing PDCP SDU is smaller than the smaller one, delivering to a higher layer entity of the PDCP entity the PDCP SDU stored in the reorder buffer with the serial number smaller than the serial number of the missing PDCP SDU, and the PDCP SDU with the serial number bigger than the serial number of the missing PDCP SDU and continuous with the missing PDCP SDU.

Owner:SHARP KK

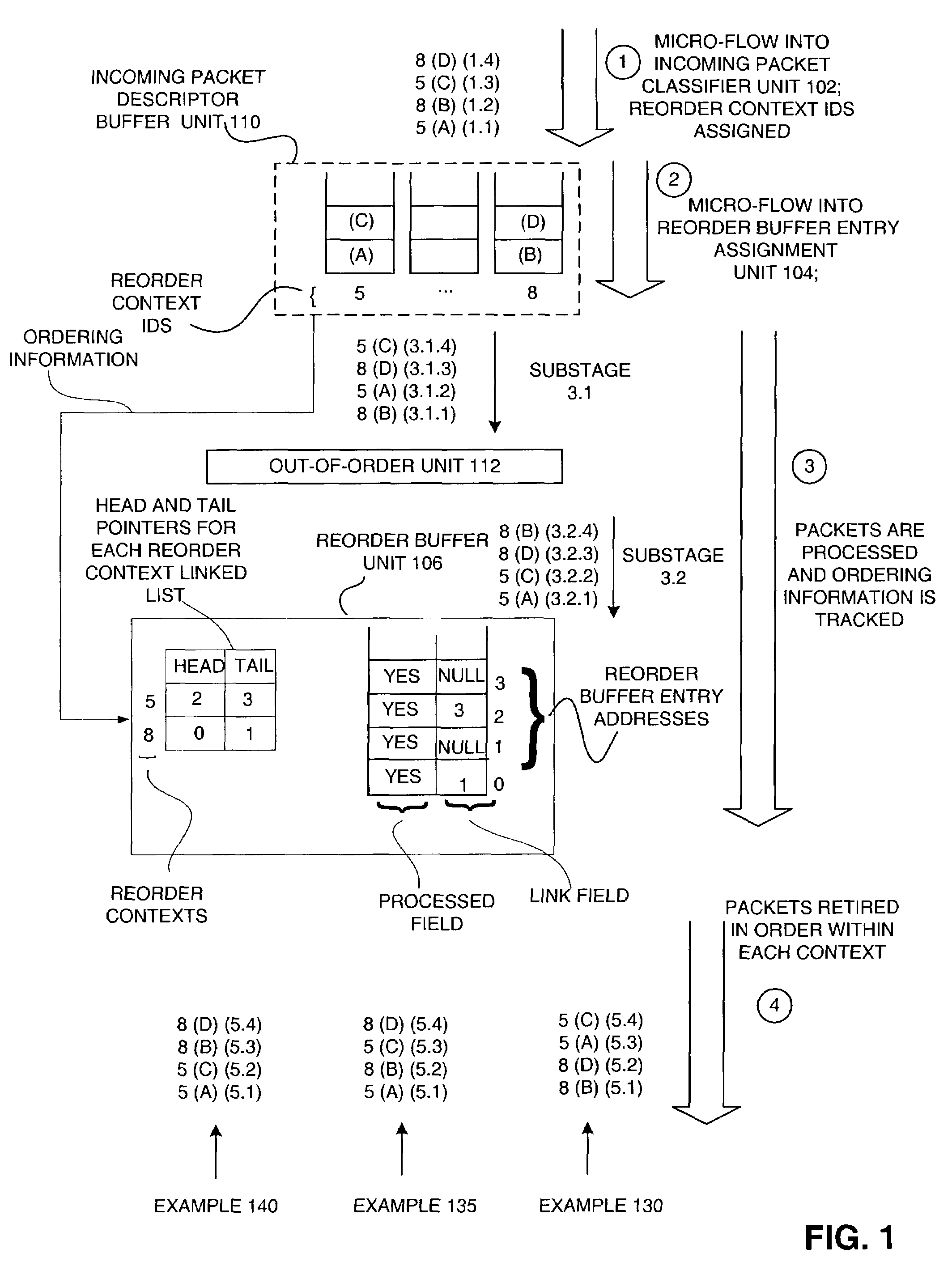

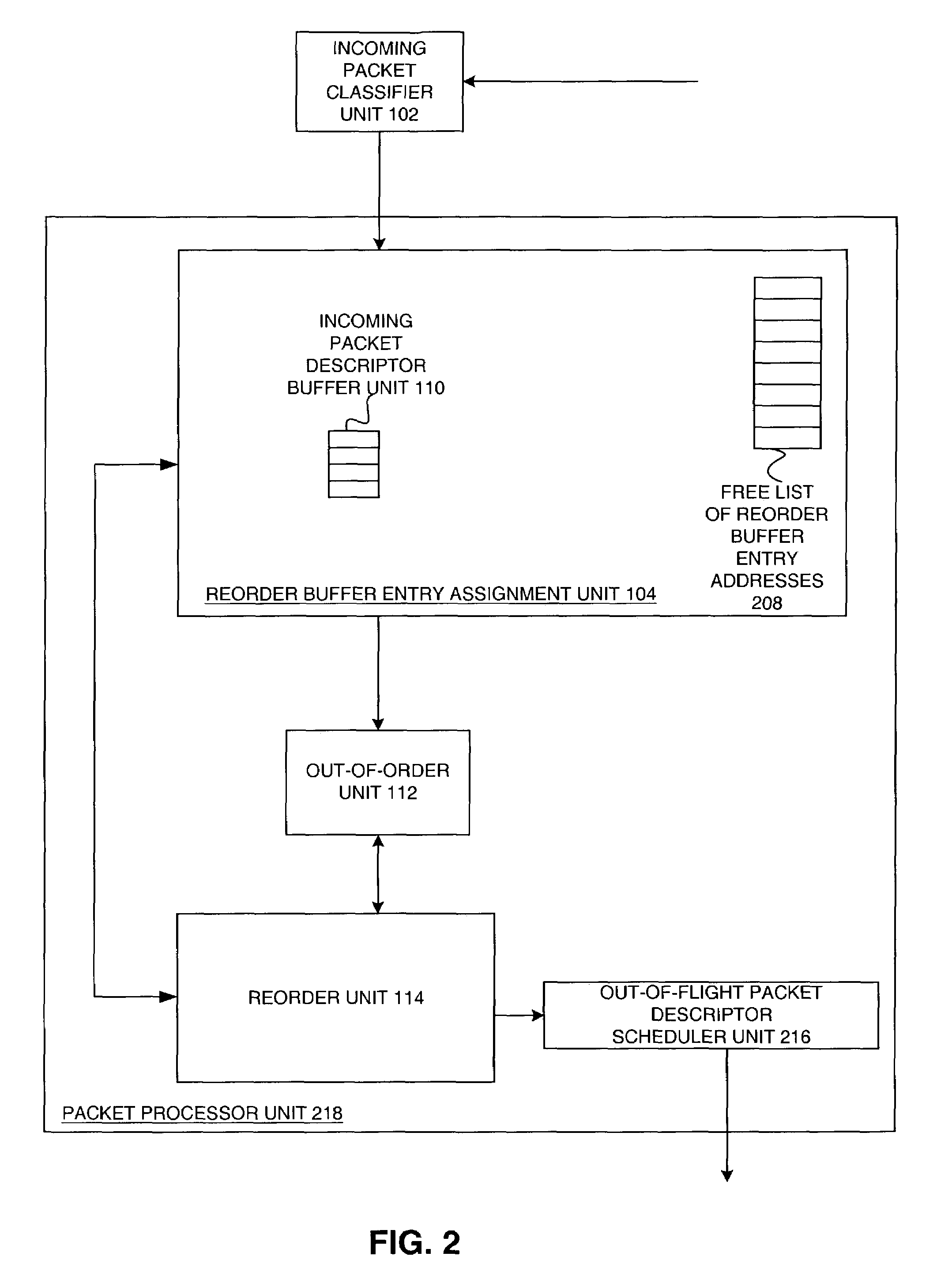

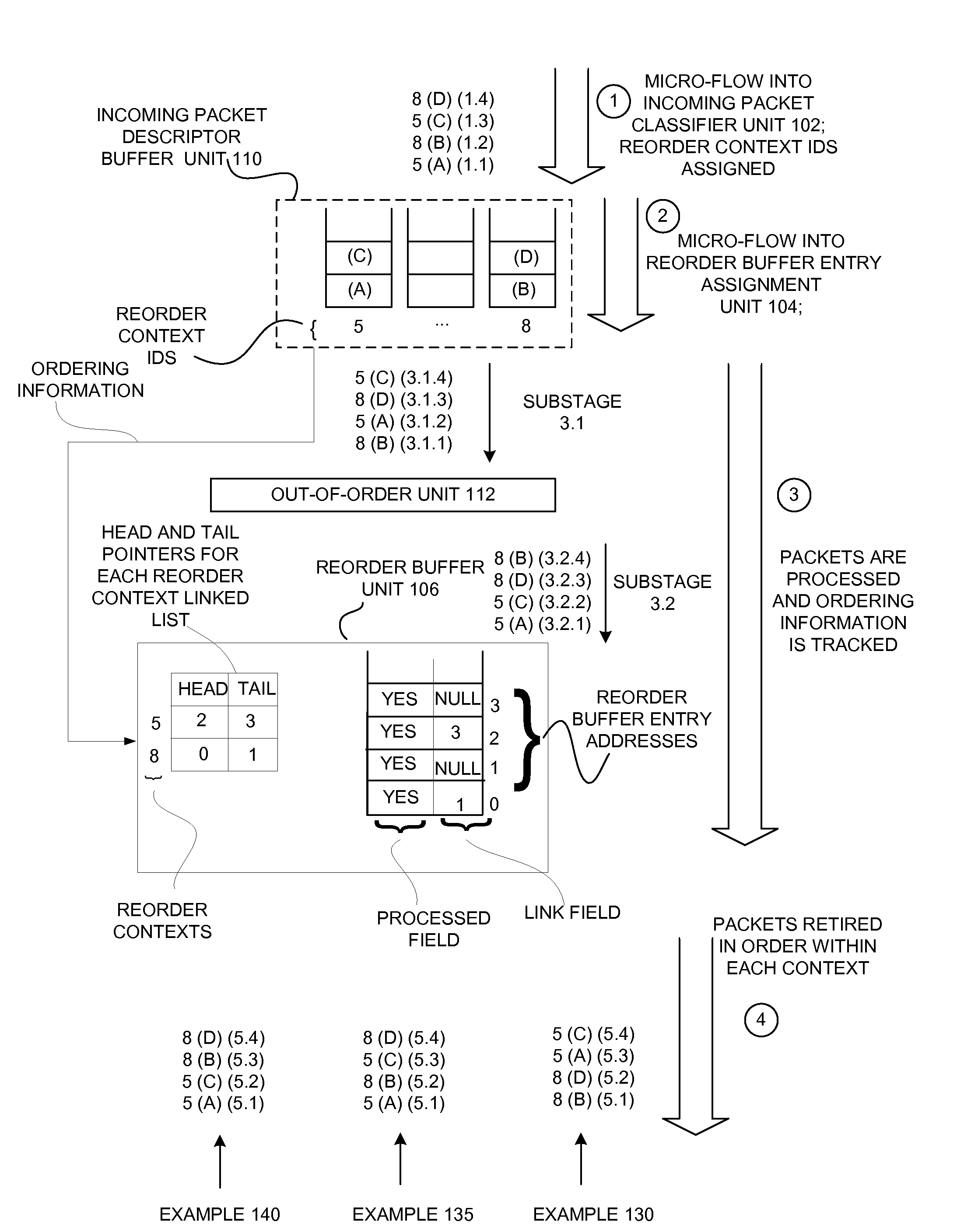

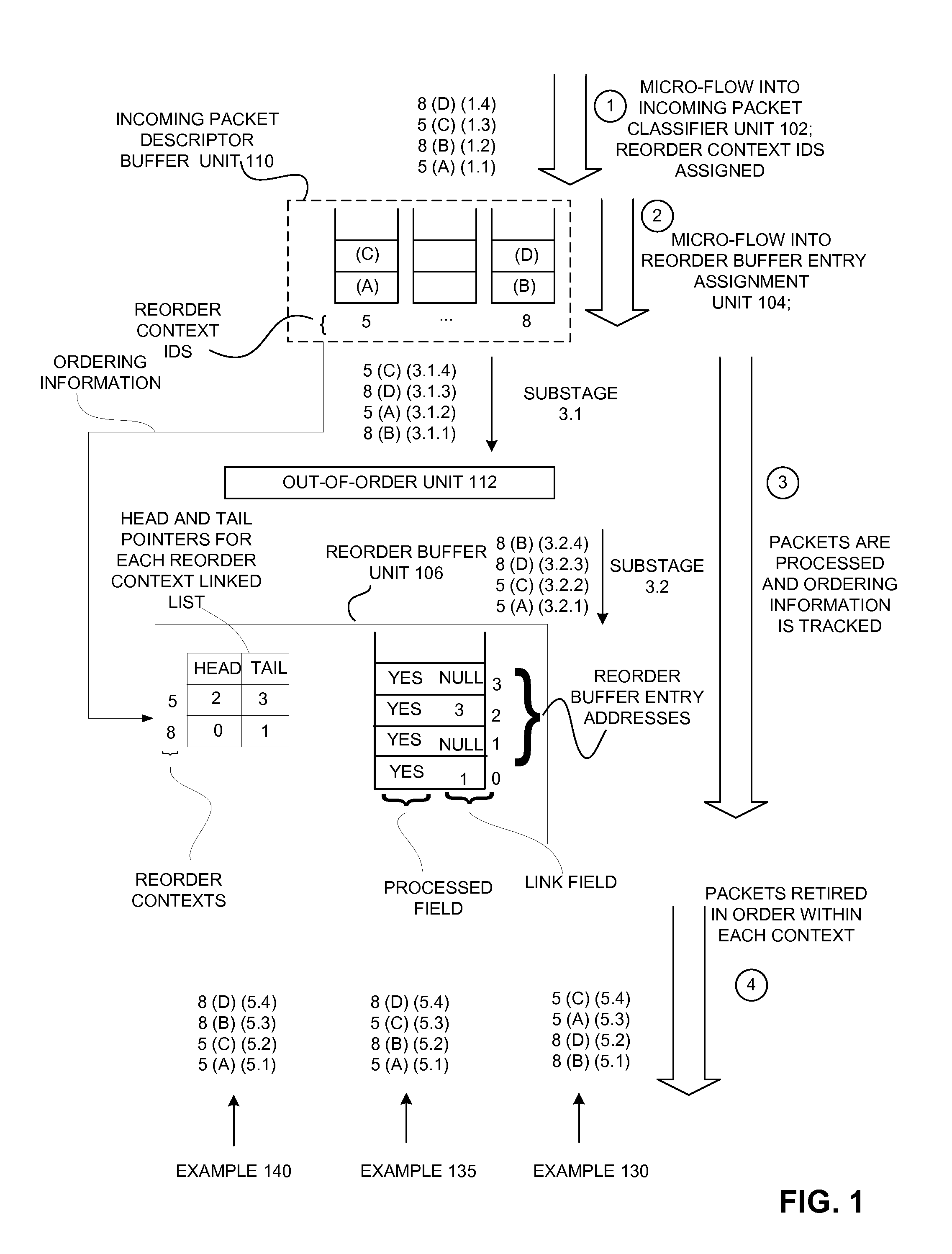

Method and apparatus for out-of-order processing of packets using linked lists

ActiveUS7349399B1Digital computer detailsData switching by path configurationOrder processingLinked list

These and other aspects of the present invention will be better described with reference to the Detailed Description and the accompanying figures. A method and apparatus for out-of-order processing of packets using linked lists is described. In one embodiment, the method includes receiving packets in a global order, the packets being designated for different ones of a plurality of reorder contexts. The method also includes storing information regarding each of the packets in a shared reorder buffer. The method also includes for each of the plurality of reorder contexts, maintaining a reorder context linked list that records the order in which those of the packets that were designated for that reorder context and that are currently stored in the shared reorder buffer were received relative to the global order. The method also includes completing processing of at least certain of the packets out of the global order and retiring the packets from the shared reorder buffer out of the global order for at least certain of the packets.

Owner:TELEFON AB LM ERICSSON (PUBL)

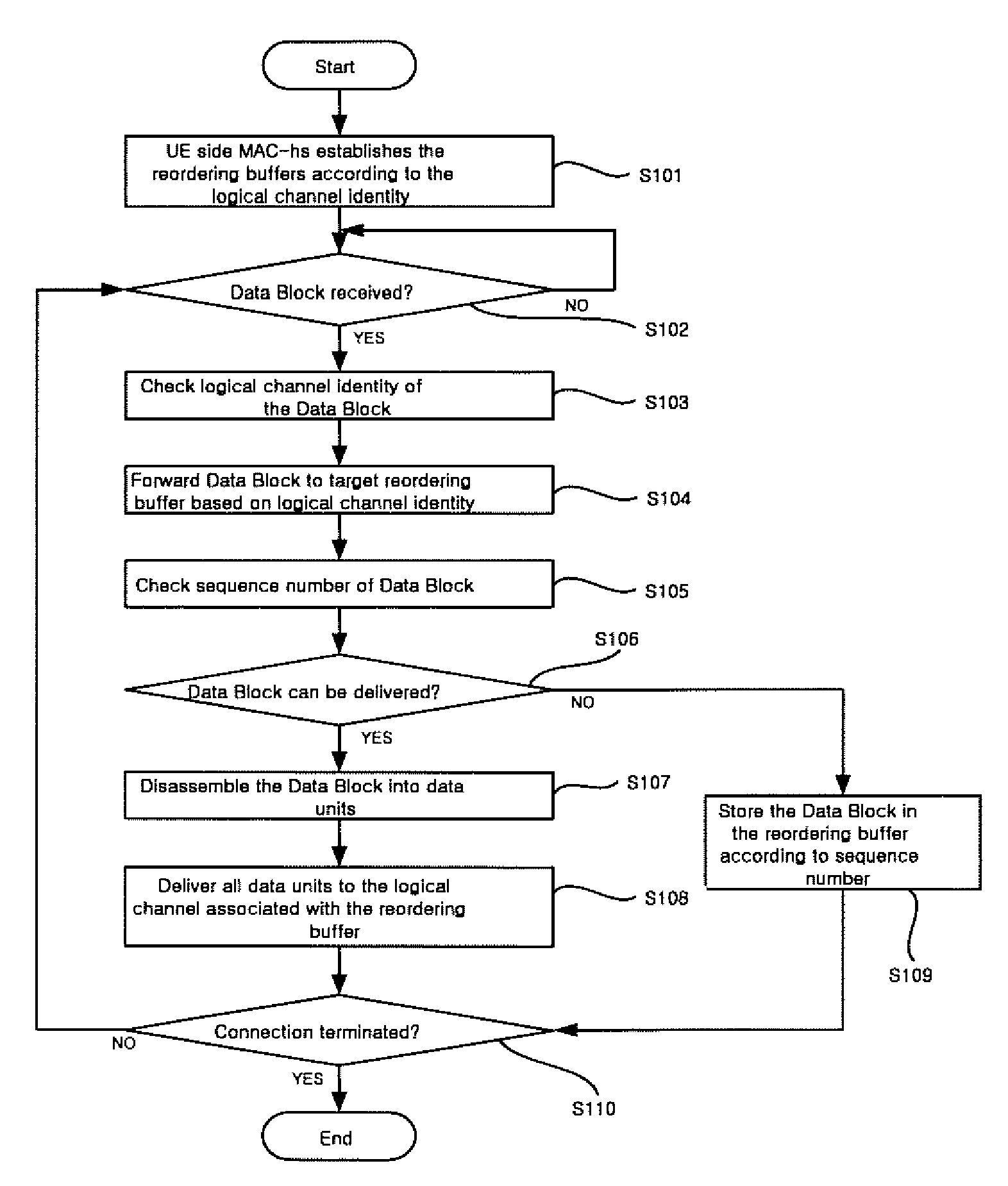

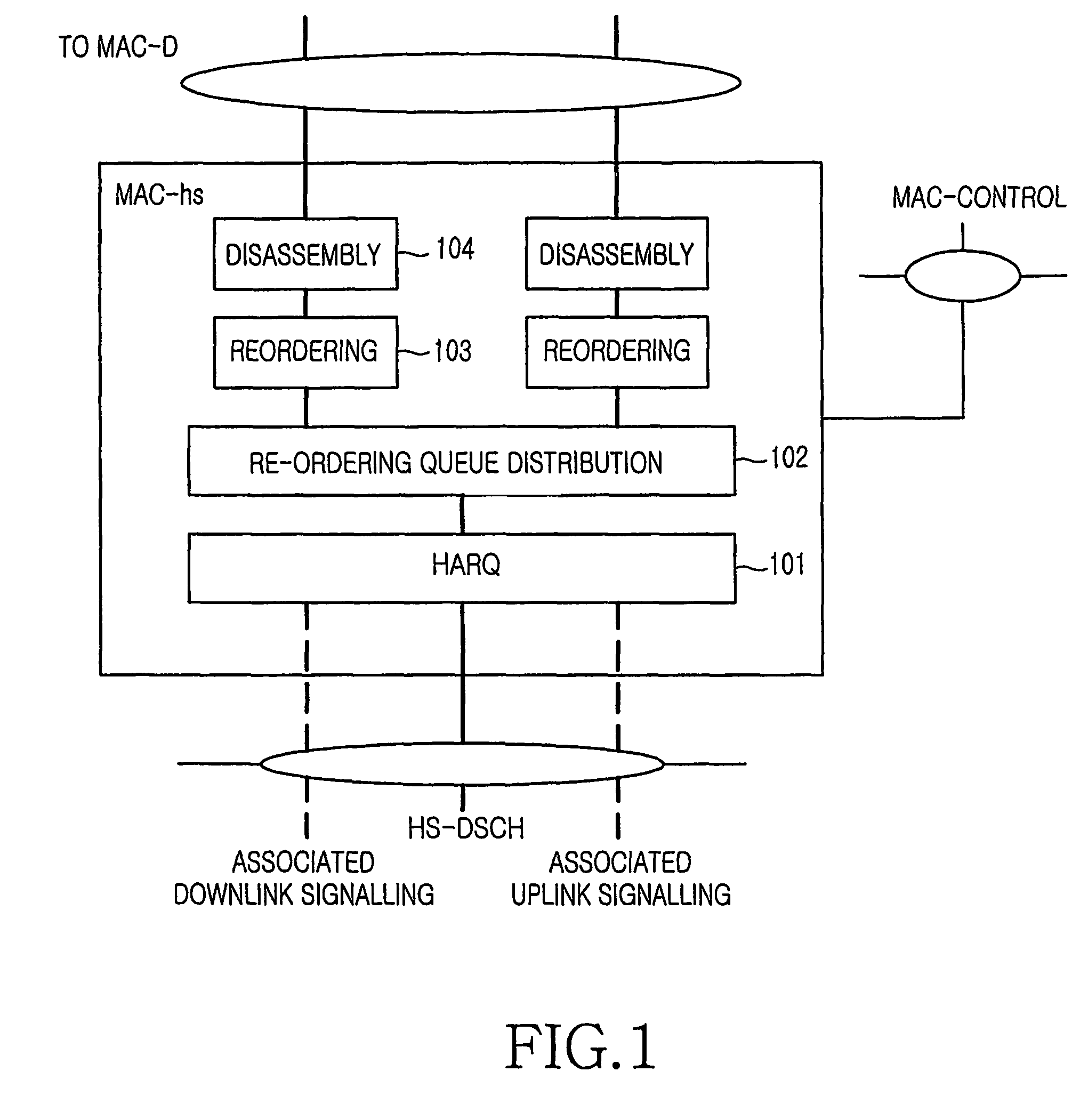

Data transmission method for HSDPA

ActiveUS7403541B2Delay minimizationFacilitate transmissionNetwork traffic/resource managementTime-division multiplexMultiplexingData transmission

In the data transmission method of an HSDPA system according to the present invention, a transmitter transmits Data Blocks each composed of one or more data units originated from a same logical channel, and a receiver receives the Data Block through a HS-DSCH and distributes the Data Block to a predetermined reordering buffer. Since each Data Block is composed of the MAC-d PDUs originated from the same logical channel, it is possible to monitor the in-sequence delivery of the data units, resulting in reduction of undesirable queuing delay caused by logical channel multiplexing.

Owner:LG ELECTRONICS INC

Method and Apparatus for Out-of-Order Processing of Packets using Linked Lists

These and other aspects of the present invention will be better described with reference to the Detailed Description and the accompanying figures. A method and apparatus for out-of-order processing of packets using linked lists is described. In one embodiment, the method includes receiving packets in a global order, the packets being designated for different ones of a plurality of reorder contexts. The method also includes storing information regarding each of the packets in a shared reorder buffer. The method also includes for each of the plurality of reorder contexts, maintaining a reorder context linked list that records the order in which those of the packets that were designated for that reorder context and that are currently stored in the shared reorder buffer were received relative to the global order. The method also includes completing processing of at least certain of the packets out of the global order and retiring the packets from the shared reorder buffer out of the global order for at least certain of the packets.

Owner:TELEFON AB LM ERICSSON (PUBL)

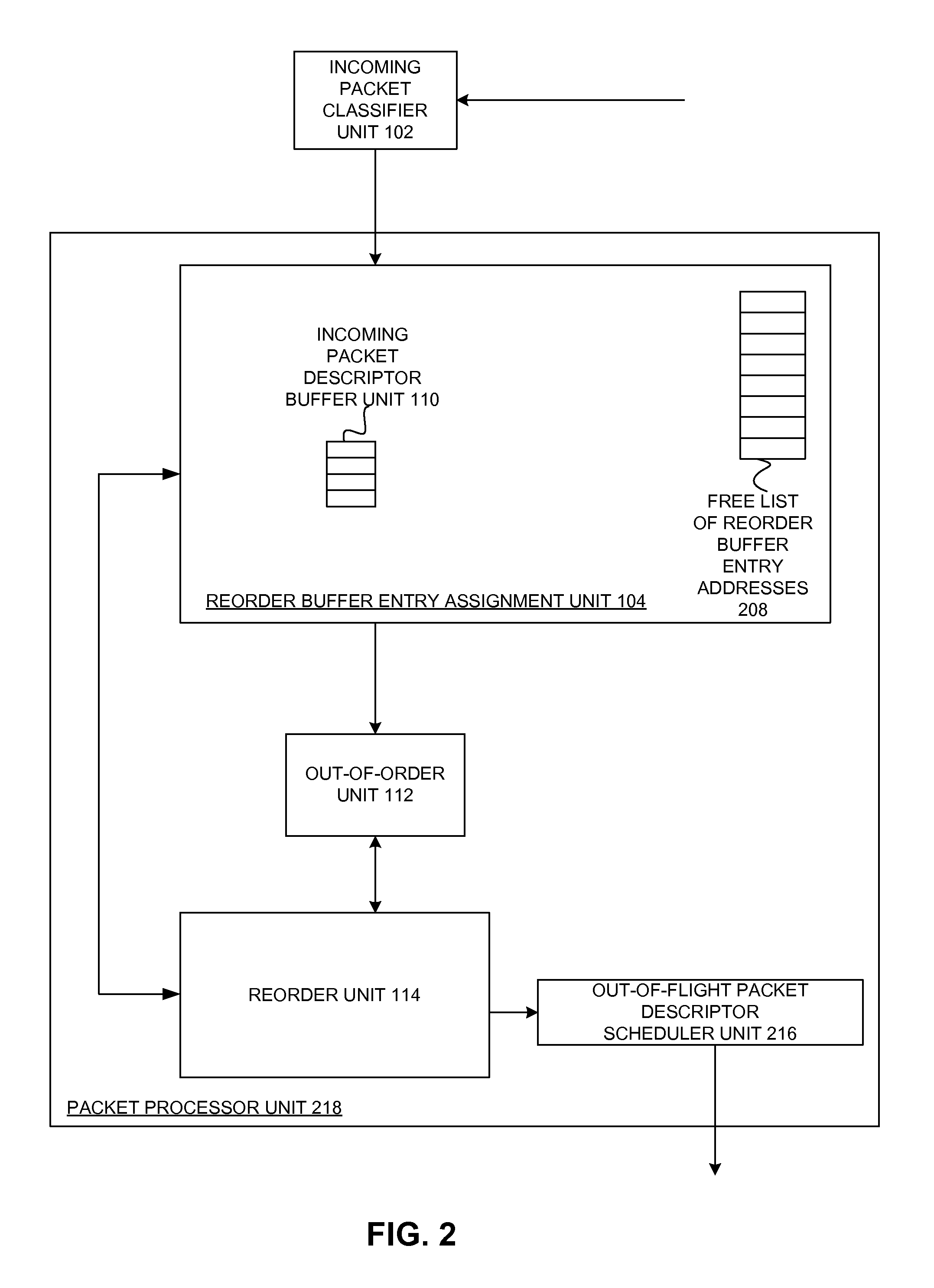

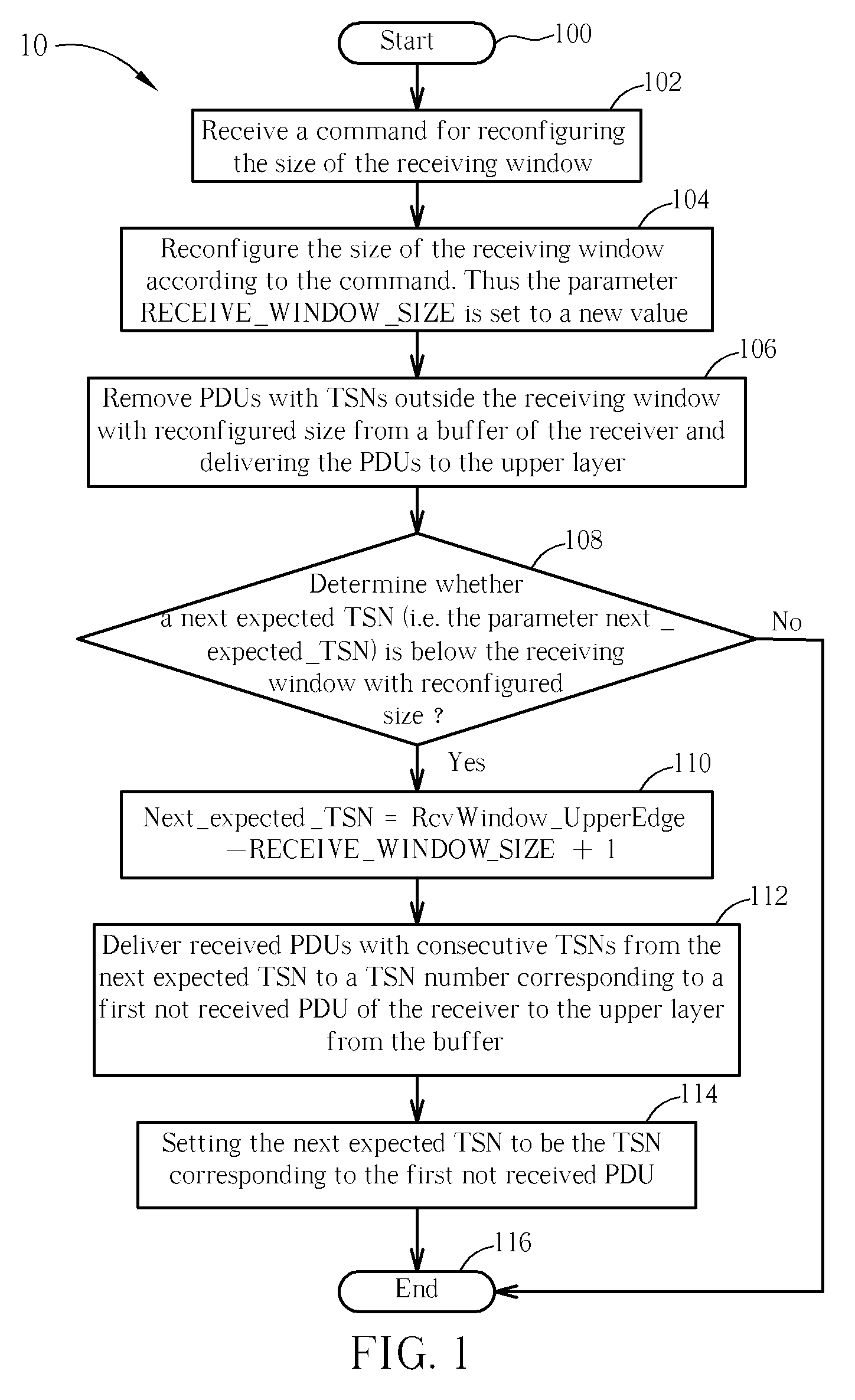

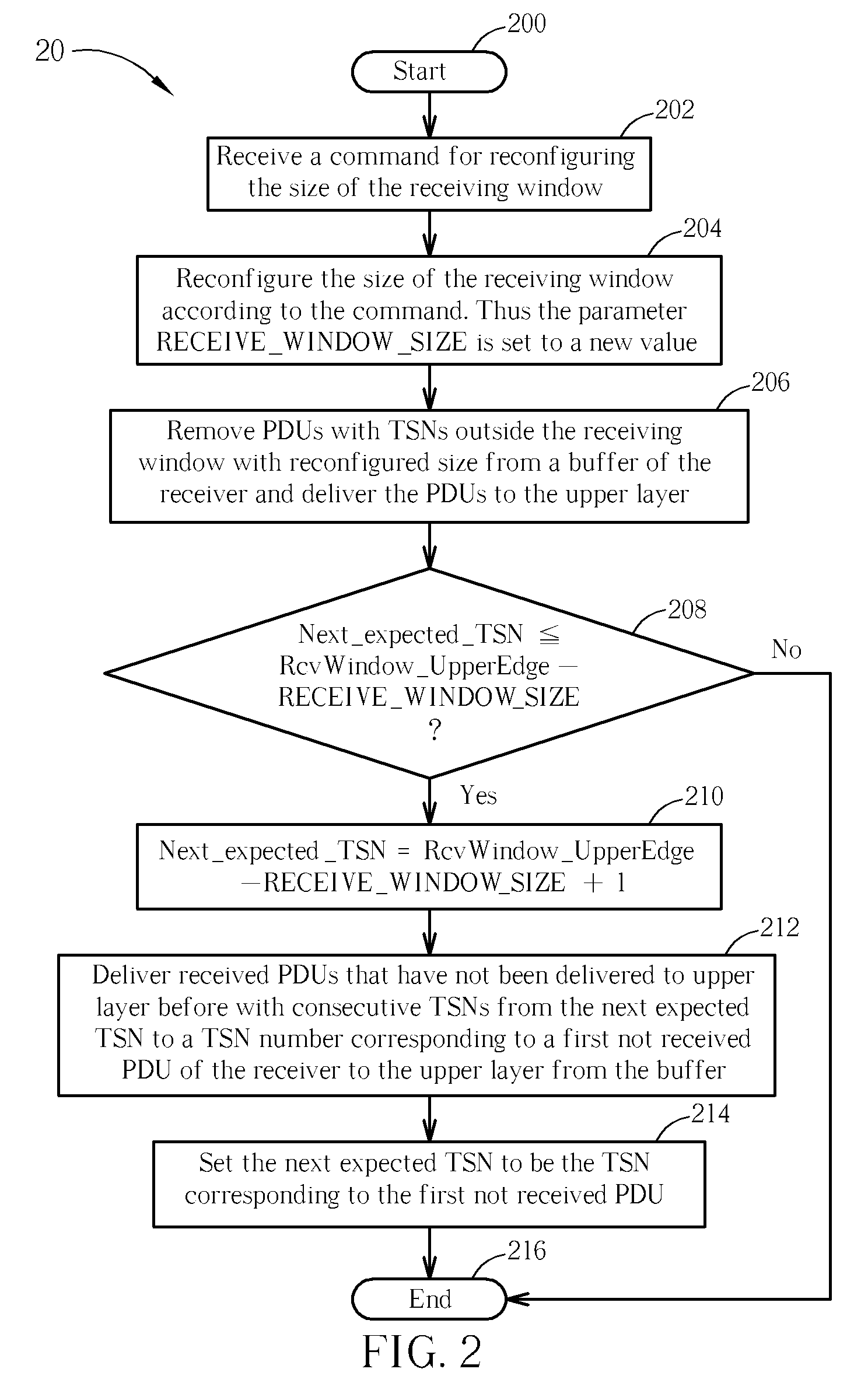

Method and Related Apparatus for Reconfiguring Size of a Receiving Window in a Communications System

ActiveUS20060221833A1Reduce memory sizeReduce window sizeError prevention/detection by using return channelSynchronising transmission/receiving encryption devicesCommunications systemRe-order buffer

A method for reconfiguring size of a receiving window in a communications system avoiding duplicate packet delivery to an upper layer to keep ciphering parameters in synchronization when the communications system reconfigures a receiving window of a receiver includes receiving a command for reconfiguring a size of the receiving window, reconfiguring the size of the receiving window according to the command, removing packets with sequence numbers outside the receiving window from buffers of the receiver and delivering the packets to the upper layer, determining whether a sequence number of a next expected packet is below the receiving window, and keeping the sequence number of the next expected packet and the packets in a reordering buffer of the receiver unchanged when the sequence number of the next expected packet is not below the receiving window.

Owner:INNOVATIVE SONIC

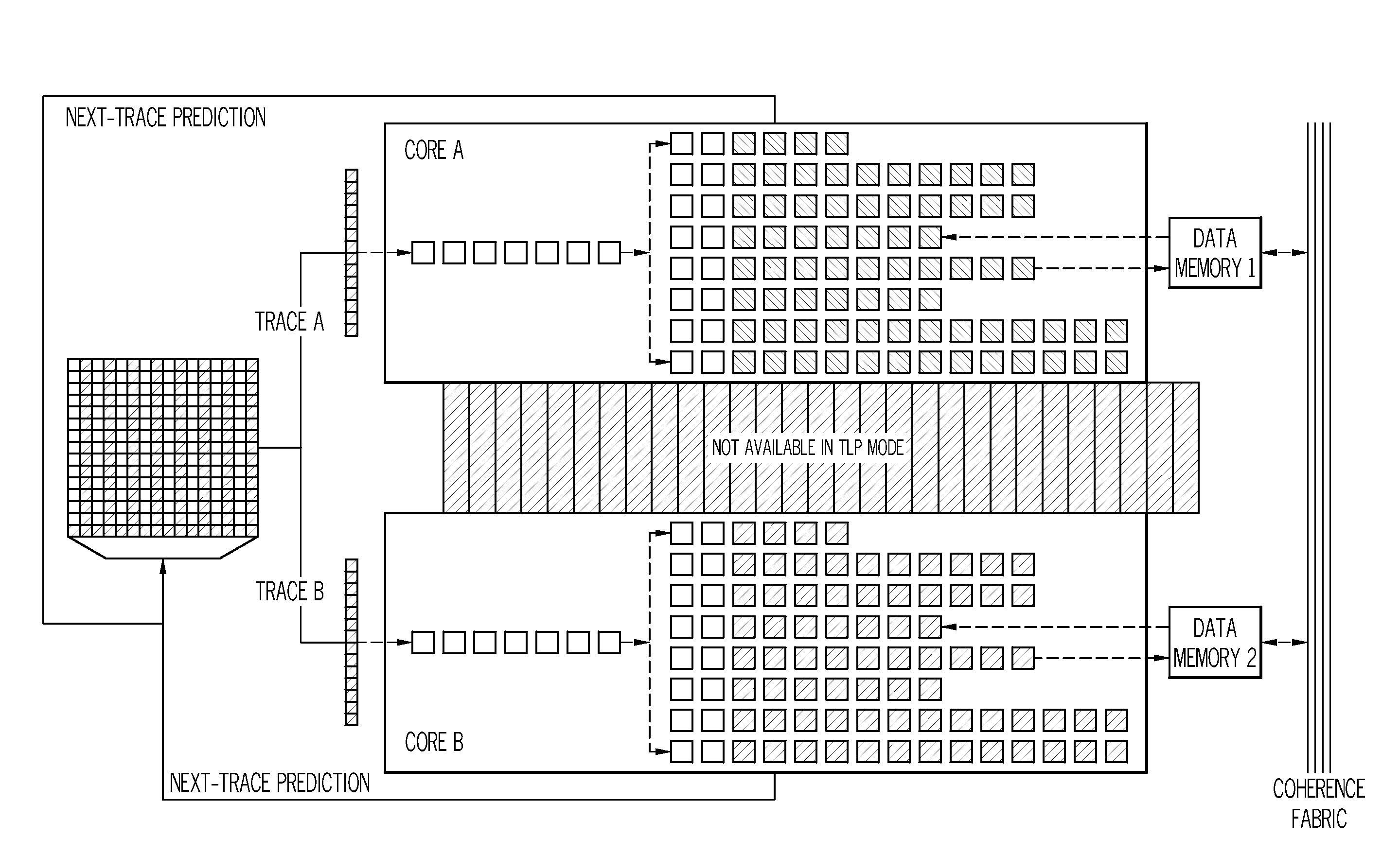

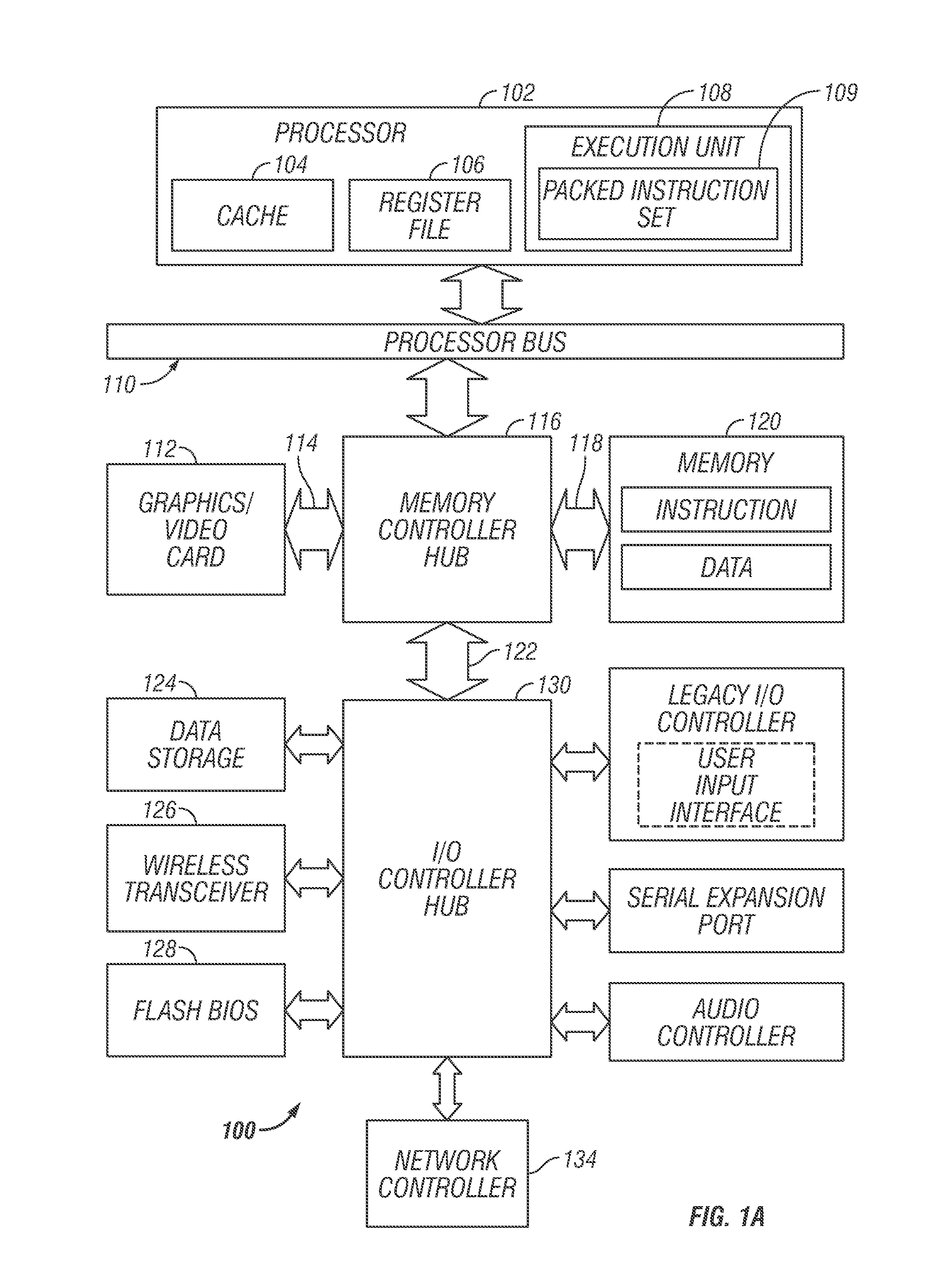

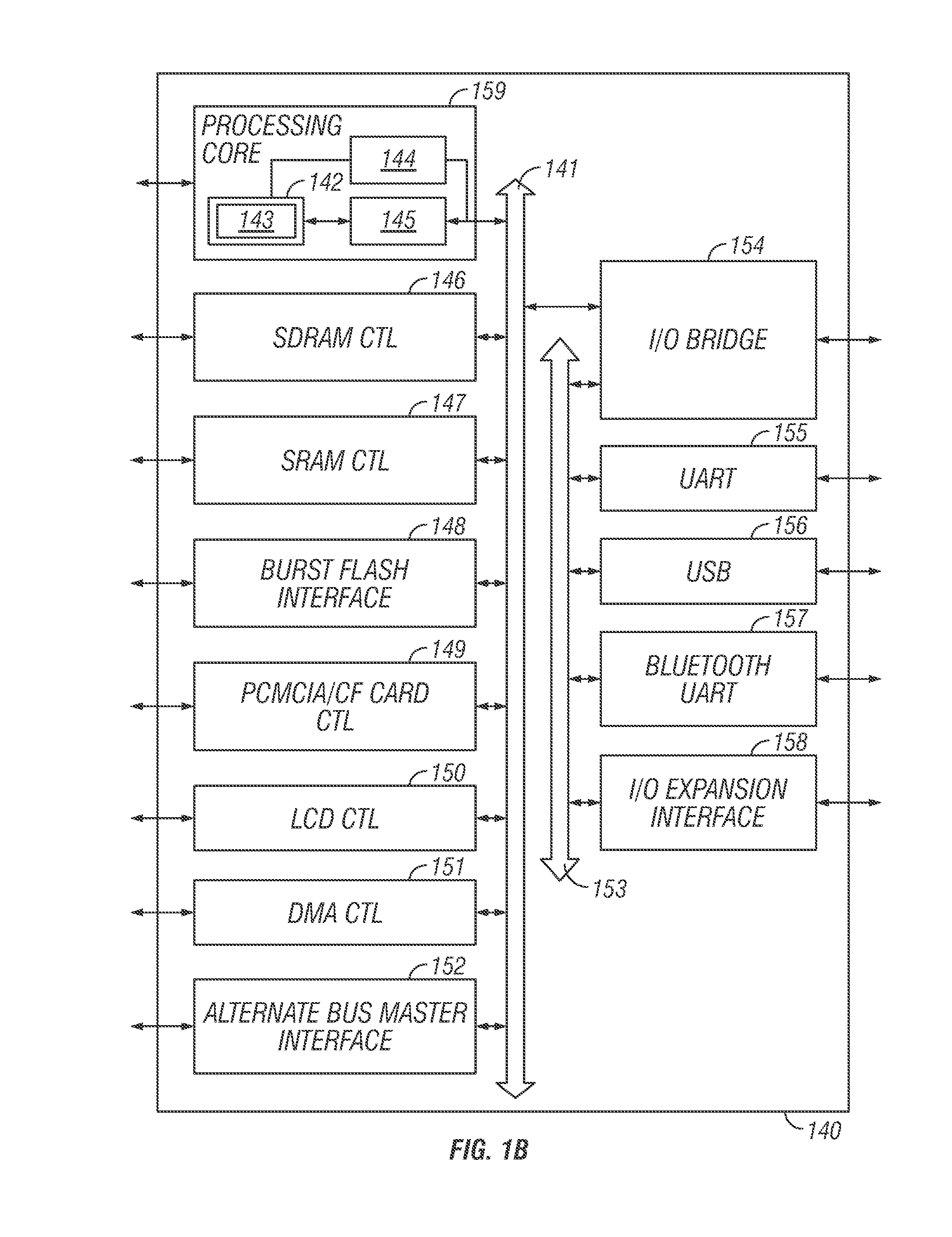

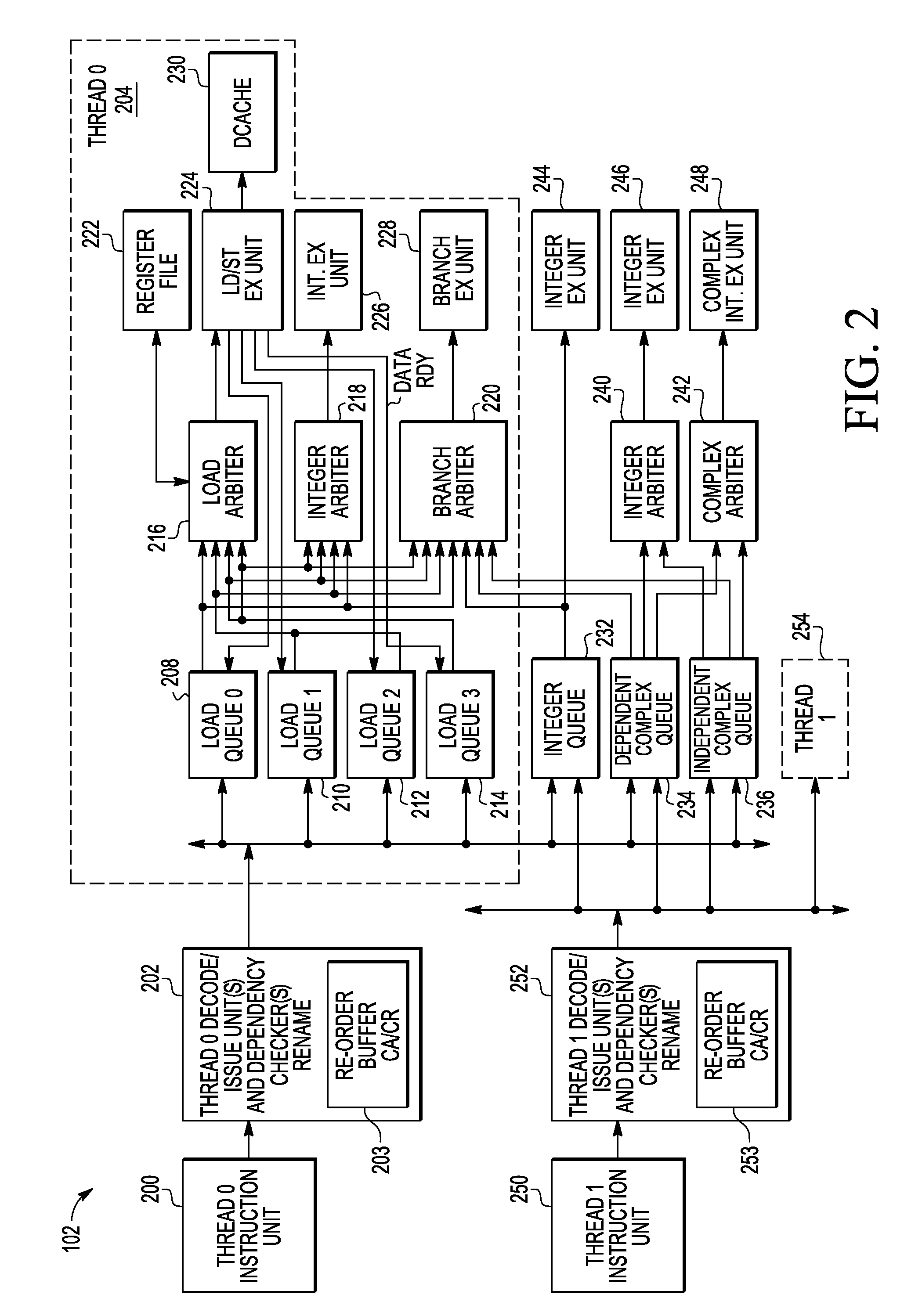

Computer processing system employing an instruction reorder buffer

InactiveUS20080162890A1General purpose stored program computerSpecific program execution arrangementsHandling systemRe-order buffer

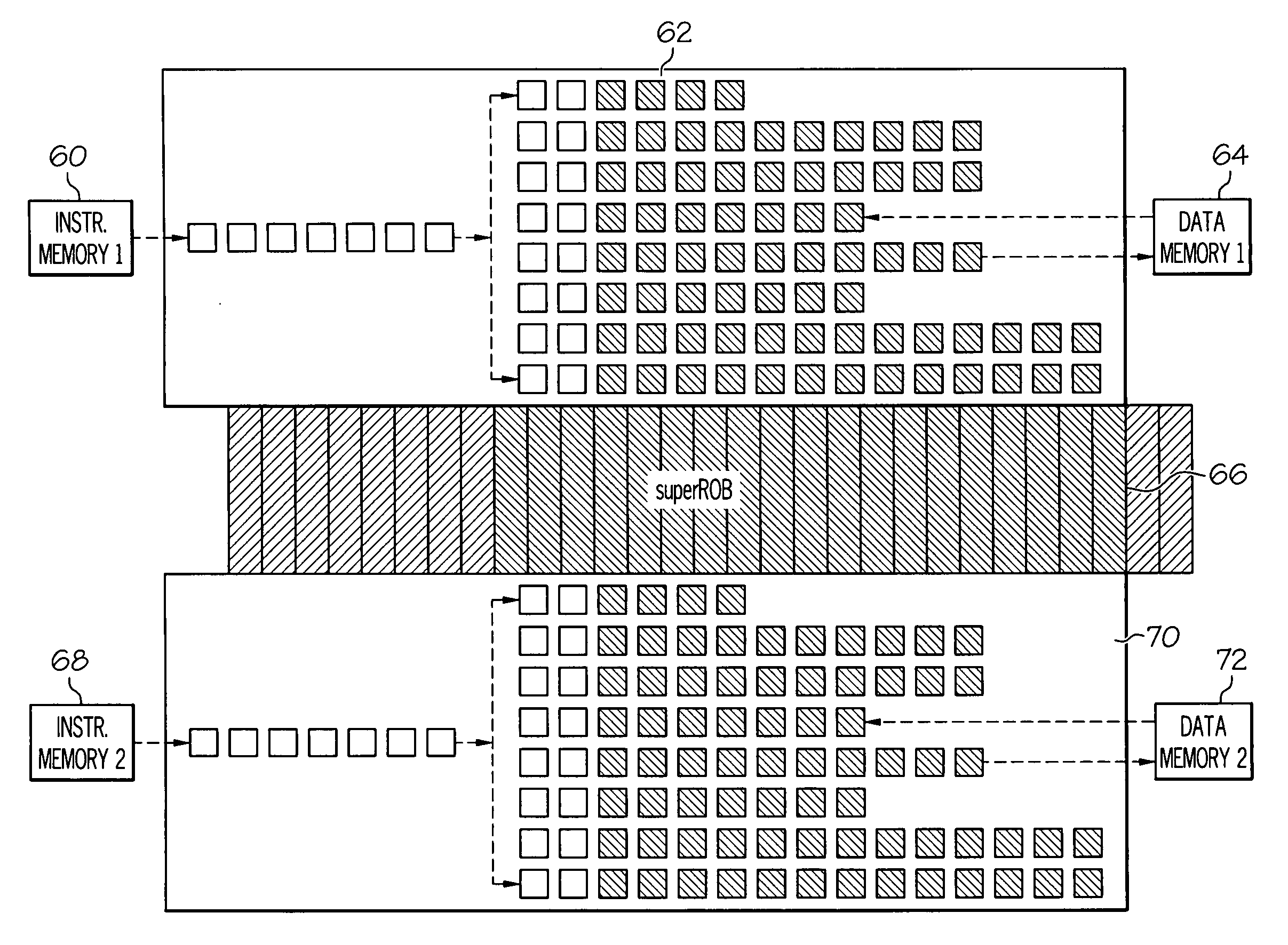

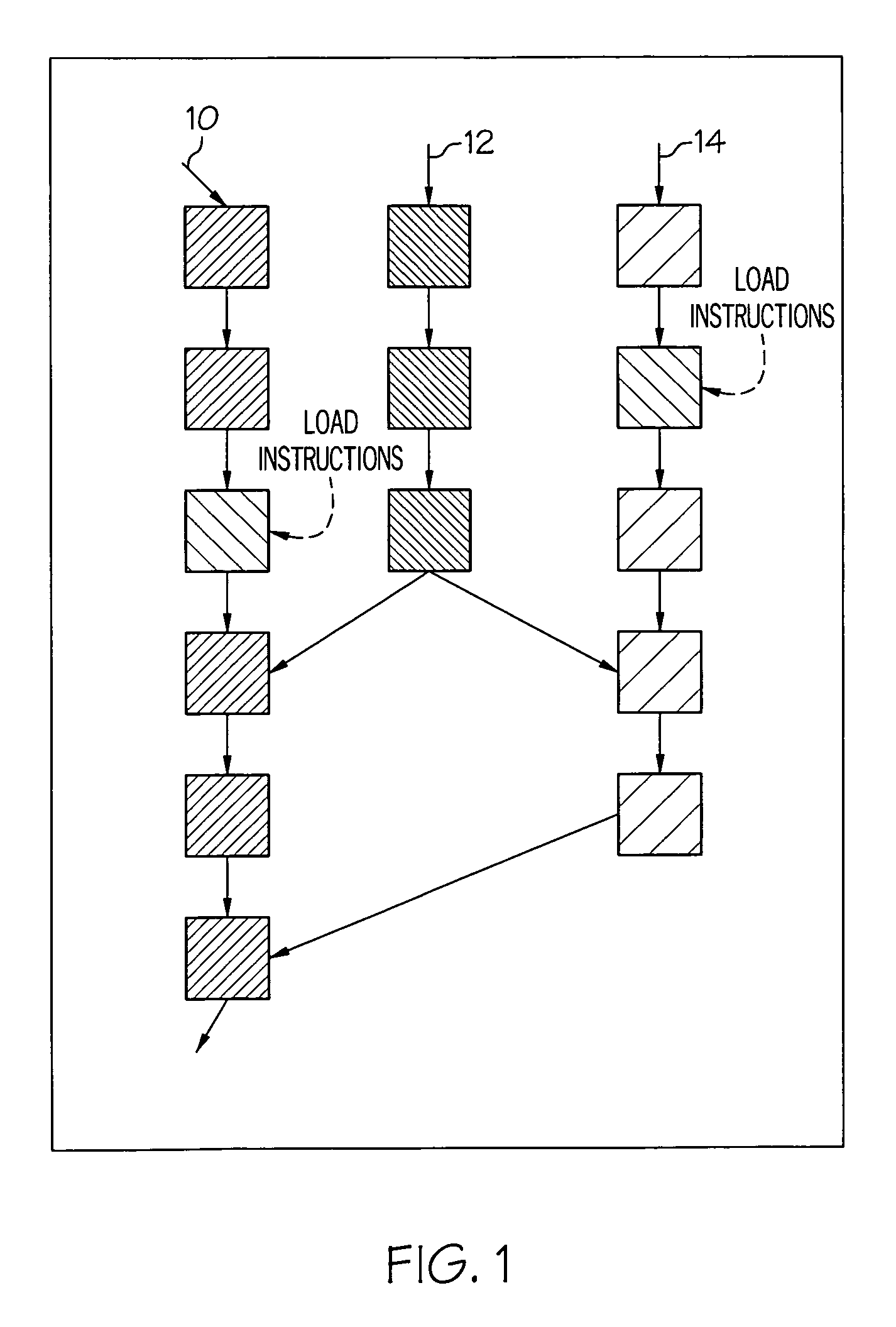

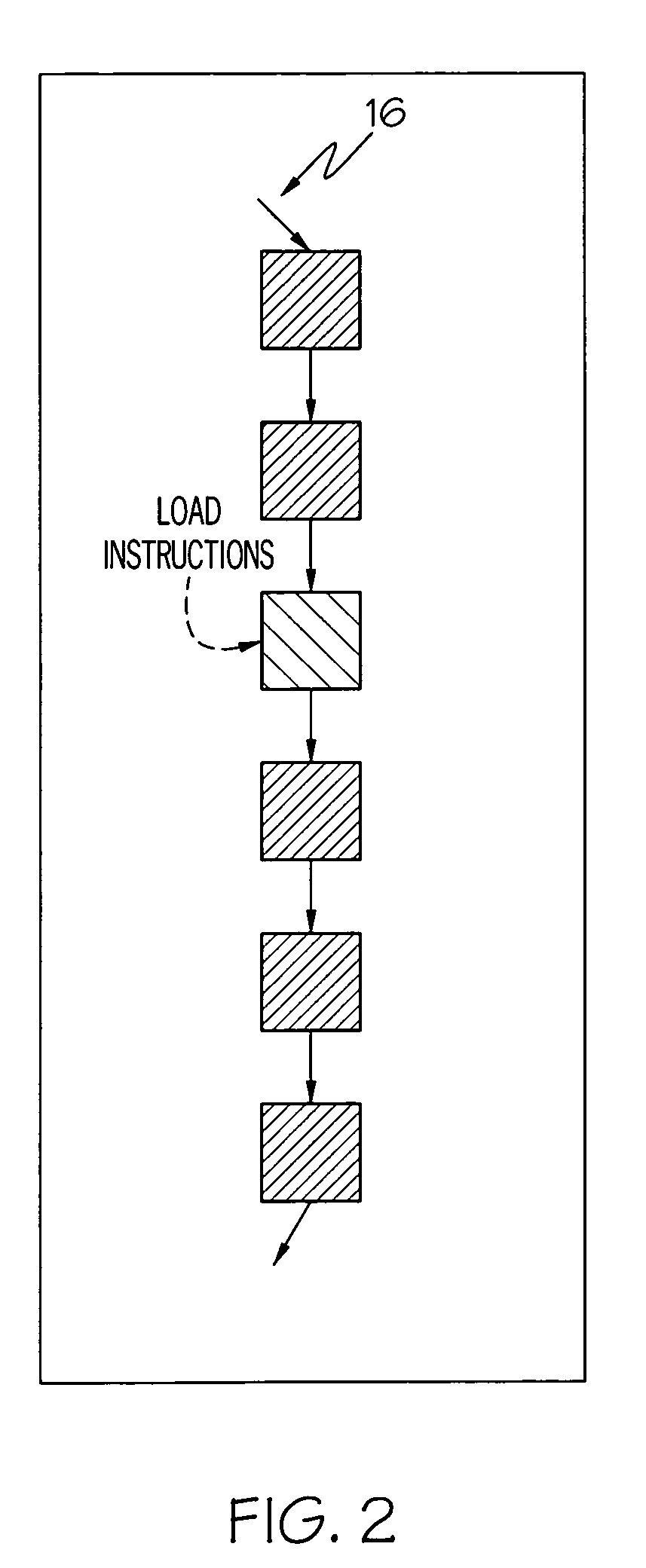

A method and a system for operating a plurality of processors that each includes an execution pipeline for processing dependence chains, the method comprising: configuring the plurality of processors to execute the dependence chains on execution pipelines; implementing a Super Re-Order Buffer (SuperROB) in which received instructions are re-ordered after out-of-order execution when at least one of the plurality of processors is in an Instruction Level Parallelism (ILP) mode and at least one of the plurality of processors has a Thread Level Parallelism (TLP) core; detecting an imbalance in a dispatch of instructions of a first dependence chain compared to a dispatch of instructions of a second dependence chain with respect to dependence chain priority; determining a source of the imbalance; and activating the ILP mode when the source of the imbalance has been determined.

Owner:INT BUSINESS MASCH CORP

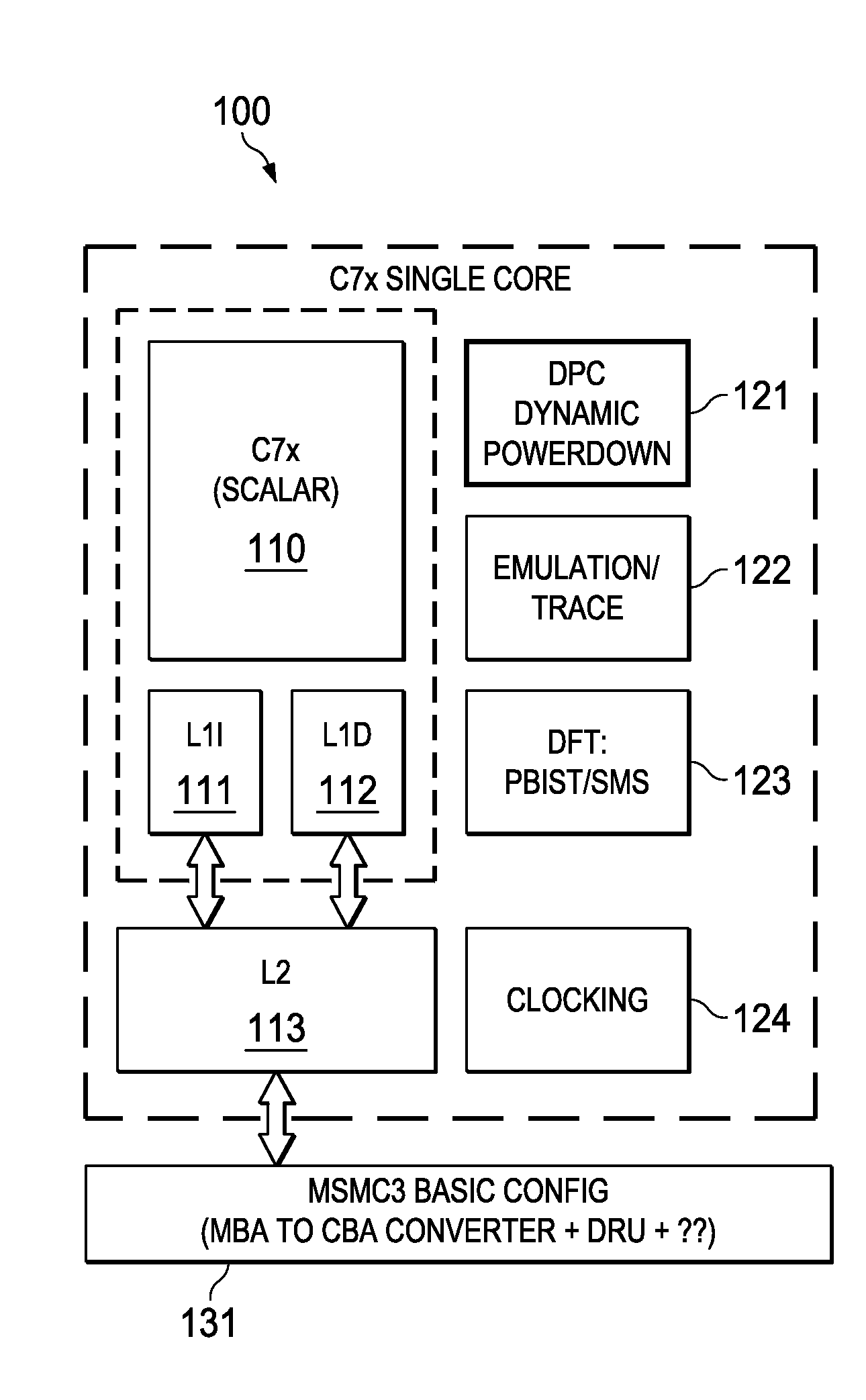

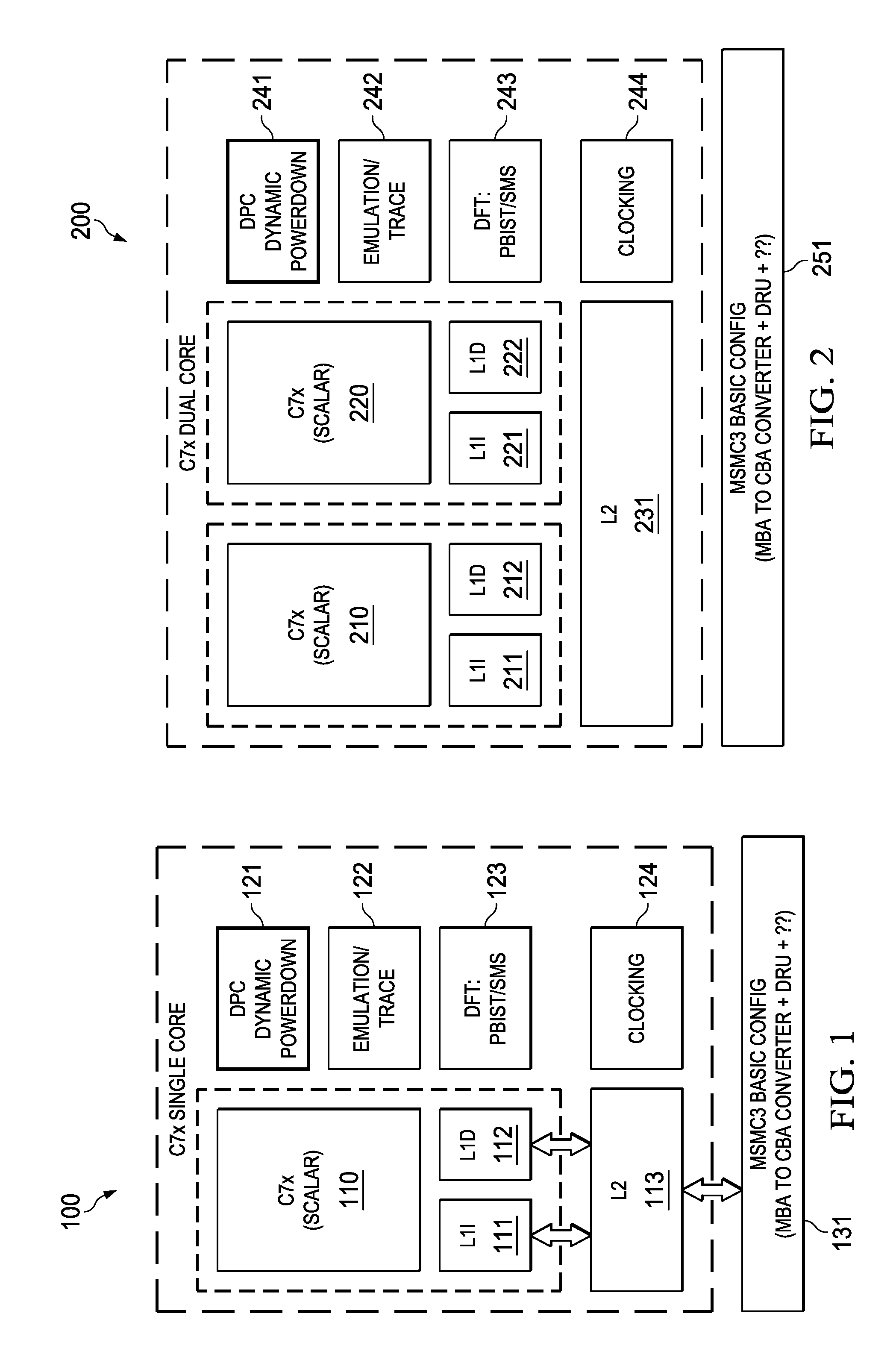

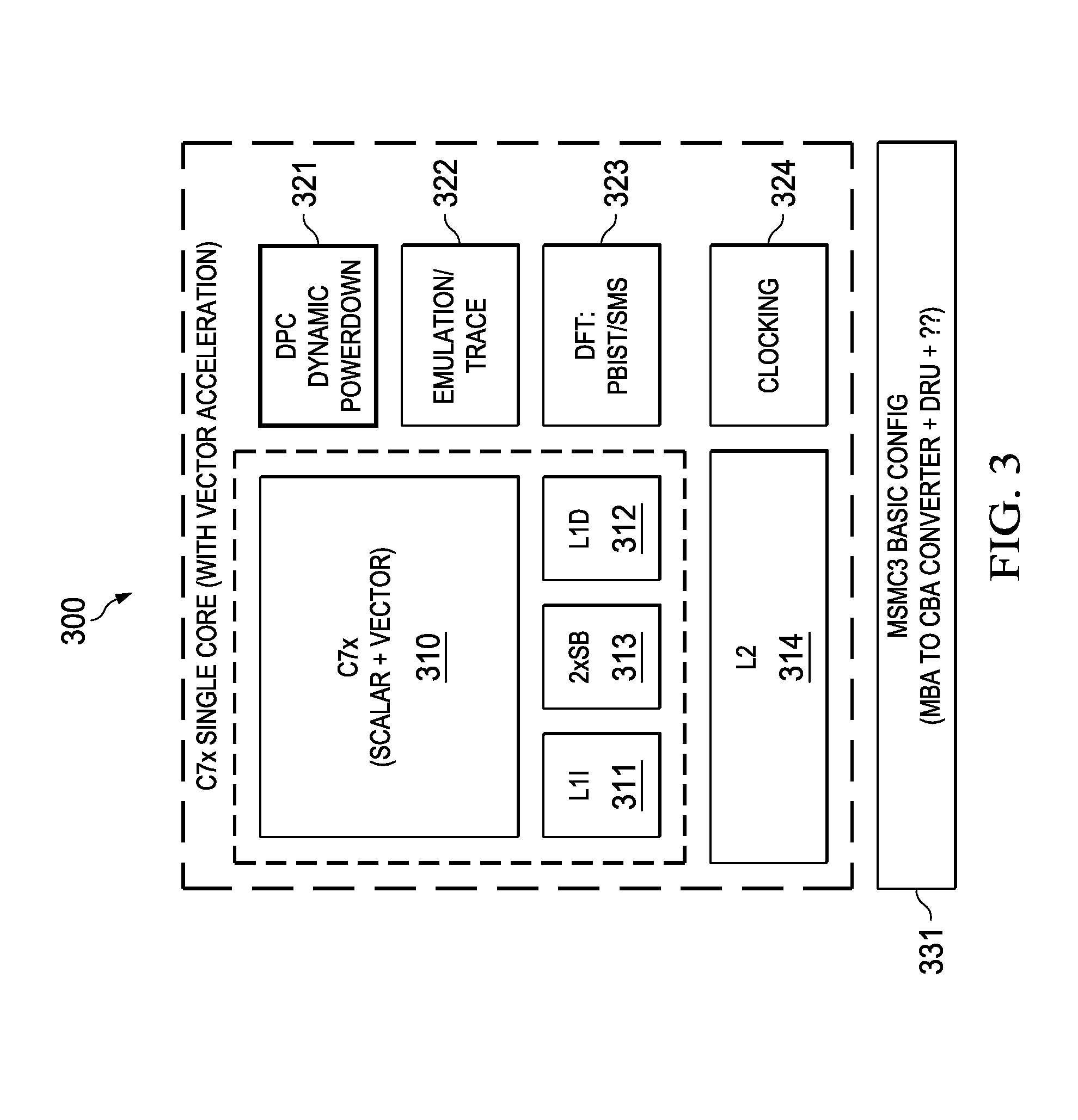

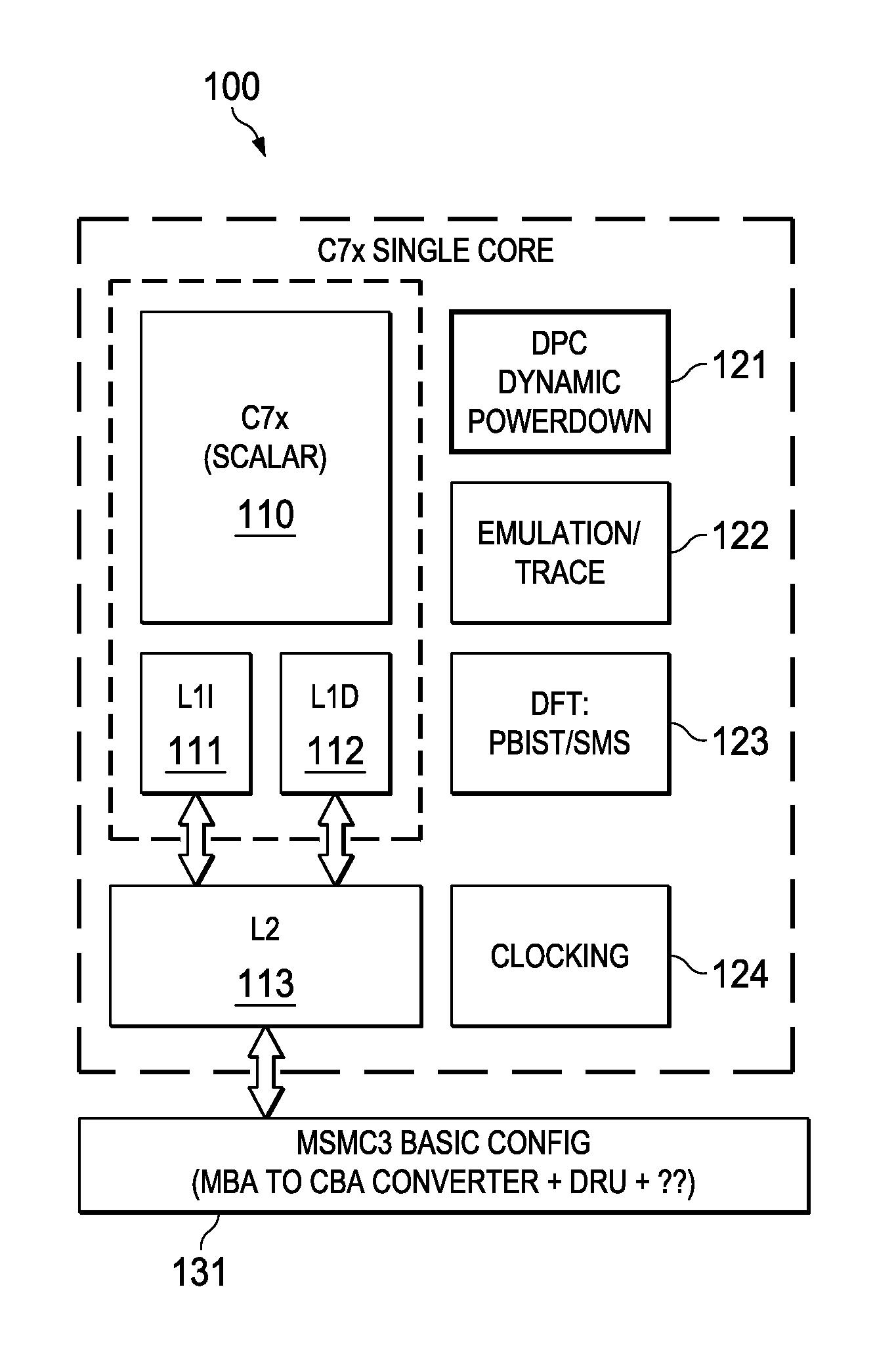

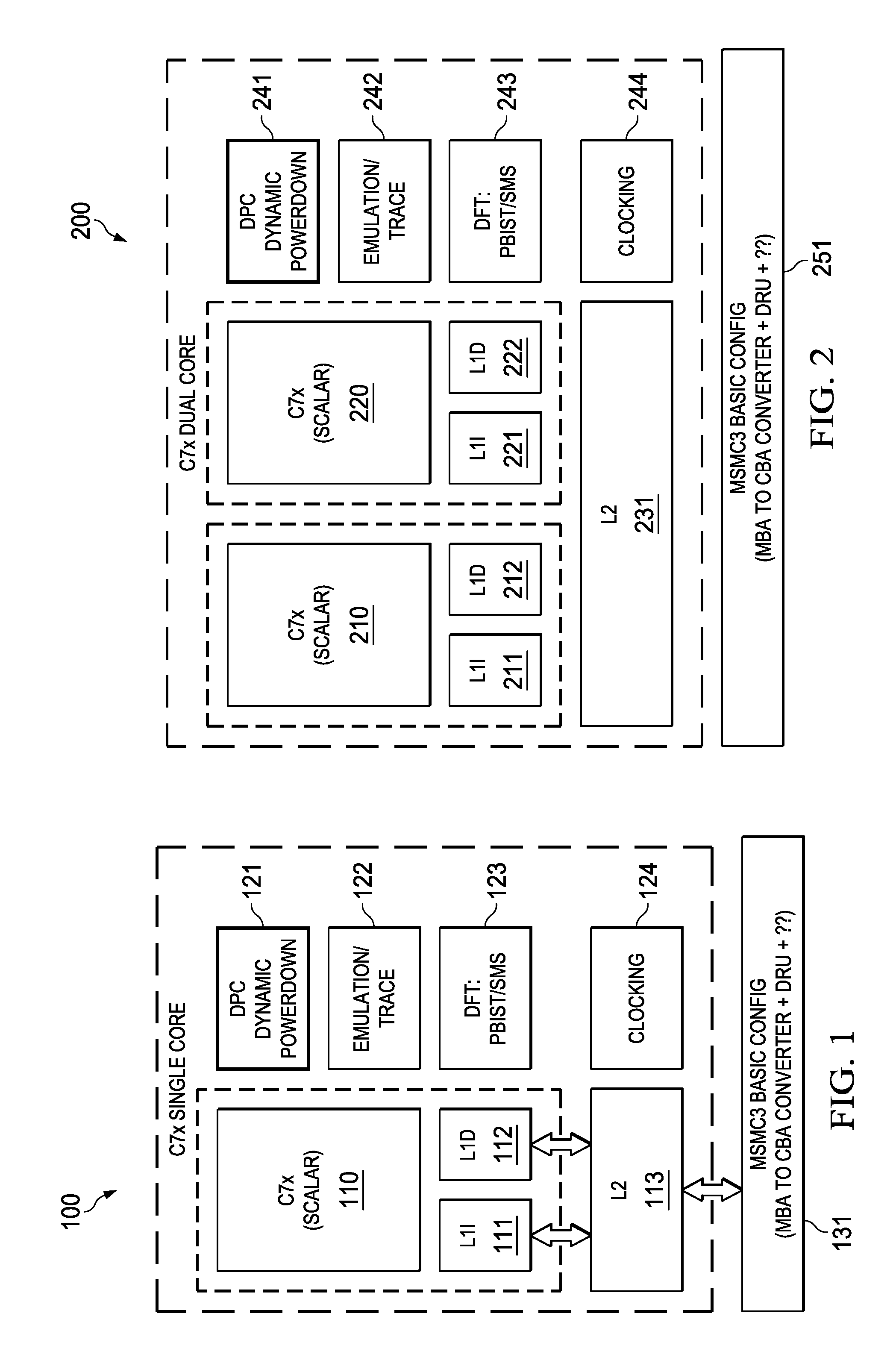

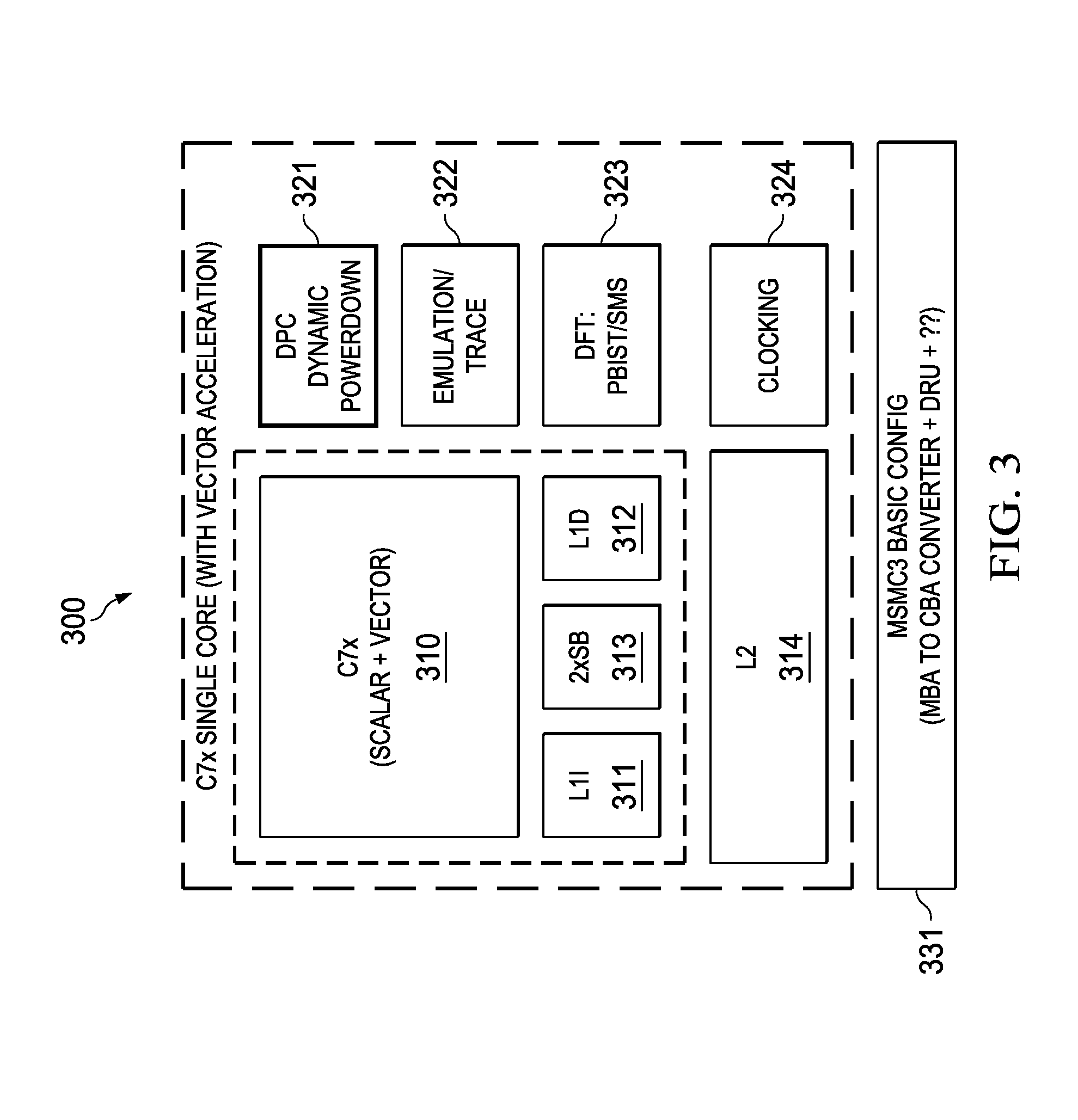

Using l1 cache as re-order buffer

ActiveUS20160019151A1Eliminate needMemory architecture accessing/allocationConditional code generationRegister bankData request

A method is shown that eliminates the need for a dedicated reorder buffer register bank or memory space in a multi level cache system. As data requests from the L2 cache may be returned out of order, the L1 cache uses it's cache memory to buffer the out of order data and provides the data to the requesting processor in the correct order from the buffer.

Owner:TEXAS INSTR INC

Computer processing system employing an instruction reorder buffer

A method and a system for operating a plurality of processors that each includes an execution pipeline for processing dependence chains, the method comprising: configuring the plurality of processors to execute the dependence chains on execution pipelines; implementing a Super Re-Order Buffer (SuperROB) in which received instructions are re-ordered after out-of-order execution when at least one of the plurality of processors is in an Instruction Level Parallelism (ILP) mode and at least one of the plurality of processors has a Thread Level Parallelism (TLP) core; detecting an imbalance in a dispatch of instructions of a first dependence chain compared to a dispatch of instructions of a second dependence chain with respect to dependence chain priority; determining a source of the imbalance; and activating the ILP mode when the source of the imbalance has been determined.

Owner:INT BUSINESS MASCH CORP

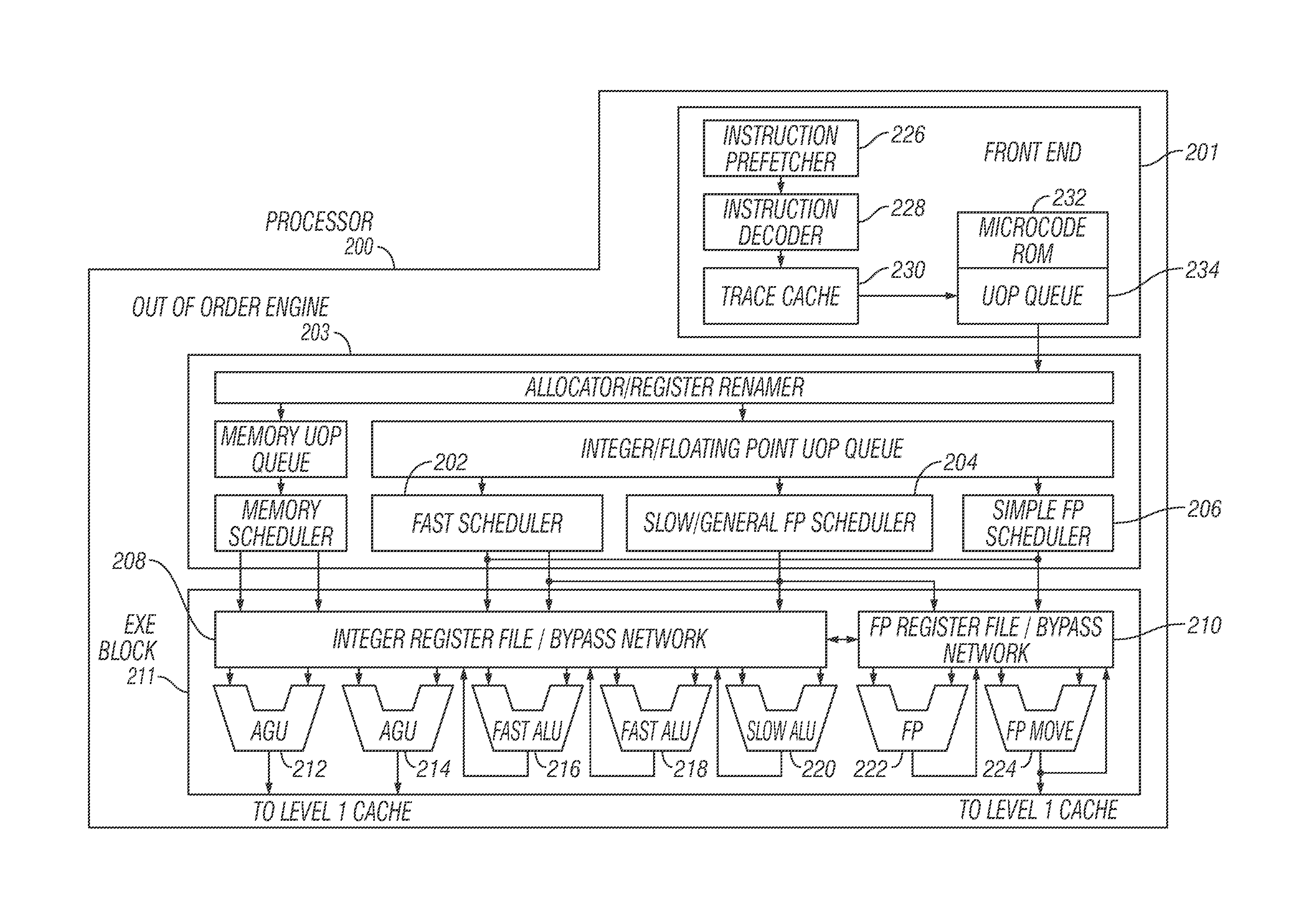

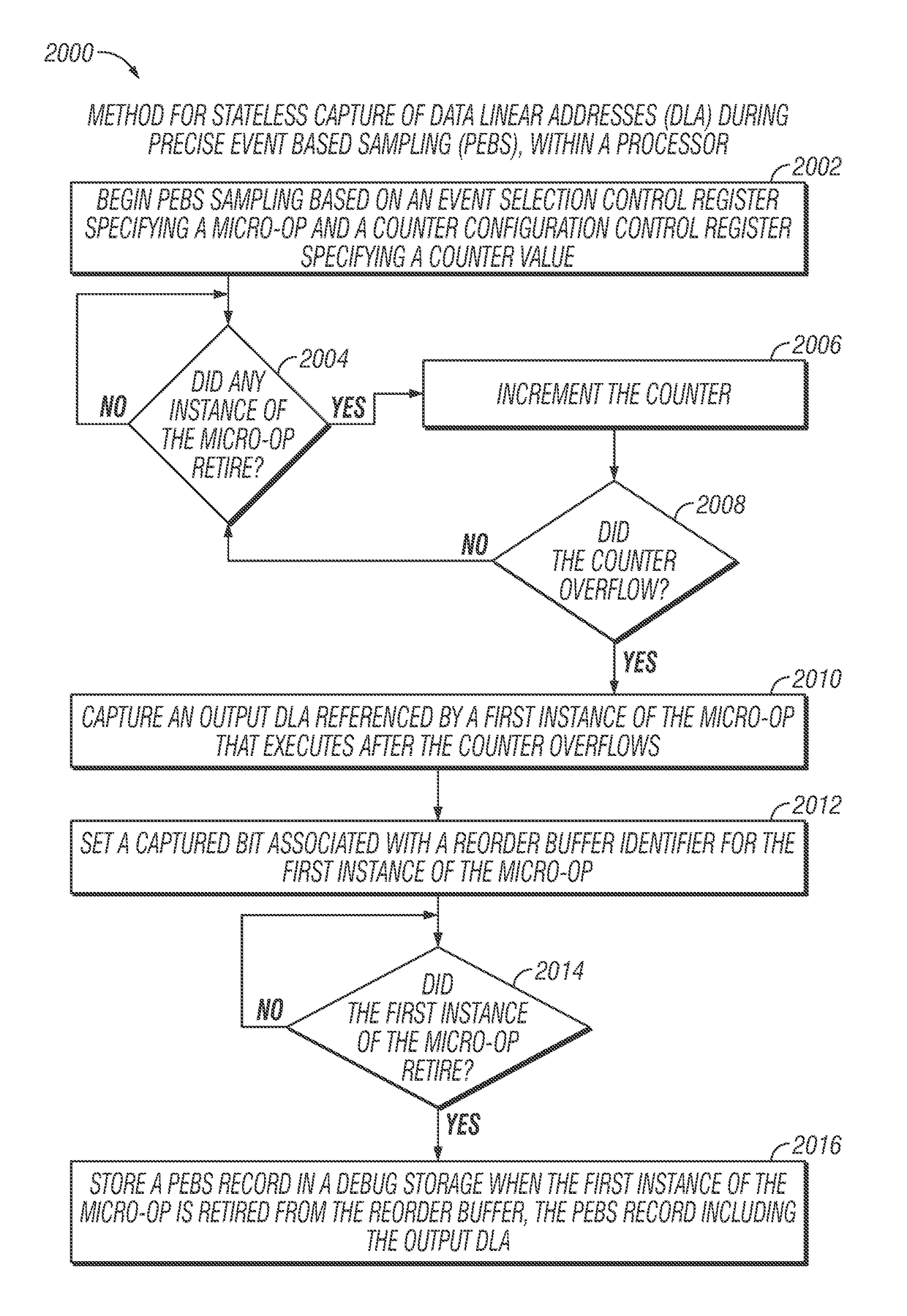

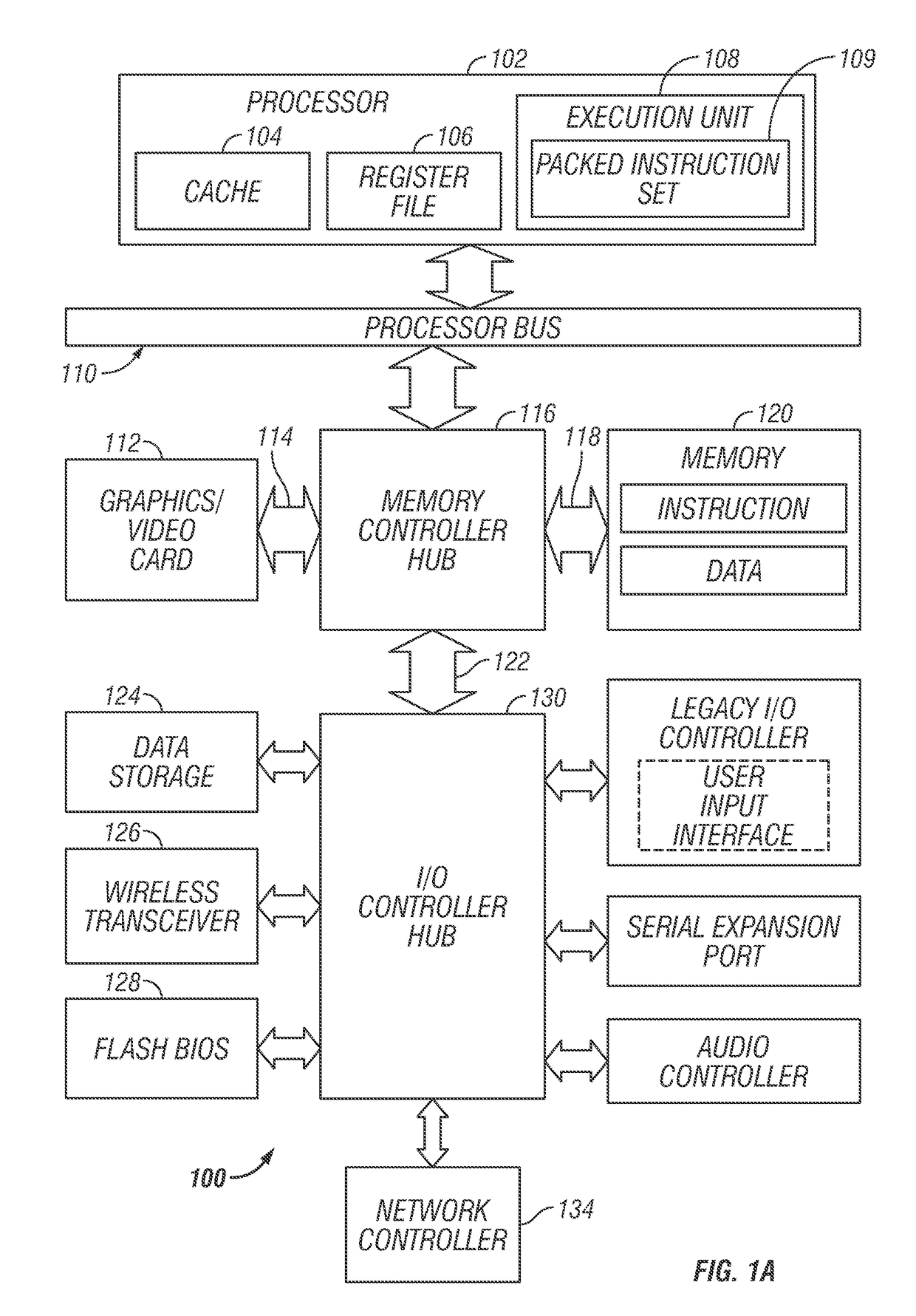

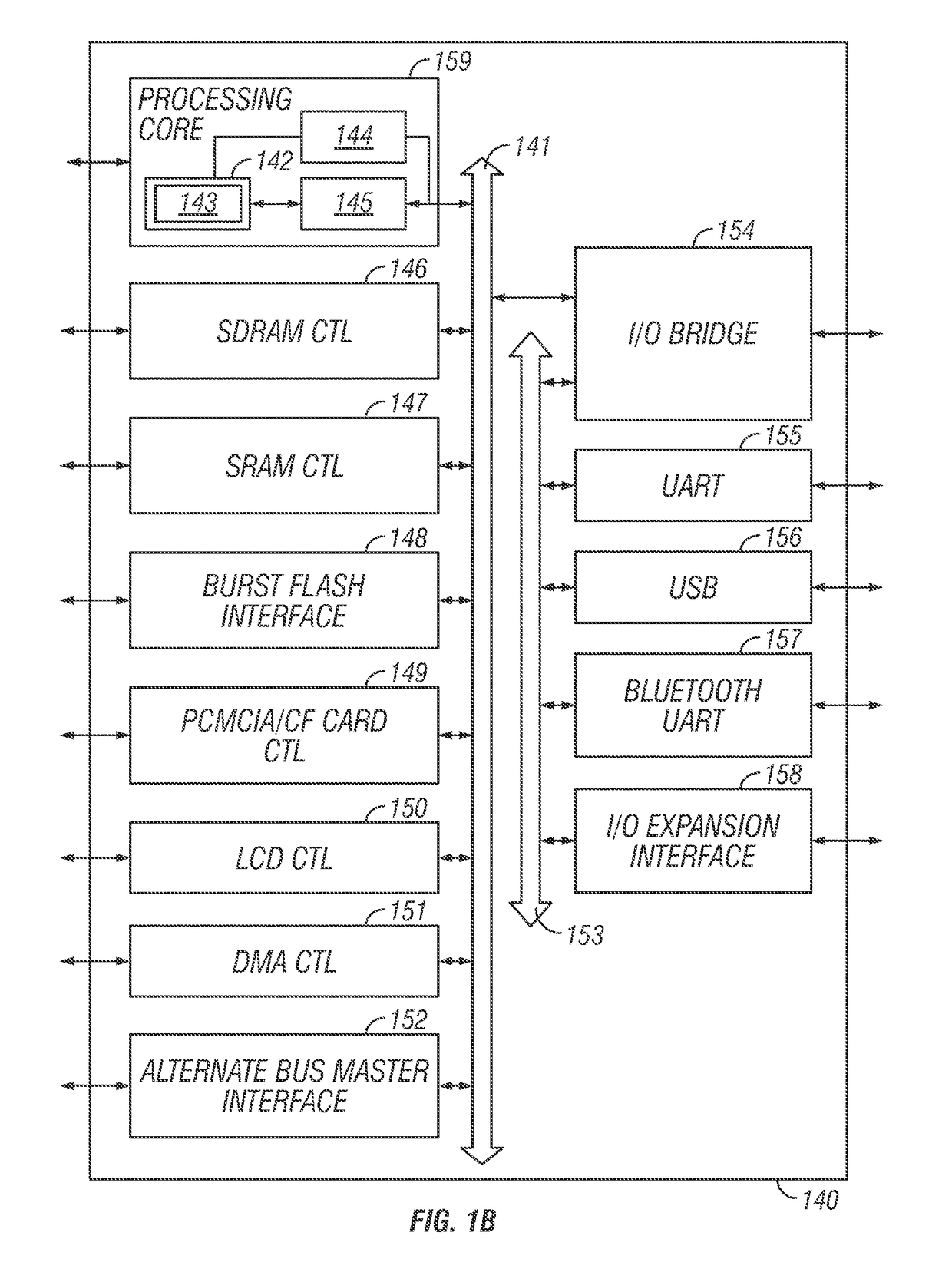

Stateless capture of data linear addresses during precise event based sampling

A processor includes a logic for stateless capture of data linear addresses (DLA) during precise event based sampling (PEBS) for an out-of-order execution engine. The engine may include a PEBS unit with logic to increment a counter each time an instance of a designated micro-op is retired a reorder buffer, capture output DLA referenced by an instance of the micro-op that executes after the counter overflows, set a captured bit associated with a reorder buffer identifier for the instance of the micro-op, and store a PEBS record in a debug storage when the instance of the micro-op is retired from the reorder buffer. The designated micro-op references a DLA of a memory accessible to the processor.

Owner:INTEL CORP

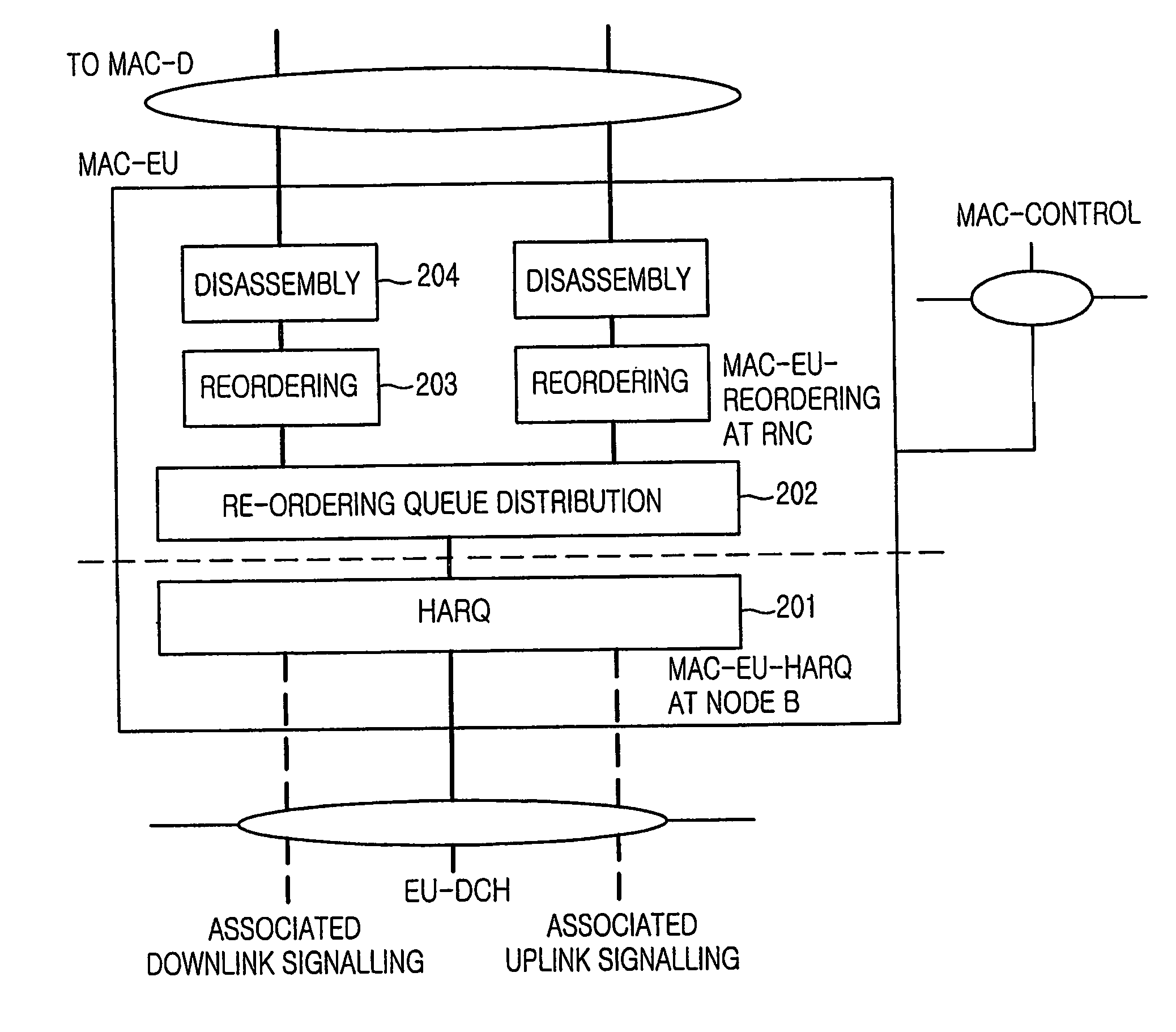

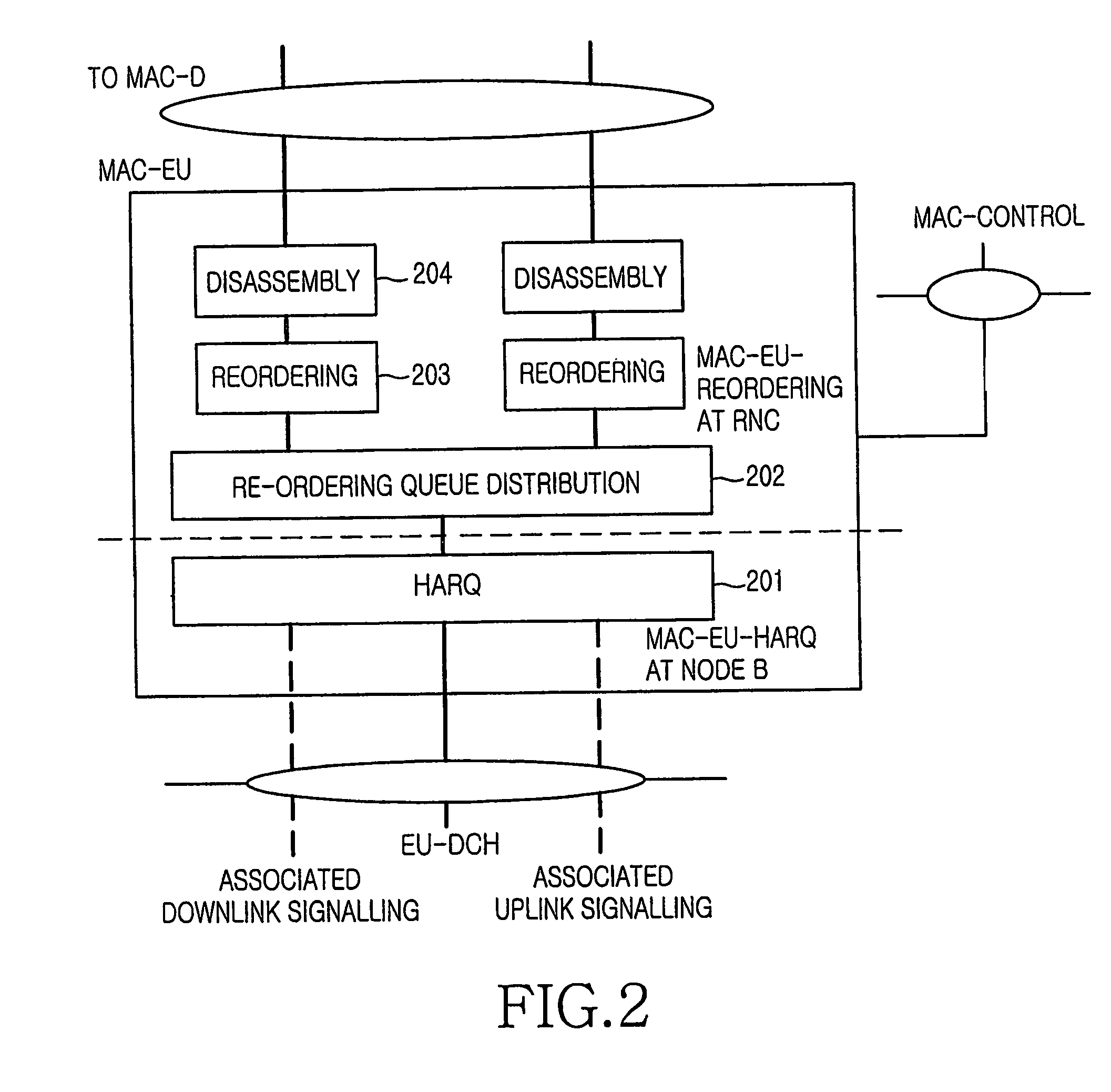

HARQ reordering method for WCDMA enhanced uplink dedicated channel

ActiveUS8285330B2More diversity gainLower latencyError prevention/detection by using return channelNetwork traffic/resource managementSeparation technologyComputer science

Owner:SAMSUNG ELECTRONICS CO LTD +1

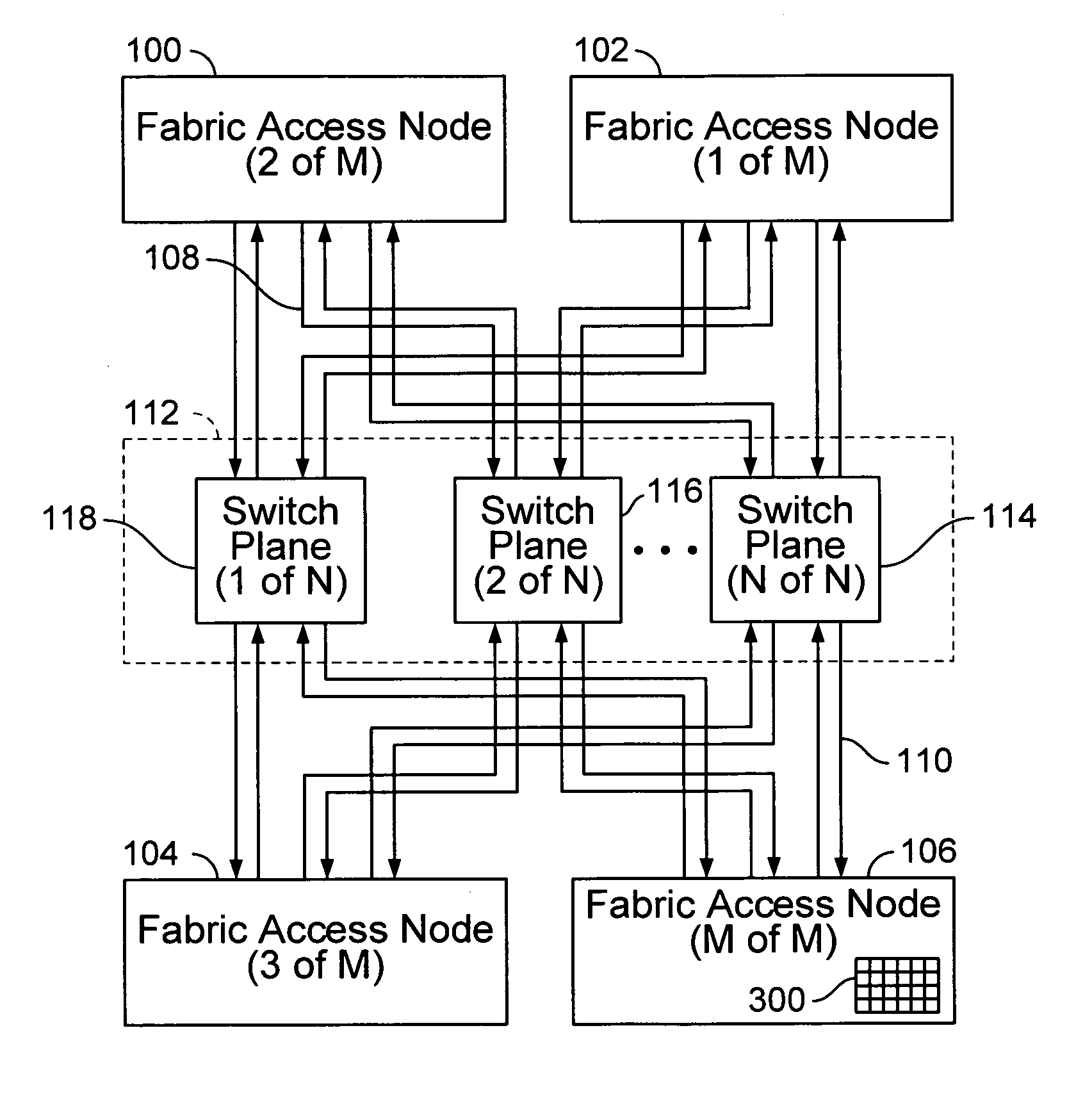

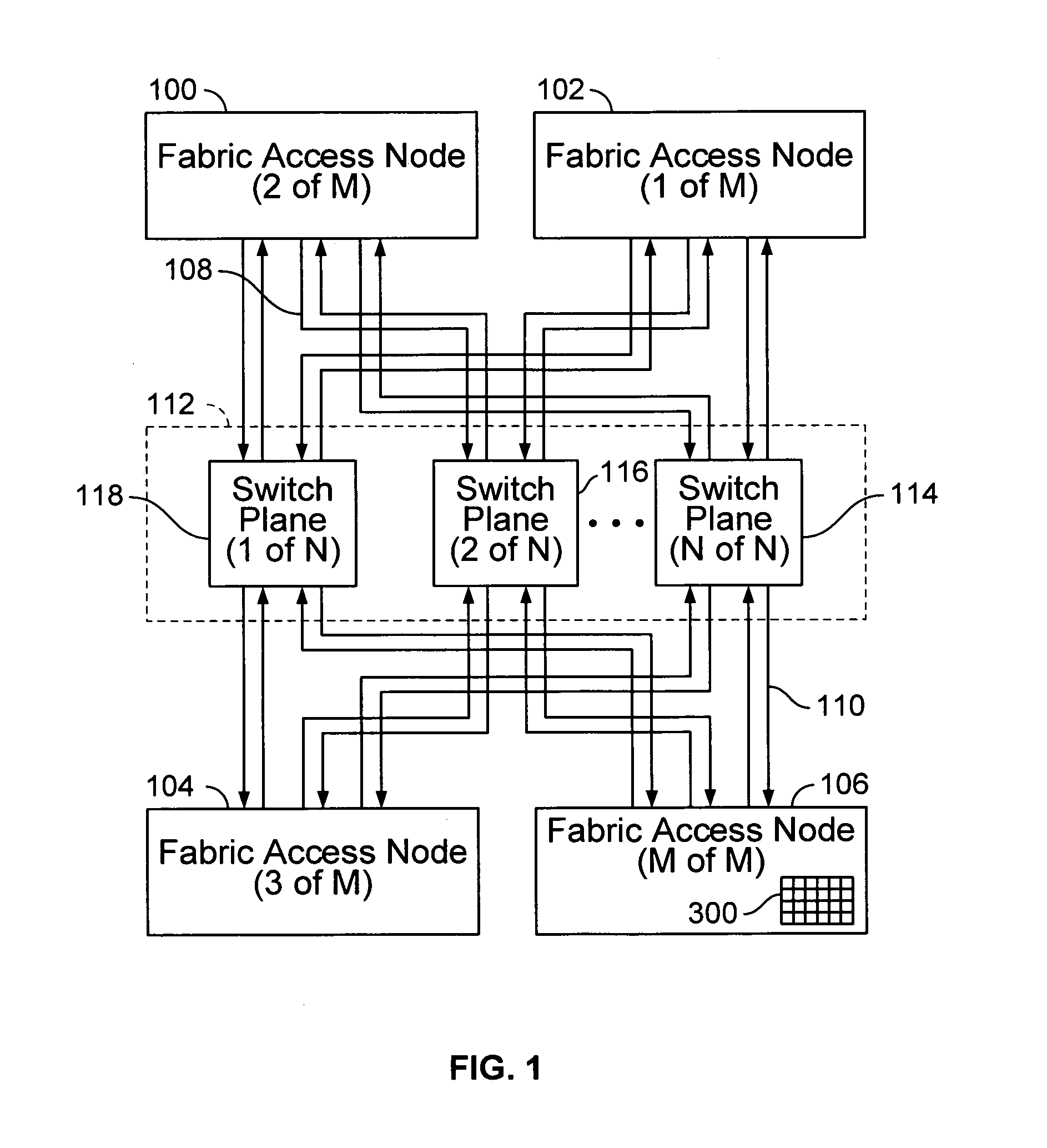

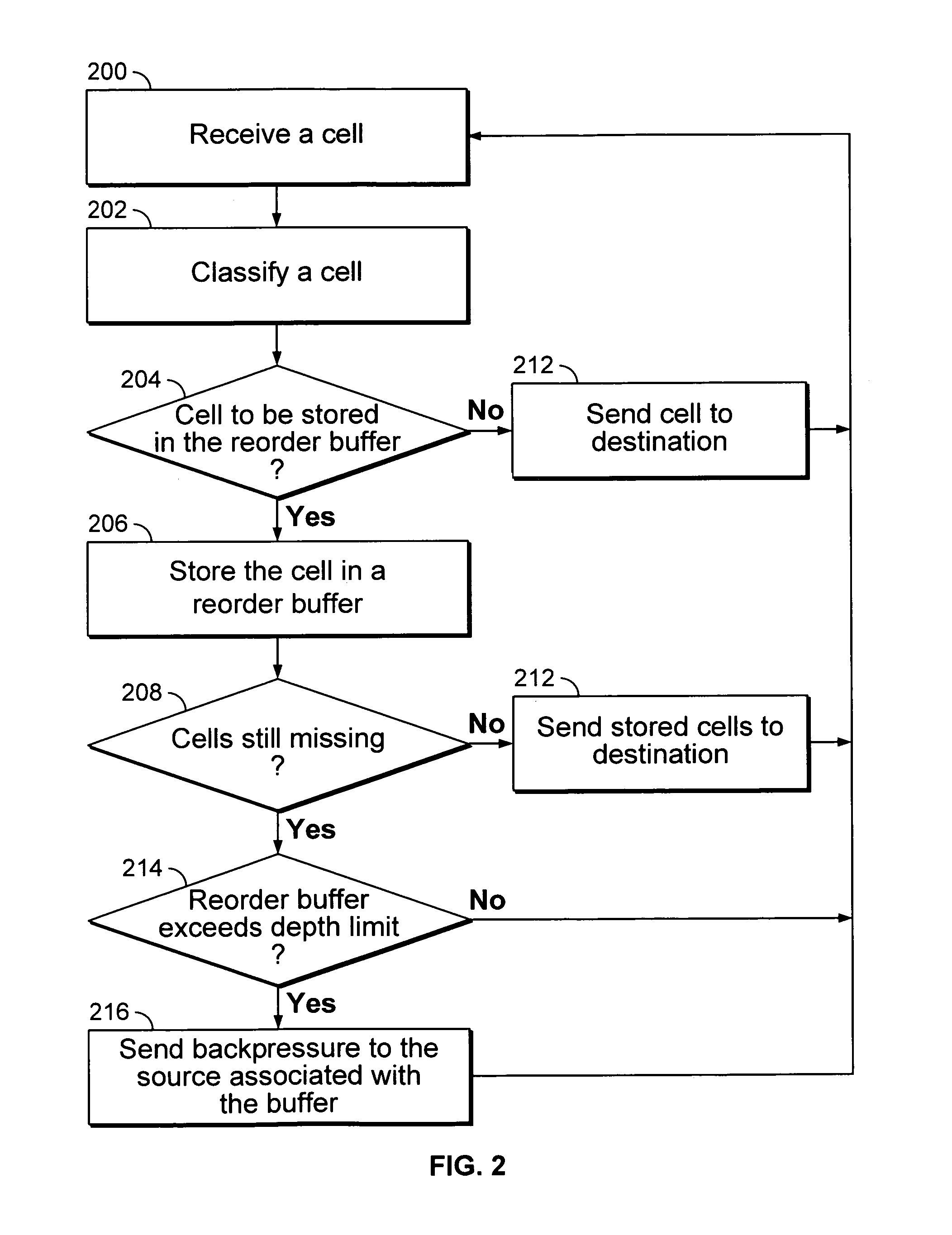

Fabric access integrated circuit configured to bound cell reorder depth

Bounding cell reorder depth is disclosed. It is determined whether a reorder buffer that is associated with a switch fabric exceeds a depth limit. In the event that the reorder buffer exceeds the depth limit, backpressure with respect to a source associated with the reorder buffer is sent. In such cases source based back pressure information is included in a reserved field in a cell that is being sent into the switch fabric. In the event that the reorder buffer does not exceed the depth limit, the cell is sent to the switch fabric. In such cases the reserved field is present in the cell but is unused.

Owner:WSOU INVESTMENTS LLC

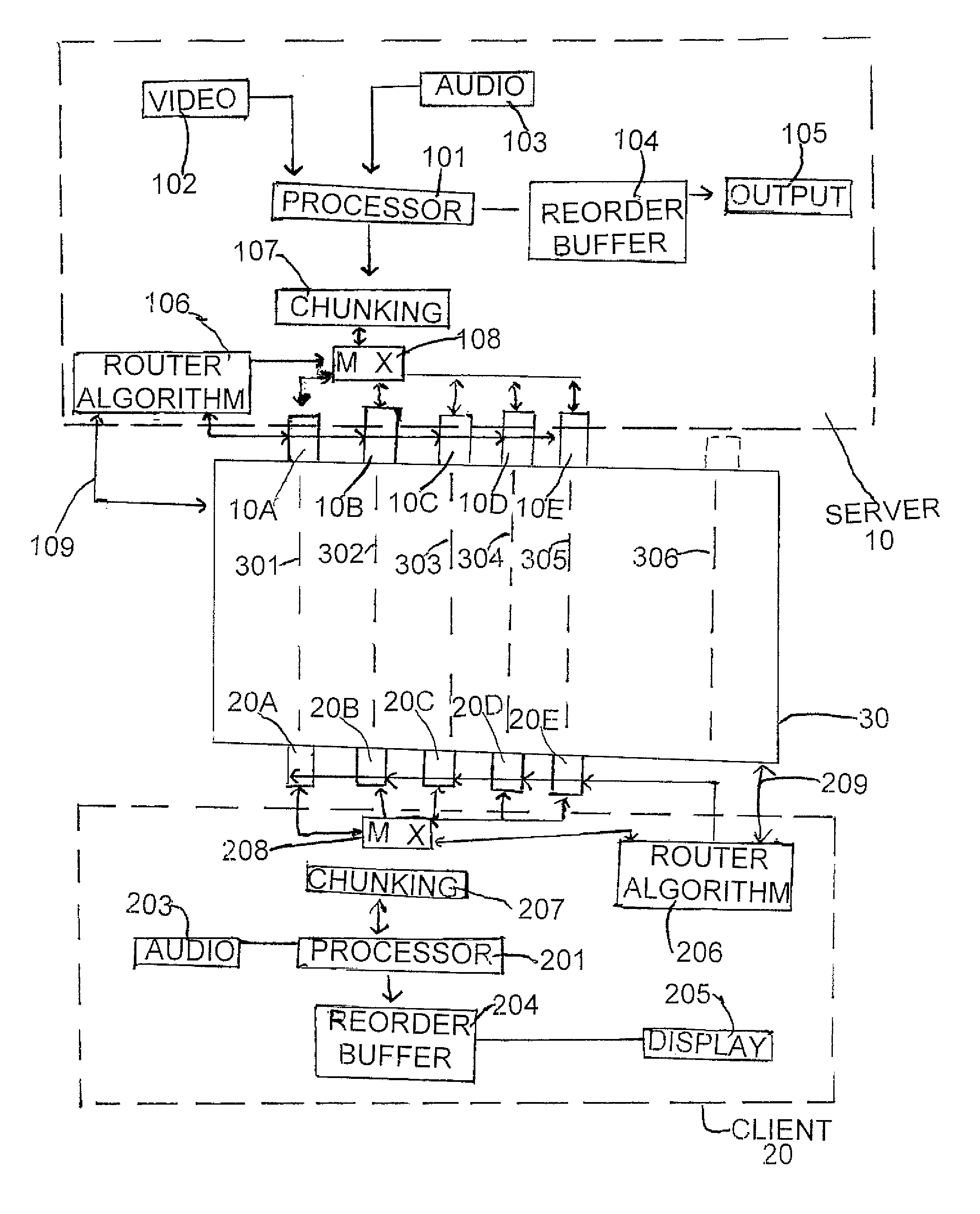

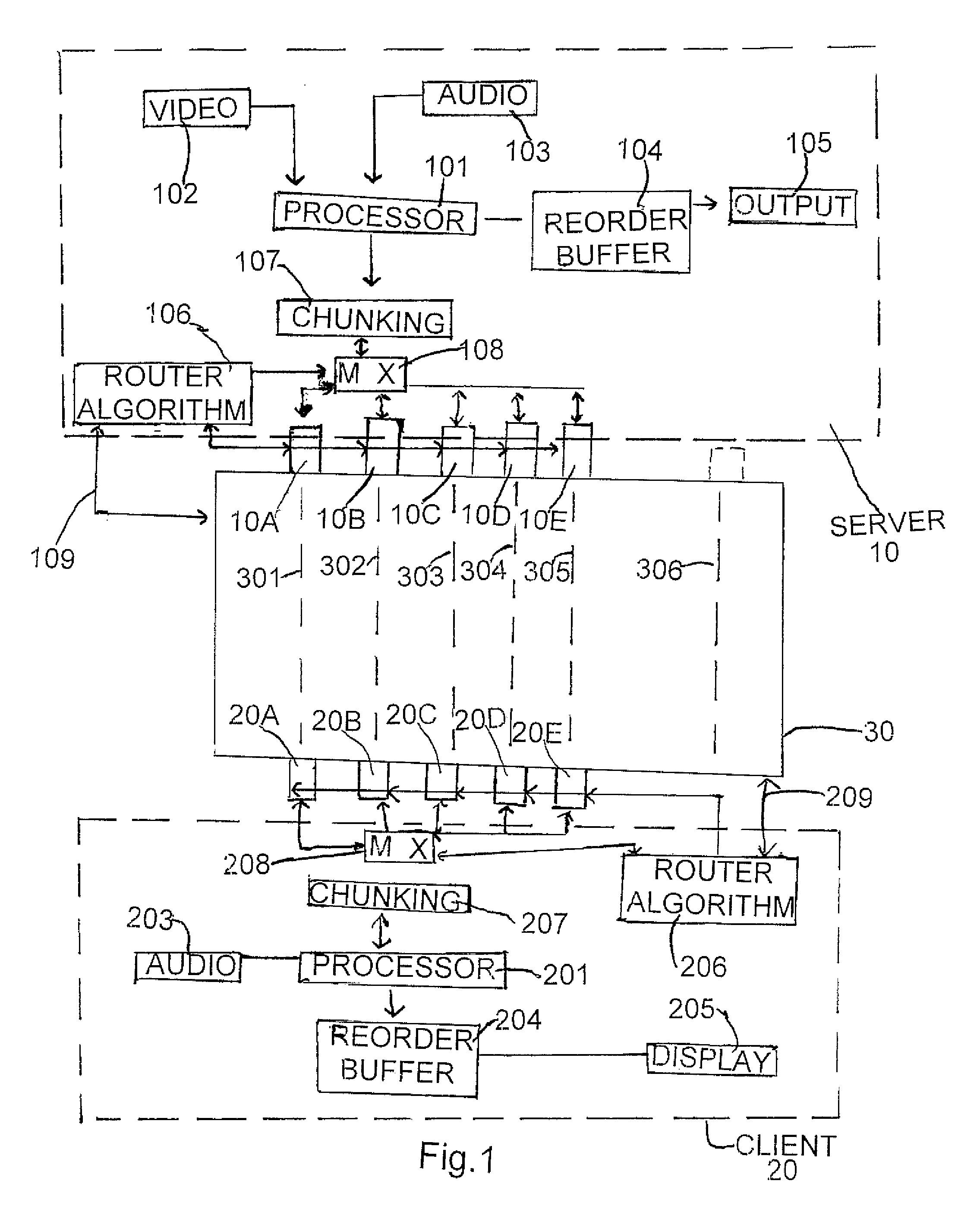

Transmitting a Media Stream Over HTTP

InactiveUS20130060906A1Improve real-time performanceMultiple digital computer combinationsTransmissionRe-order bufferData buffer

A media stream is transmitted over HTTP from a server which accepts TCP connections to a client. The system generates for a session a plurality of dedicated tunnels through the network. The stream is encapsulated into a series of data blocks with a sequence number in the header. Each time a block is sent, the system selects from the available tunnels that which currently has the least pending sends. At the client the blocks are re-ordered in a re-ordering buffer into sequential order and used to generate the media stream. The buffer ignores any data blocks which are not received within a set time period. New tunnels are opened when the number of pending blocks at the one with the least number is greater than a set number, but only up to a set maximum and only after a set delay time from the last tunnel opening.

Owner:LIBRESTREAM TECH

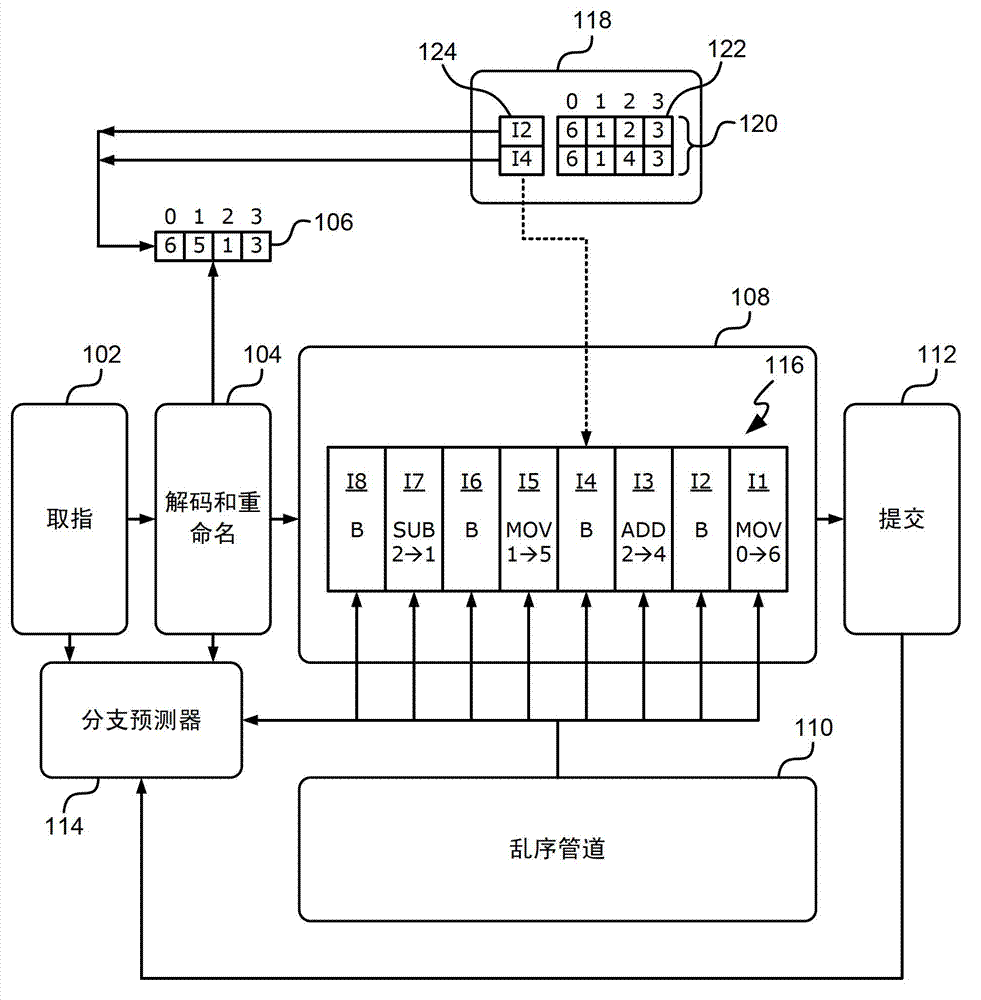

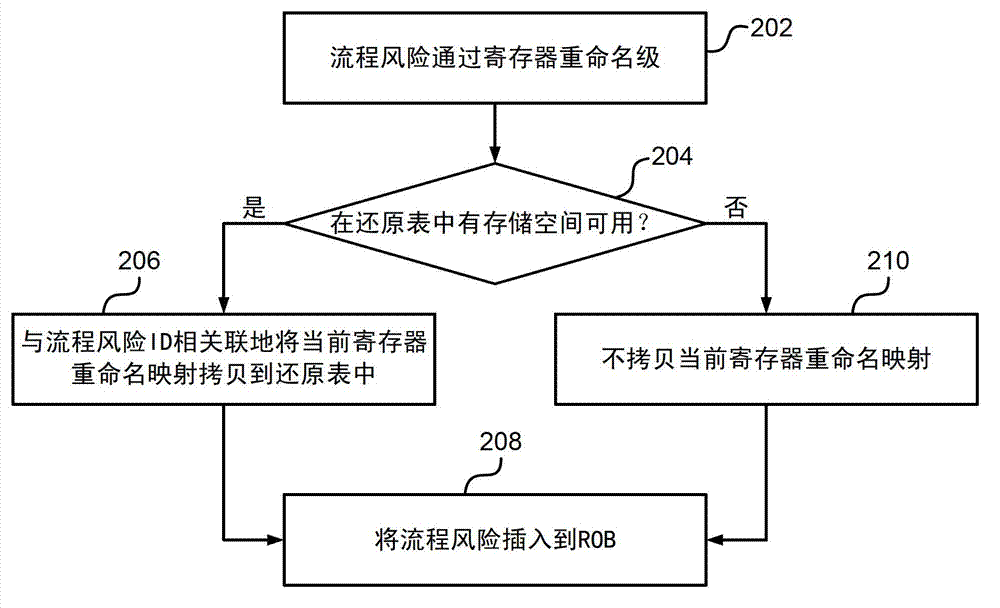

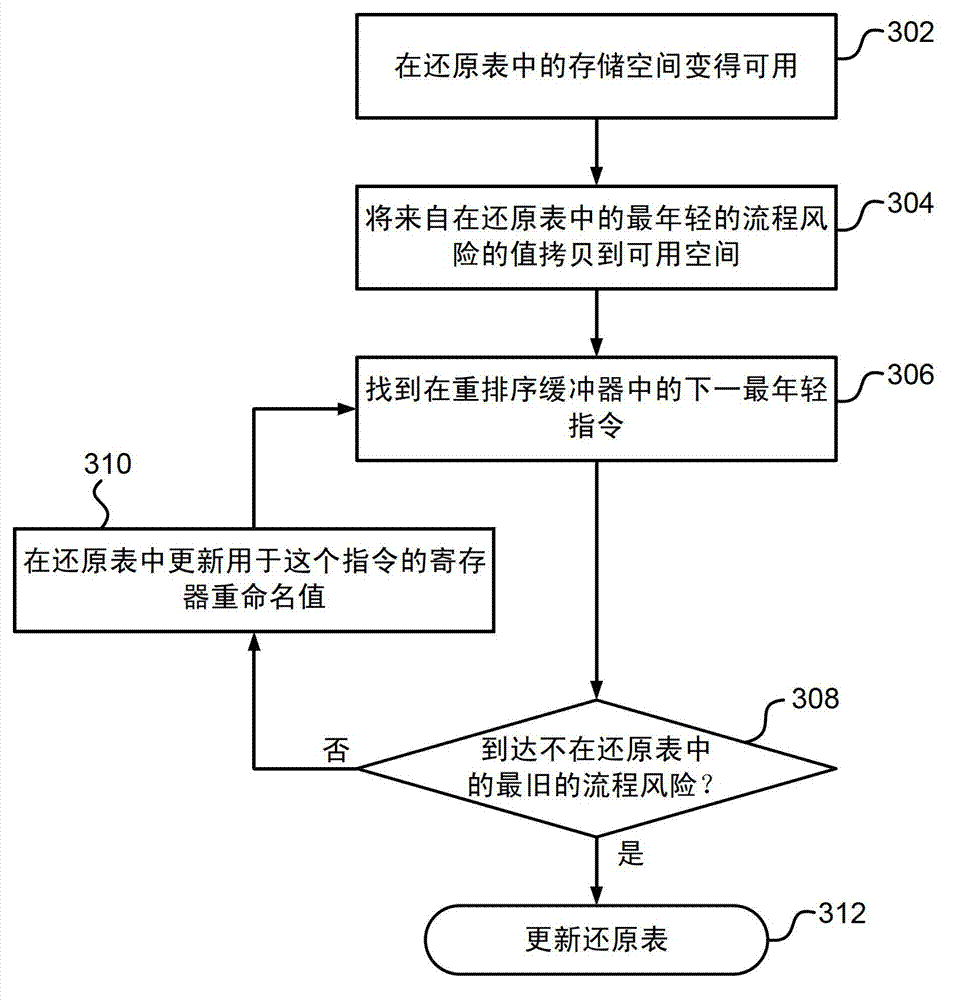

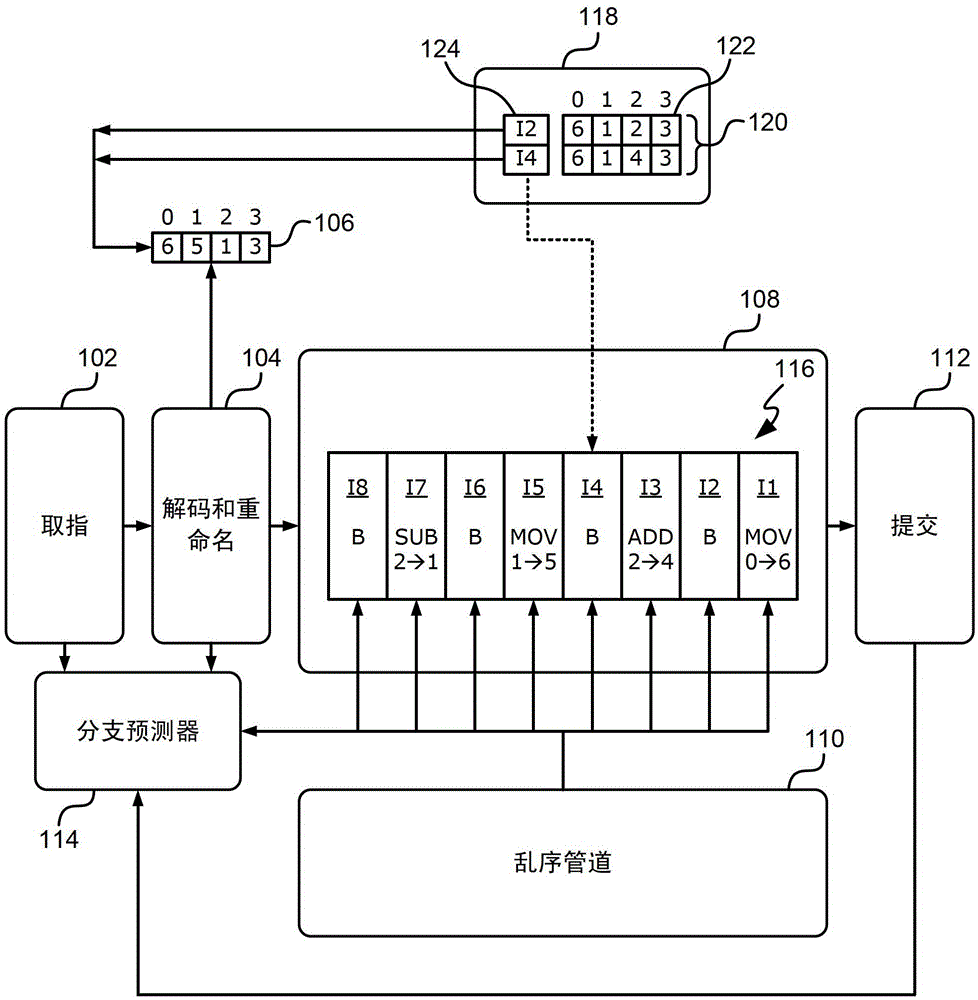

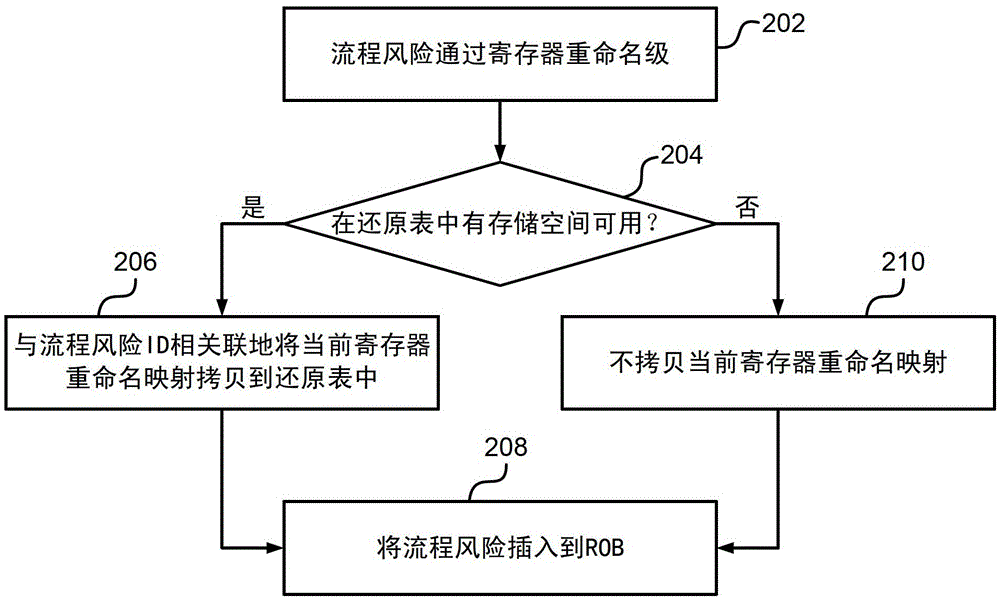

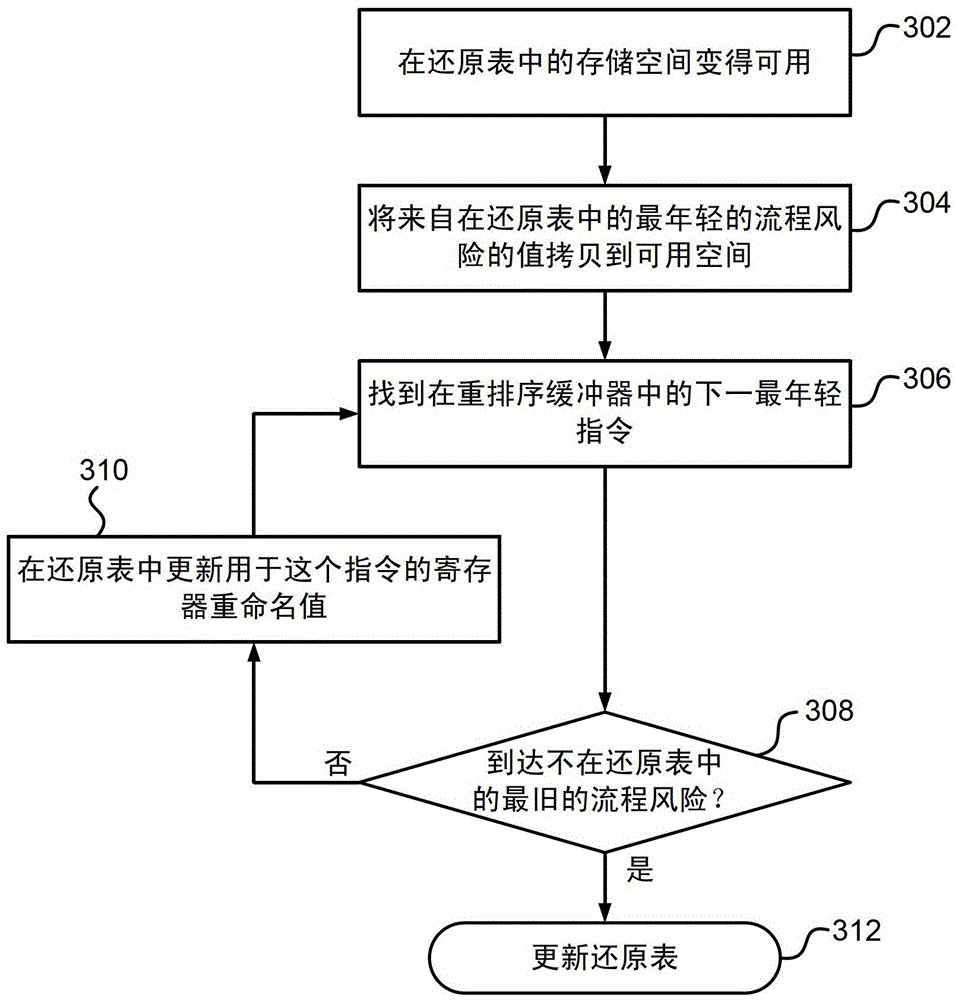

Restoring a register renaming map

A technique for restoring a register renaming map is described. In one example, a restore table having a number of storage locations saves a copy of the register renaming map whenever a flow-risk instruction is passed to a re-order buffer. When all storage locations are full, further instructions still pass to the re-order buffer, but a copy of the map is not saved. A storage location subsequently becomes available when its associated flow-risk instruction is executed. A register renaming map state for an unrecorded flow-risk instruction passed to the re-order buffer whilst the storage locations were full is generated and stored in the available location. This is generated using the restore table entry for a previous flow-risk instruction and re-order buffer values for intervening instructions between the previous and unrecorded flow-risk instructions. The restore table can be used to restore the map if an unexpected change in instruction flow occurs.

Owner:MIPS TECH INC

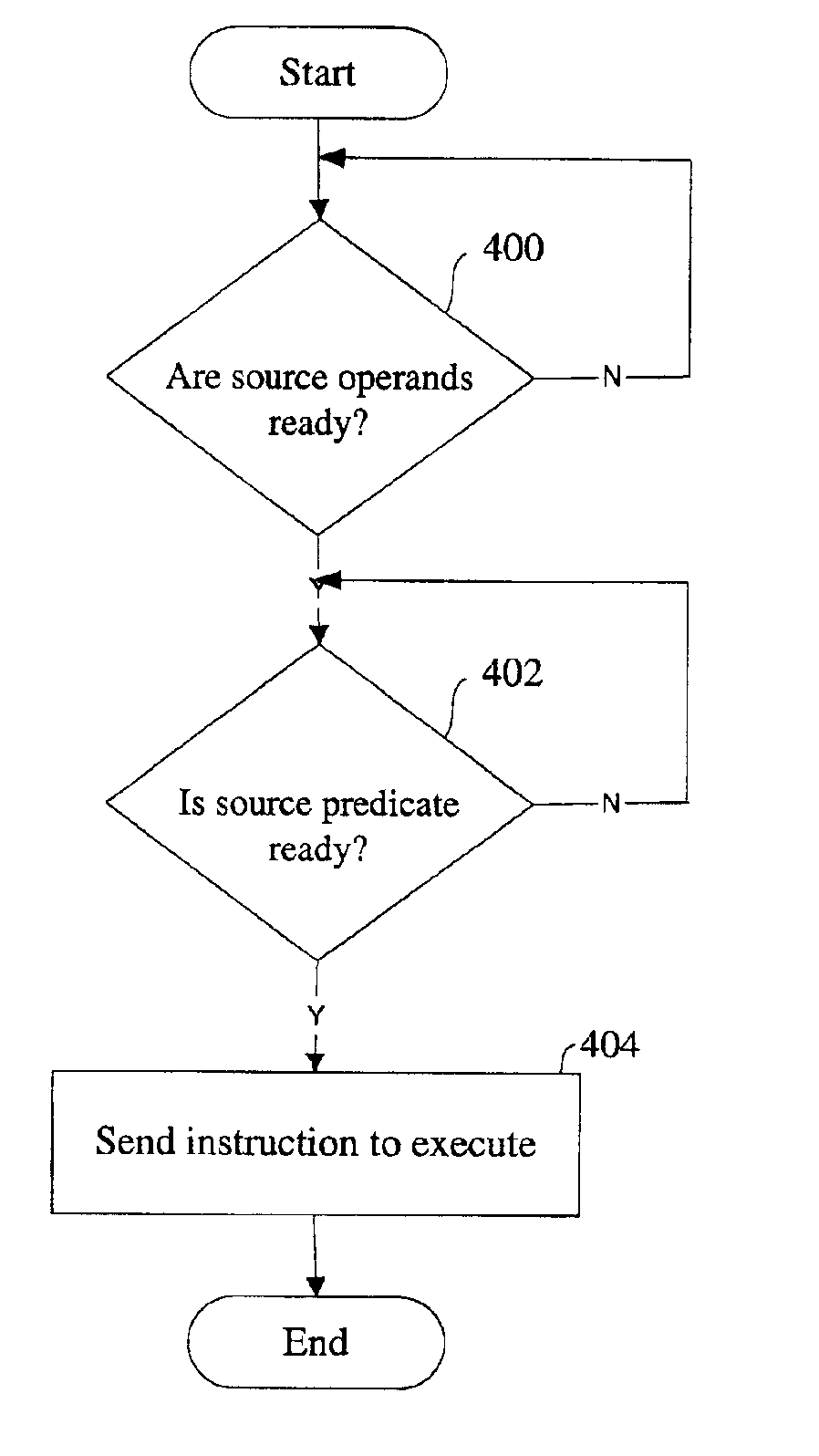

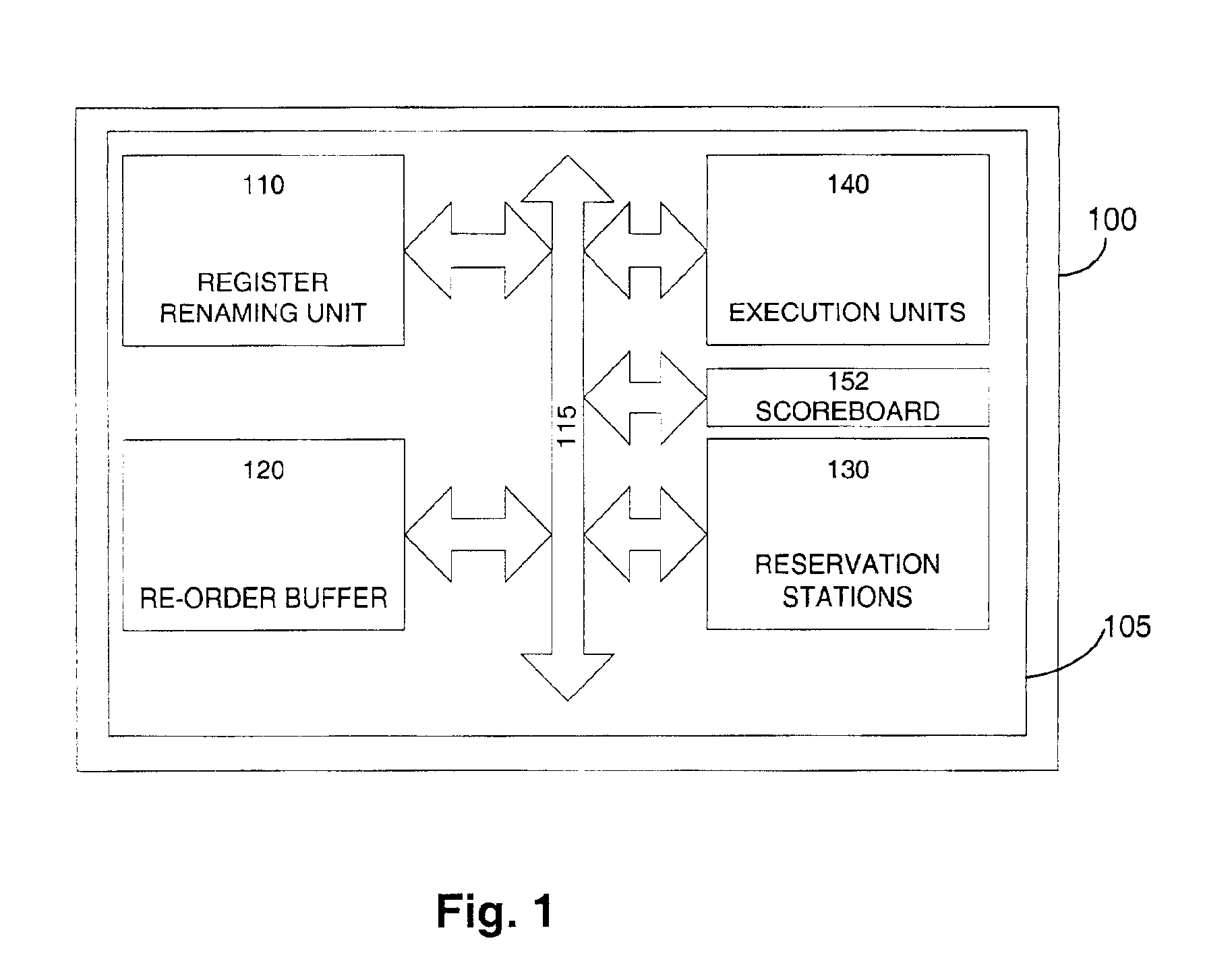

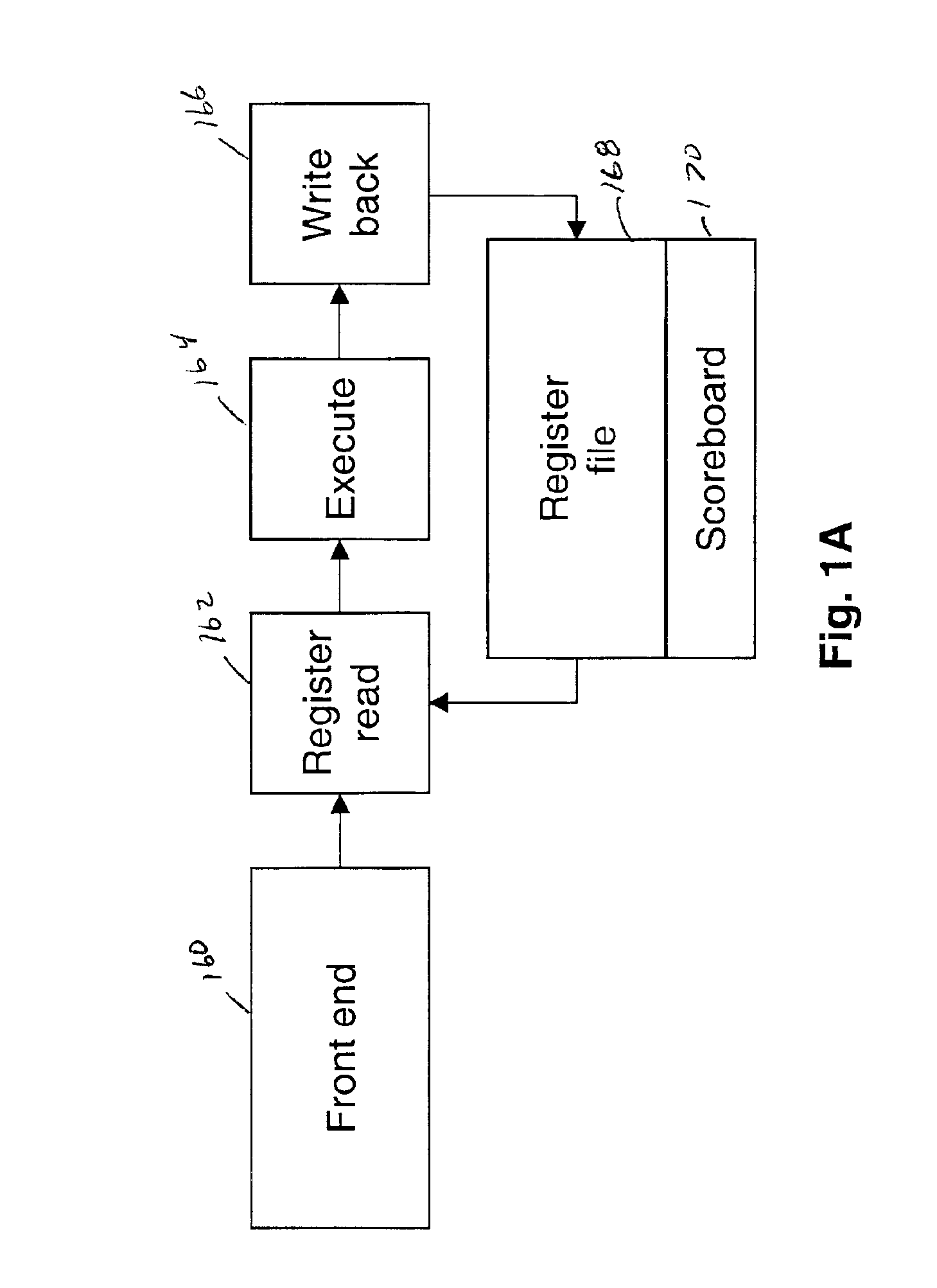

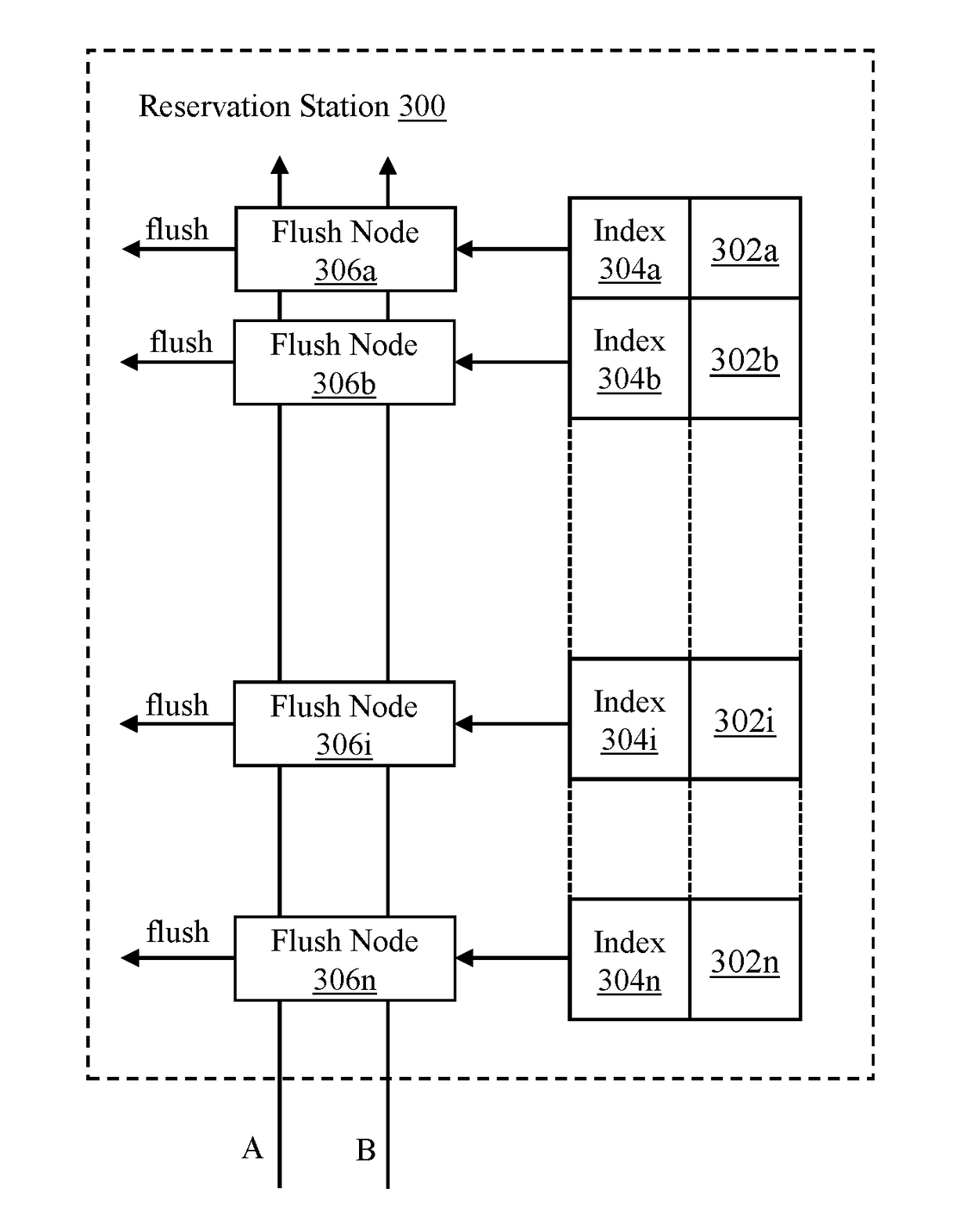

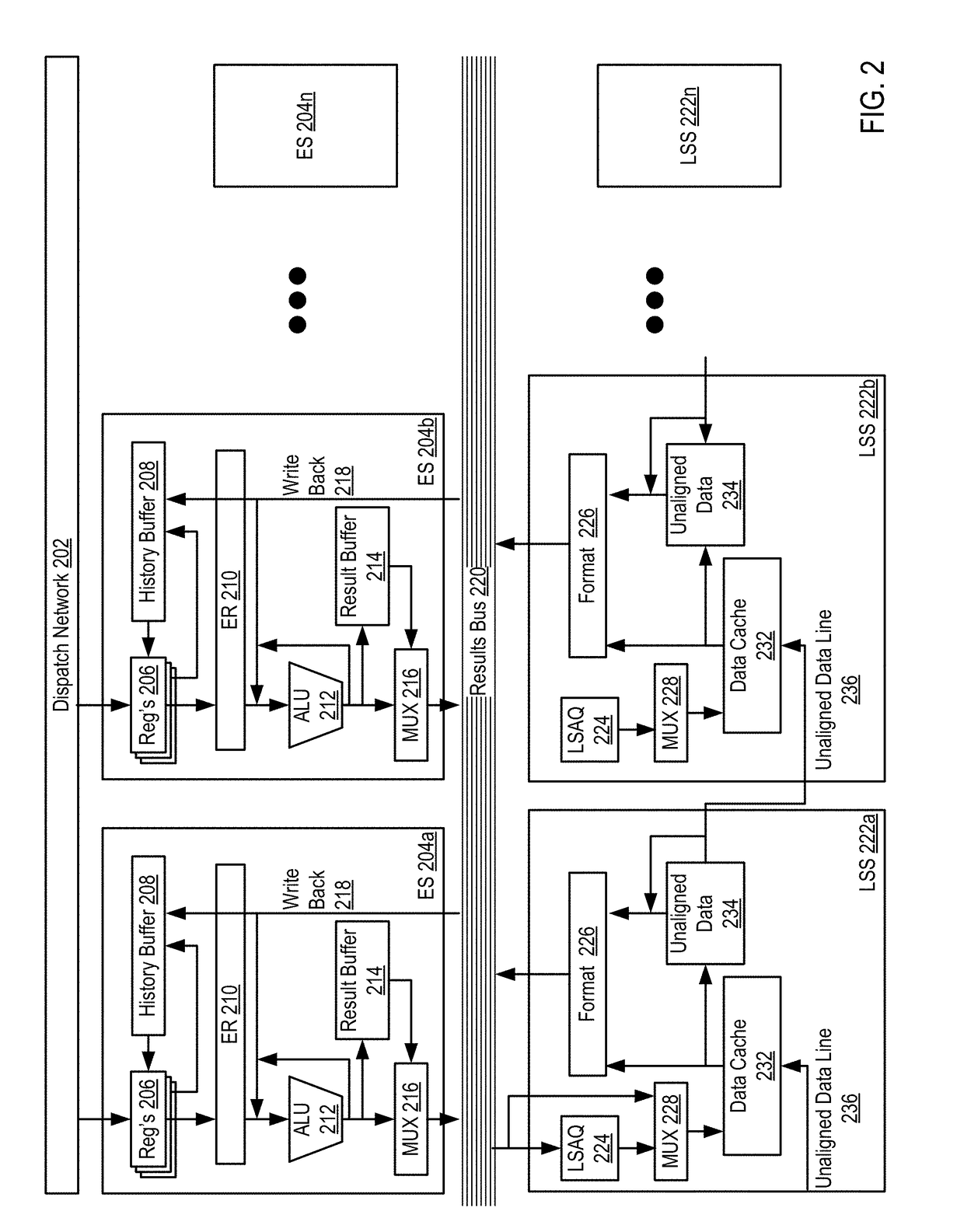

Method and apparatus for processing a predicated instruction using limited predicate slip

InactiveUS6883089B2Digital computer detailsConcurrent instruction executionReservation stationExecution unit

A system and method of processing a predicated instruction is disclosed. A consumer instruction and a predicated instruction are received in an reservation station of an out-order processor. The consumer instruction depends on a result of the predicated instruction. The predicated instruction is dispatched to an execution unit for execution. The executed predicate instruction is stored in a re-order buffer.

Owner:INTEL CORP

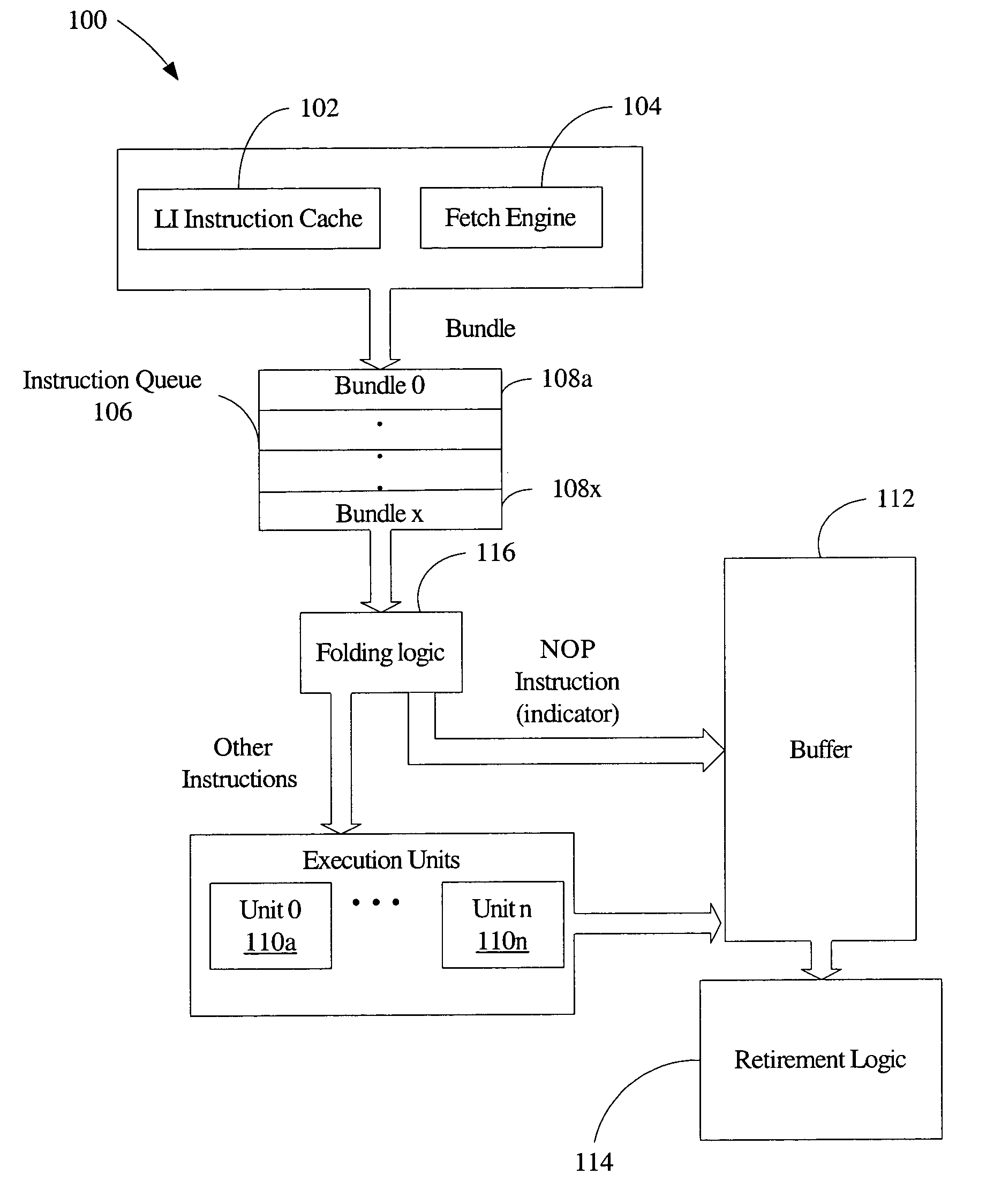

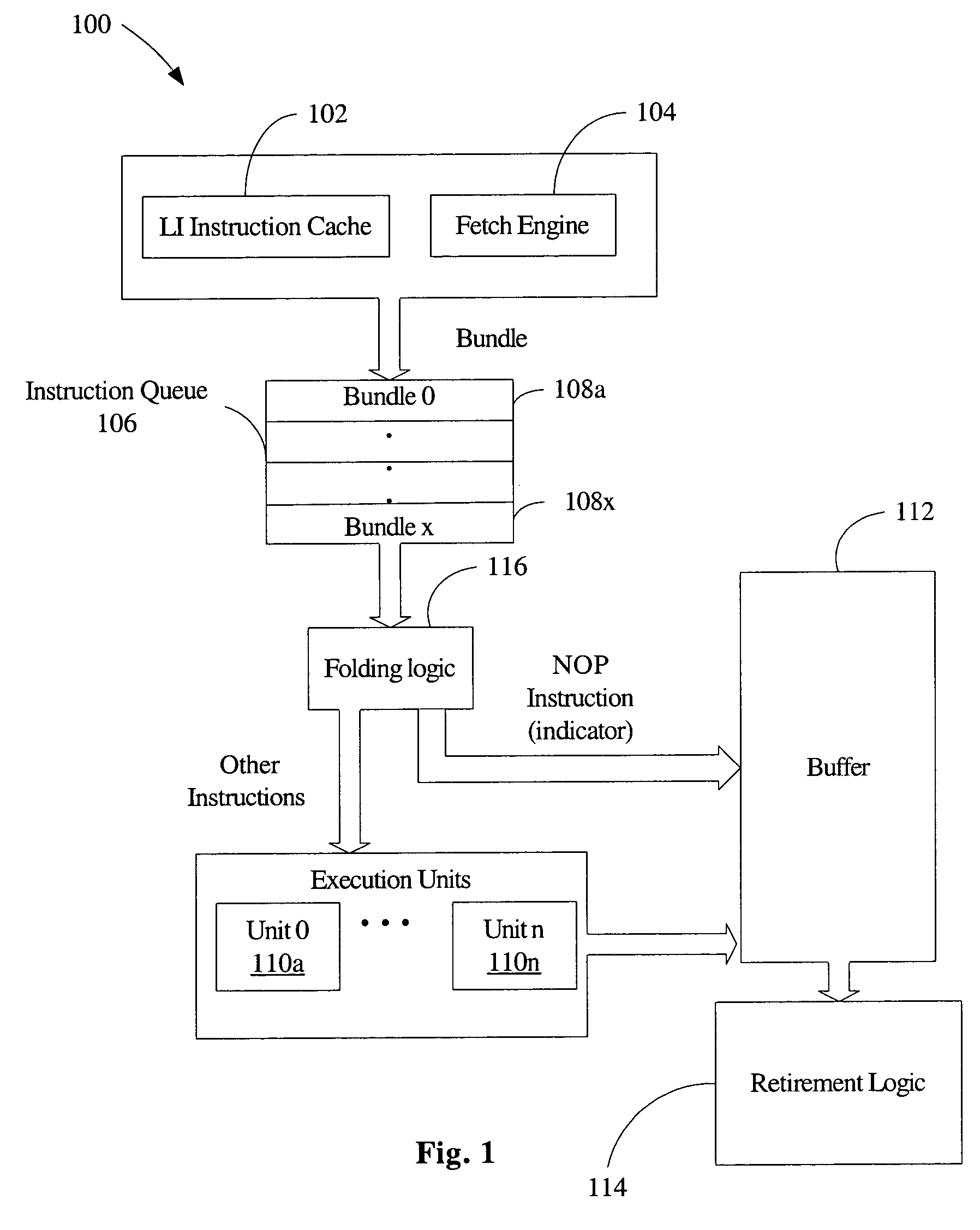

Method and apparatus for NOP folding

InactiveUS7111154B2General purpose stored program computerConcurrent instruction executionNOPInstruction stream

Embodiments of an apparatus, method, and system provide for no-operation instruction (“NOP”) folding such that information regarding the presence of a NOP instruction in the instruction stream is folded into a buffer entry for another instruction. Information regarding a target NOP instruction is thus maintained in a buffer entry associated with an instruction other than the target NOP instruction. For at least one embodiment, NOP information is folded into entries of a re-order buffer.

Owner:INTEL CORP

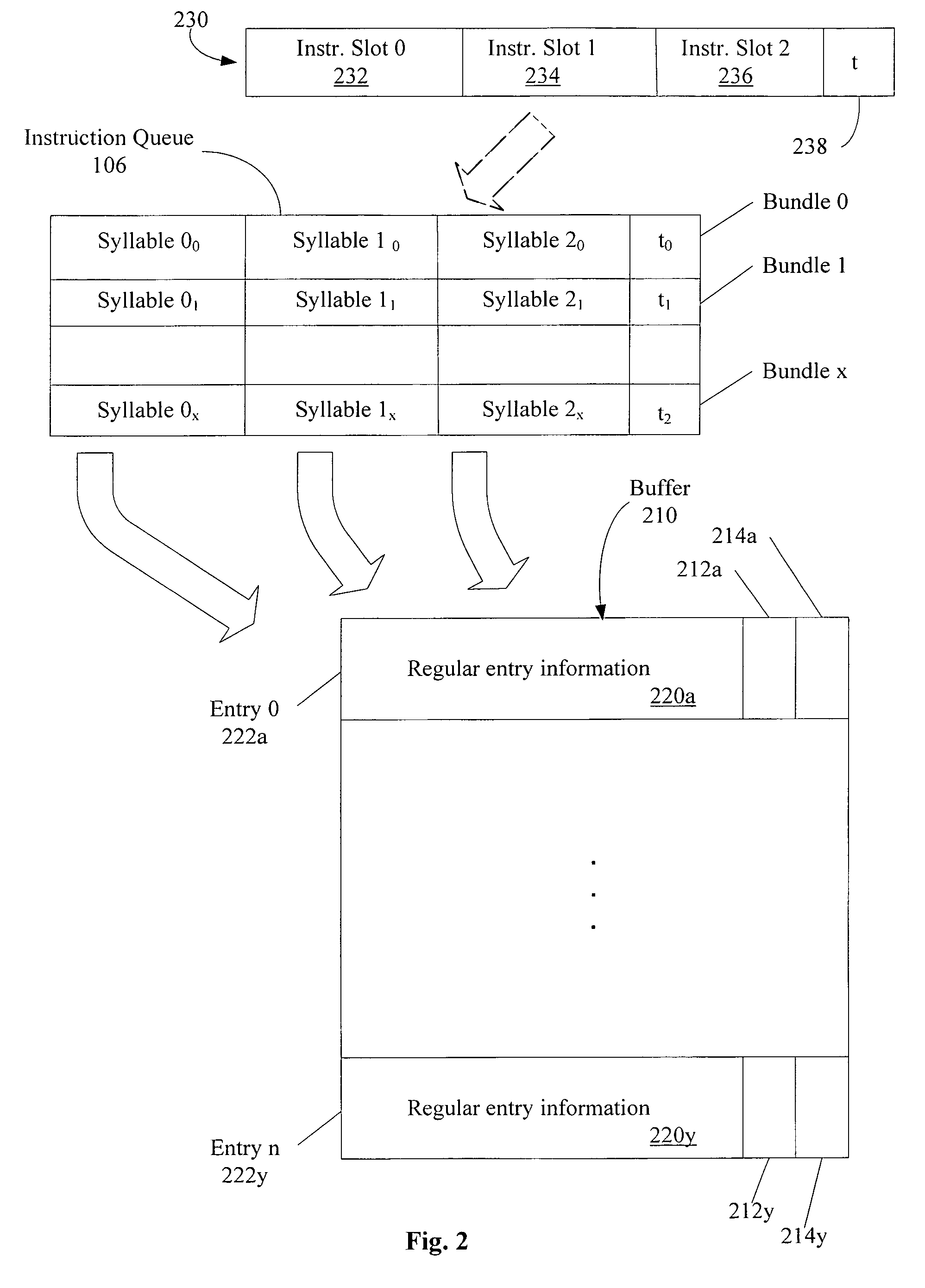

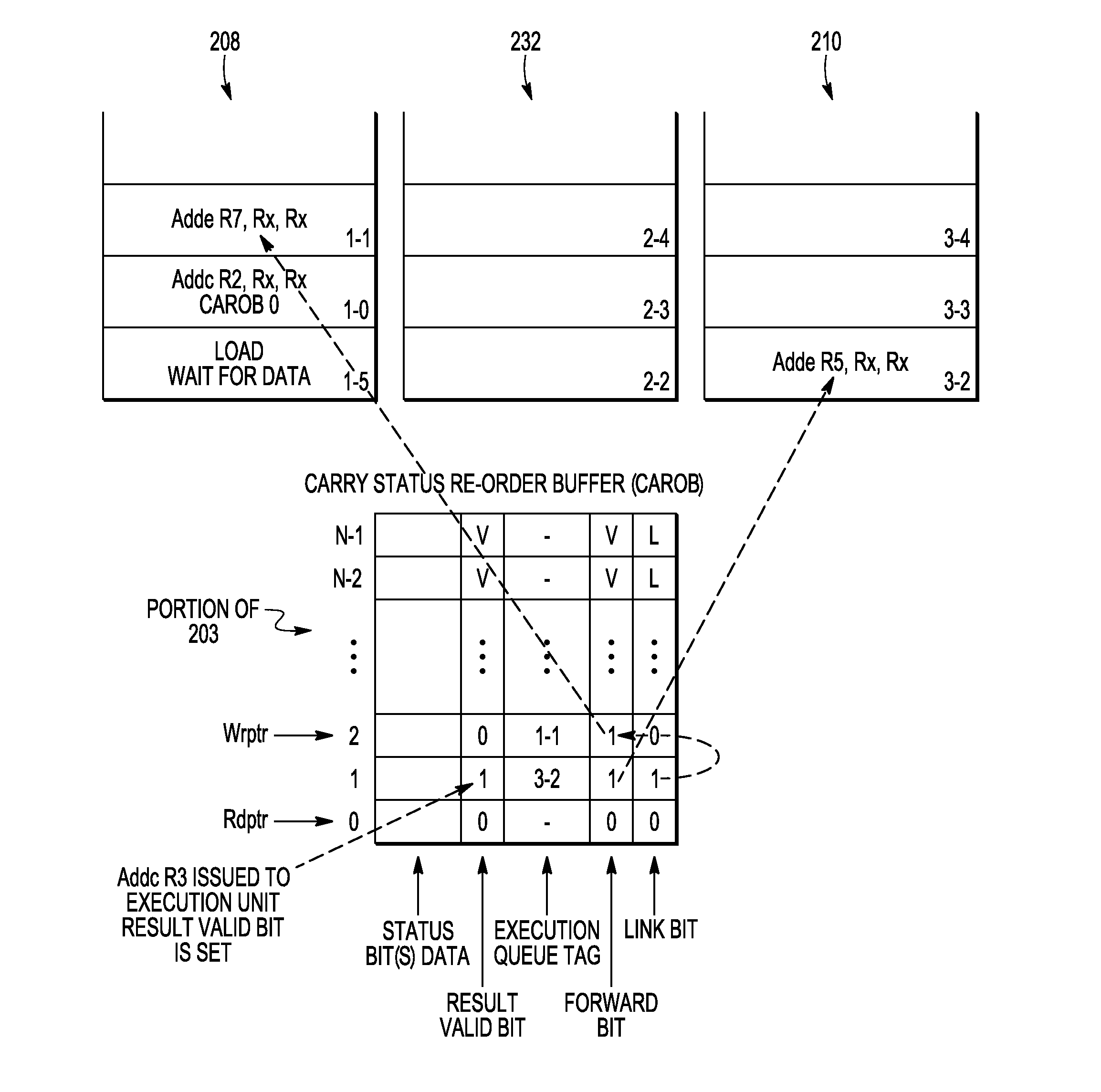

Data processing system with latency tolerance execution

InactiveUS20130212358A1Conditional code generationDigital computer detailsData processingRe-order buffer

A data processing system comprises a processor unit that includes an instruction decode / issue unit including a re-order buffer having entries that include an execution queue tag that indicates an execution queue location of an instruction to which a re-order buffer entry is assigned, a result valid indicator to indicate that a corresponding instruction has executed with a status bit valid result, and a forward indicator to indicate that the status bit can be forwarded to an execution queue of an instruction pointed to that is waiting to receive the status bit.

Owner:NXP USA INC

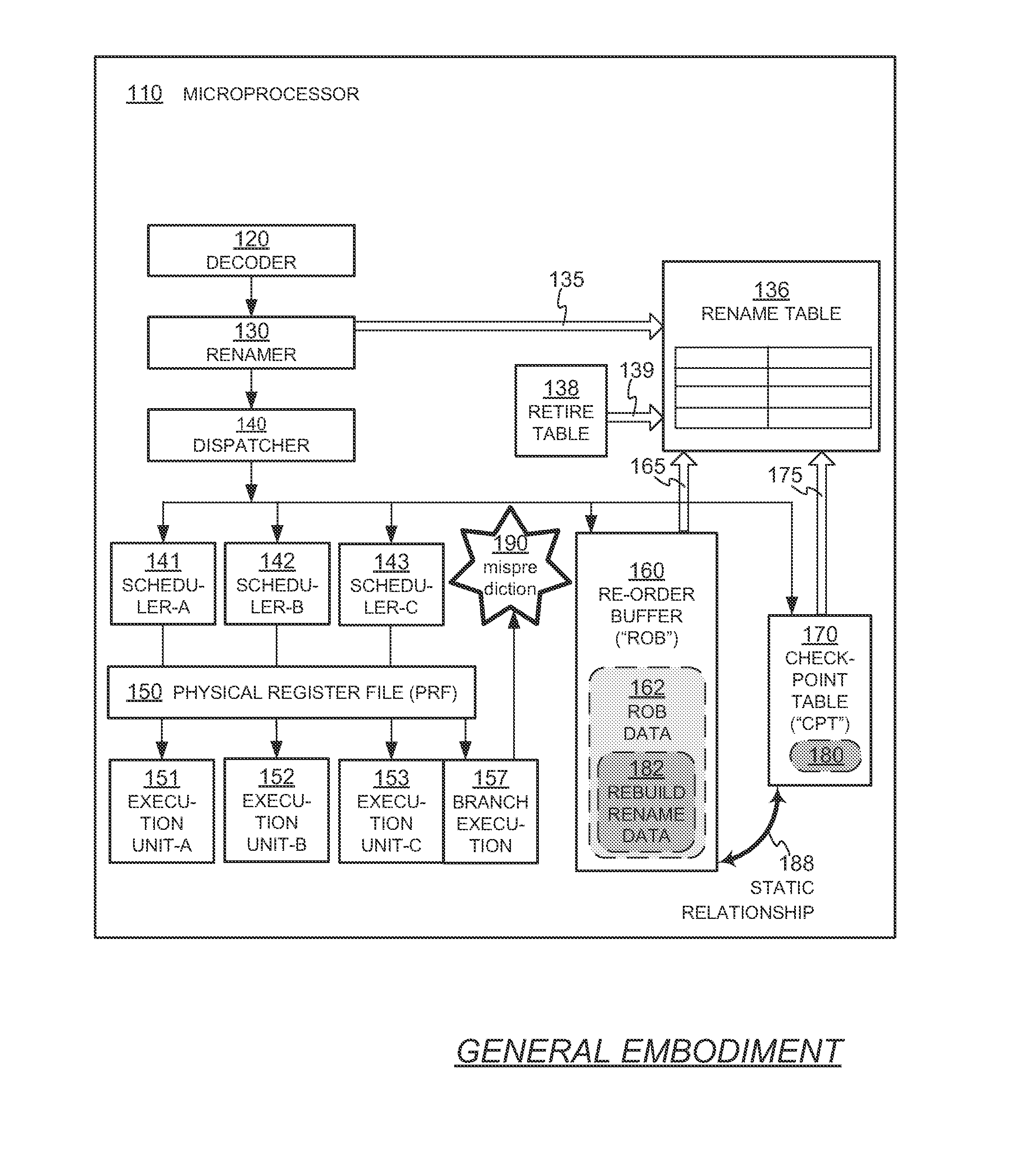

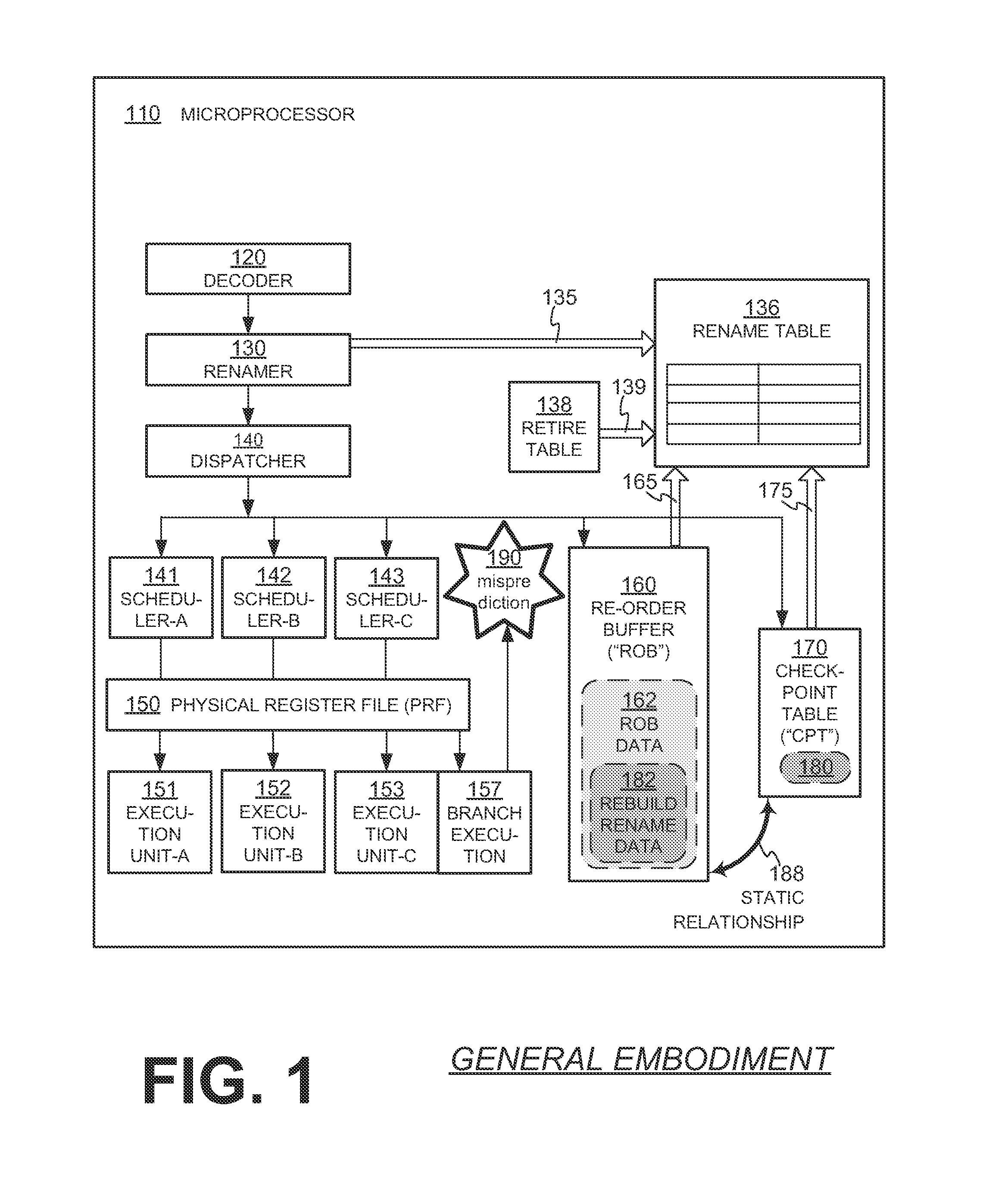

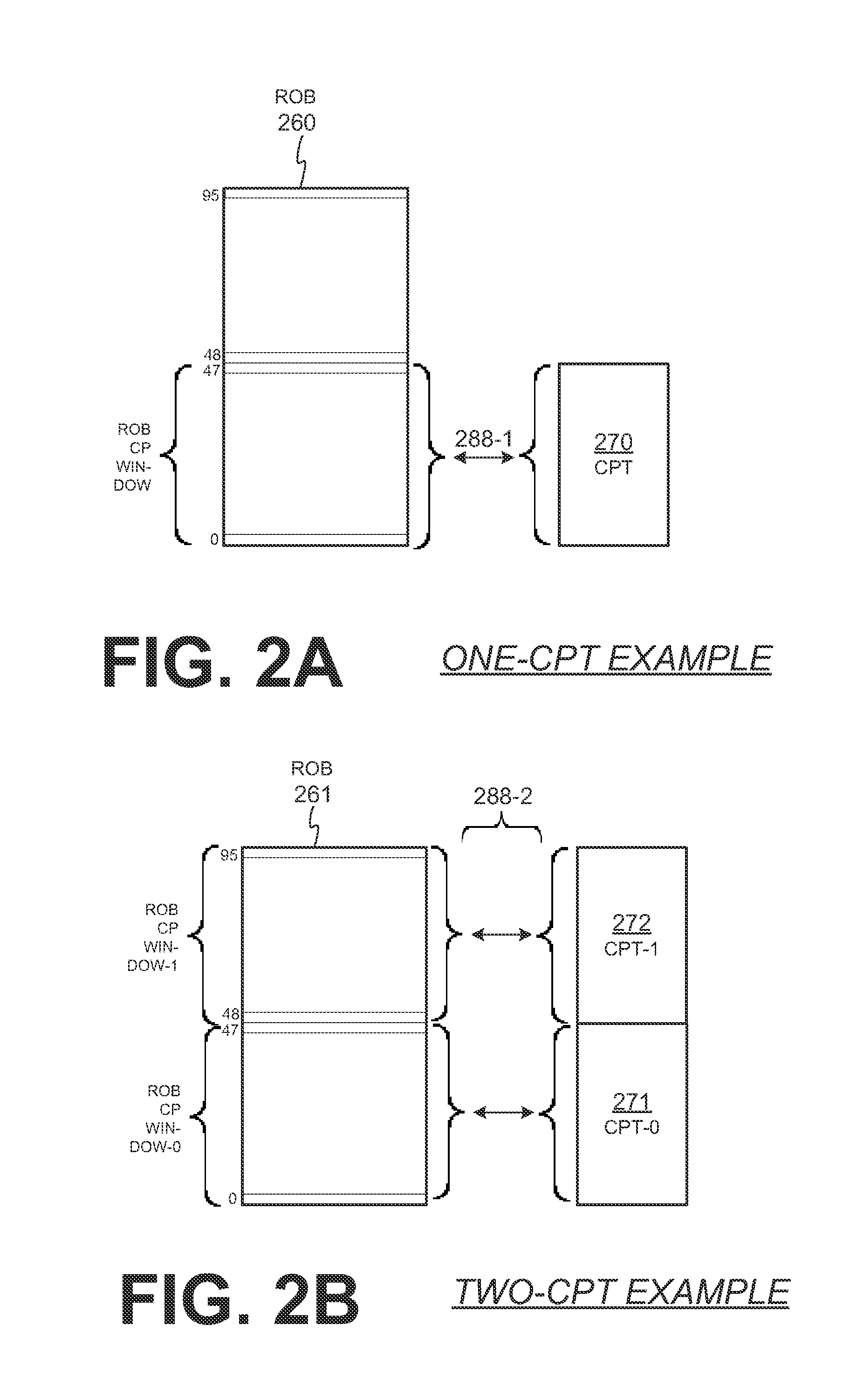

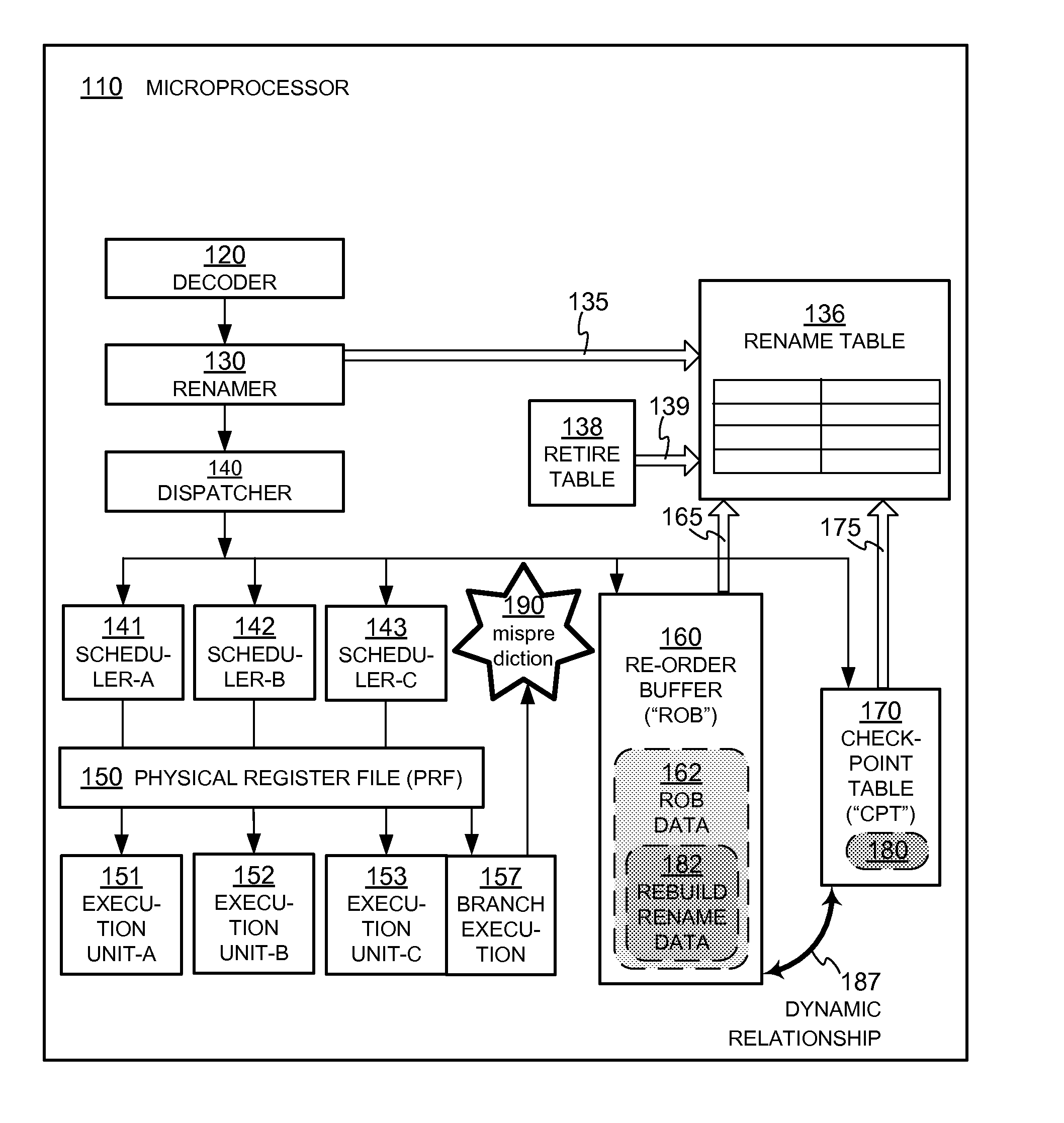

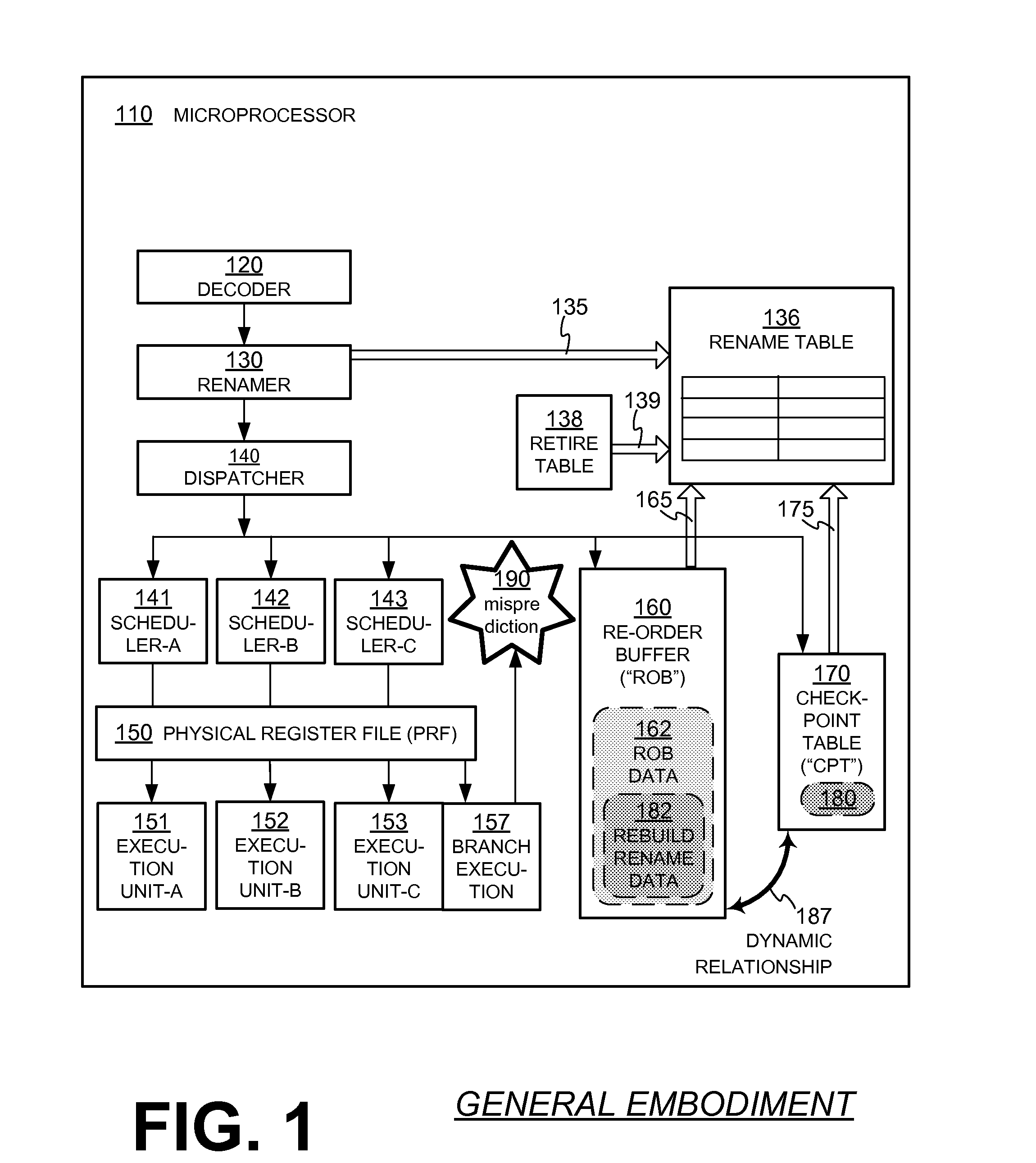

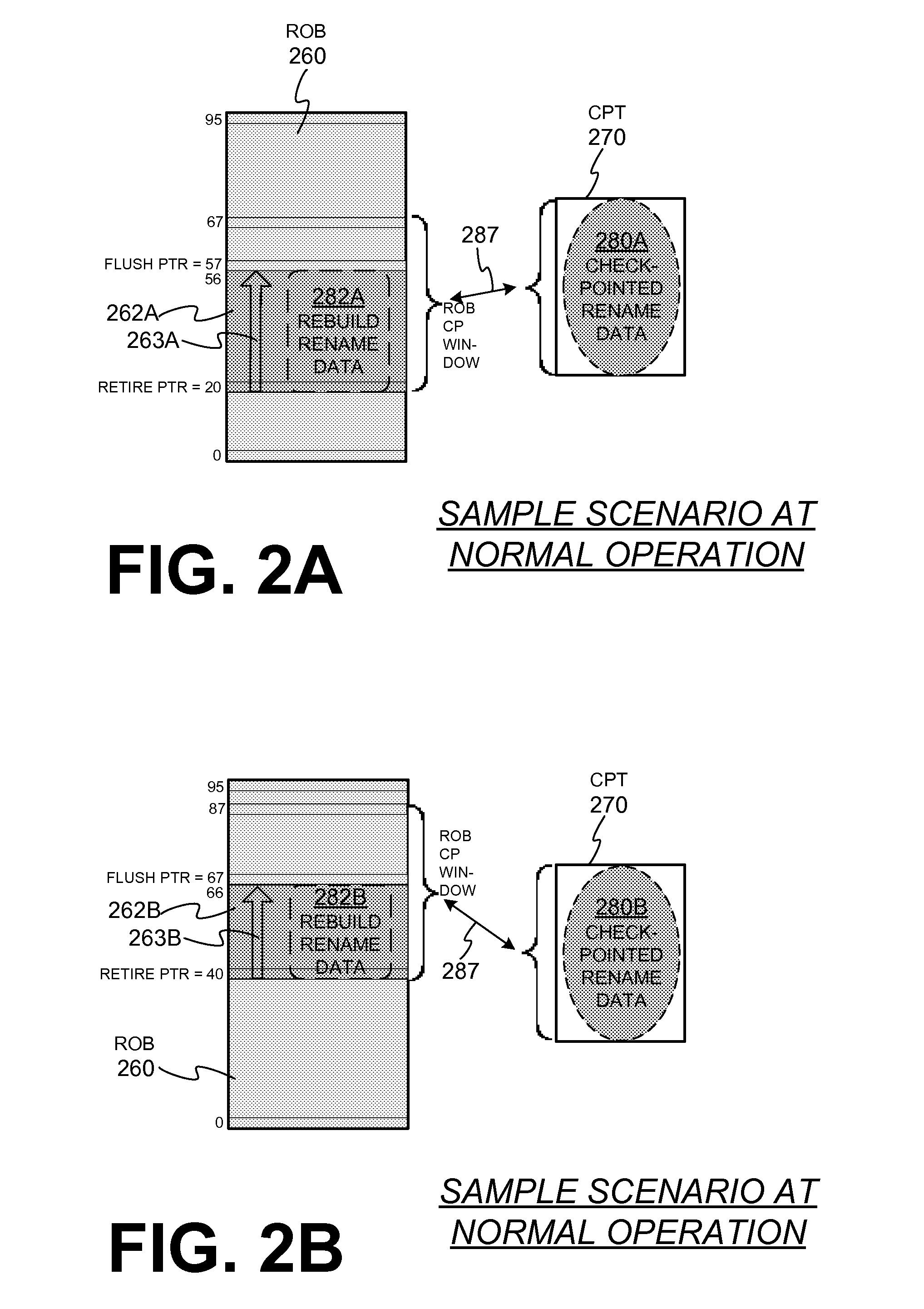

Reorder-buffer-based static checkpointing for rename table rebuilding

ActiveUS20140281393A1Reduce in quantityShorten the timeRegister arrangementsDigital computer detailsCheck pointStatic mapping

Out-of-order CPUs, devices and methods diminish the time penalty from stalling the pipe to rebuild a rename table, such as due to a misprediction. A microprocessor can include a pipe that has a decoder, a dispatcher, and at least one execution unit. A rename table stores rename data, and a check-point table (“CPT”) stores rename data received from the dispatcher. A Re-Order Buffer (“ROB”) stores ROB data, and has a static mapping relationship with the CPT. If the rename table is flushed, such as due to a misprediction, the rename table is rebuilt at least in part by concurrent copying of rename data stored in the CPT, in coordination with walking the ROB.

Owner:SAMSUNG ELECTRONICS CO LTD

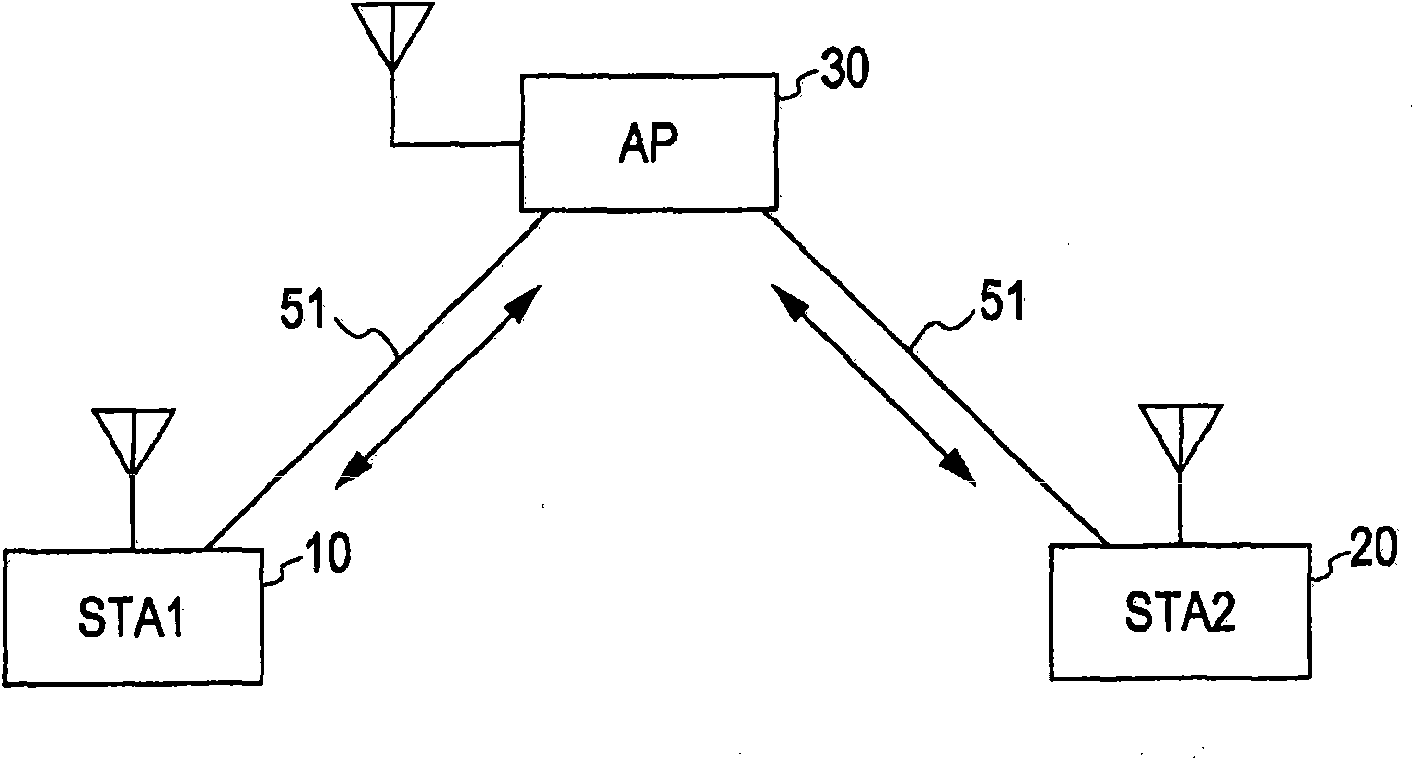

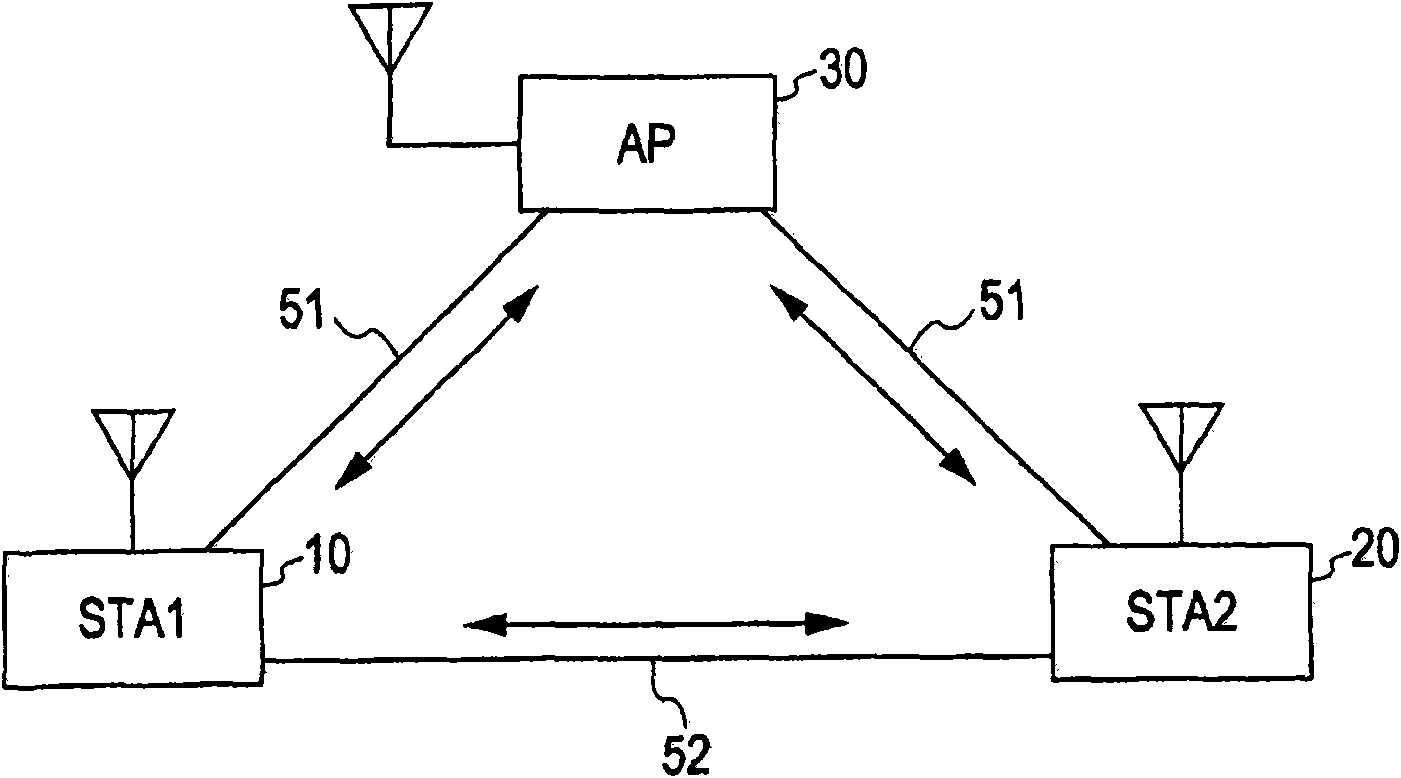

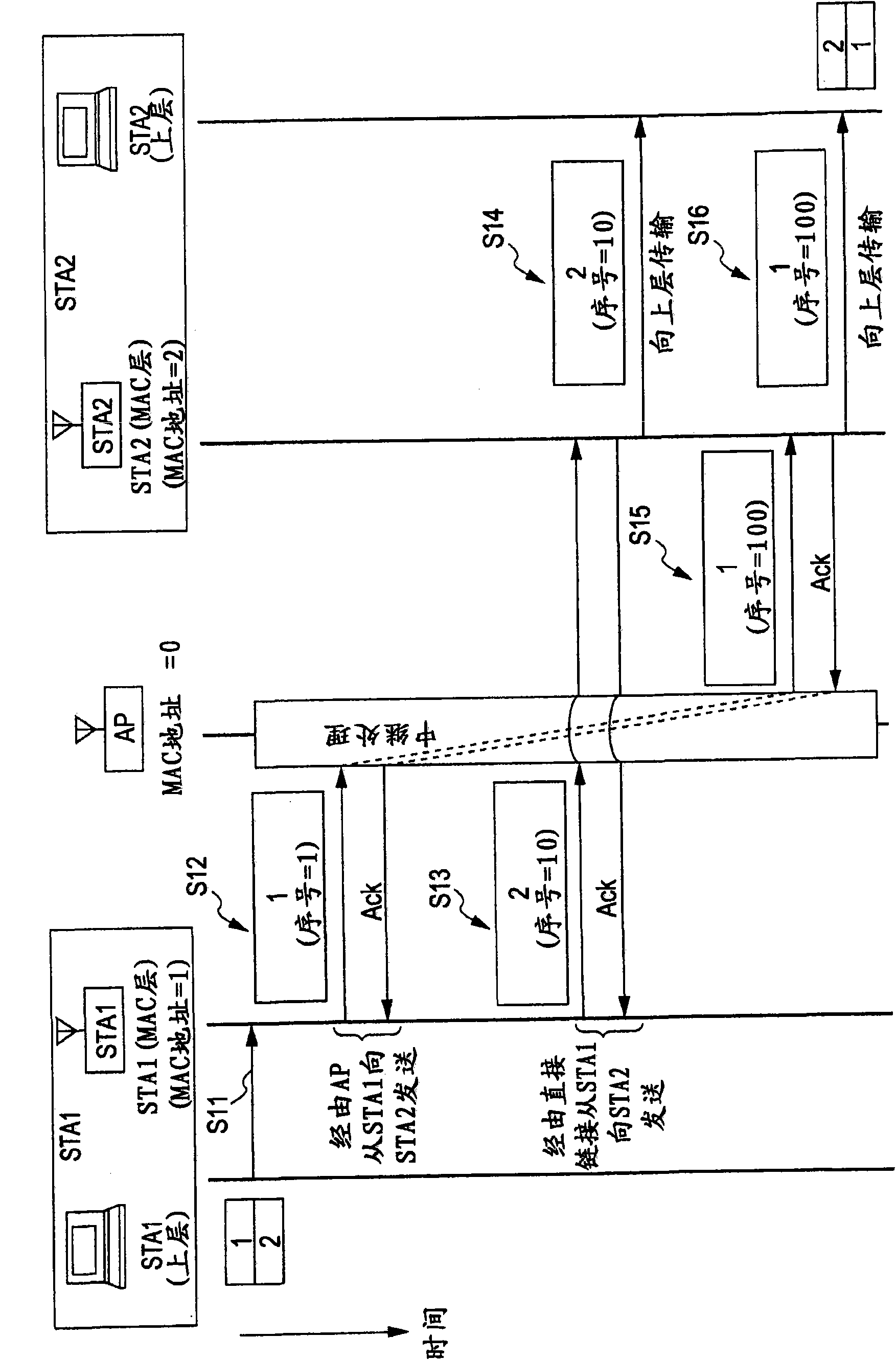

Wireless communication device, communication system, communication control method, and program

InactiveCN101656986APrevent misorderingError prevention/detection by using return channelNetwork traffic/resource managementControl communicationsData source

The invention provides a wireless communication device, a communication system, a communication control method and a program. The wireless communication device includes: a control unit configured to control communication data; and memory configured to store communication data; wherein the control unit performs processing of setting a re-order buffer corresponding to a source address, for storing received data in increments of source address in the memory, storing received packets from a single data source in the re-order buffer corresponding to a source address, and arraying the packet order following sequence numbers set to the received packets.

Owner:SONY GRP CORP

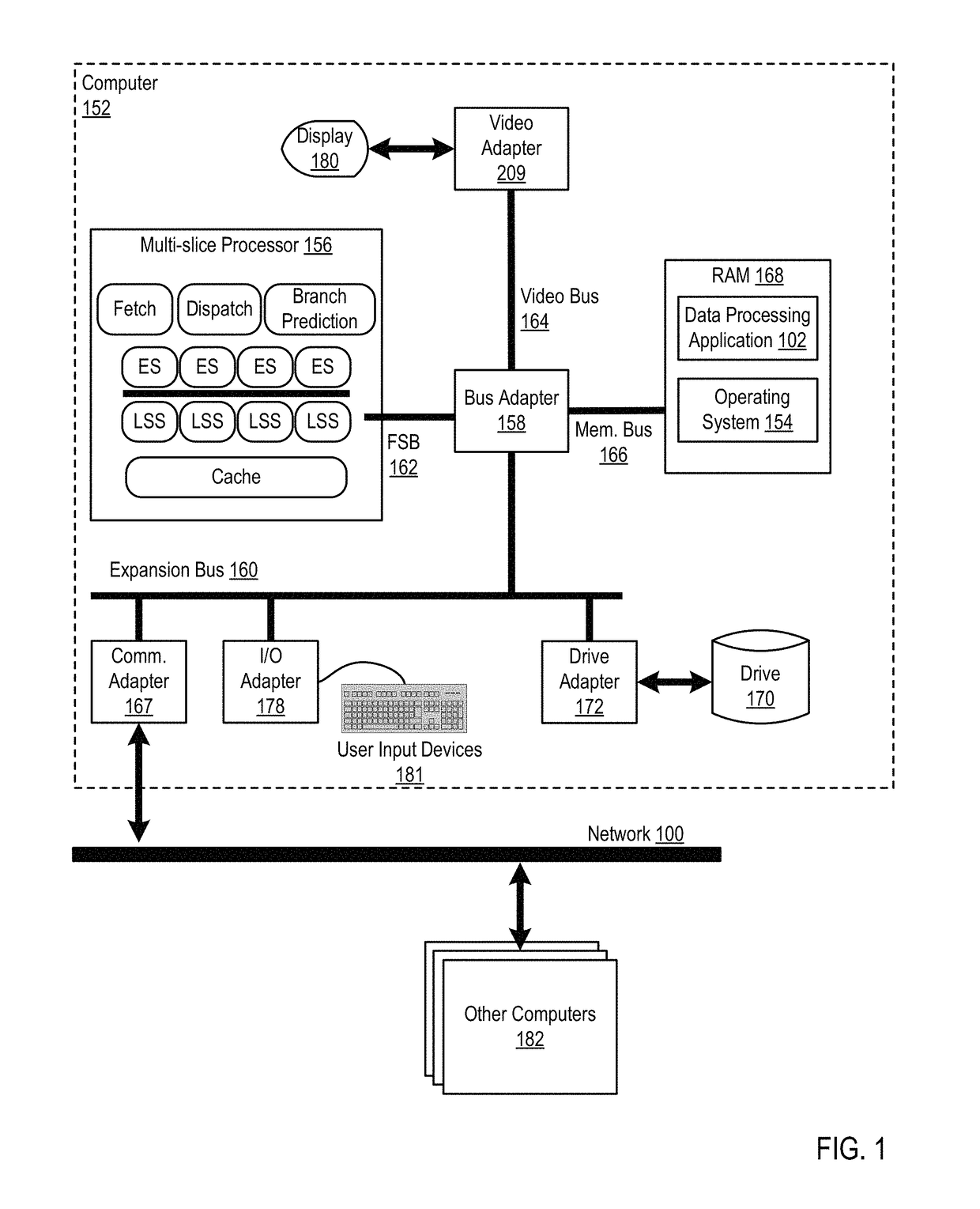

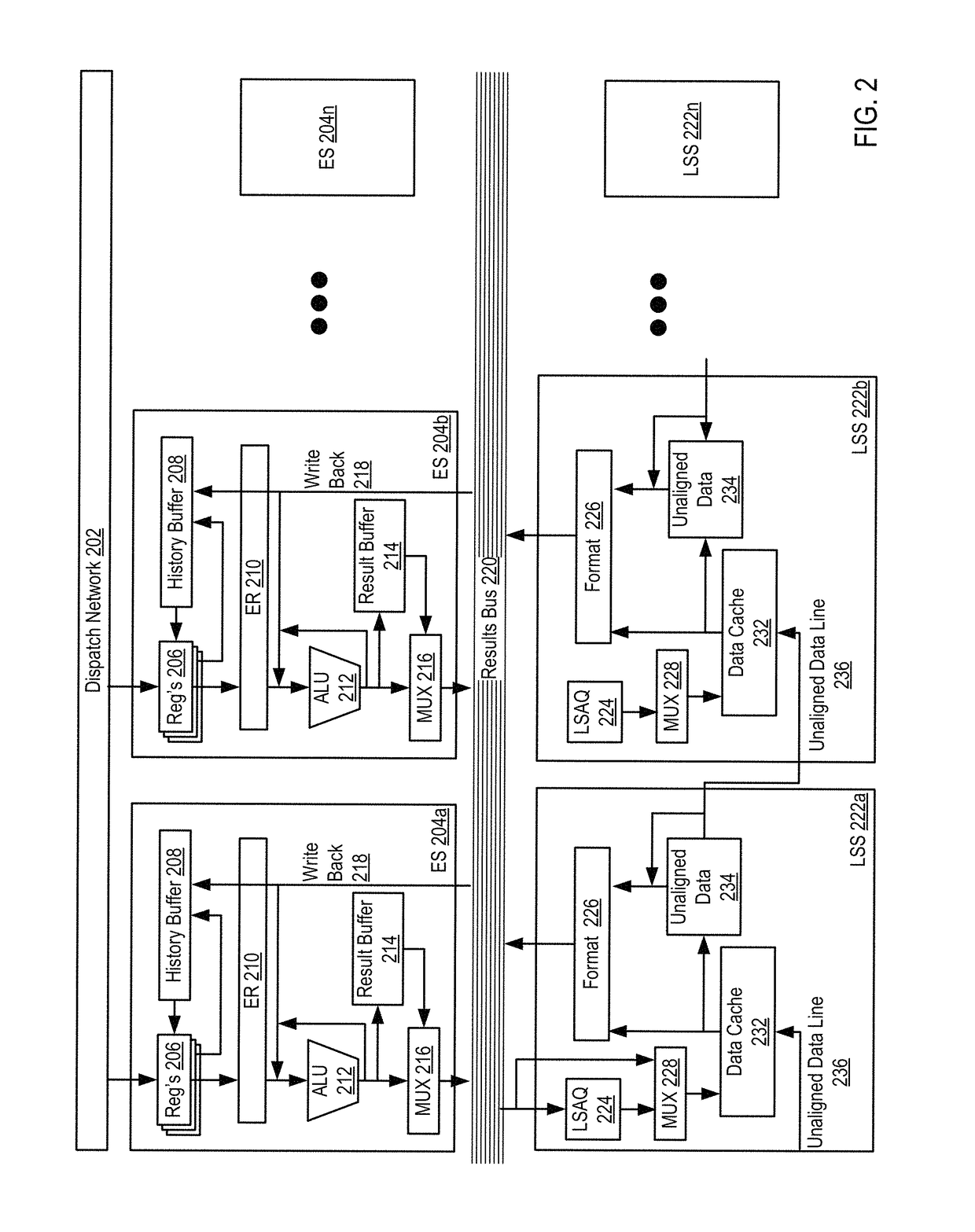

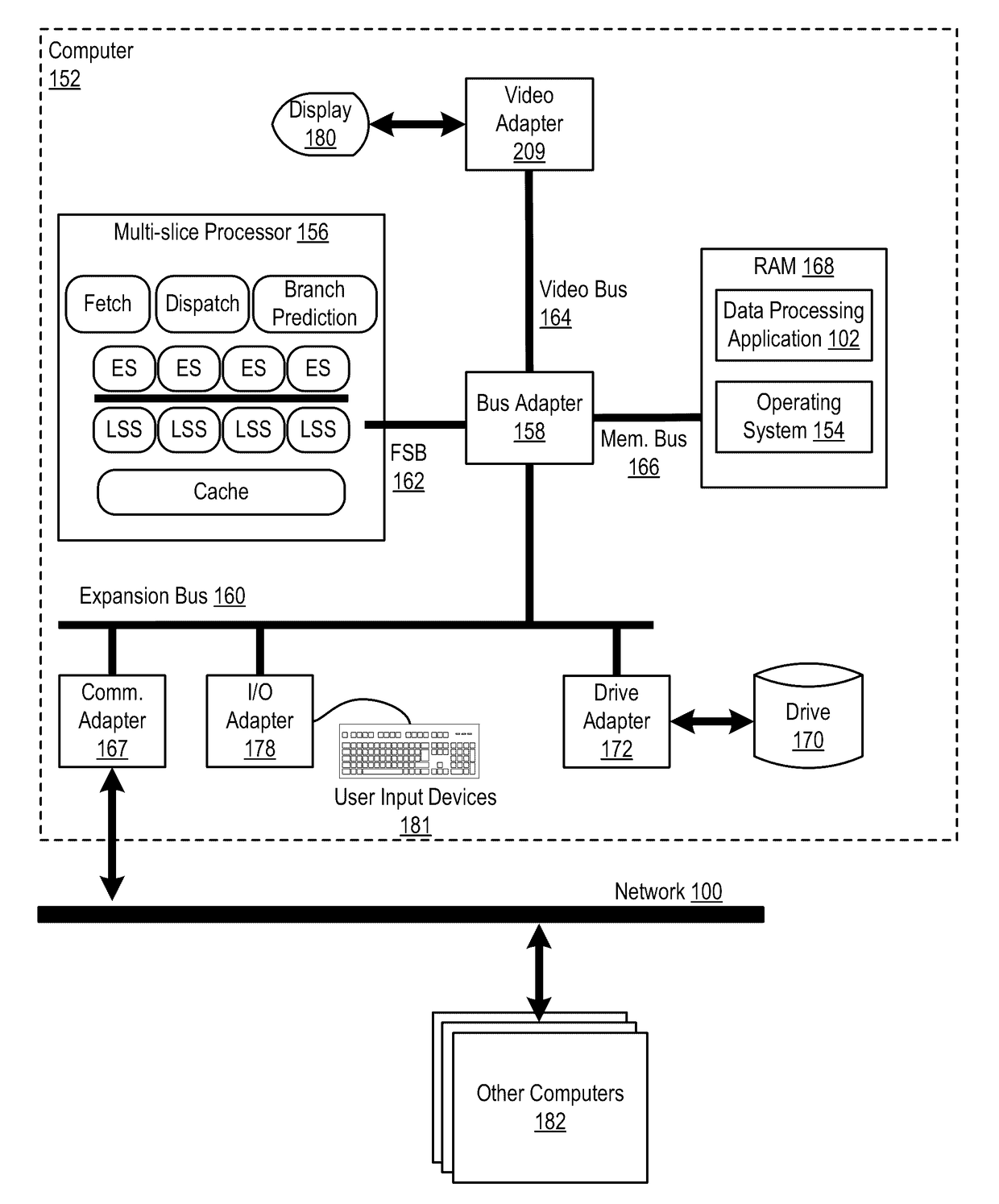

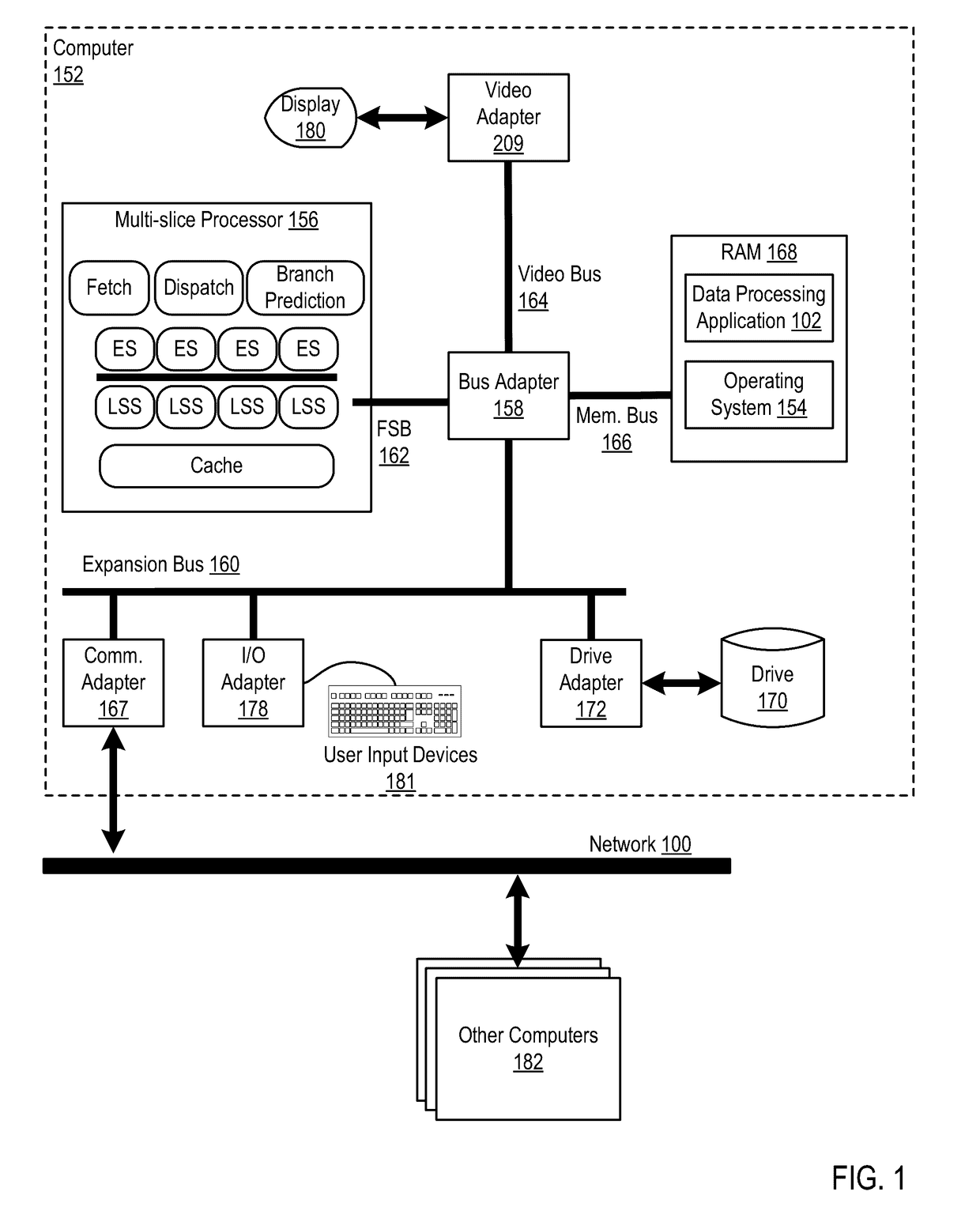

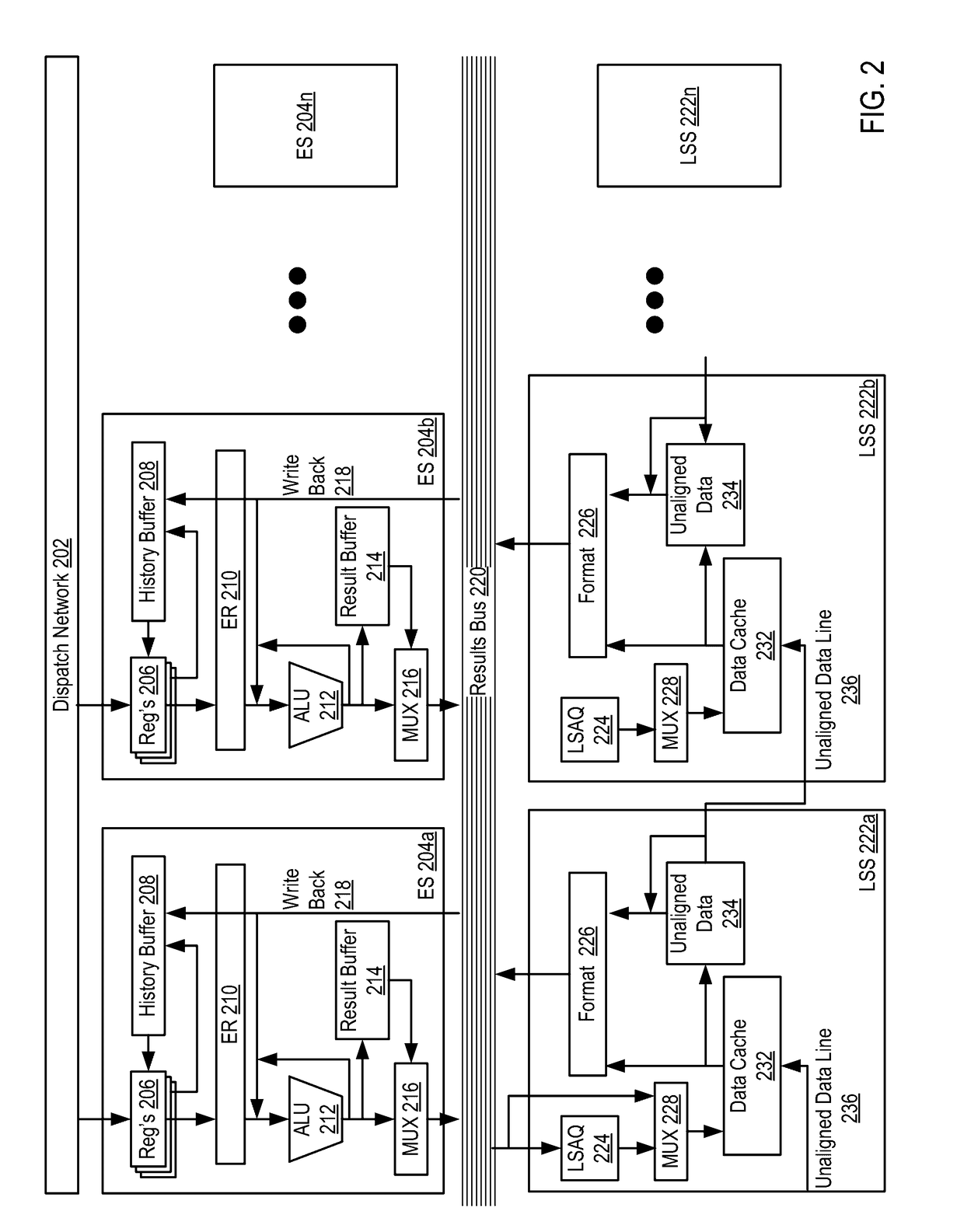

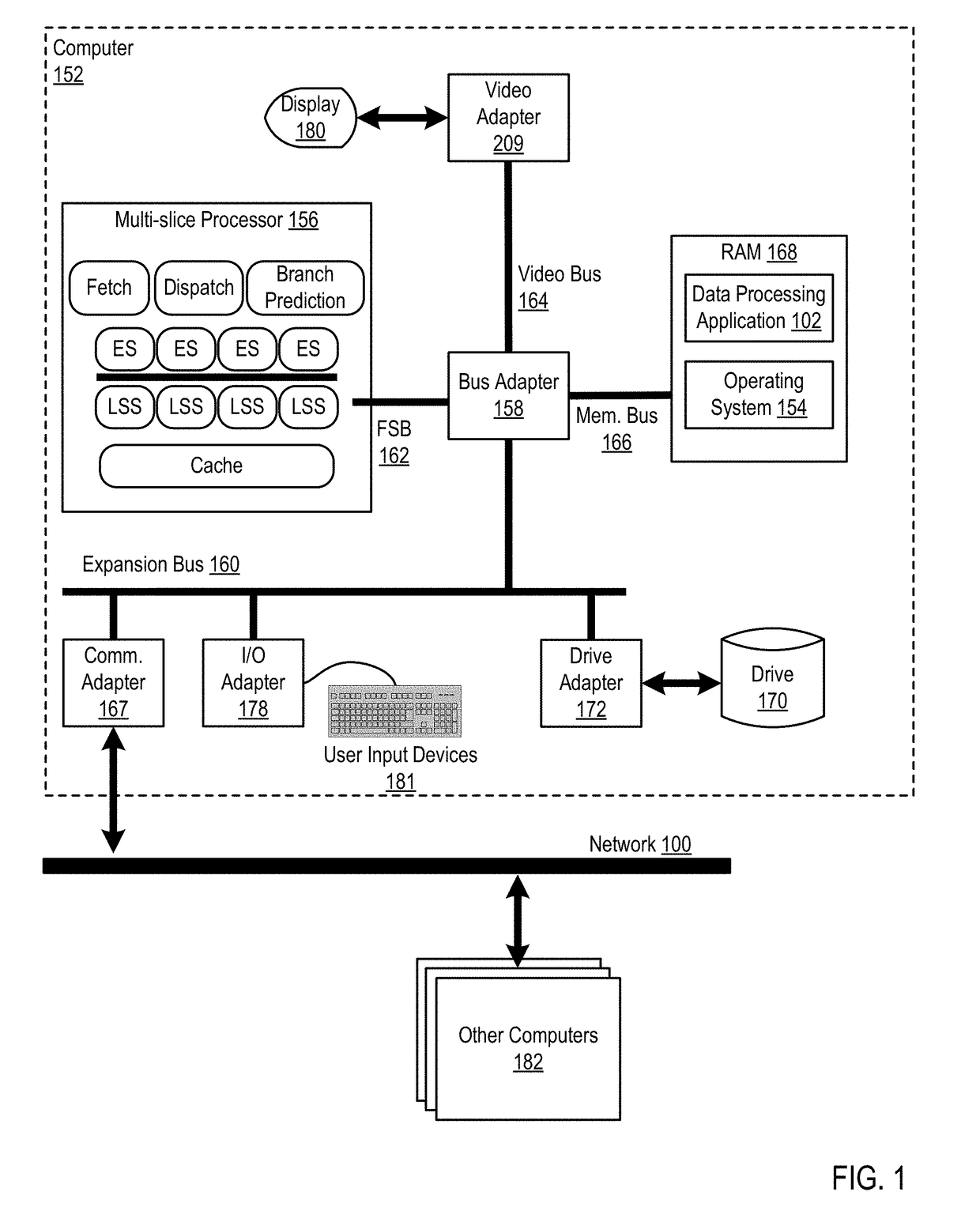

Reducing power consumption in a multi-slice computer processor

InactiveUS9870045B2Volume/mass flow measurementInterprogram communicationProcessing InstructionMulti slice

Owner:INT BUSINESS MASCH CORP

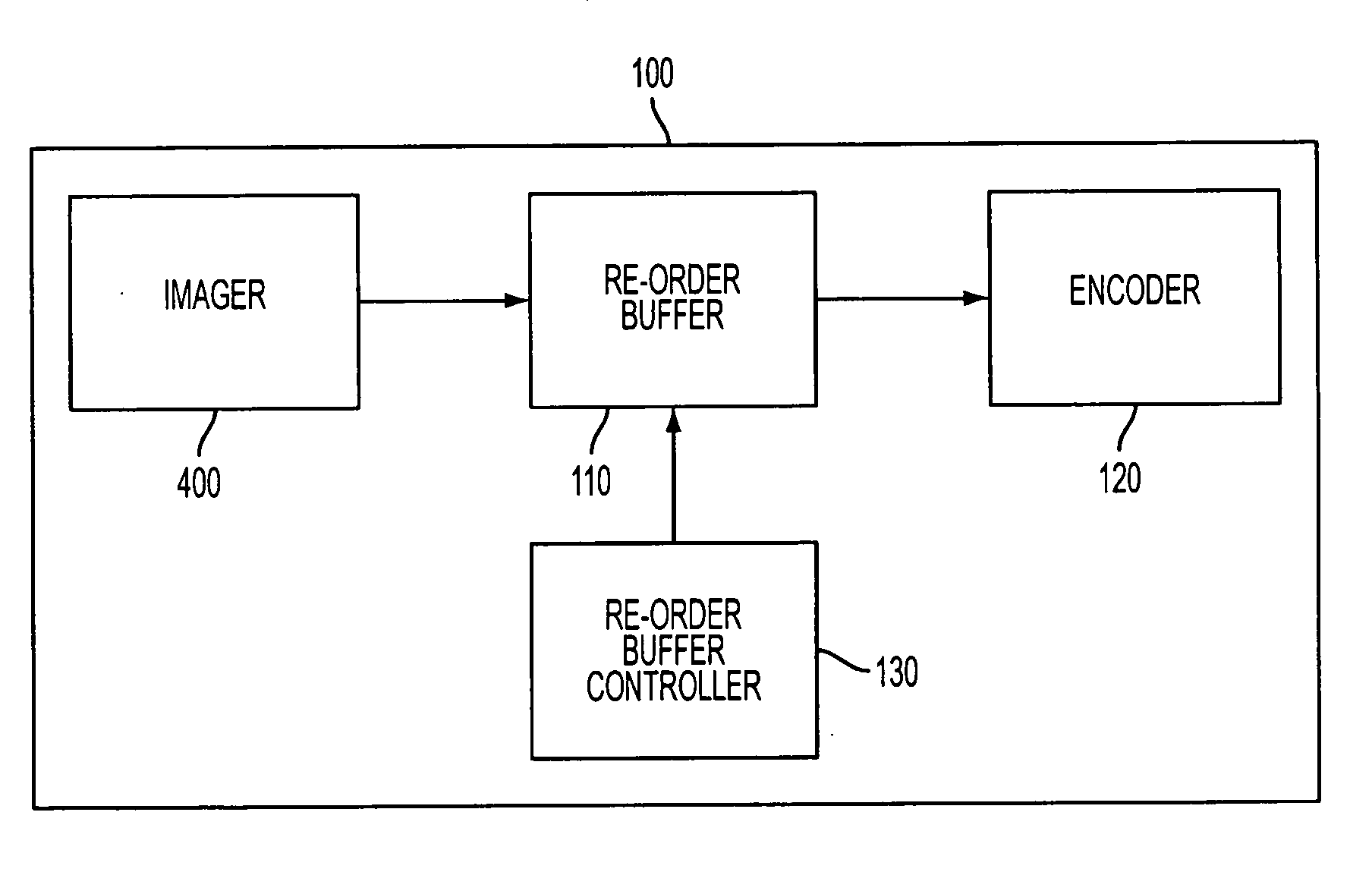

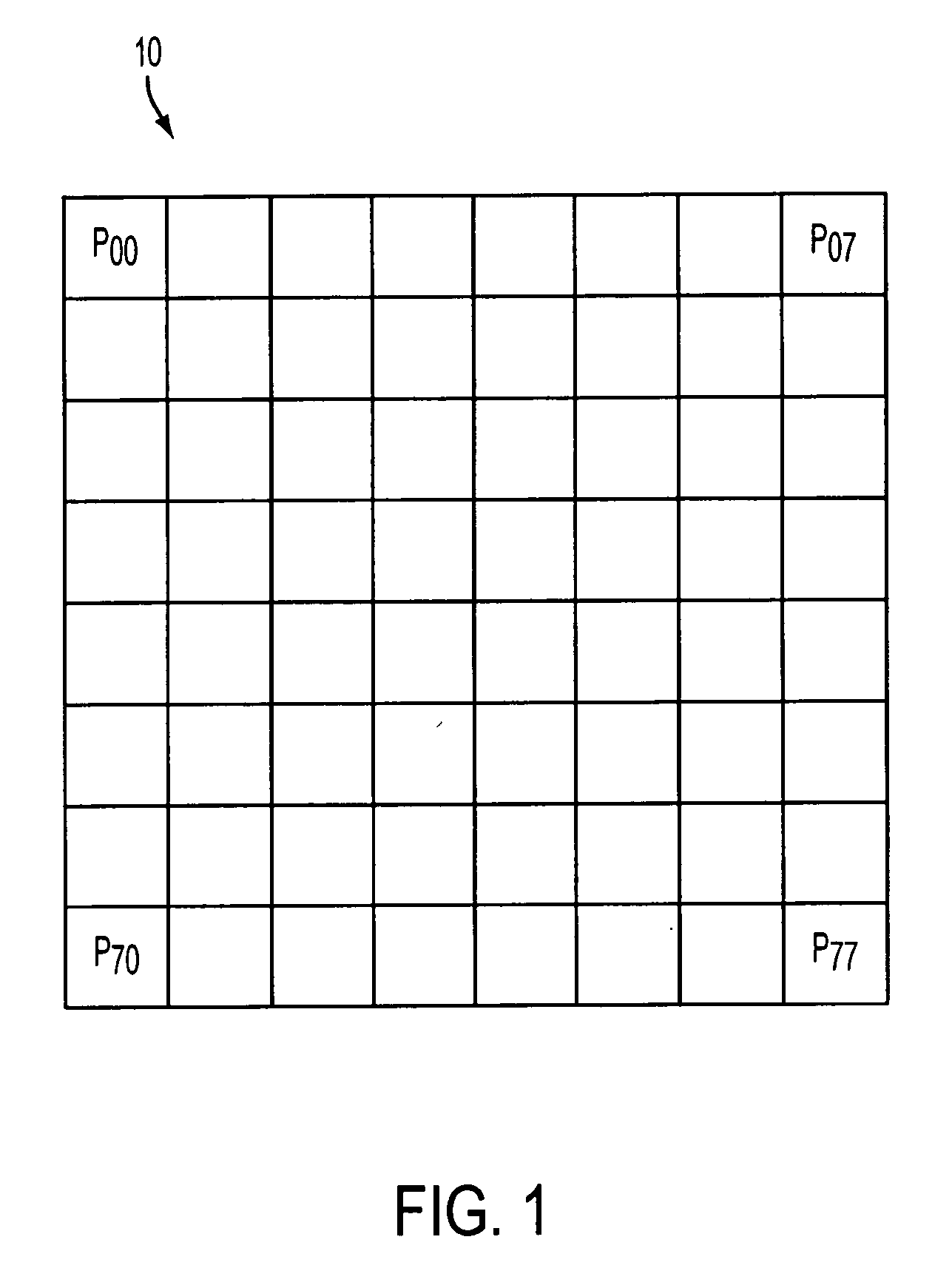

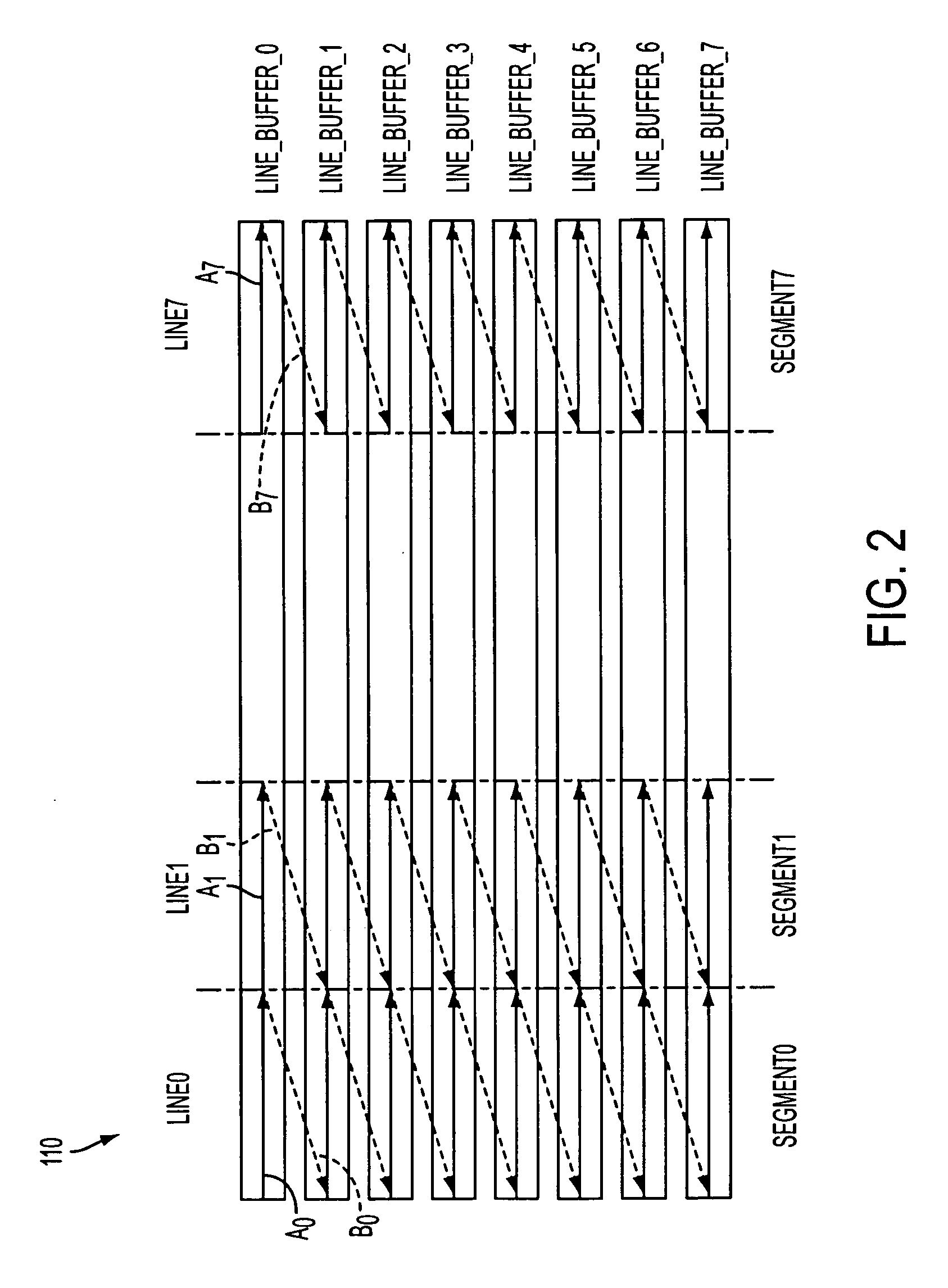

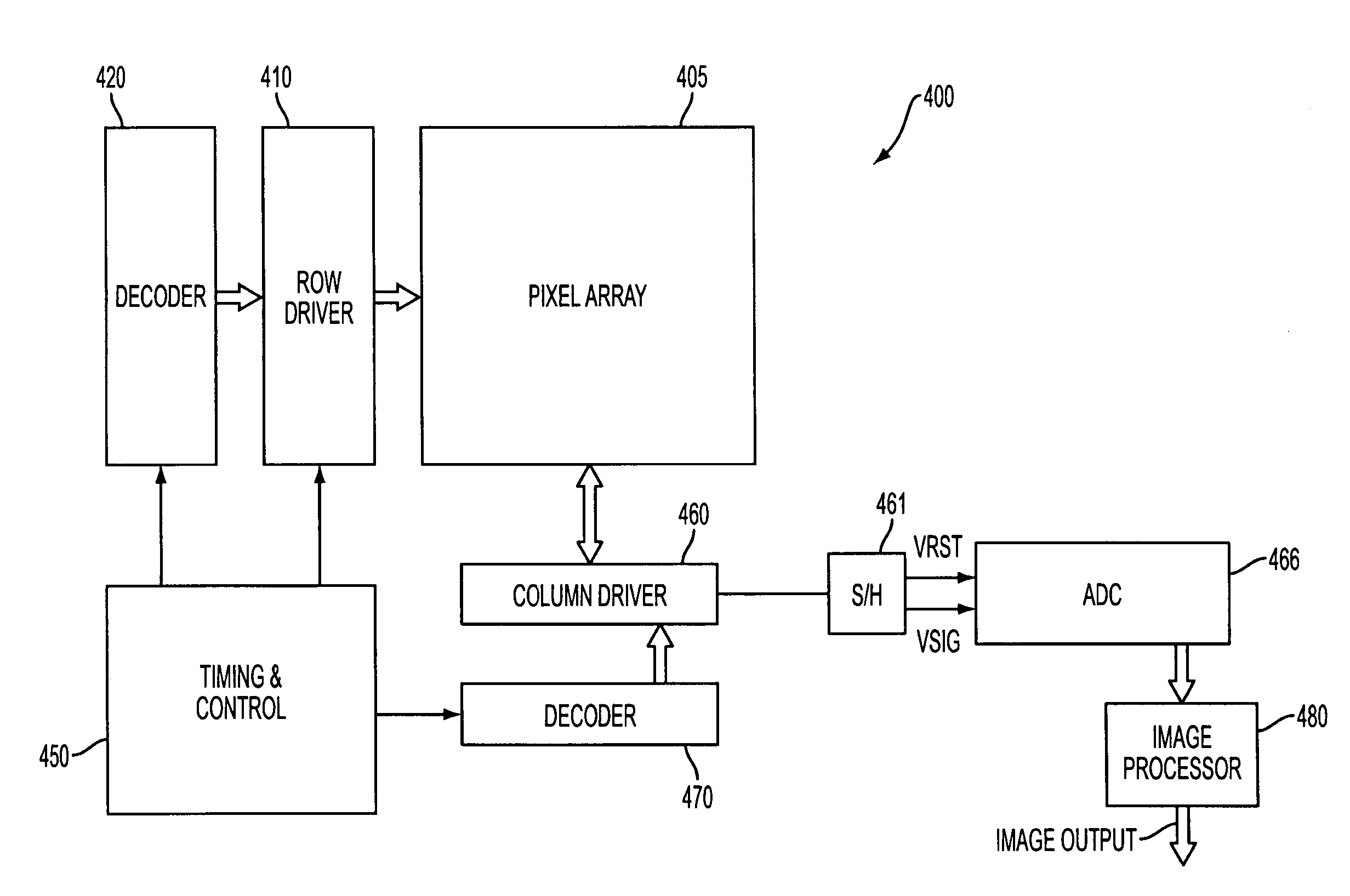

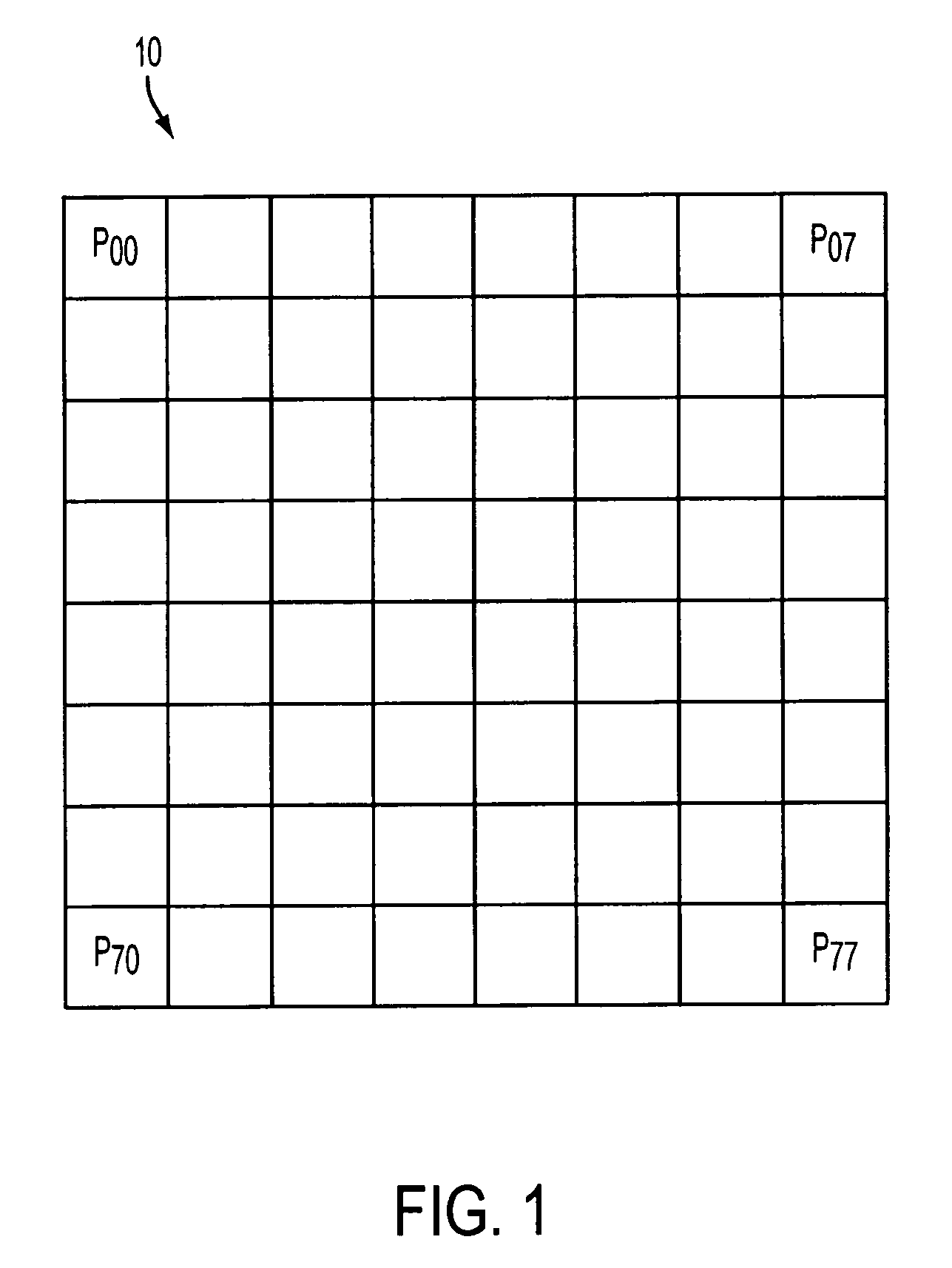

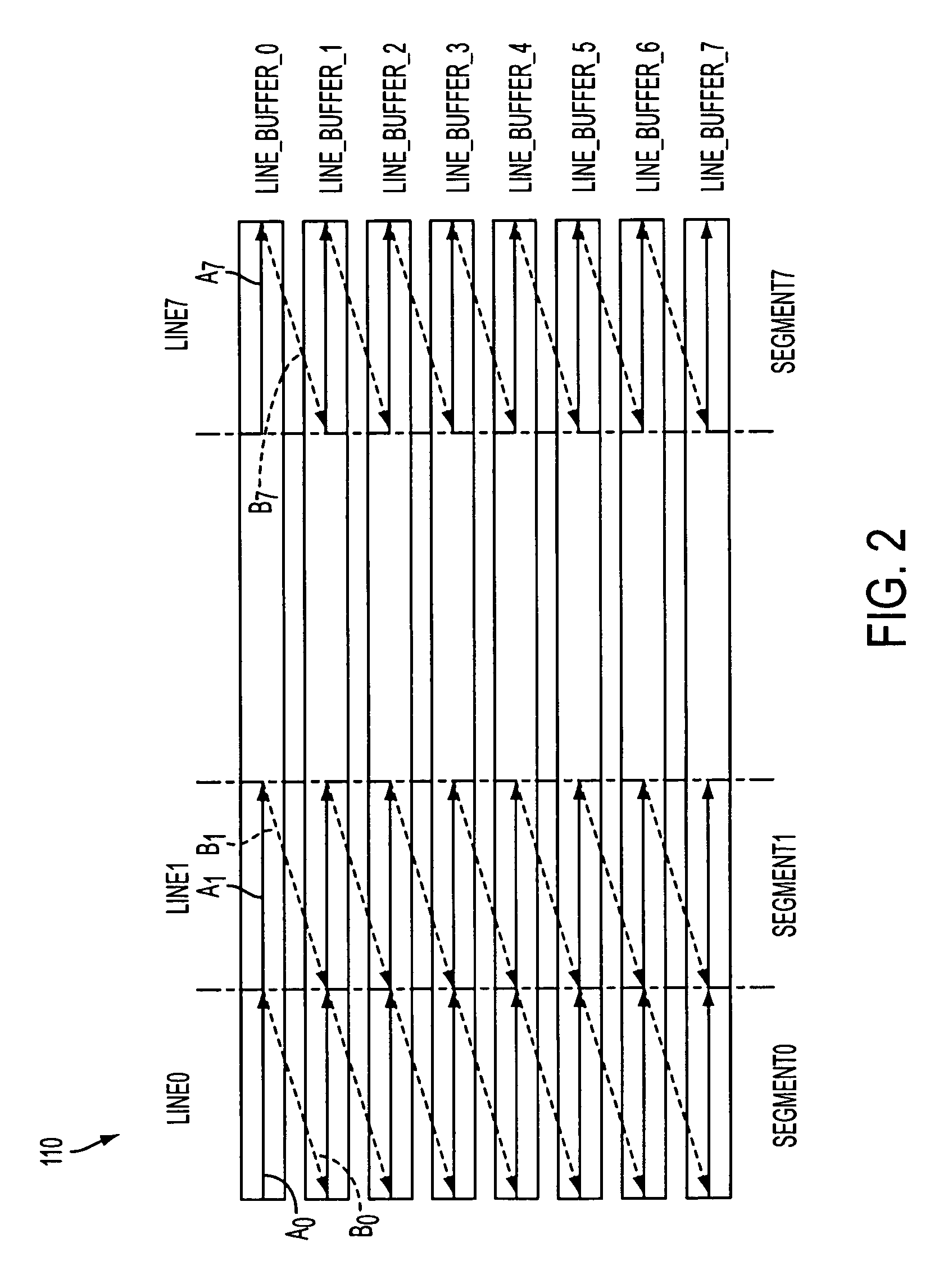

Scan line to block re-ordering buffer for image compression

ActiveUS20070031044A1Character and pattern recognitionDigital video signal modificationScan lineImage compression

A re-order buffer memory in a real-time application such as e.g., an imager. Initially, input data is written into the re-order buffer using a first addressing mode, which causes the data to be stored in a line-by-line manner. Prior to receiving the last line of input data, the stored data is read-out in blocks of data that spans multiples lines in the buffer. This frees up space in the re-order buffer. Subsequently received input data is written into the re-order buffer using a second addressing mode, which stores the newly received data in vertical segments of the re-order buffer whose stored data has already been read-out. Writing / reading of the re-order buffer alternates between the first and second addressing modes. Using this technique, a single buffer may be used to input new data while existing data is being read-out.

Owner:MICRON TECH INC

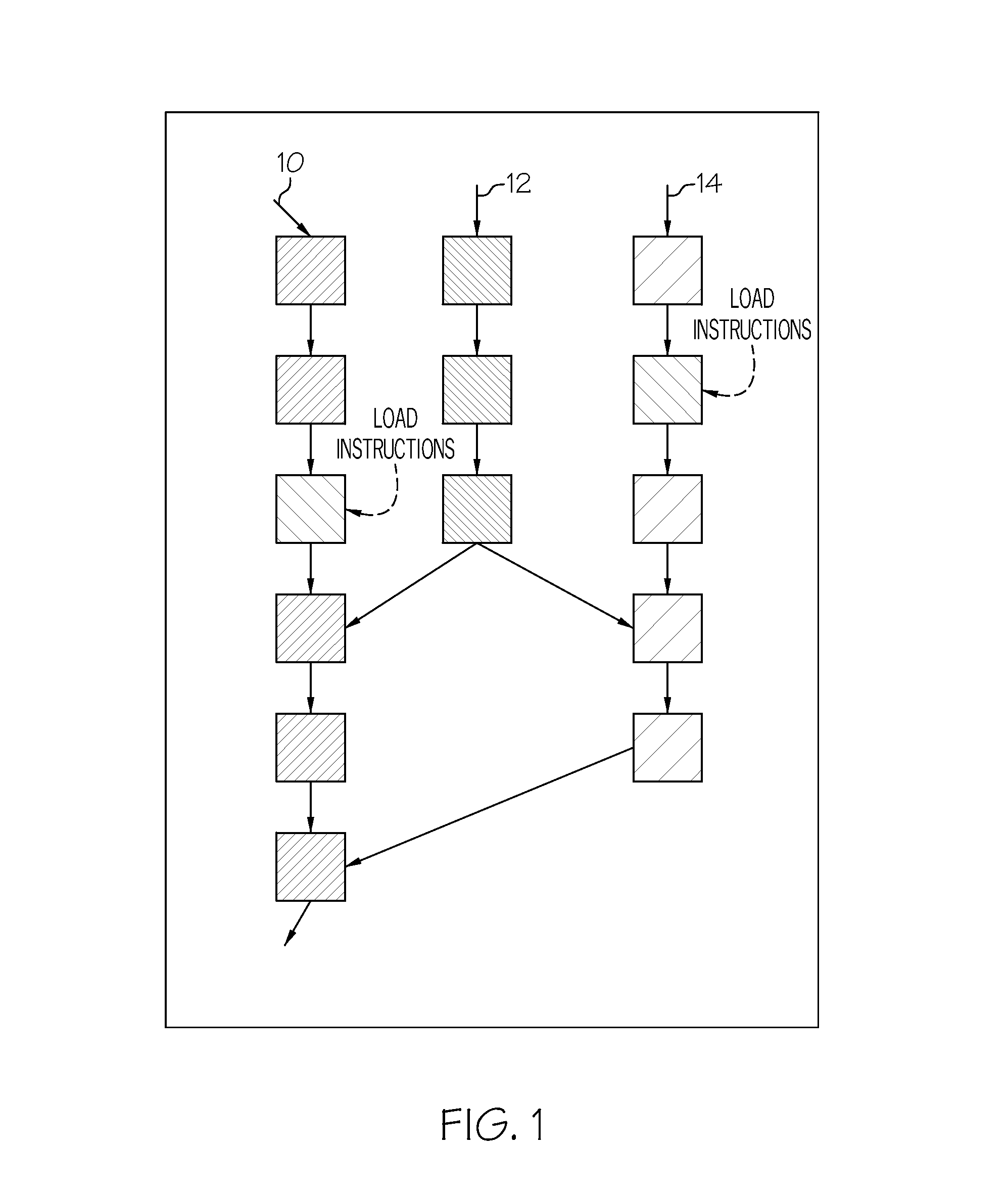

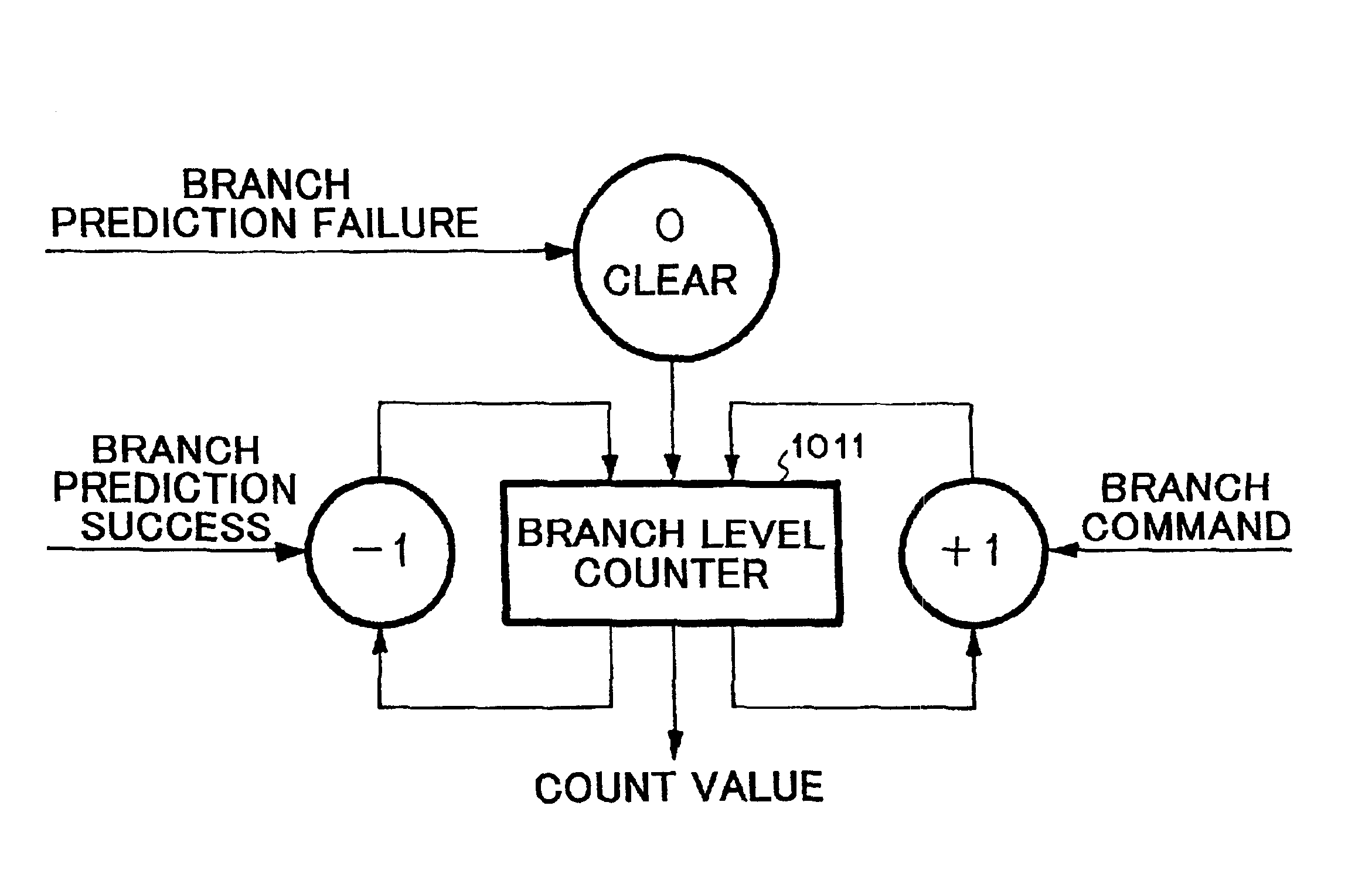

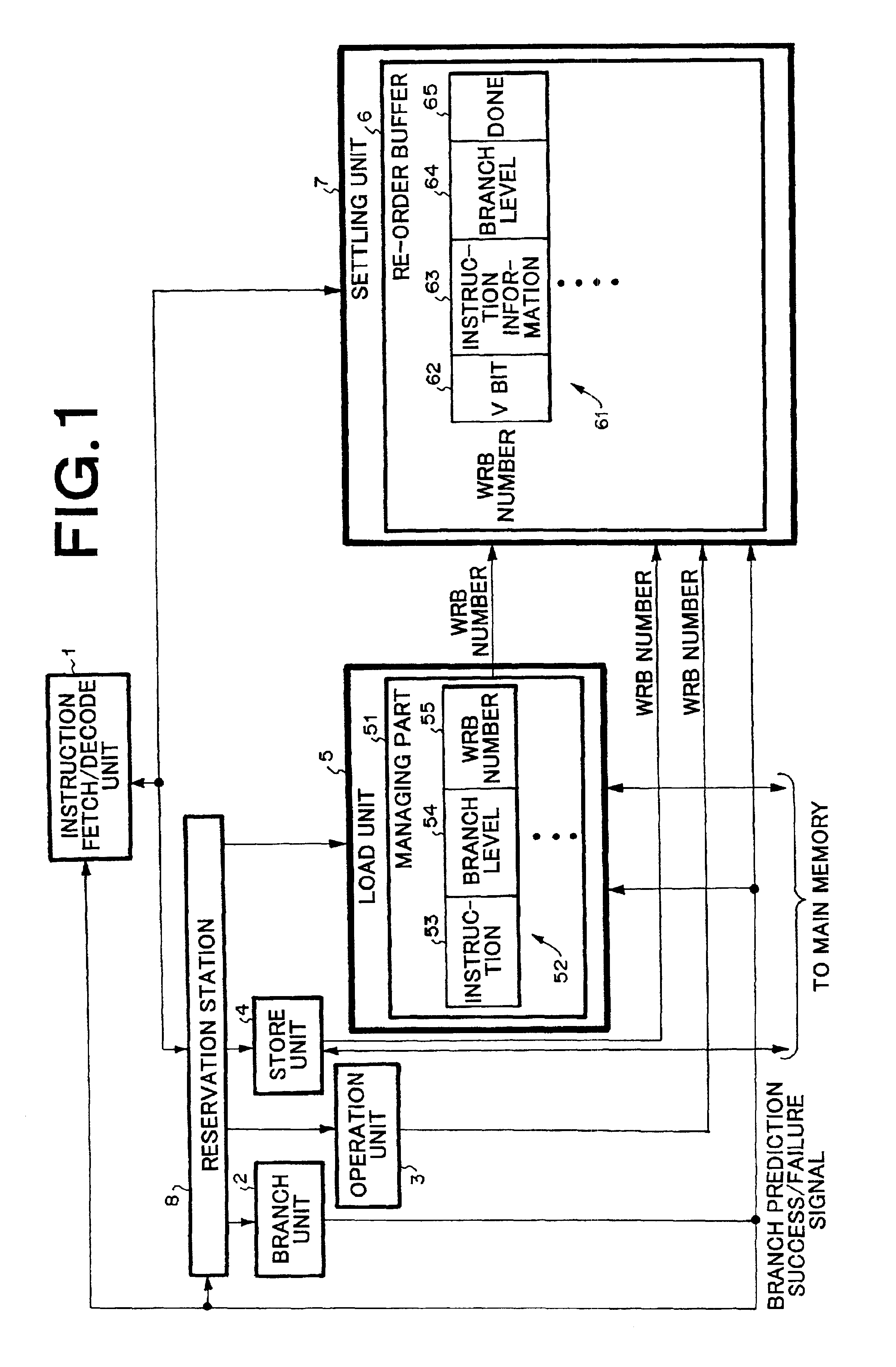

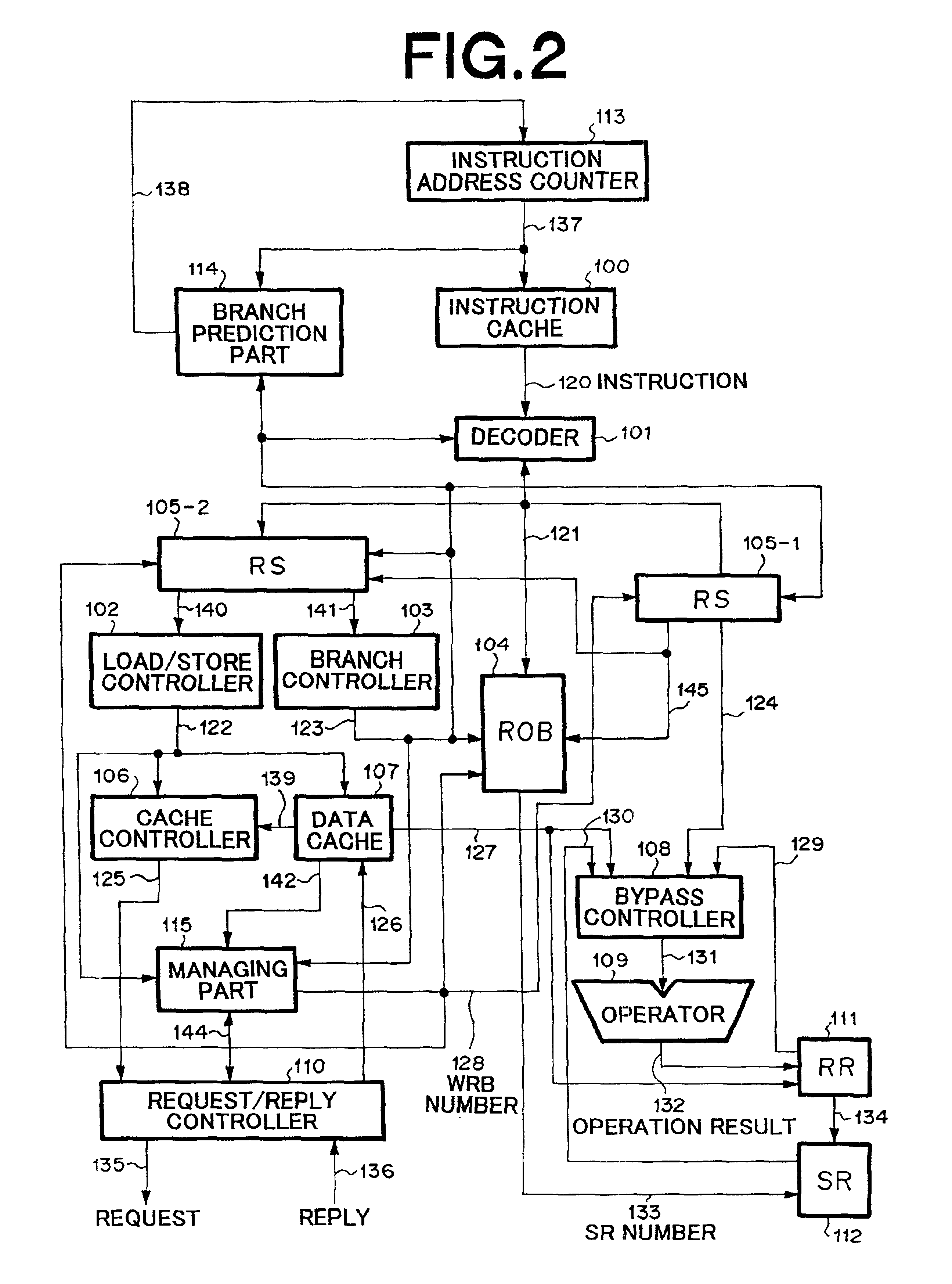

Processor for managing latest speculation states and efficiently reusing reorder buffer entries

InactiveUS6938150B2Improve efficiencySuppress notificationDigital computer detailsConcurrent instruction executionLoad instructionRe-order buffer

By using an entry number (WRB number) of a re-order buffer 6, each of function units such as an operation unit 3, a store unit 4, a load unit 5, etc. notifies to the re-order buffer 6 the processing end for a instruction stored in the entry concerned in the unit thereof. The load unit 5 manages the latest speculation state of a load instruction issued on the basis of a branch prediction success / failure signal output from the branch unit 2, and makes no notification to the re-order buffer 6 on the basis of WRB number for subsequent load instructions of a branch-prediction failed branch instruction even when the processing of the instruction is finished. Accordingly, the re-order buffer 6 can re-use entries in which the subsequent instructions of the branch prediction failed branch instruction are stored.

Owner:NEC CORP

Stateless capture of data linear addresses during precise event based sampling

A processor includes a logic for stateless capture of data linear addresses (DLA) during precise event based sampling (PEBS) for an out-of-order execution engine. The engine may include a PEBS unit with logic to increment a counter each time an instance of a designated micro-op is retired a reorder buffer, capture output DLA referenced by an instance of the micro-op that executes after the counter overflows, set a captured bit associated with a reorder buffer identifier for the instance of the micro-op, and store a PEBS record in a debug storage when the instance of the micro-op is retired from the reorder buffer. The designated micro-op references a DLA of a memory accessible to the processor.

Owner:INTEL CORP

Reorder-buffer-based dynamic checkpointing for rename table rebuilding

ActiveUS20140281414A1Reduce in quantityShorten the timeRegister arrangementsDigital computer detailsCheck pointTheoretical computer science

Out-of-order CPUs, devices and methods diminish the time penalty from stalling the pipe to rebuild a rename table, such as due to a misprediction. A microprocessor can include a pipe that has a decoder, a dispatcher, and at least one execution unit. A rename table stores rename data, and a check-point table (“CPT”) stores rename data received from the dispatcher. A Re-Order Buffer (“ROB”) stores ROB data, and has a dynamic mapping relationship with the CPT. If the rename table is flushed, such as due to a misprediction, the rename table is rebuilt at least in part by concurrent copying of rename data stored in the CPT, in coordination with walking the ROB.

Owner:SAMSUNG ELECTRONICS CO LTD

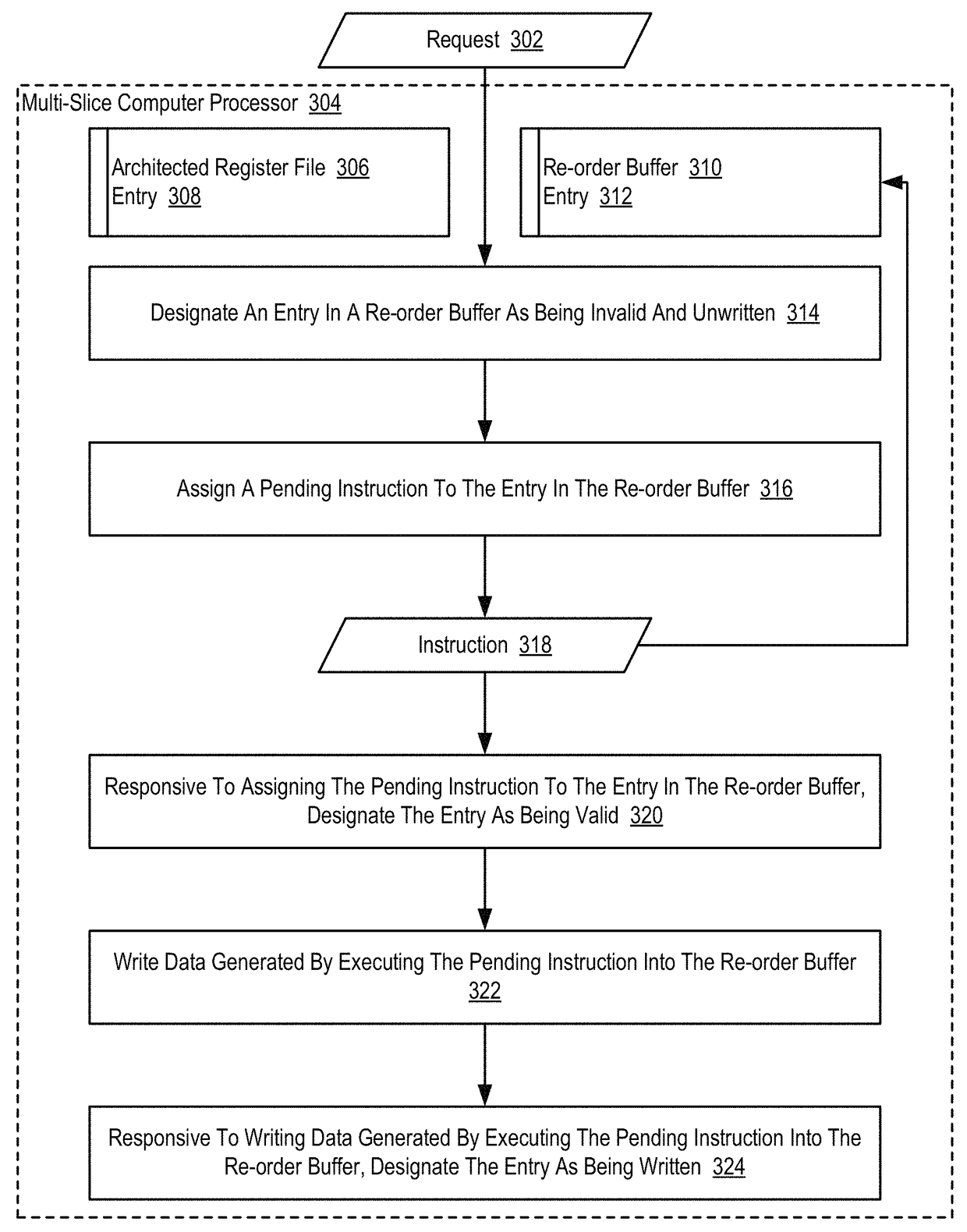

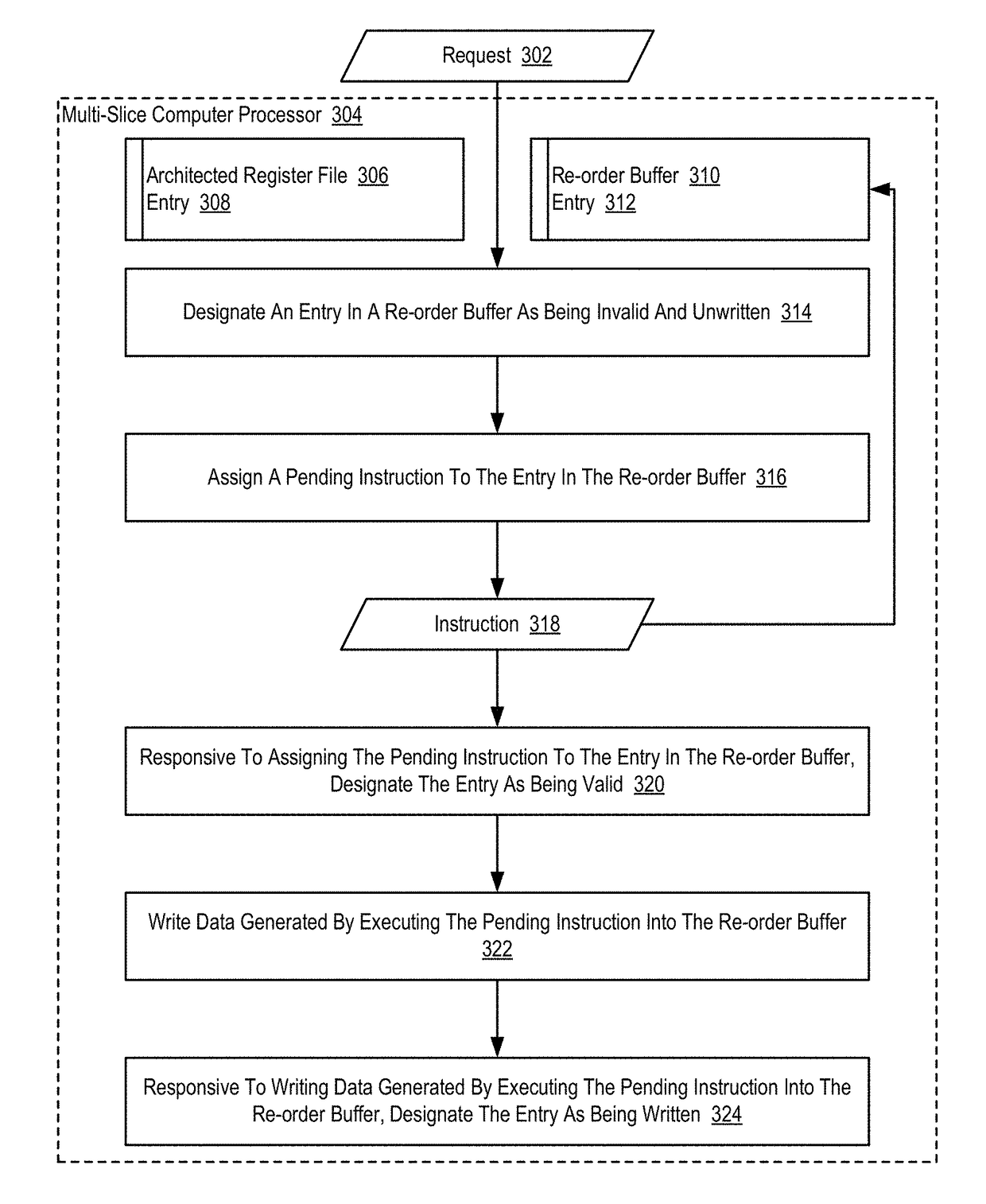

Reducing power consumption in a multi-slice computer processor

InactiveUS20170168539A1Reduce power consumptionConcurrent instruction executionPower supply for data processingProcessing InstructionMulti slice

Reducing power consumption in a multi-slice computer processor that includes a re-order buffer and an architected register file, including: designating an entry in the re-order buffer as being invalid and unwritten; assigning a pending instruction to the entry in the re-order buffer; responsive to assigning the pending instruction to the entry in the re-order buffer, designating the entry as being valid; writing data generated by executing the pending instruction into the re-order buffer; and responsive to writing data generated by executing the pending instruction into the re-order buffer, designating the entry as being written.

Owner:IBM CORP

Using L1 cache as re-order buffer

ActiveUS9471320B2Eliminate needMemory architecture accessing/allocationConditional code generationRegister bankData request

A method is shown that eliminates the need for a dedicated reorder buffer register bank or memory space in a multi level cache system. As data requests from the L2 cache may be returned out of order, the L1 cache uses it's cache memory to buffer the out of order data and provides the data to the requesting processor in the correct order from the buffer.

Owner:TEXAS INSTR INC

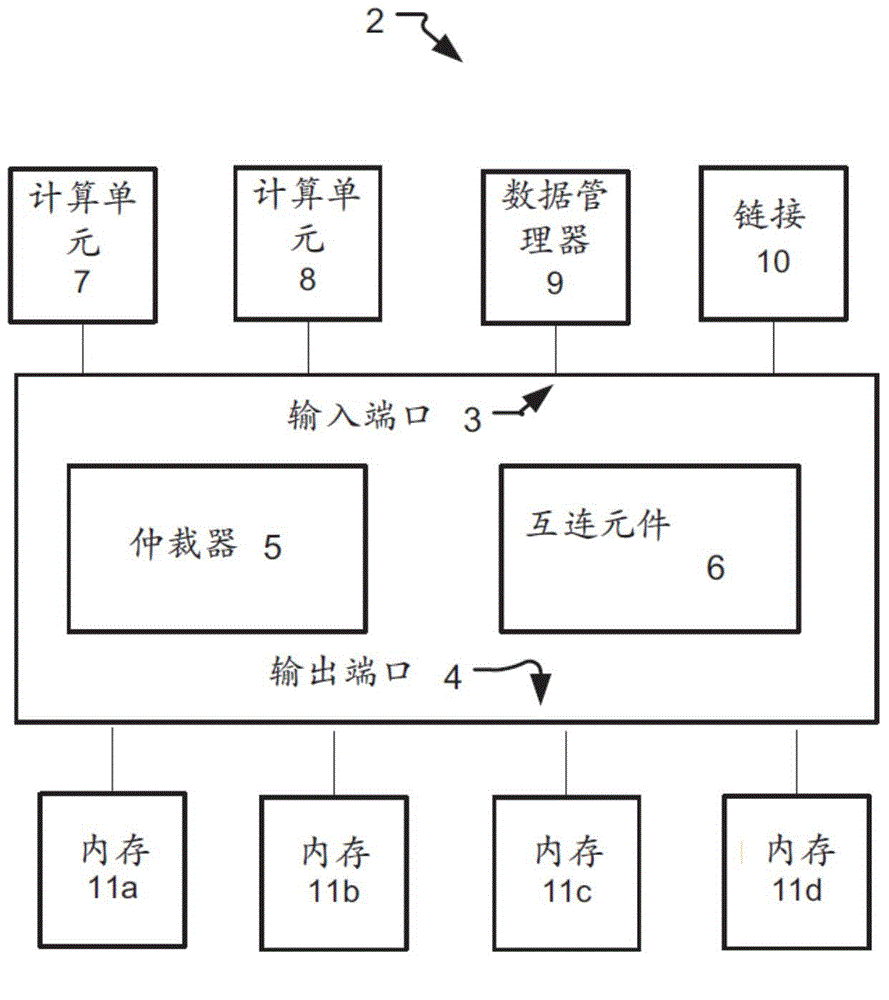

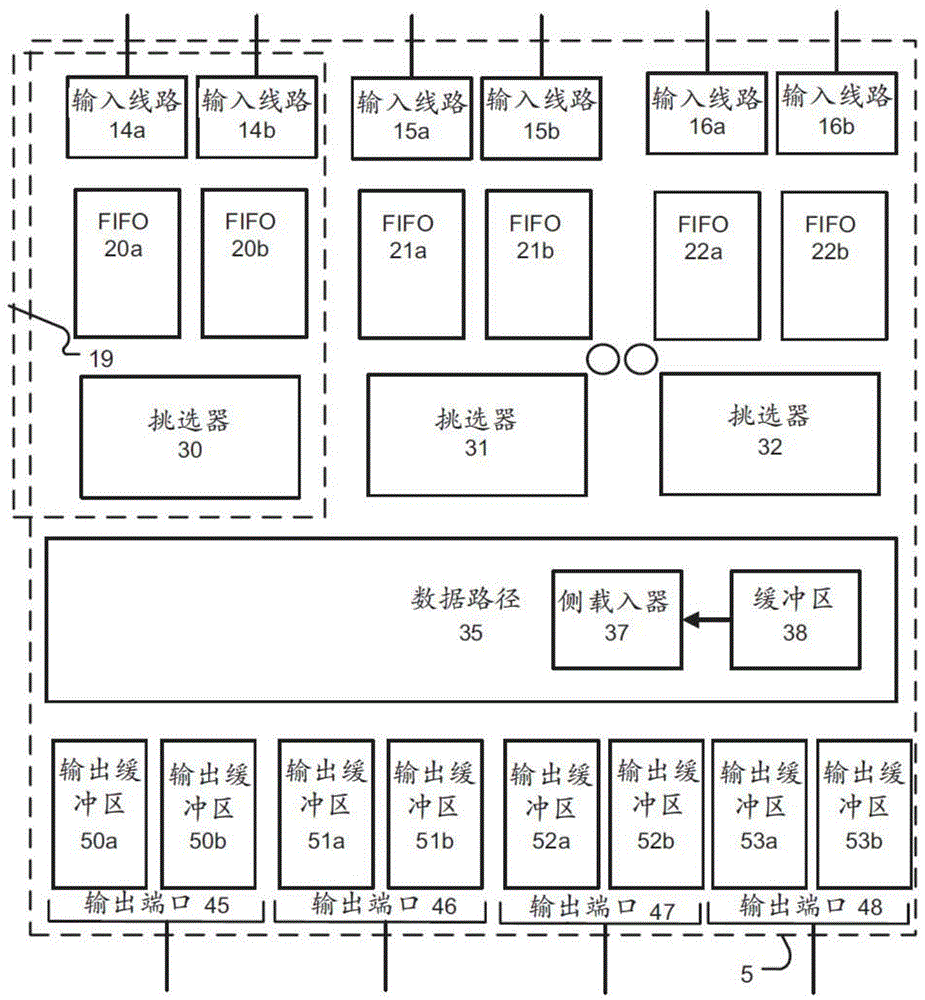

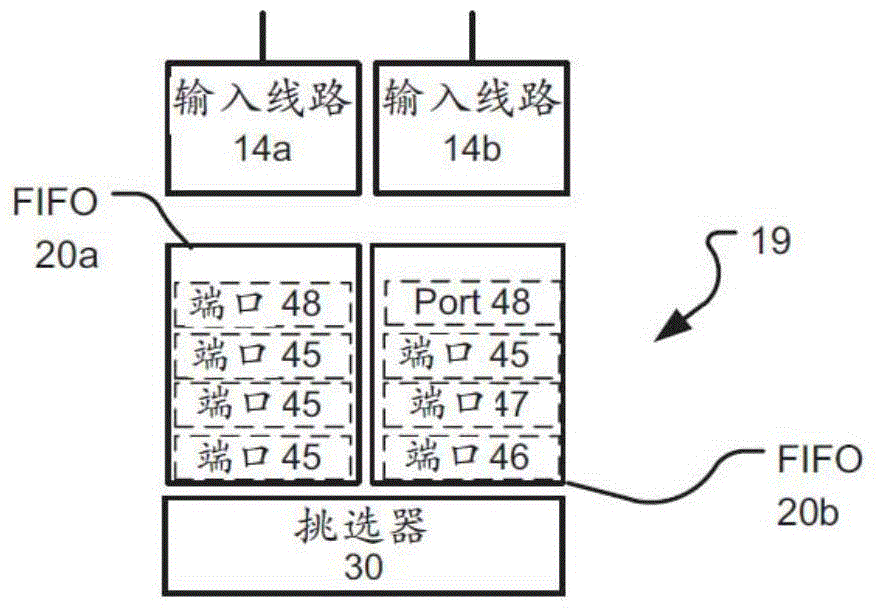

System And Method of Arbitrating Access to Interconnect

ActiveCN104052686AData switching networksElectric digital data processingRe-order bufferReal-time computing

Owner:IMAGINATION TECH LTD

Scan line to block re-ordering buffer for image compression

ActiveUS7496235B2Character and pattern recognitionDigital video signal modificationScan lineImage compression

Owner:MICRON TECH INC

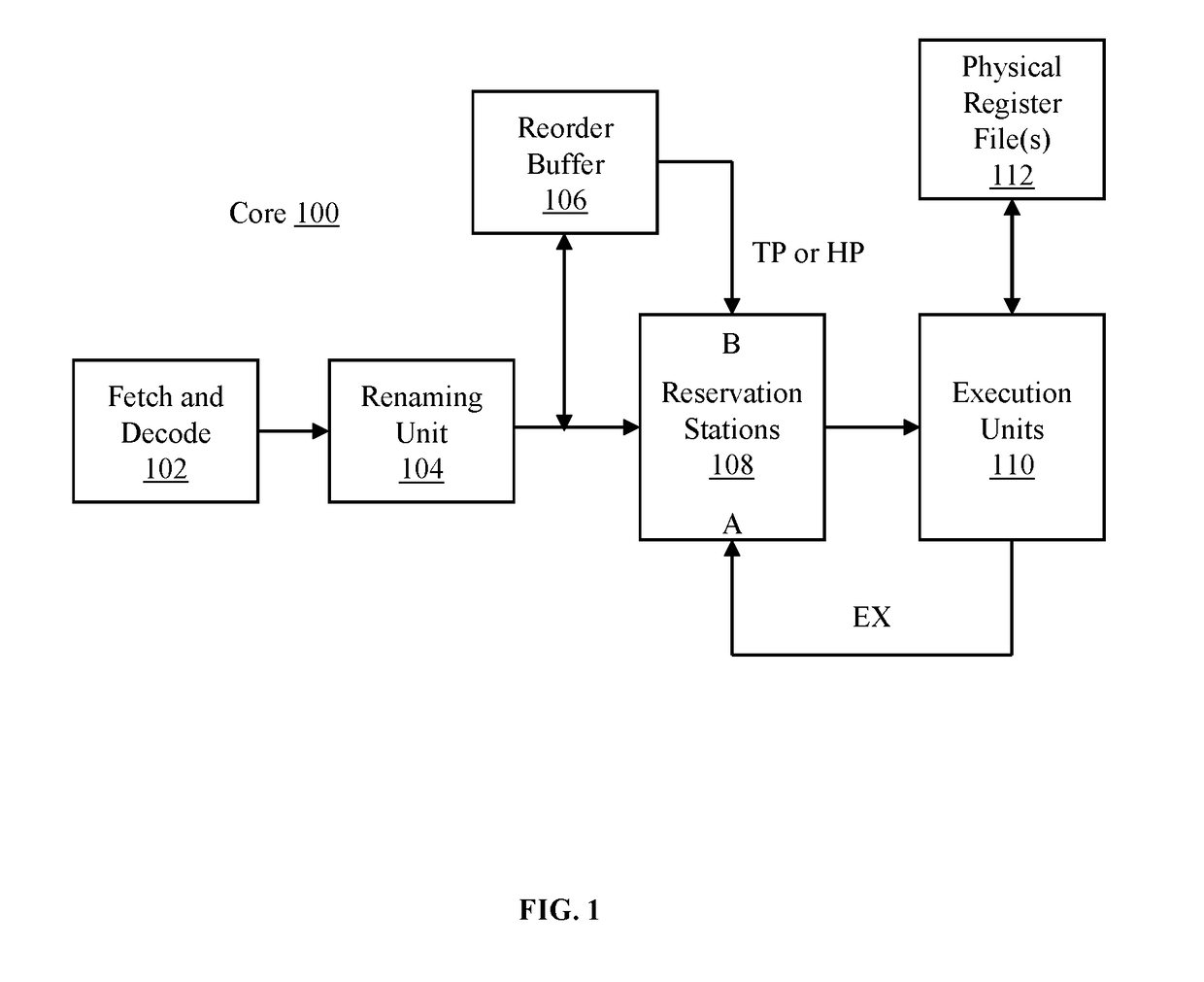

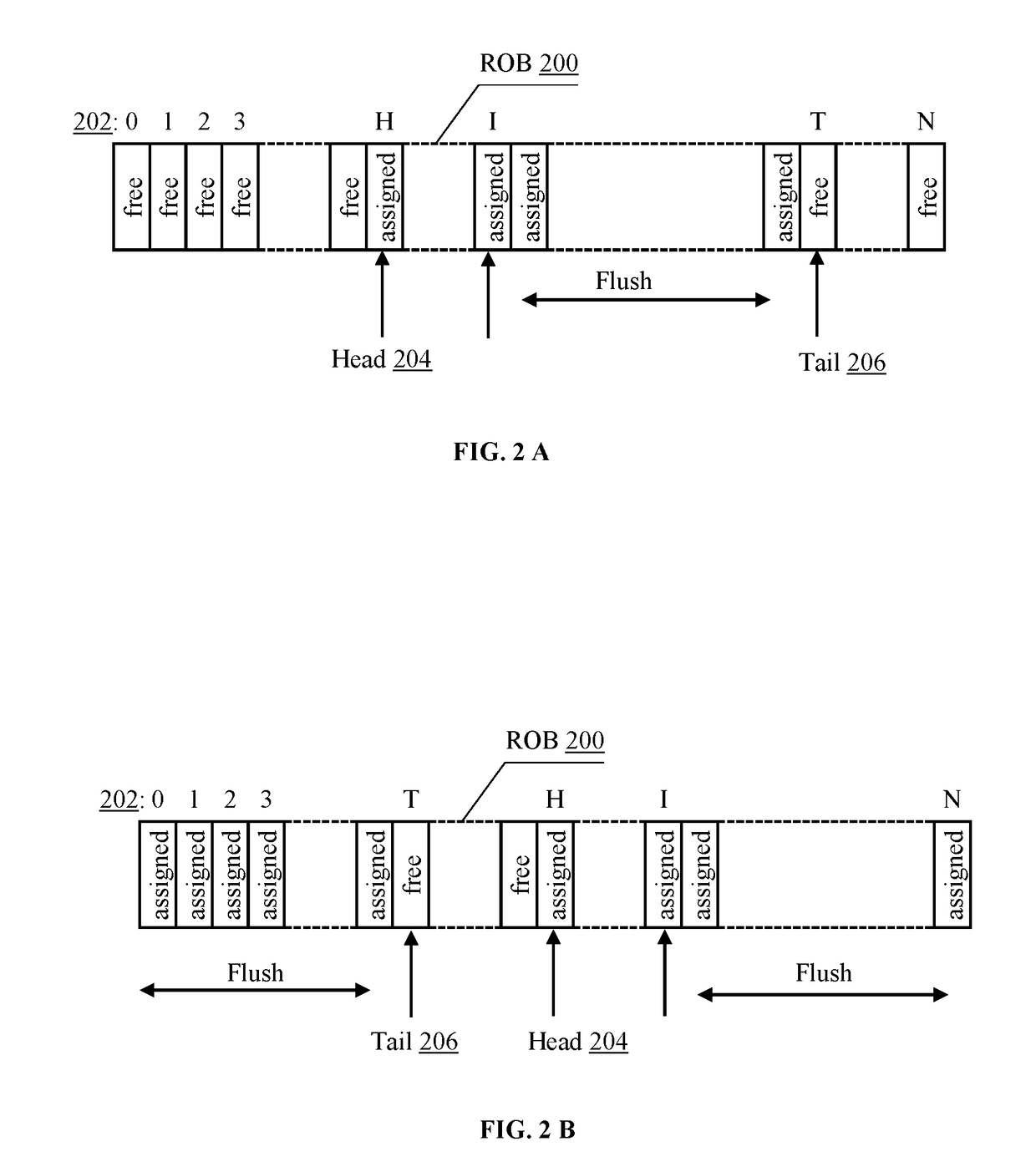

Method and apparatus for flushing instructions from reservation stations

A processor may include a reorder buffer, reservation stations, and execution units. The reorder buffer may be a circular buffer with a head pointer and a tail pointer, configured to assign indexes to instructions. Reservation stations may be configured to host instructions with the assigned indexes, while waiting to be issued to the execution units. Responsive to exception event, reservation stations may be configured to flush instructions that are younger, in program order, than the instruction executed with exception. Execution units may provide the reorder buffer index EX of the instruction executed with exception. The reorder buffer may provide the reorder buffer index TP stored in the tail pointer. Reservation stations may be configured to flush instructions with assigned indexes in the wrapped-around increasing interval from the index EX to the index TP.

Owner:SPASOV DEJAN

Reducing power consumption in a multi-slice computer processor

Reducing power consumption in a multi-slice computer processor that includes a re-order buffer and an architected register file, including: designating an entry in the re-order buffer as being invalid and unwritten; assigning a pending instruction to the entry in the re-order buffer; responsive to assigning the pending instruction to the entry in the re-order buffer, designating the entry as being valid; writing data generated by executing the pending instruction into the re-order buffer; and responsive to writing data generated by executing the pending instruction into the re-order buffer, designating the entry as being written.

Owner:INT BUSINESS MASCH CORP

Method and apparatus for restoring register renaming mapping

A technique for restoring a register renaming map is described. In one example, a restore table with multiple storage locations holds a copy of the register renaming map whenever a flow risk instruction is passed to the reorder buffer. When all storage locations are full, further instructions are still passed to the reorder buffer, but no copy of the mapping is kept. A storage location then becomes available when the process risk instruction associated with that storage location is executed. A state of a register rename map for unrecorded flow-risk instructions passed to the reorder buffer when the plurality of memory locations are full is generated and stored in the available locations. The state of the register renaming map is generated using a restore table entry for a previous flow-risk instruction and a reorder buffer value for an intermediate instruction between the previous flow-risk instruction and the Between the above undocumented process risk instructions. The restore table can be used to restore the mapping if an unexpected change occurs in the instruction flow.

Owner:MIPS TECH INC