PROCESS FOR AUTOMATIC DYNAMIC RELOADING OF DATA FLOW PROCESSORS (DFPs) AND UNITS WITH TWO- OR THREE-DIMENSIONAL PROGRAMMABLE CELL ARCHITECTURES (FPGAs, DPGAs AND THE LIKE)

a data flow processor and automatic dynamic reloading technology, applied in the direction of electric digital data processing, instruments, logic circuits, etc., can solve the problems of inability to reconfigure the whole unit during operation, inability to further process data, and inability to achieve data processing. the effect of re-configuration of the programmable unit considerably more rapidly and rapid availability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

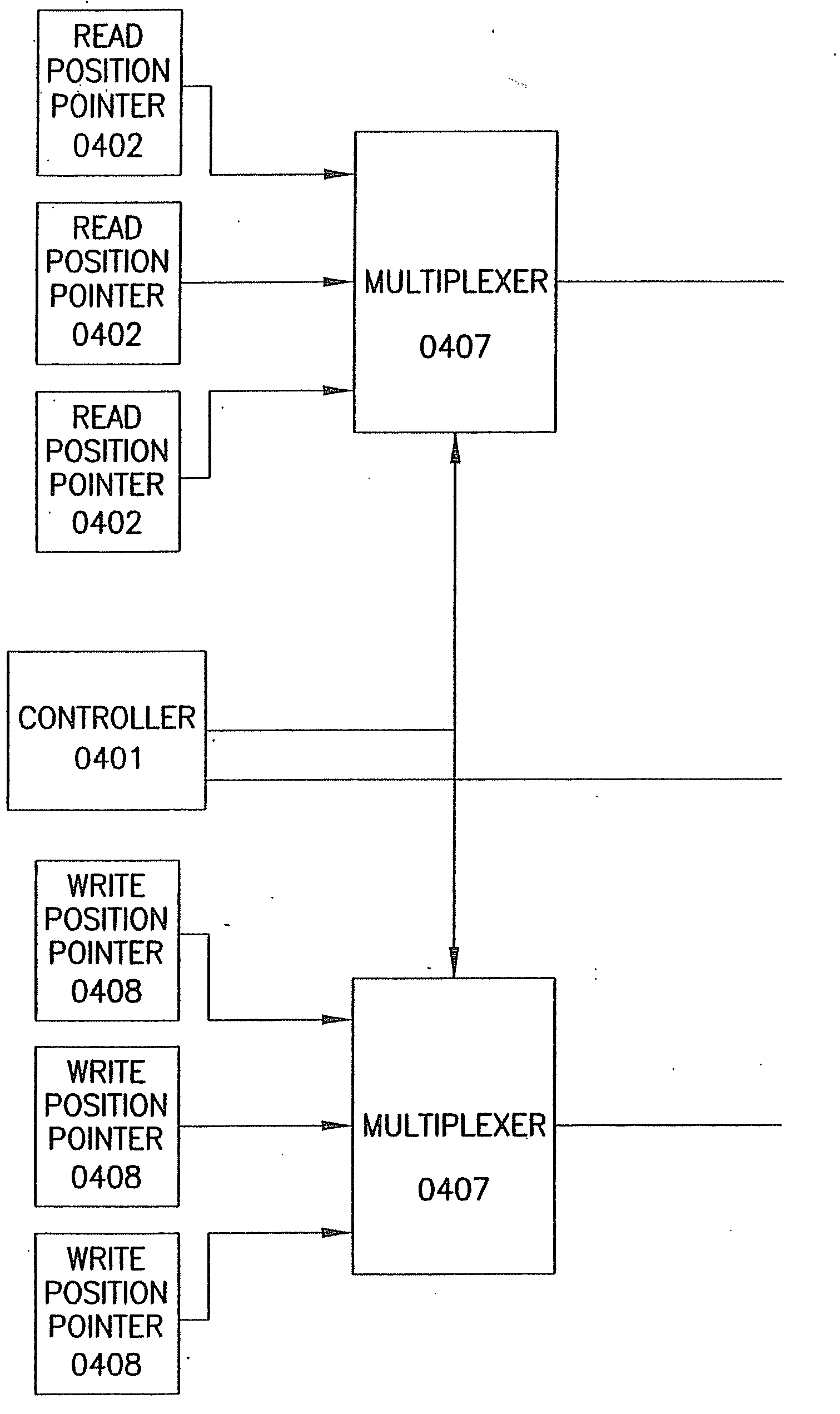

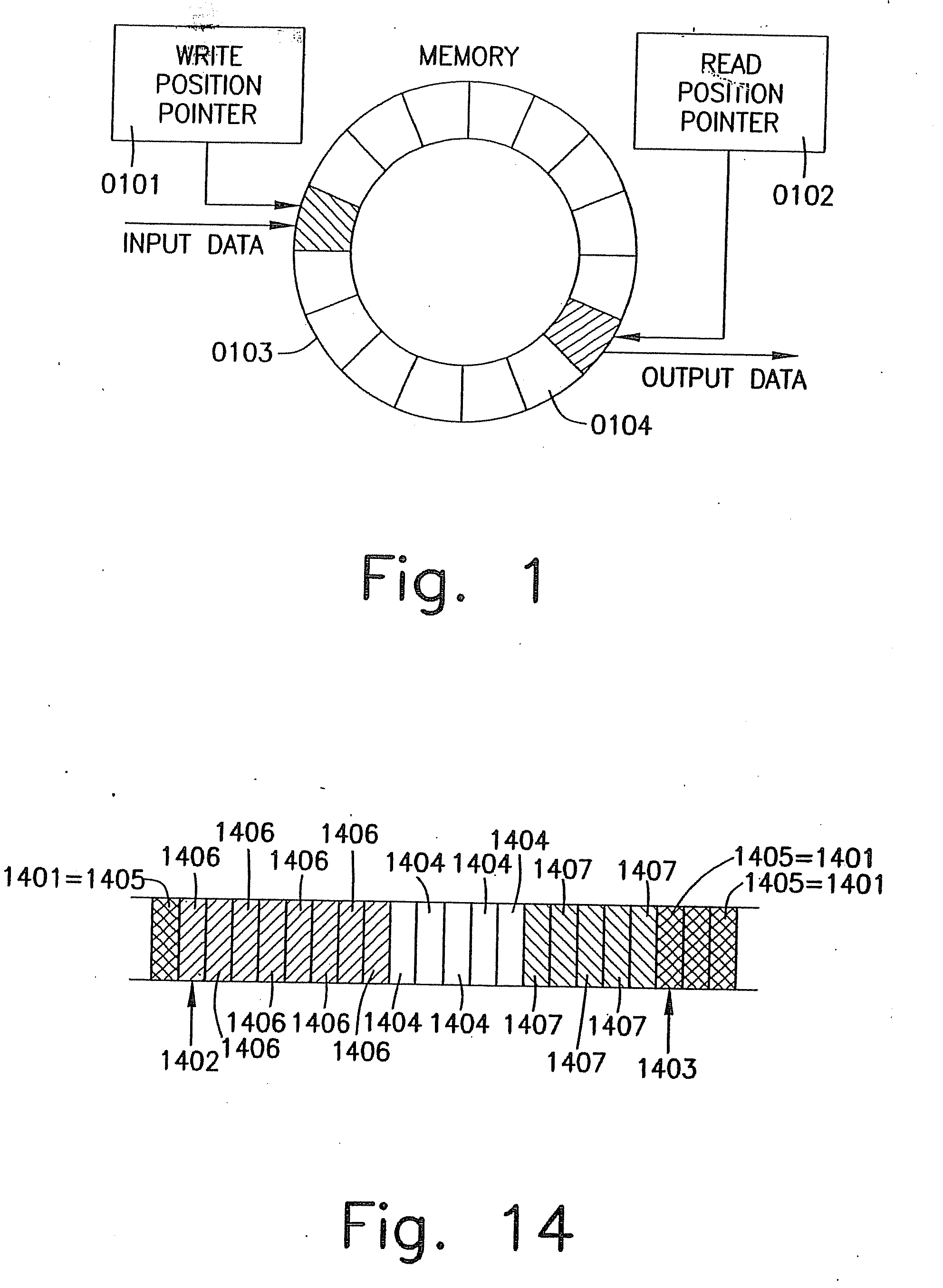

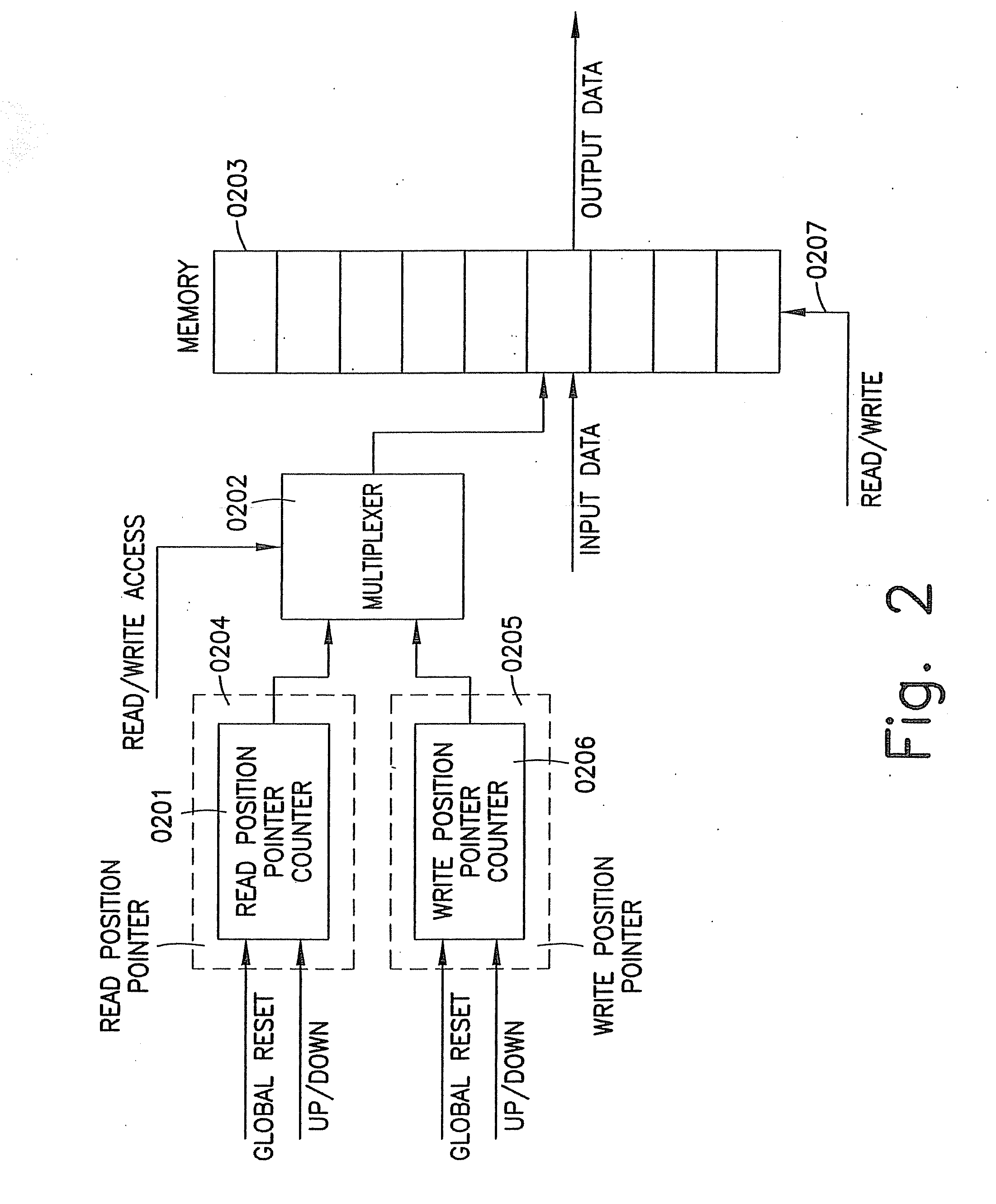

[0038]There is a plurality of ring memories in a programmable unit or connected externally to said unit. The one or more ring memories have one or more controllers controlling the one or more ring memories. These controllers are part of the PLU named in German Patent Application No. DE 44 16 881 A1. The ring memories contain configuration strings for the configurable elements of one or a plurality of configurable units; the configurable elements can also be expressly used for interconnecting function groups and they can be crossbar circuits or multiplexers for interconnecting bus architectures, which are conventional.

[0039]Ring memories and ring memory controllers can be either directly hardware-implemented or first obtained by configuring one or more configurable cells of a configurable unit (e.g., FPGA).

[0040]Conventional ring memories can be used as ring memories, in particular ring memories and / or controllers with the following properties:[0041]where not all records are used, an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More