Facilitating quiesce operations within a logically partitioned computer system

a computer system and logical partition technology, applied in the direction of multi-programming arrangements, instruments, program control, etc., to achieve the effect of fast conversion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

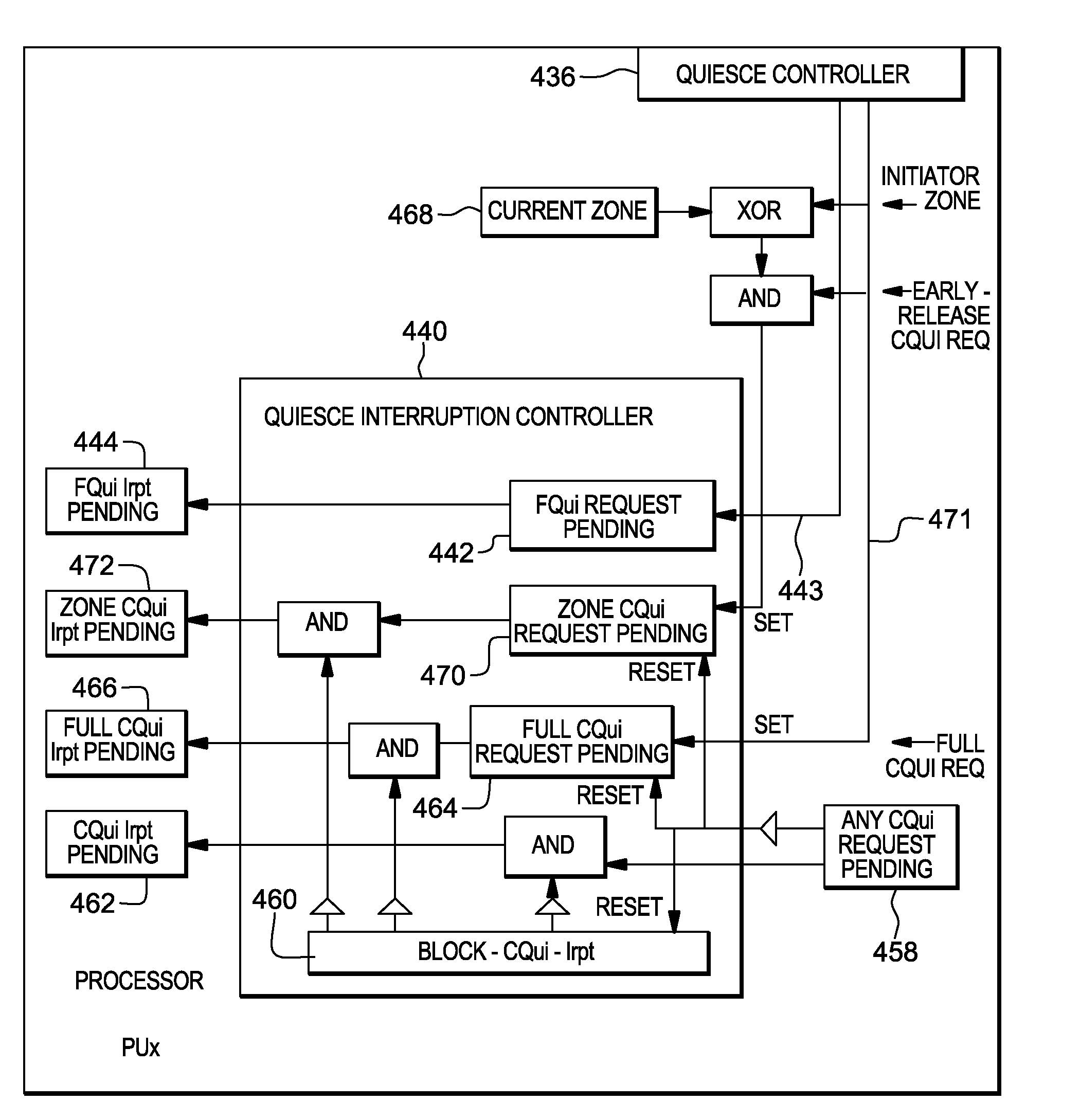

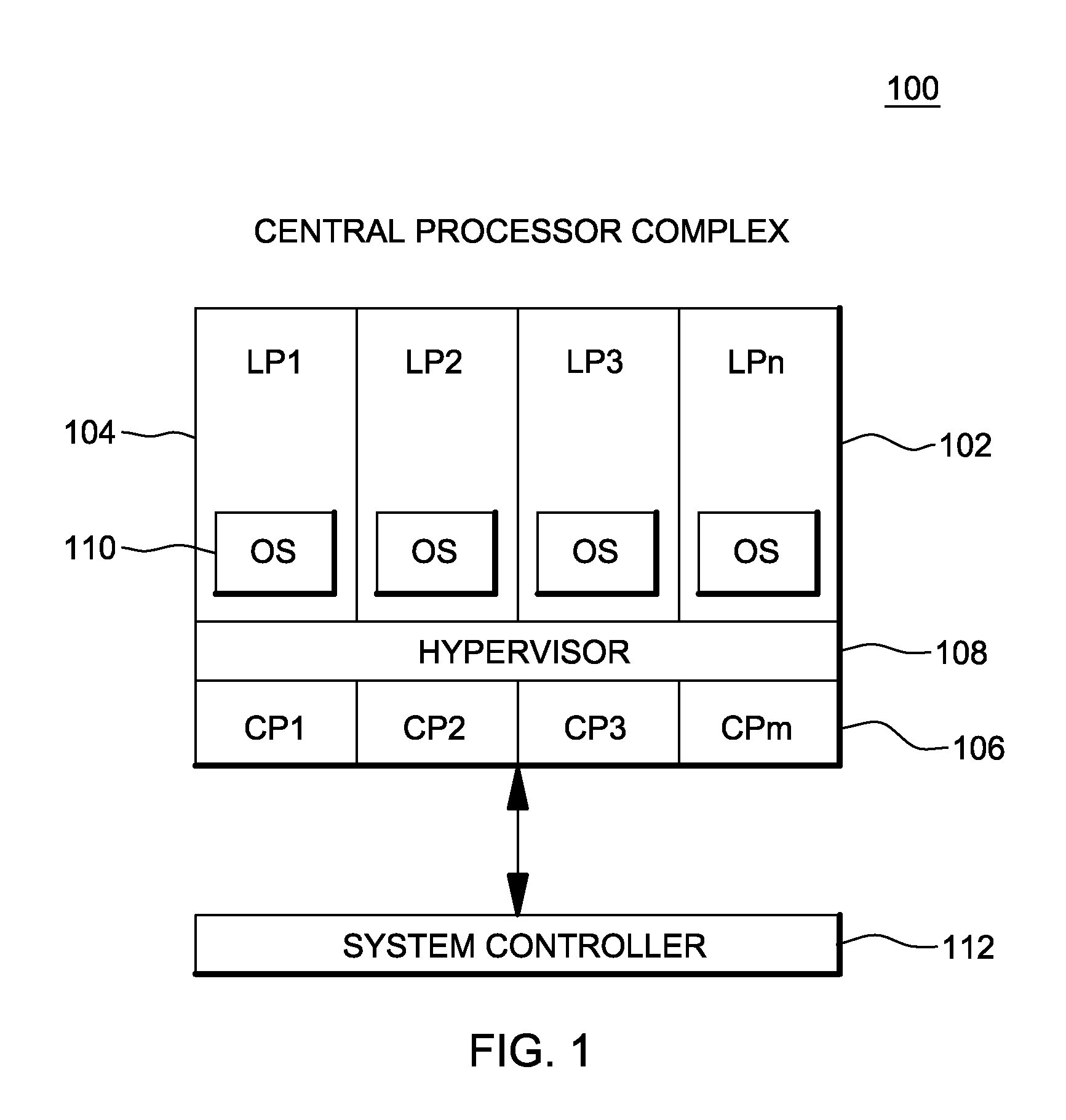

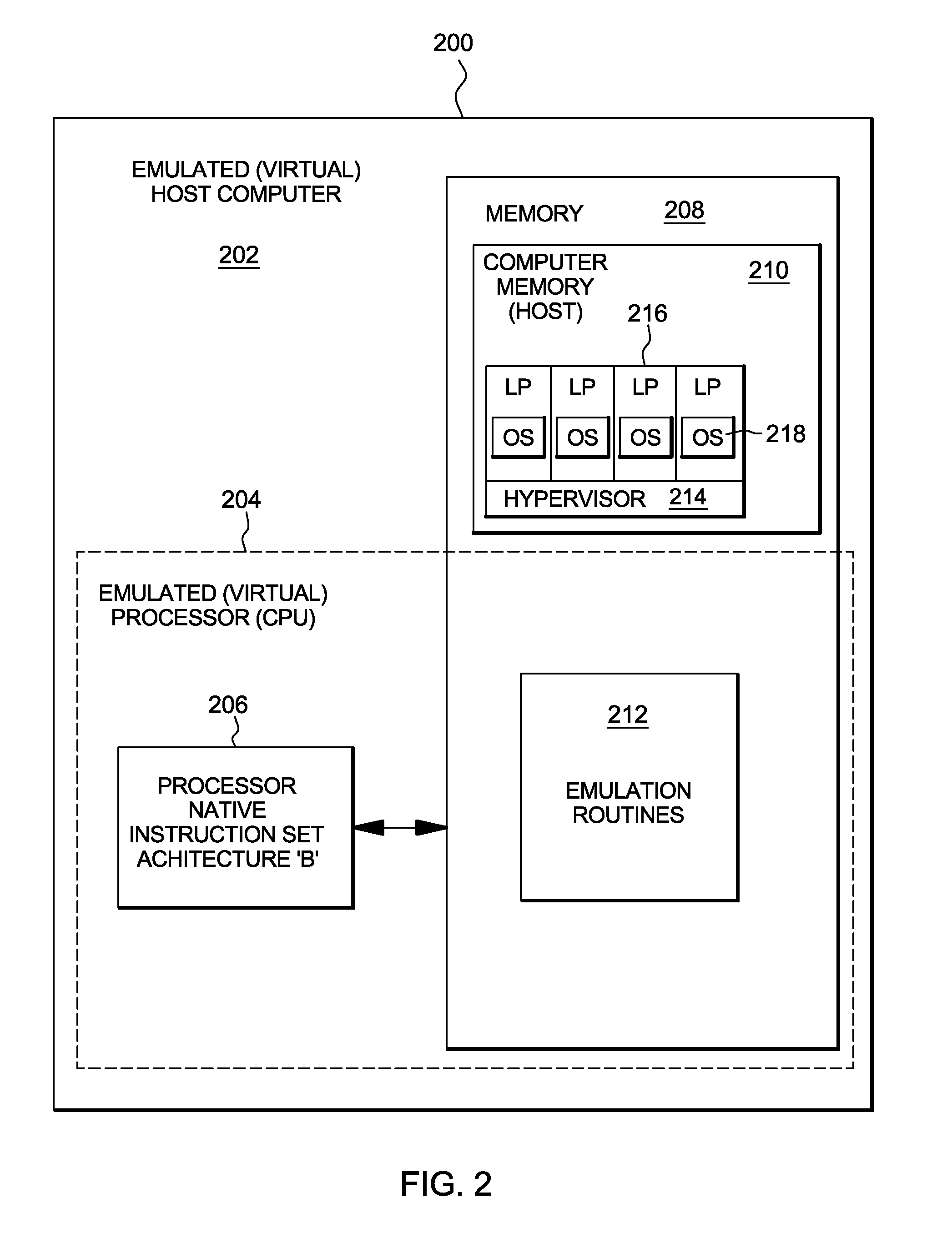

[0027]Conventionally, a quiesce operation forces all appropriate processors in a multiprocessor computer system to suspend most normal processing operations, while the processor initiating the quiesce operation affects a change in the system state. The conventional quiesce operation utilizes system operations to communicate among the processors. Conventionally, a SET conventional quiesce command is issued by an initiating processor to indicate that the processor requests all other processors to enter a “quiesced state”. Having all processors enter a quiesced state ensures that the processors not currently using the common resource to be updated, and that they are not making or using any buffered copies dependent on that resource. After the necessary invalidation and resource updates are complete, a RESET conventional quiesce command is issued by the processor previously issuing the SET conventional quiesce command, and which has now completed the operation for which the quiesced sta...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More