Patents

Literature

54 results about "Compare-and-swap" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer science, compare-and-swap (CAS) is an atomic instruction used in multithreading to achieve synchronization. It compares the contents of a memory location with a given value and, only if they are the same, modifies the contents of that memory location to a new given value. This is done as a single atomic operation. The atomicity guarantees that the new value is calculated based on up-to-date information; if the value had been updated by another thread in the meantime, the write would fail. The result of the operation must indicate whether it performed the substitution; this can be done either with a simple boolean response (this variant is often called compare-and-set), or by returning the value read from the memory location (not the value written to it).

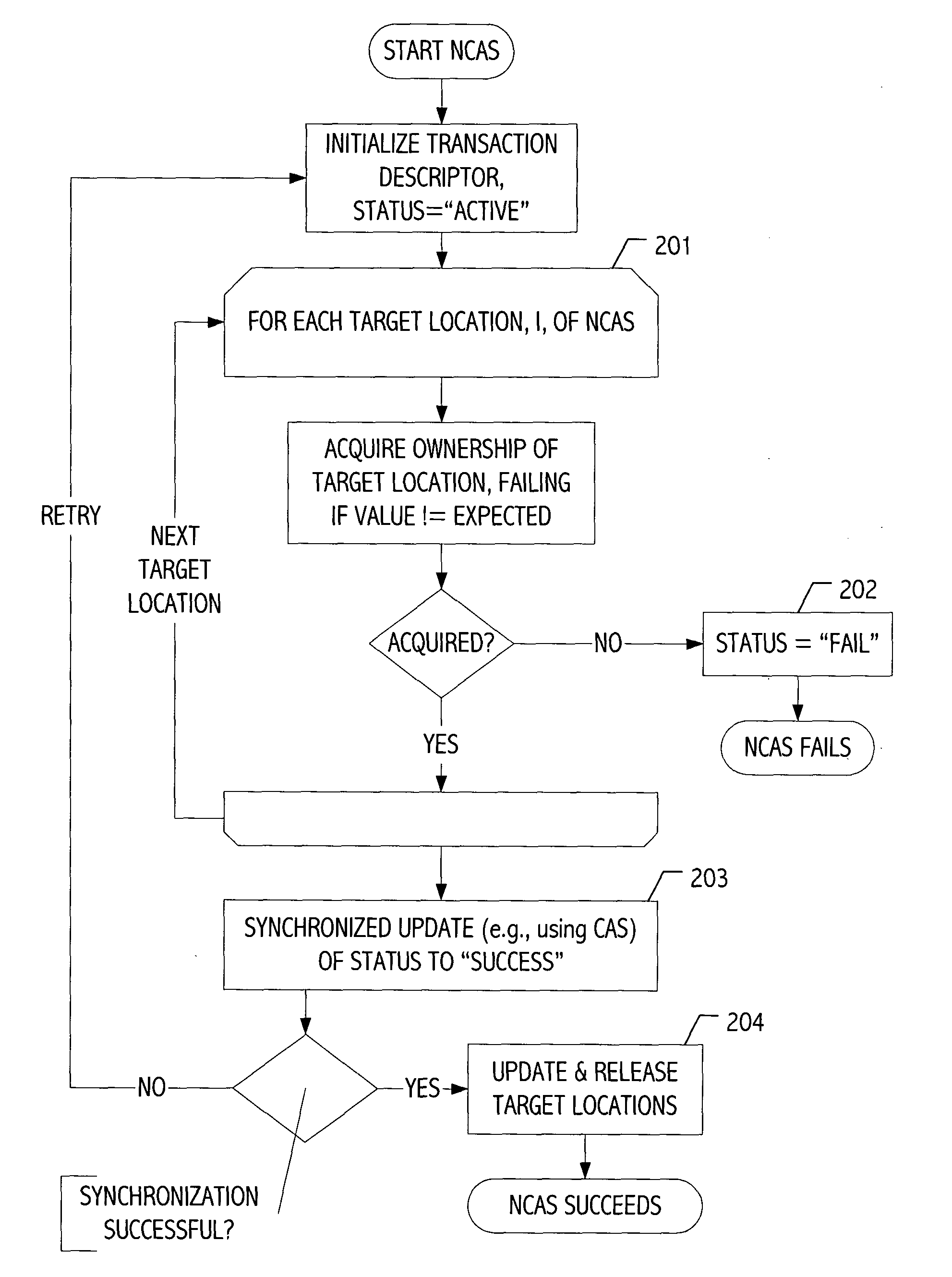

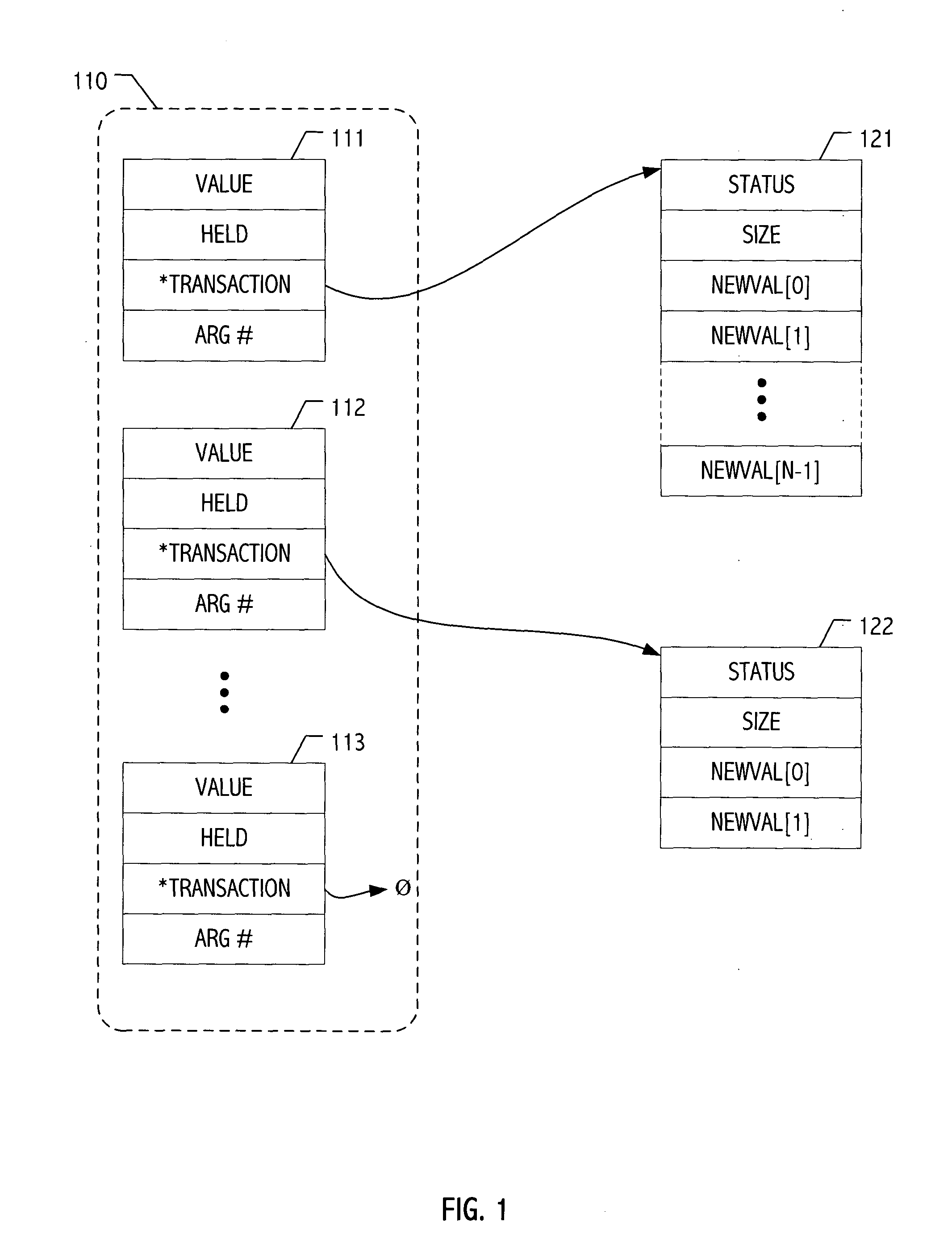

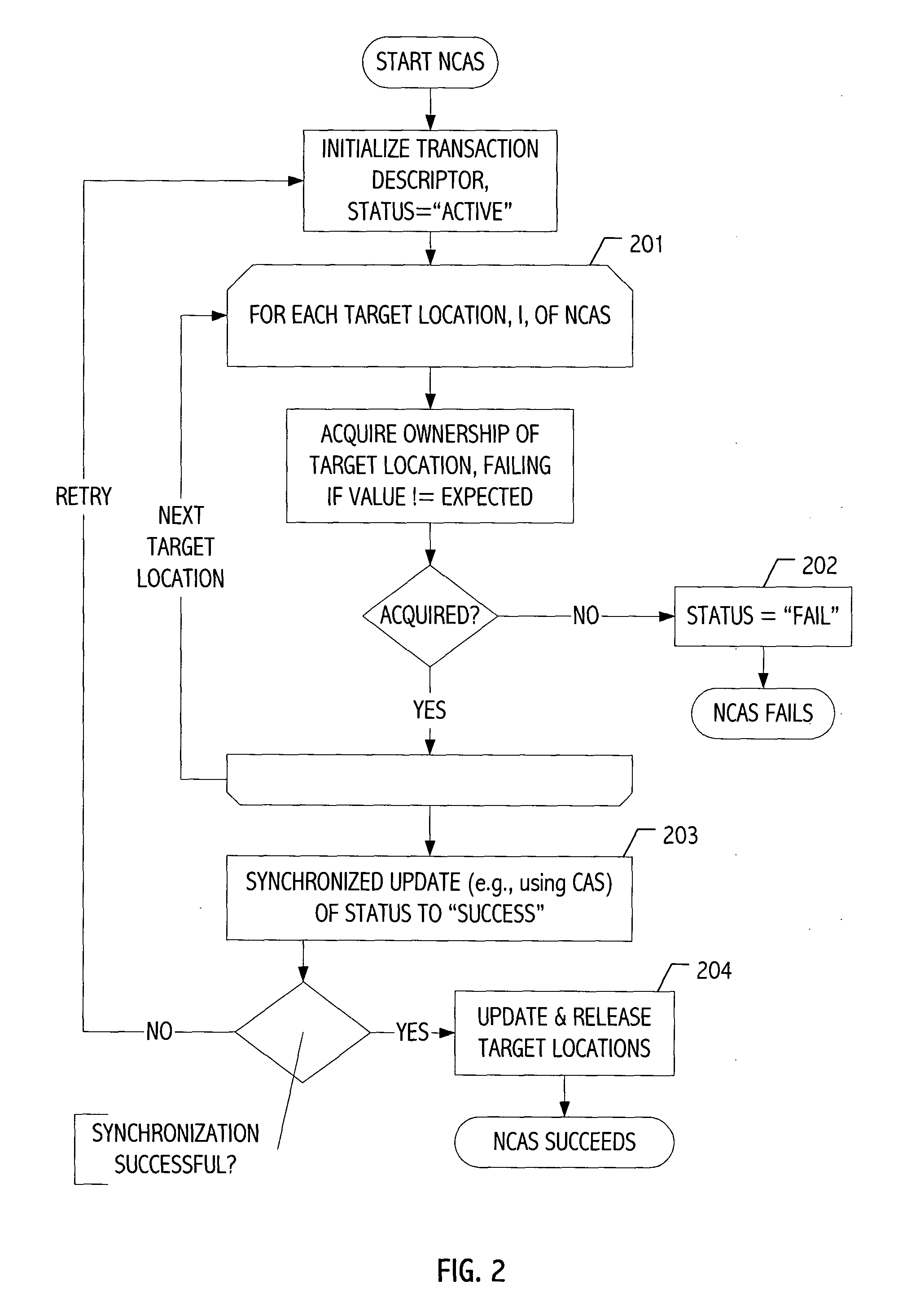

Obstruction-free mechanism for atomic update of multiple non-contiguous locations in shared memory

ActiveUS20040034673A1Data processing applicationsError preventionTransactional memoryMulti targeting

We present a technique for implementing obstruction-free atomic multi-target transactions that target special "transactionable" locations in shared memory. A programming interface for using operations based on these transactions can be structured in several ways, including as n-word compare-and-swap (NCAS) operations or as atomic sequences of single-word loads and stores (e.g., as transactional memory).

Owner:ORACLE INT CORP

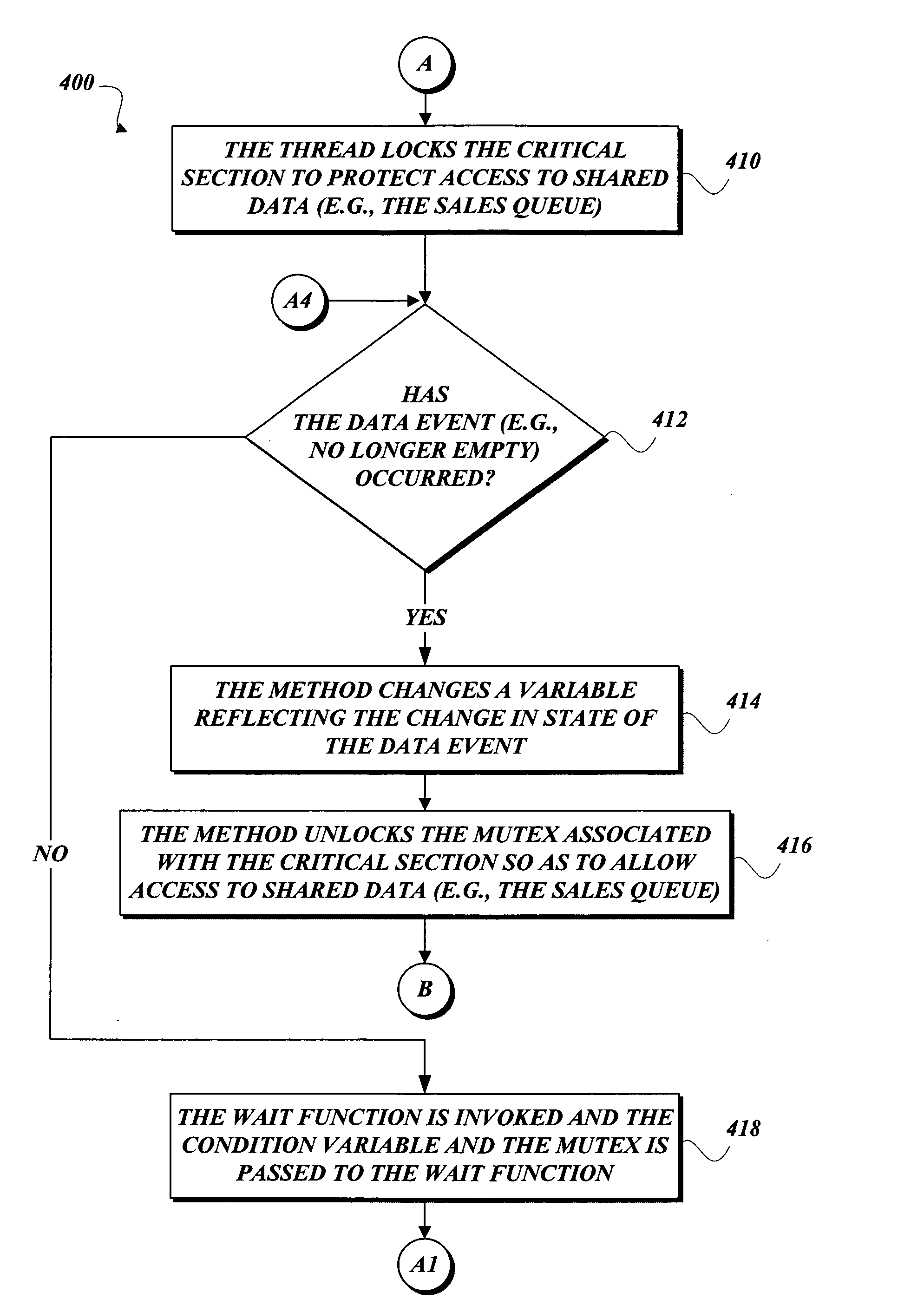

Conditional variables without spinlocks

The use of spinlocks is avoided in the combination of mutex and condition variables by using any suitable atomic compare and swap functionality to add a thread to a list of waiting threads that waits for a data event to occur. Various embodiments of the present invention also provide an organization scheme of data, which describes an access bit, an awaken count, and a pointer to the list of waiting threads. This organization scheme of data helps to optimize the list of waiting threads so as to better awaken a waiting thread or all waiting threads at once.

Owner:MICROSOFT TECH LICENSING LLC

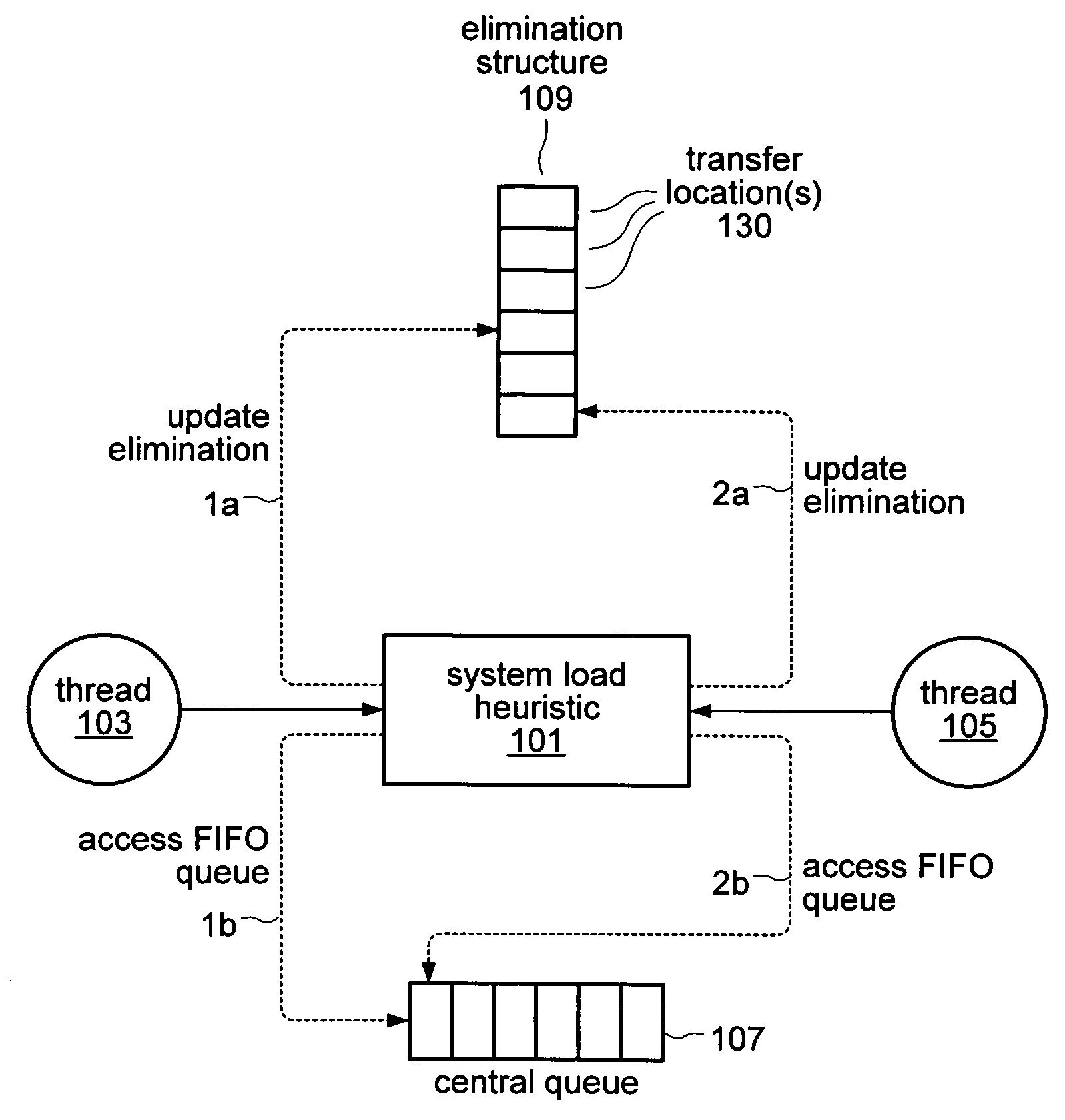

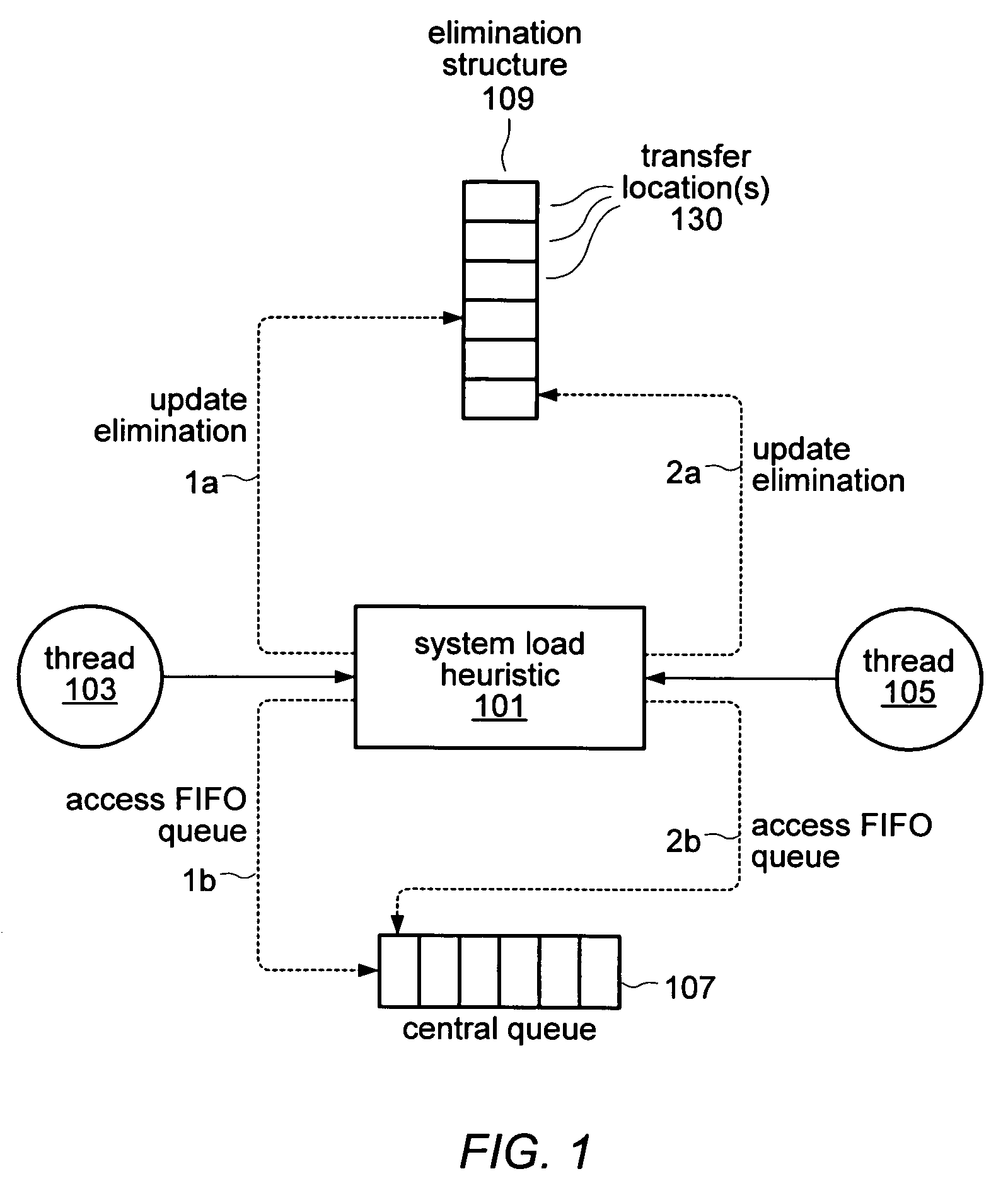

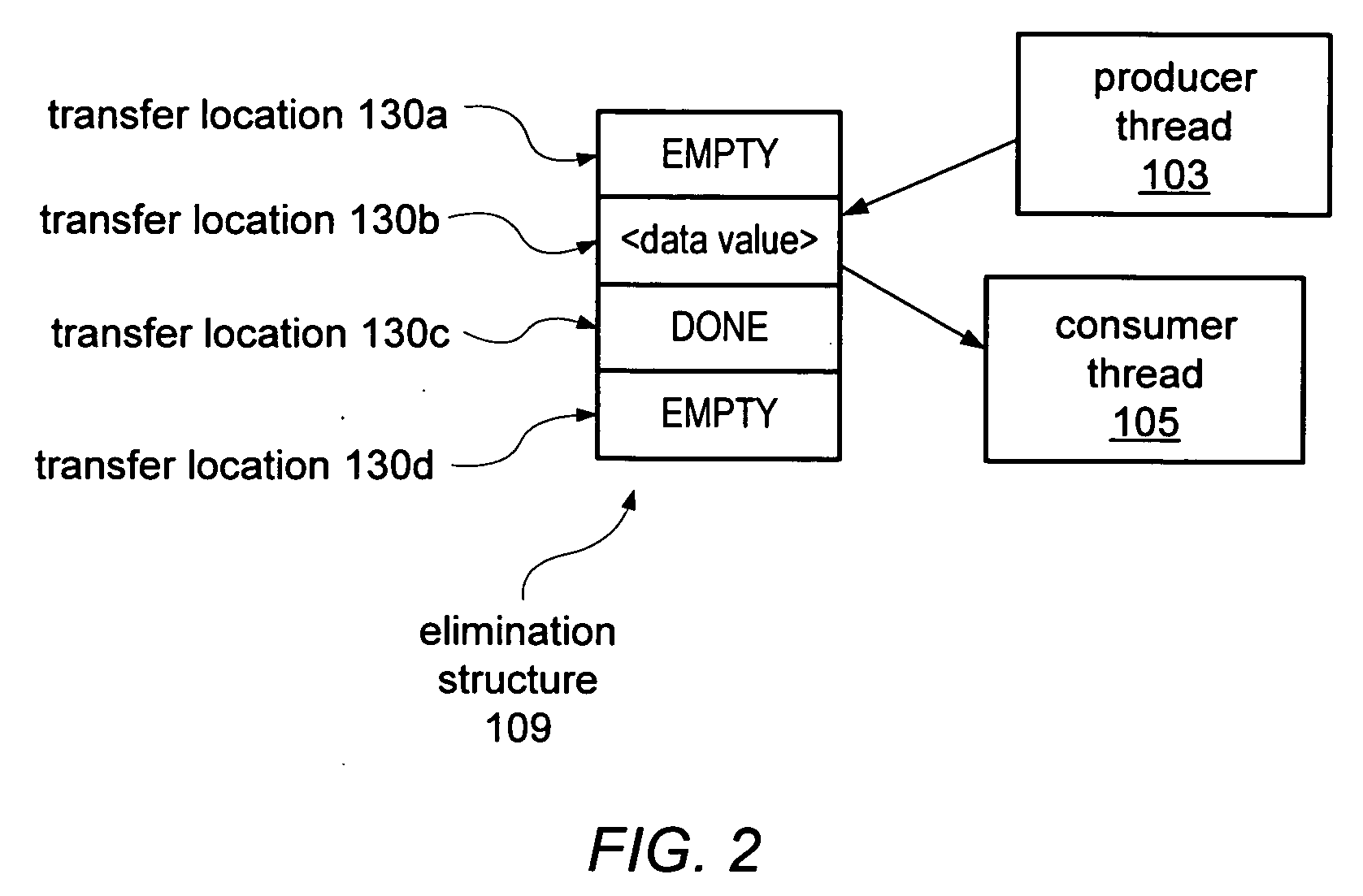

Scalable method for producer and consumer elimination

ActiveUS20060123156A1Avoid bottlenecksLimited scalabilityGeneral purpose stored program computerSpecific program execution arrangementsData storeCompare-and-swap

Producers and consumer processes may synchronize and transfer data using a shared data structure. After locating a potential transfer location that indicates an EMPTY status, a producer may store data to be transferred in the transfer location. A producer may use a compare-and-swap (CAS) operation to store the transfer data to the transfer location. A consumer may subsequently read the transfer data from the transfer location and store, such as by using a CAS operation, a DONE status indicator in the transfer location. The producer may notice the DONE indication and may then set the status location back to EMPTY to indicate that the location is available for future transfers, by the same or a different producer. The producer may also monitor the transfer location and time out if no consumer has picked up the transfer data.

Owner:ORACLE INT CORP

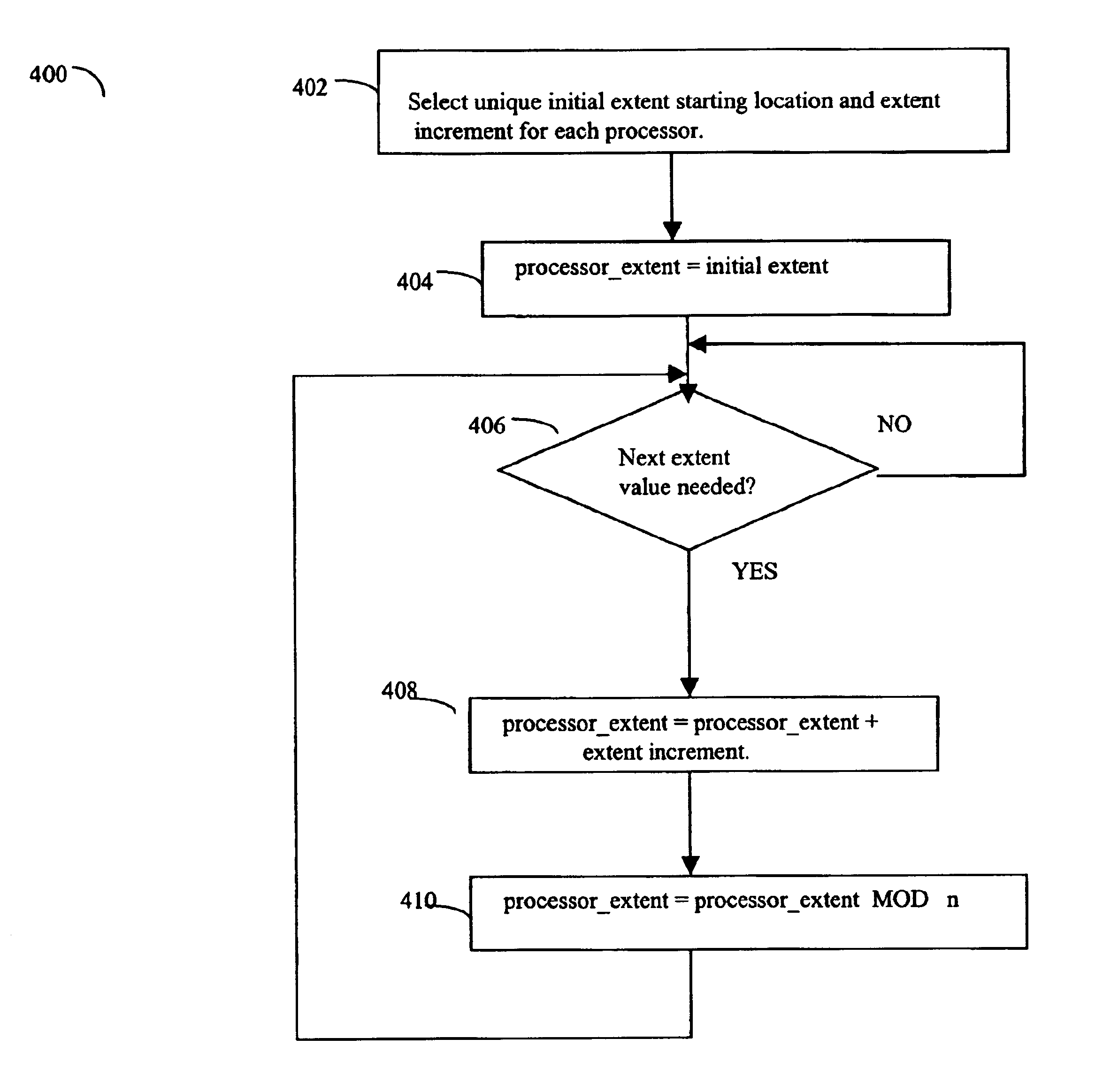

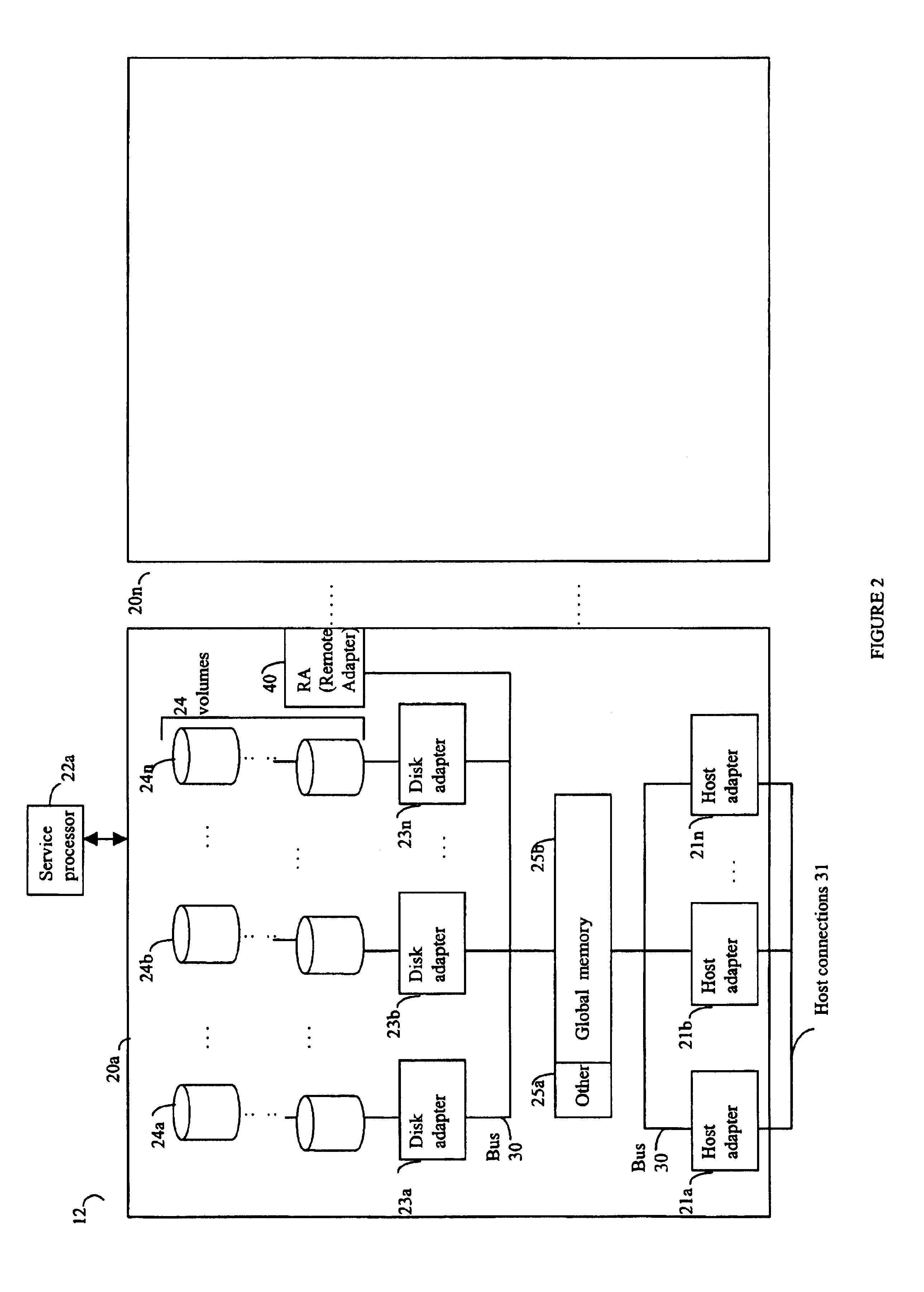

Advancing bank pointer in prime numbers unit

InactiveUS6807619B1Data processing applicationsMemory adressing/allocation/relocationMemory bankParallel computing

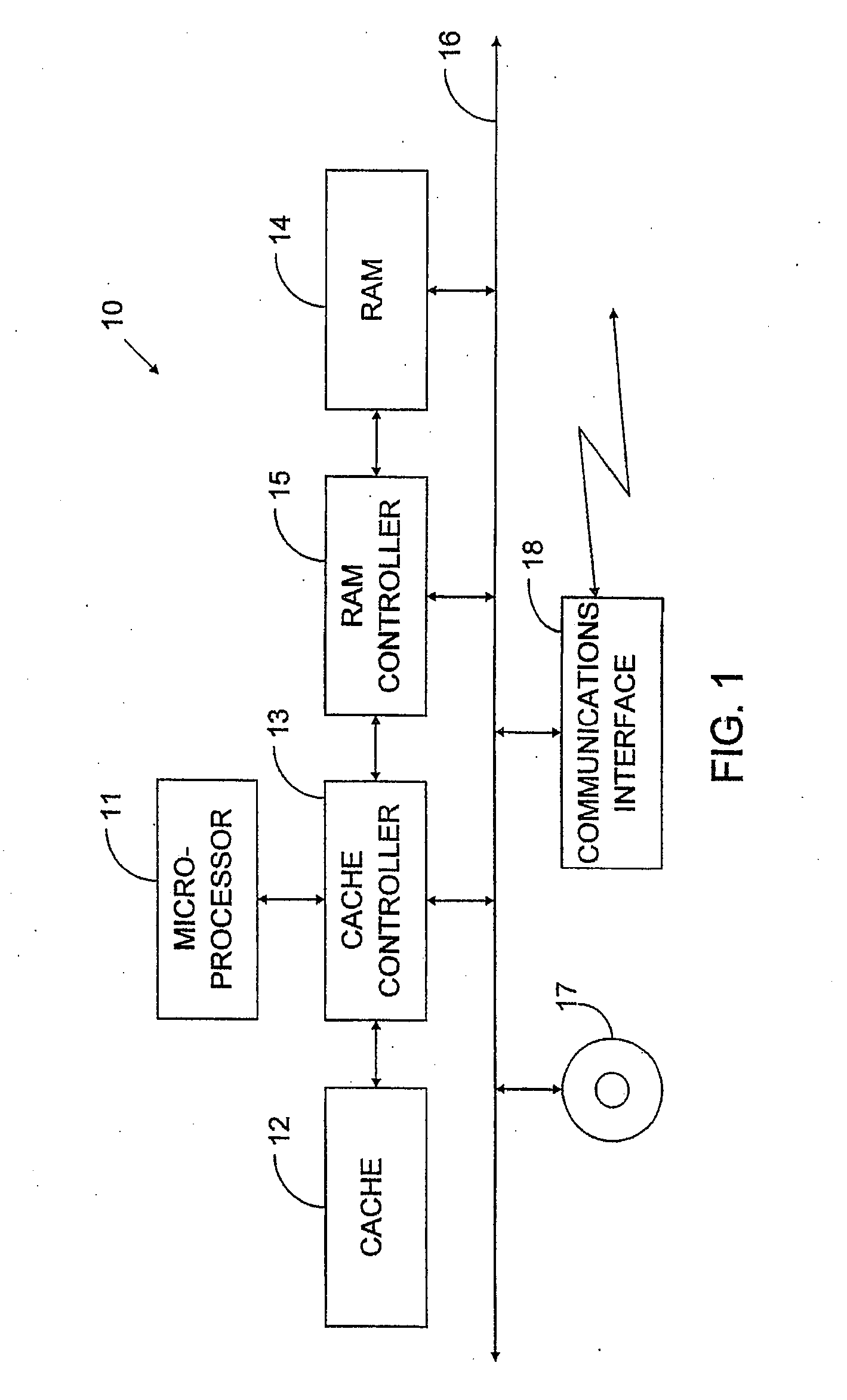

The cache arrangement includes a cache that may be organized as a plurality of memory banks in which each memory bank includes a plurality of slots. Each memory bank has an associated control slot that includes groups of extents of tags. Each cache slot has a corresponding tag that includes a bit value indicating the availability of the associated cache slot, and a time stamp indicating the last time the data in the slot was used. The cache may be shared by multiple processors. Exclusive access of the cache slots is implemented using an atomic compare and swap instruction. The time stamp of slots in the cache may be adjusted to indicate ages of slots affecting the amount of time a particular portion of data remains in the cache. Associated with each processor is a unique extent increment used to determine a next location for that particular processor when attempting to locate an available slot.

Owner:EMC IP HLDG CO LLC

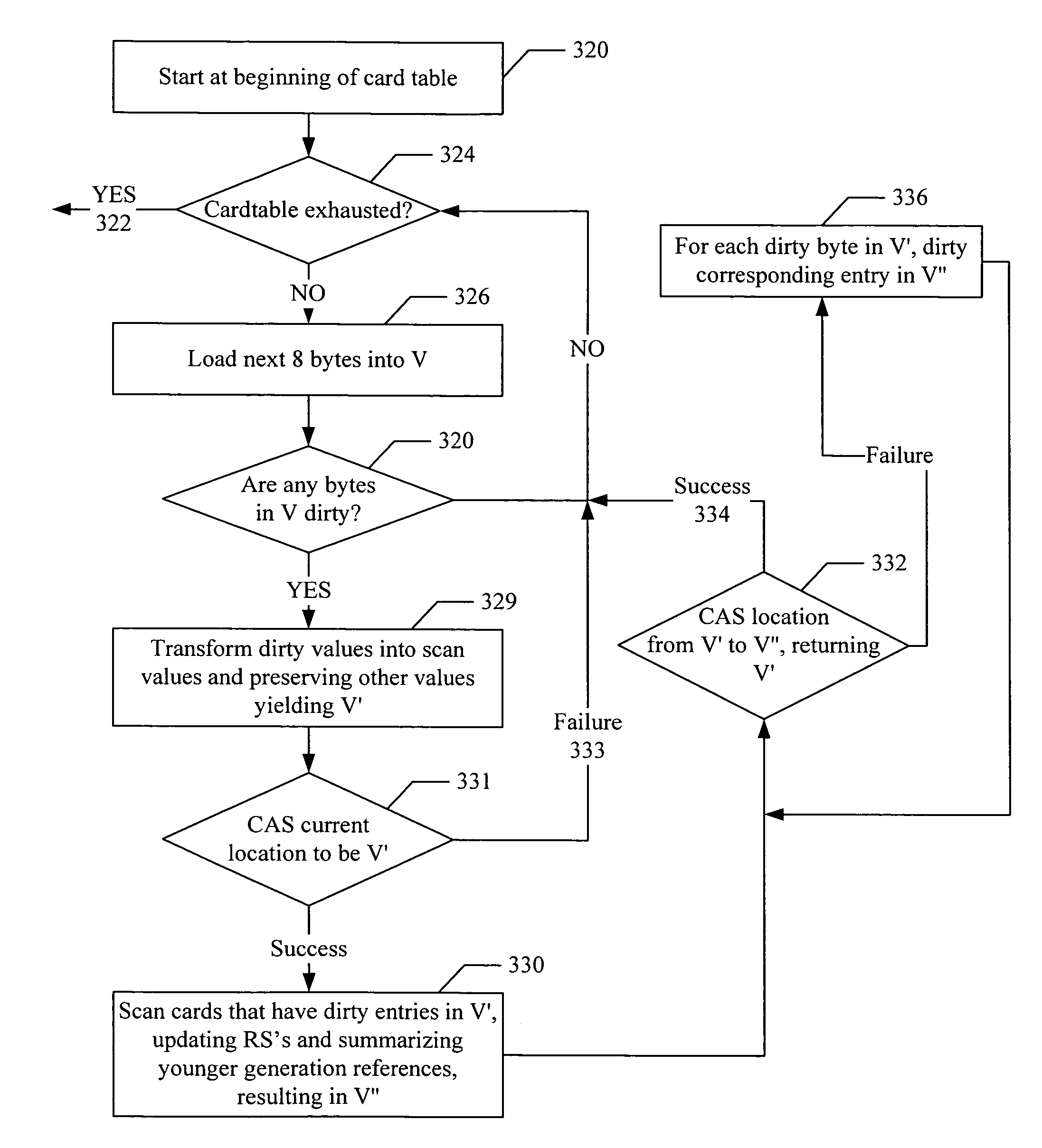

Concurrent incremental garbage collector with a card table summarizing modified reference locations

ActiveUS7412580B1High maintenance costMemory adressing/allocation/relocationWaste collectionMemory cards

A concurrent incremental garbage collector where tracking and summarization of modified references is concurrent with application operations. A card table is arranged with write barriers so that an application's modification of objects in memory cards are memorialized in the card table. The collector performs an atomic operation, e.g., a compare-and-swap (CAS), on the card table to detect modified or written to objects. Card table indicators of dirtied cards are reset or emptied and the corresponding dirtied cards are scanned for the modifications and the remembered sets updated. Another CAS is performed on the same card table and if any dirtied cards are indicated the collector preserves the card table with the dirtied indicators and operates on a distant card table. If the CAS succeeds no modifications were made and the collector operates on the next scheduled card table group.

Owner:ORACLE INT CORP

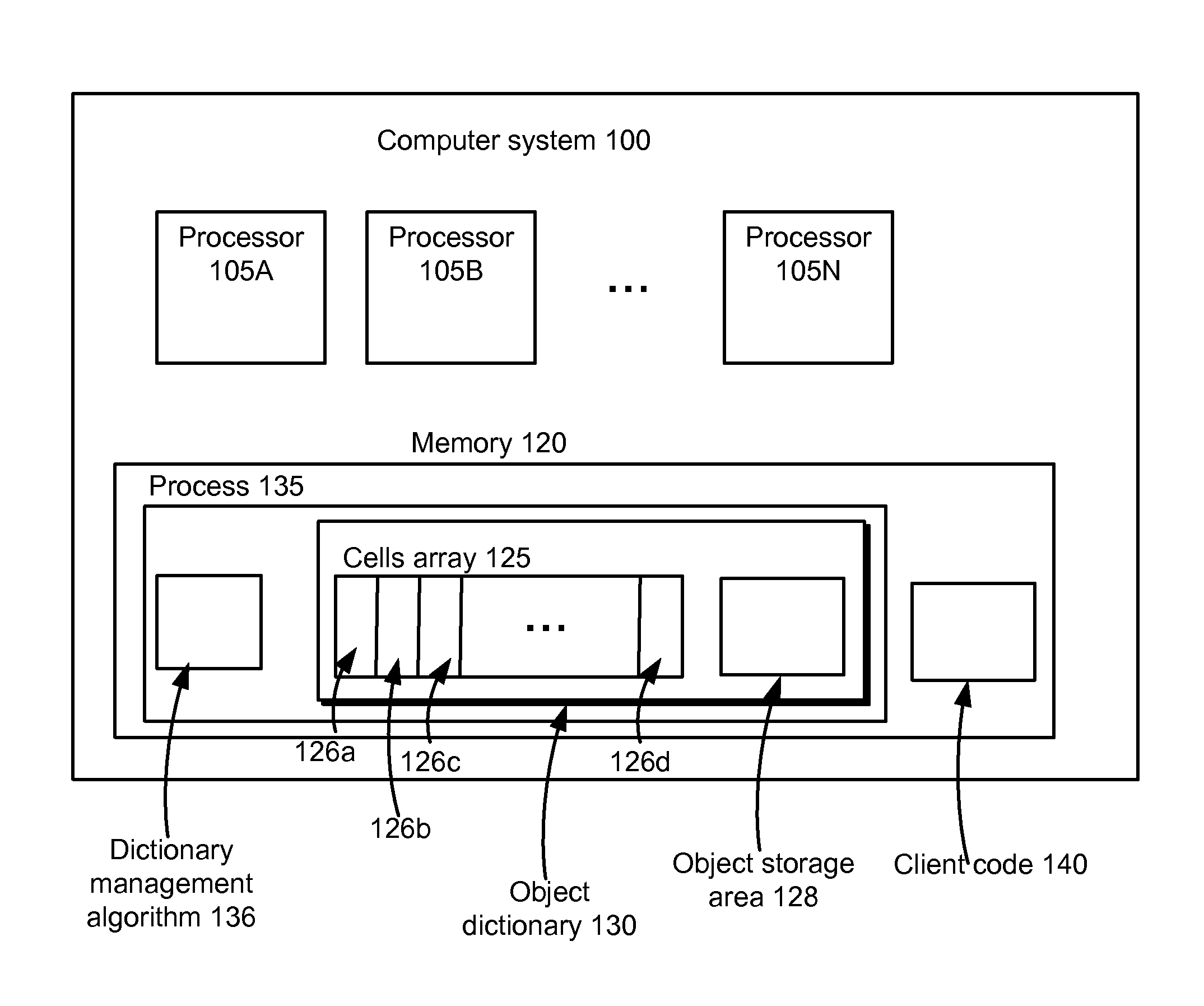

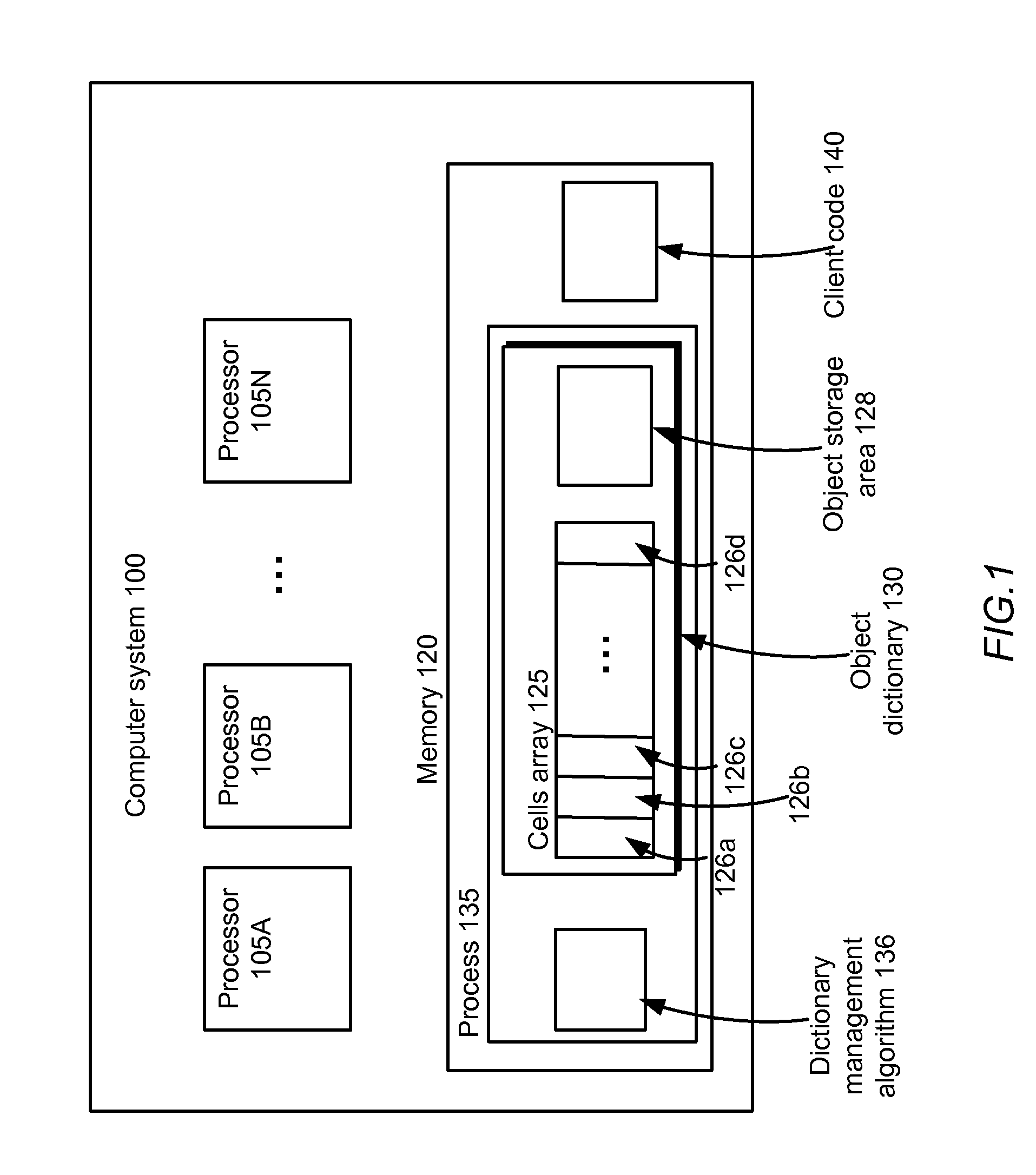

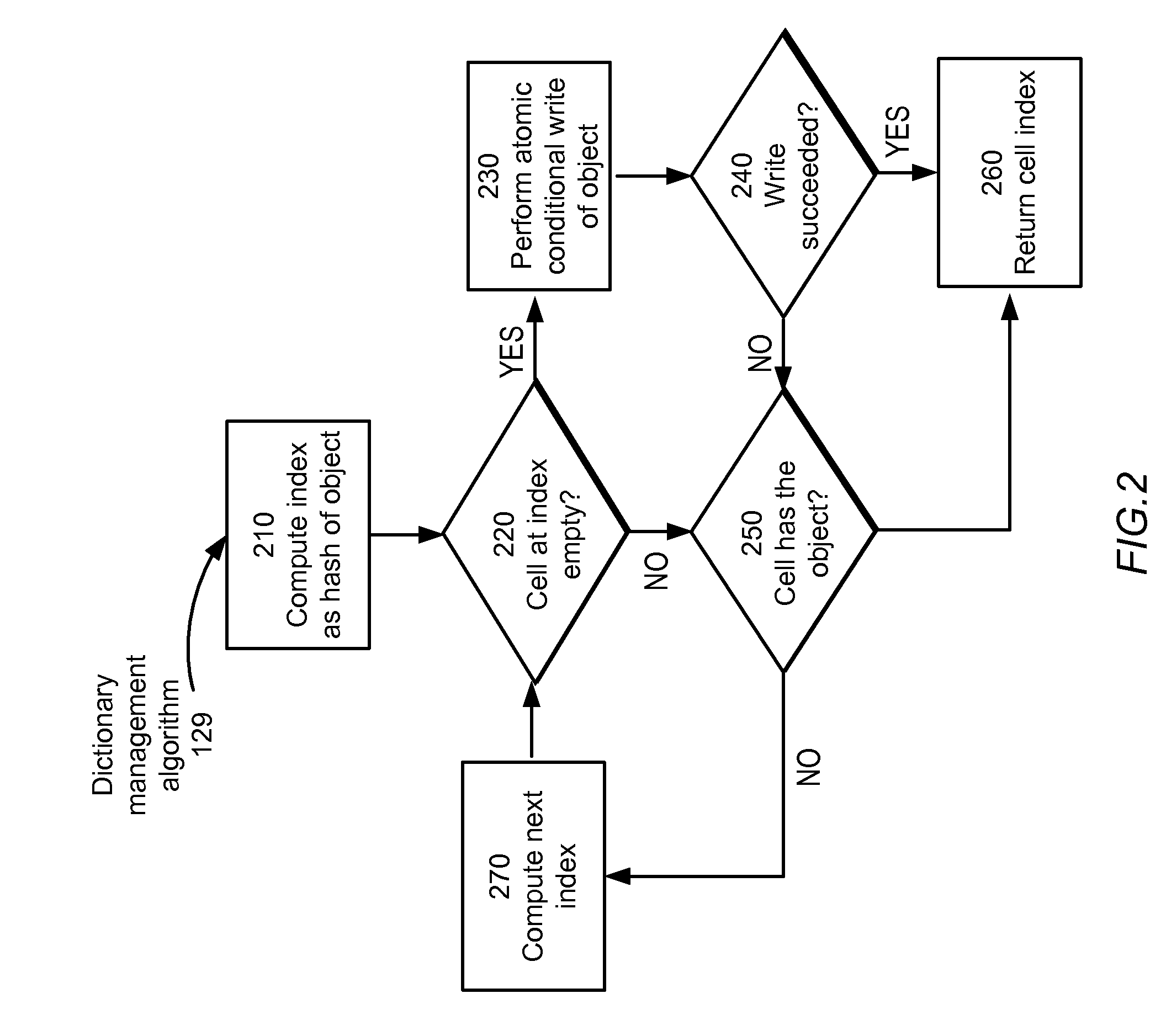

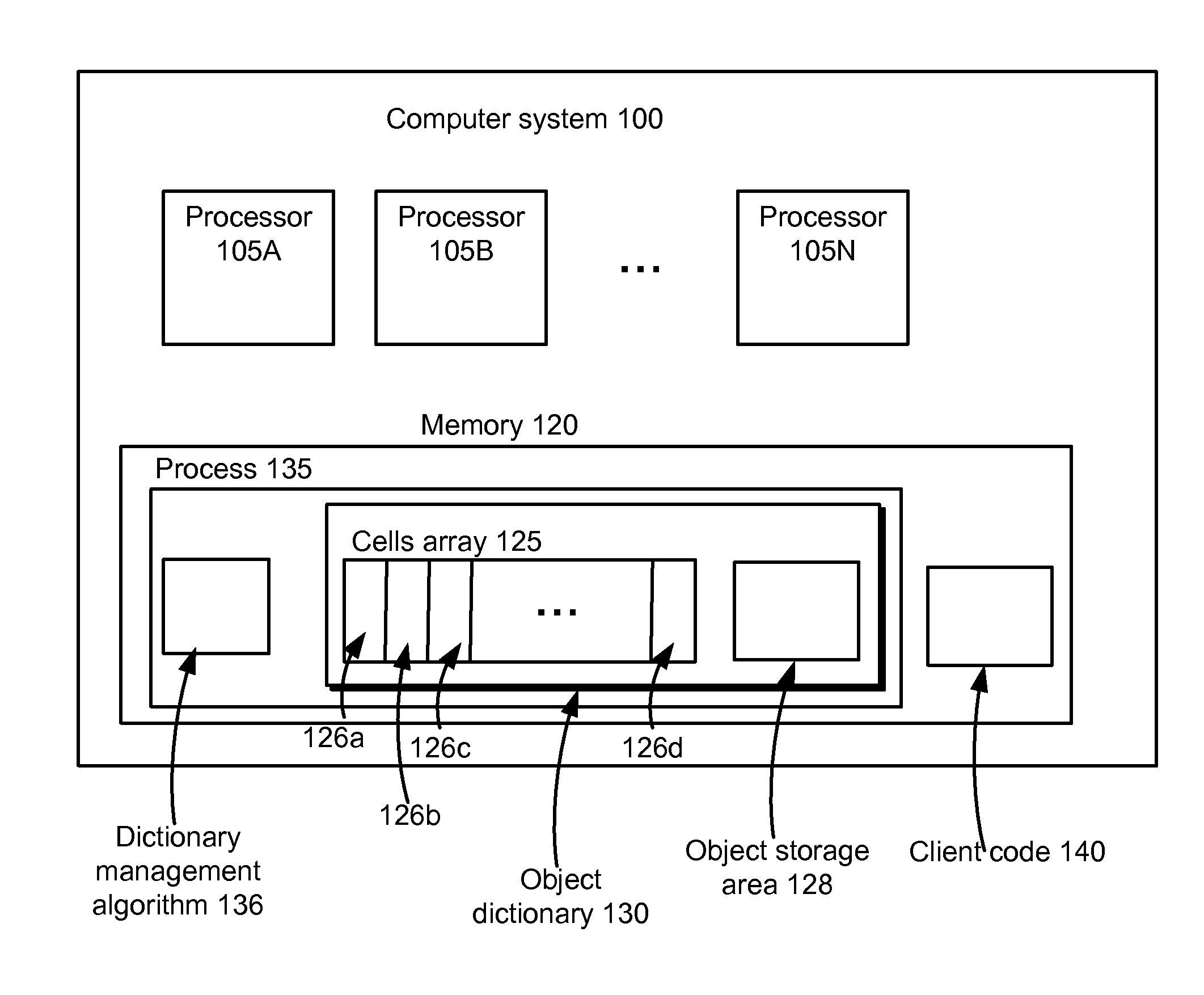

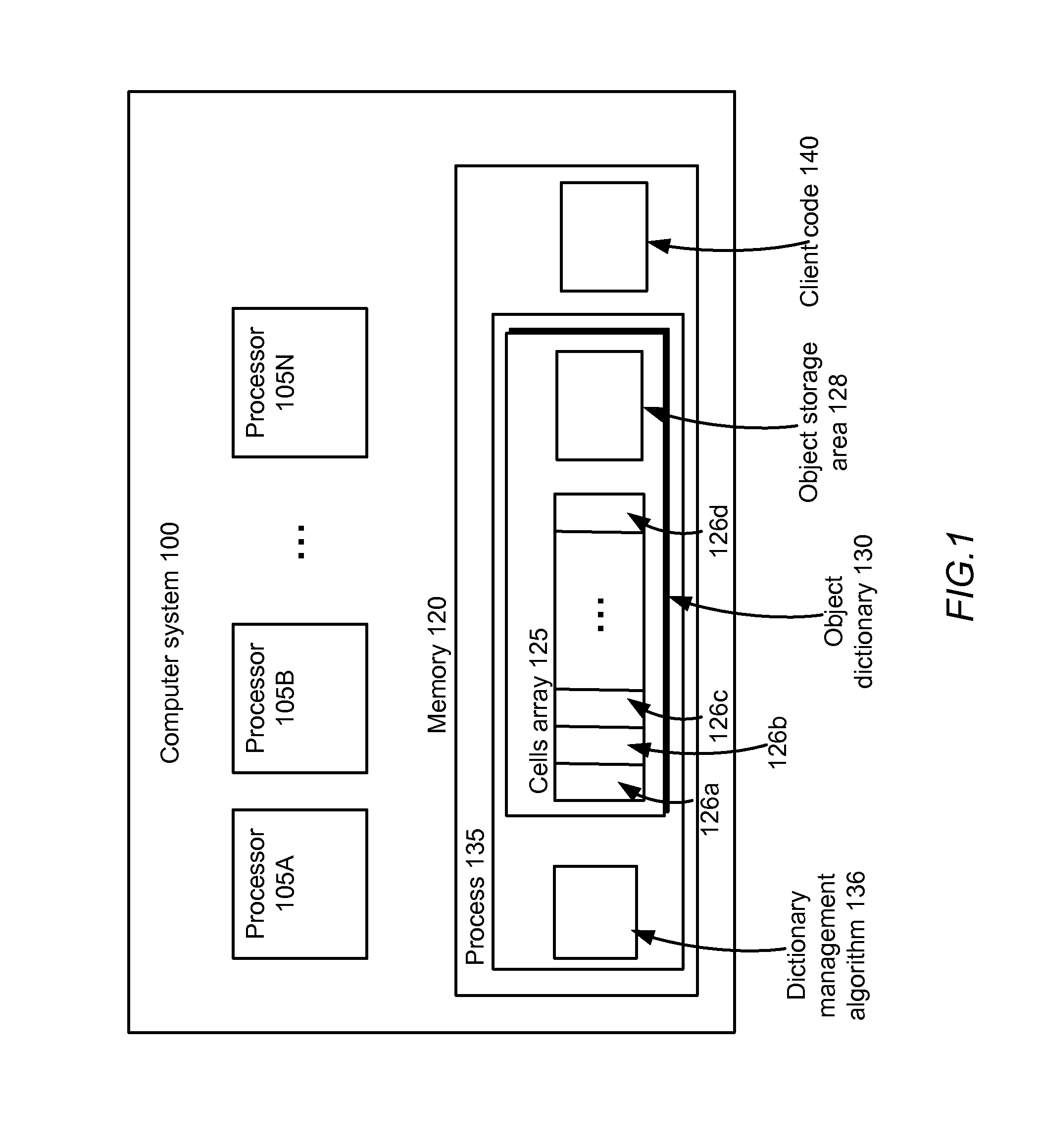

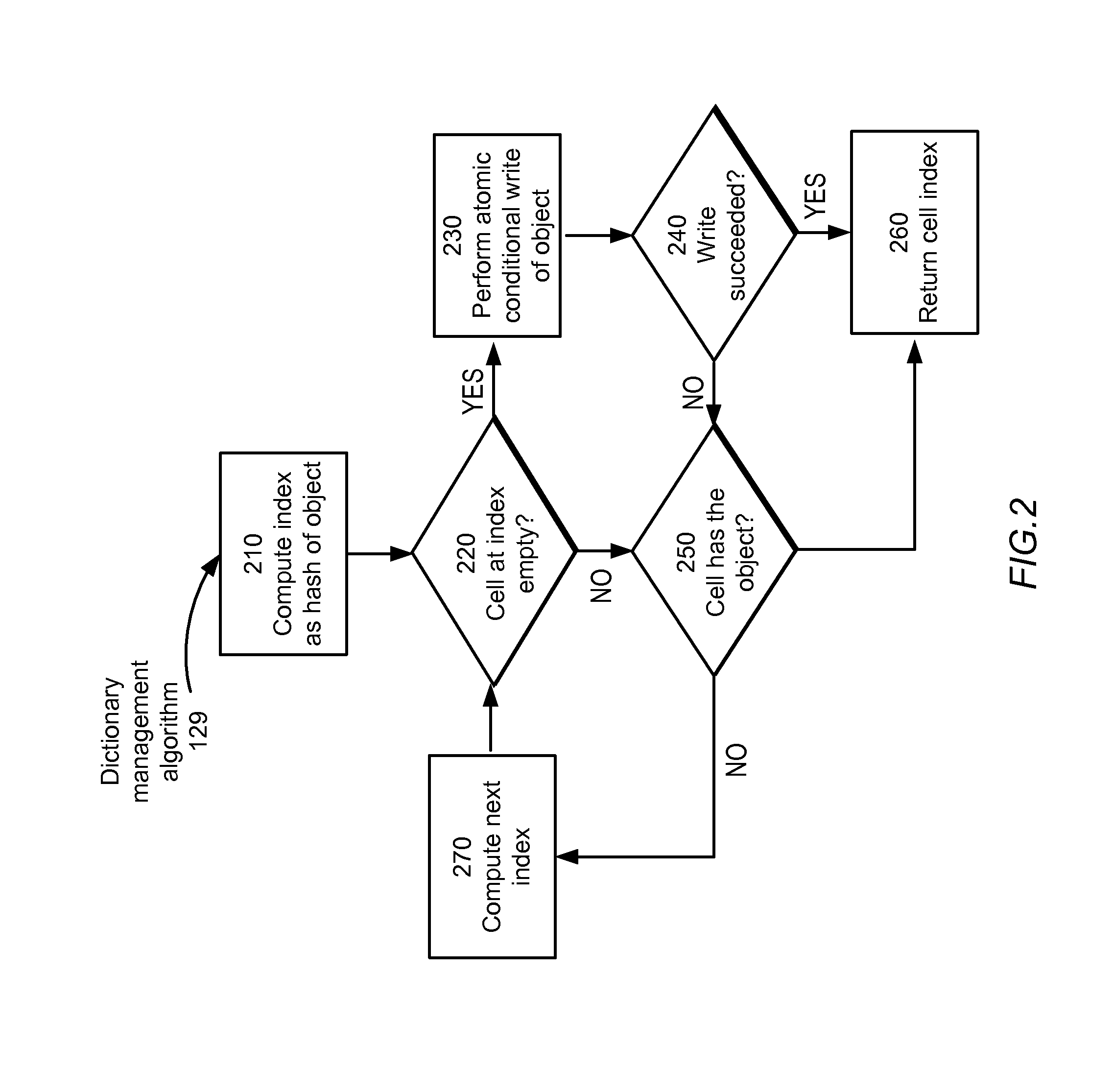

Lock-free concurrent object dictionary

ActiveUS20110161602A1Reduce memory requirementsSave memoryMemory adressing/allocation/relocationProgram controlObject storage64-bit computing

An object storage system comprises one or more computer processors or threads that can concurrently access a shared memory, the shared memory comprising an array of equally-sized cells. In one embodiment, each cell is of the size used by the processors to represent a pointer, e.g., 64 bits. Using an algorithm performing only one memory write, and using a hardware-provided transactional operation, such as a compare-and-swap instruction, to implement the memory write, concurrent access is safely accommodated in a lock-free manner.

Owner:META PLATFORMS INC

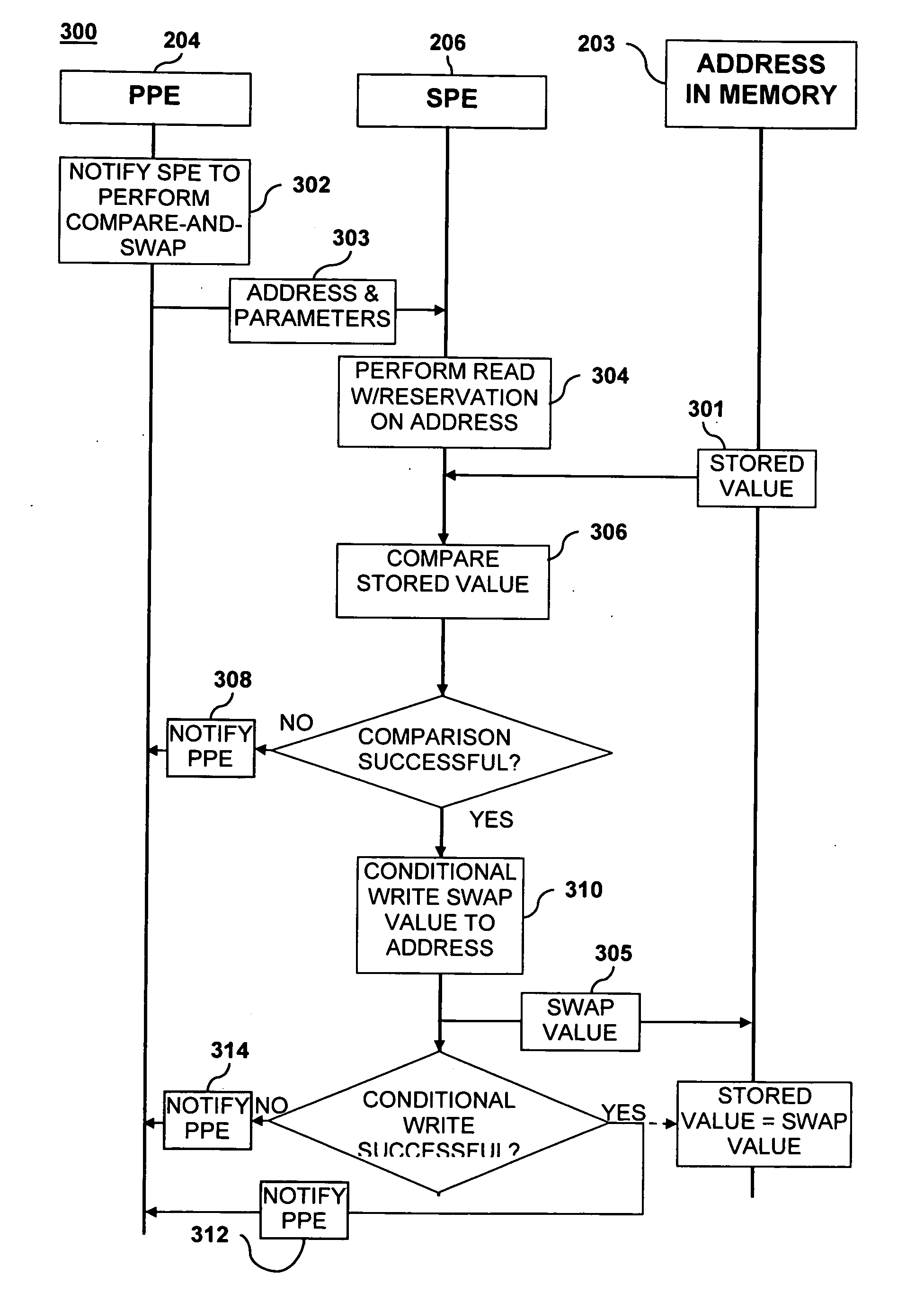

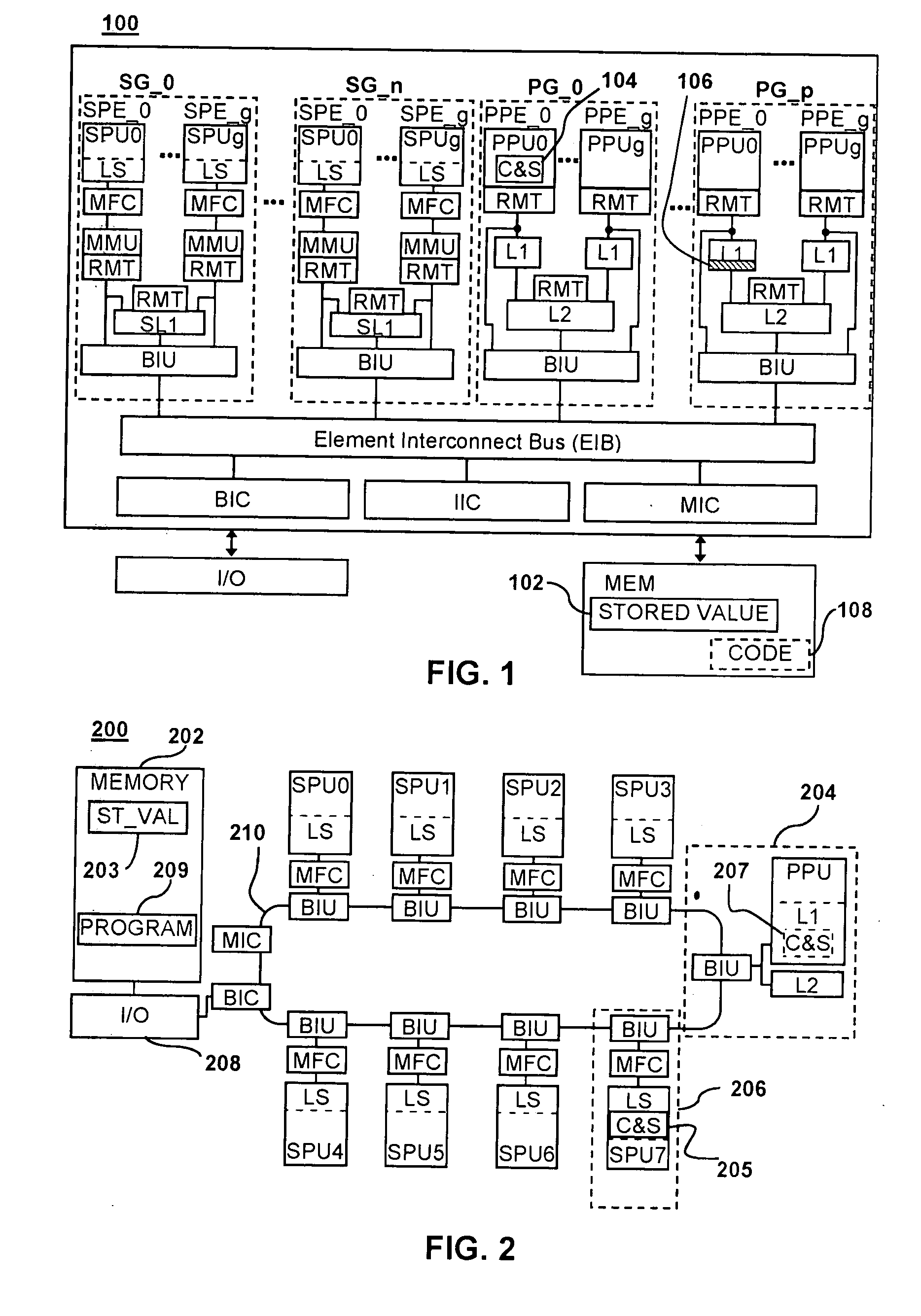

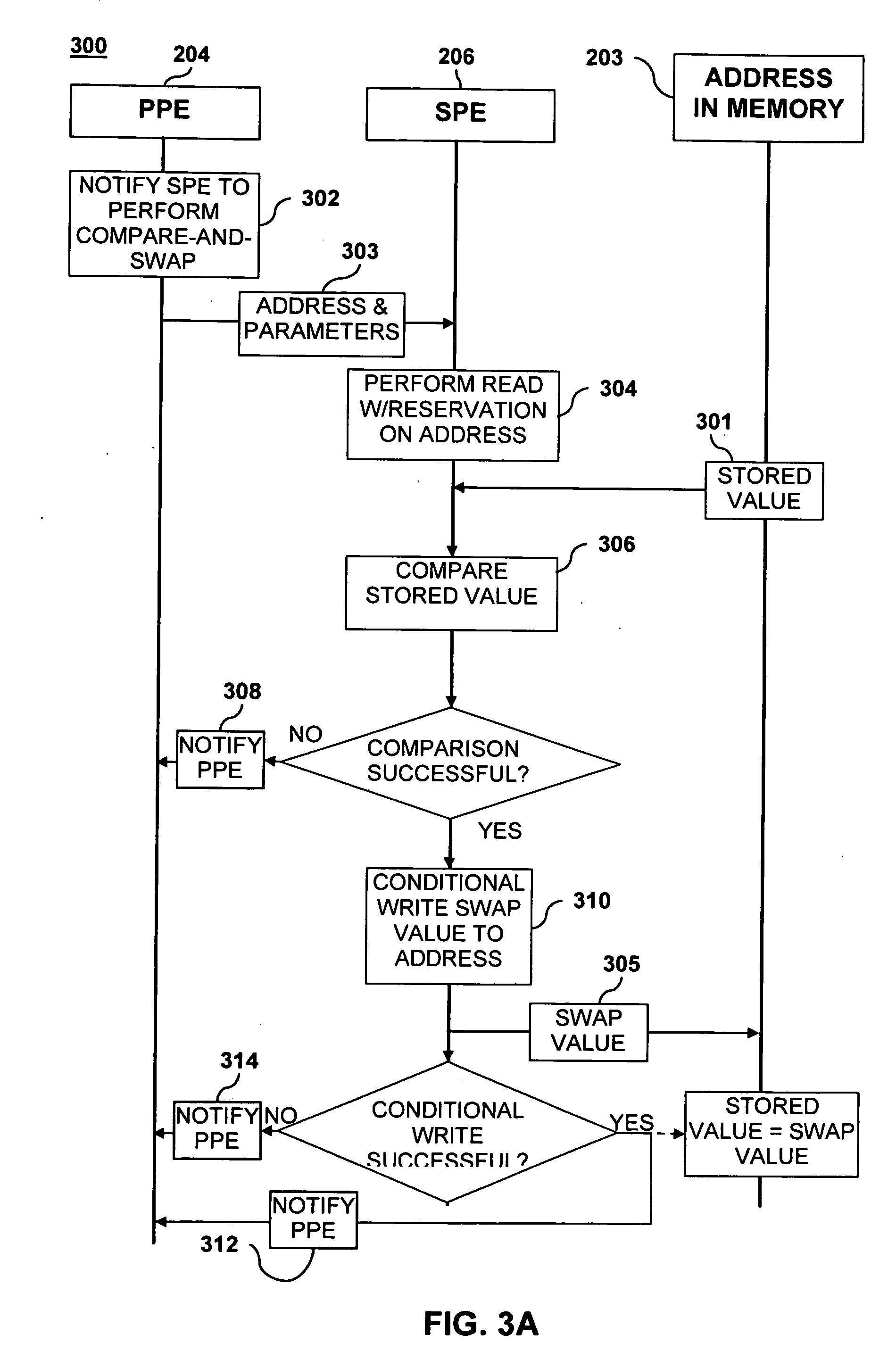

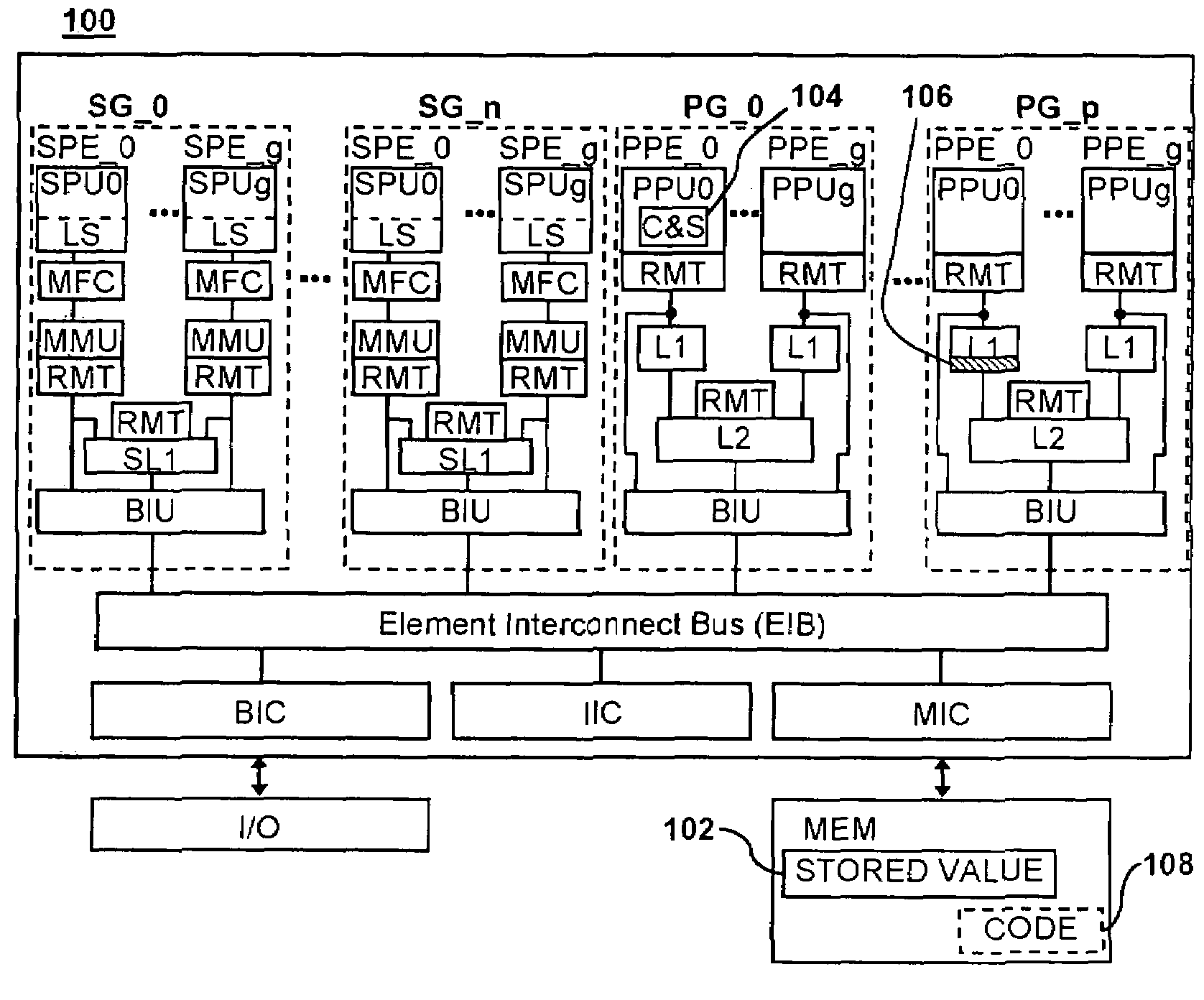

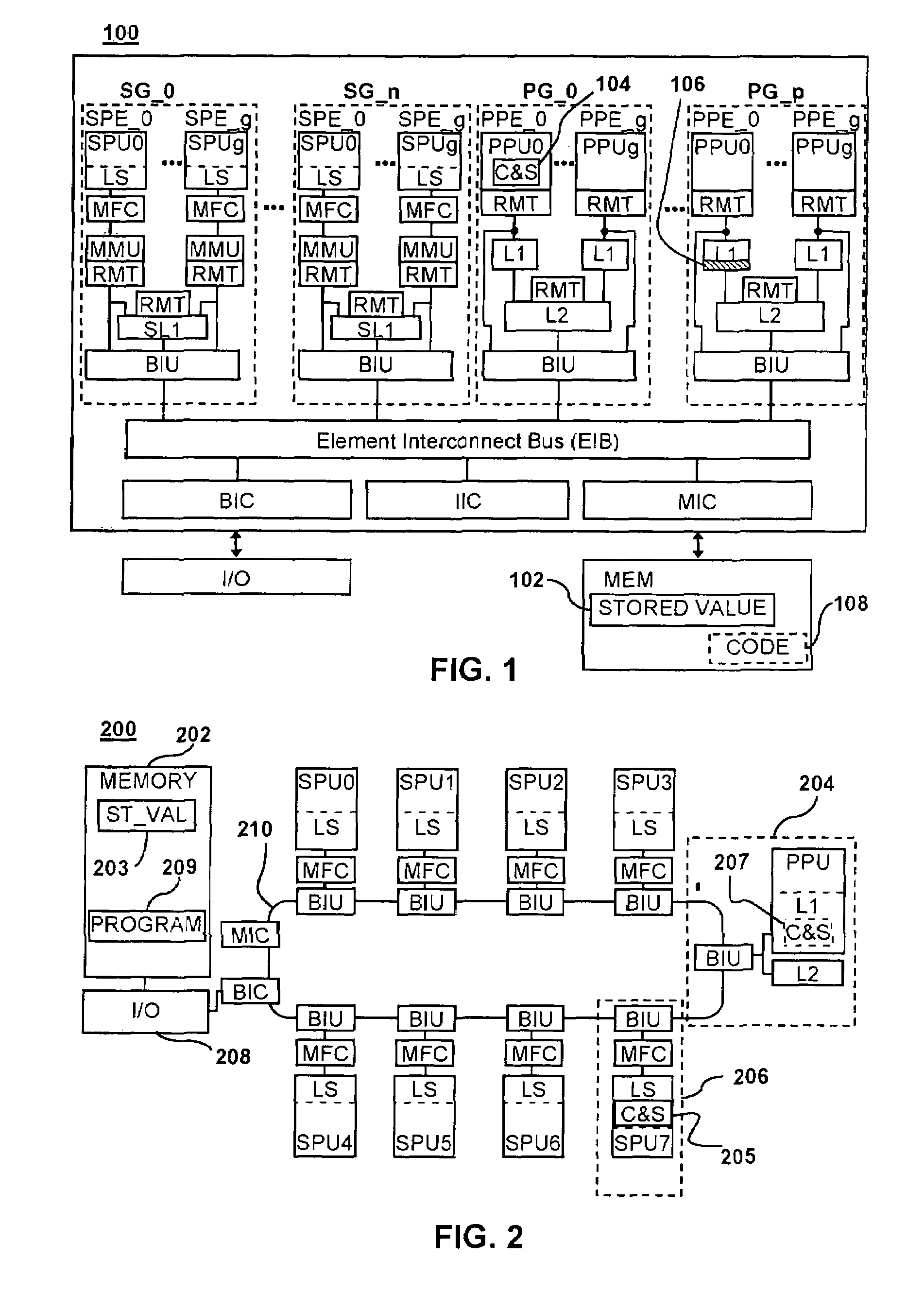

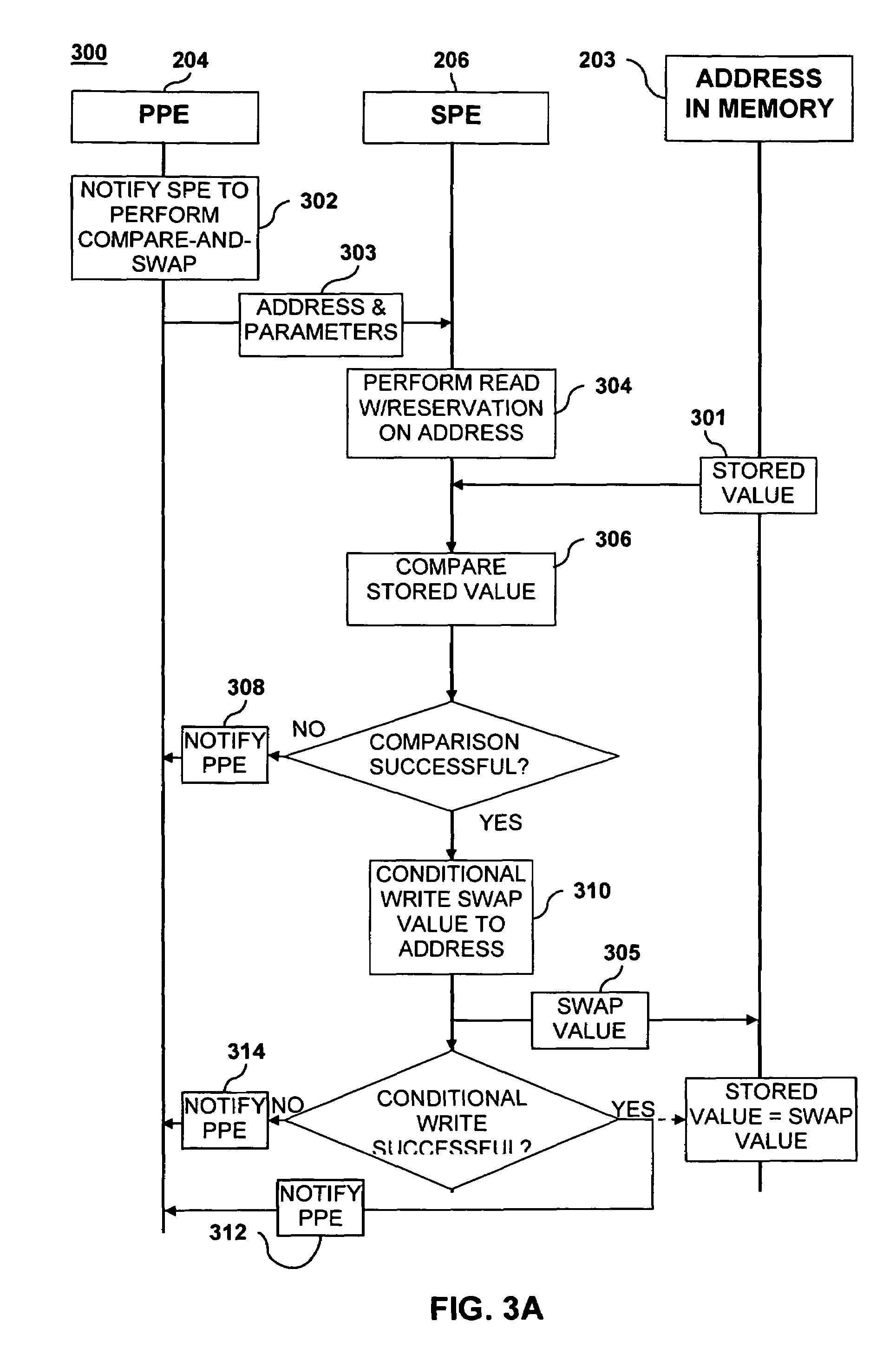

Cell processor atomic compare and swap using dedicated SPE

An atomic compare and swap operation that can be implemented in processor system having a power processor element (PPE) and a synergistic processor element (SPE) that have different sized memory transfer capabilities. The PPE notifies an SPE to perform a compare and swap operation on an address in main memory. The address has a size less than or equal to a maximum memory transfer size for the SPE and greater than a maximum memory transfer size for the PPE. The SPE atomically performs the compare and swap operation and notifies the PPE of the success or failure of the compare and swap operation.

Owner:SONY COMPUTER ENTERTAINMENT INC

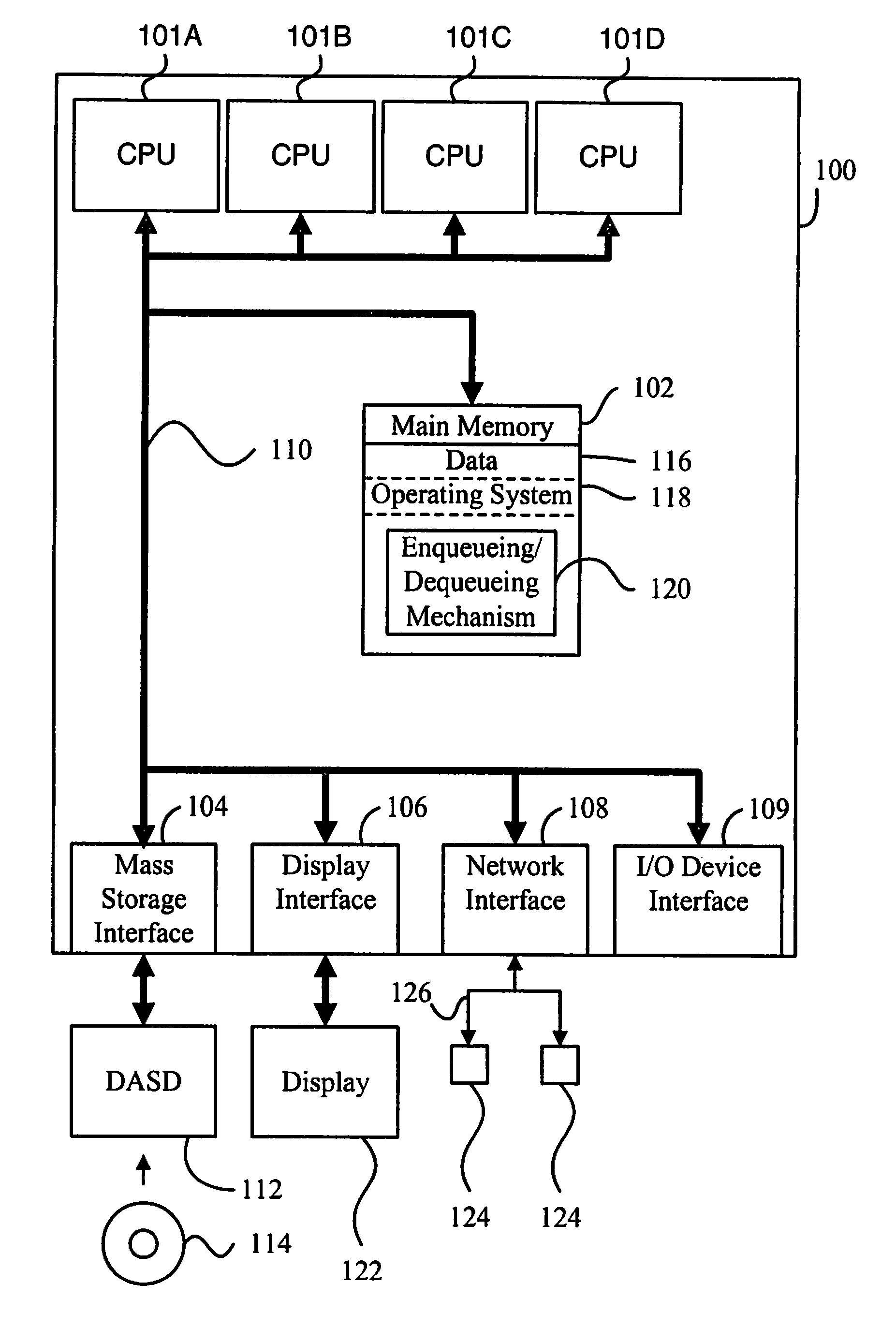

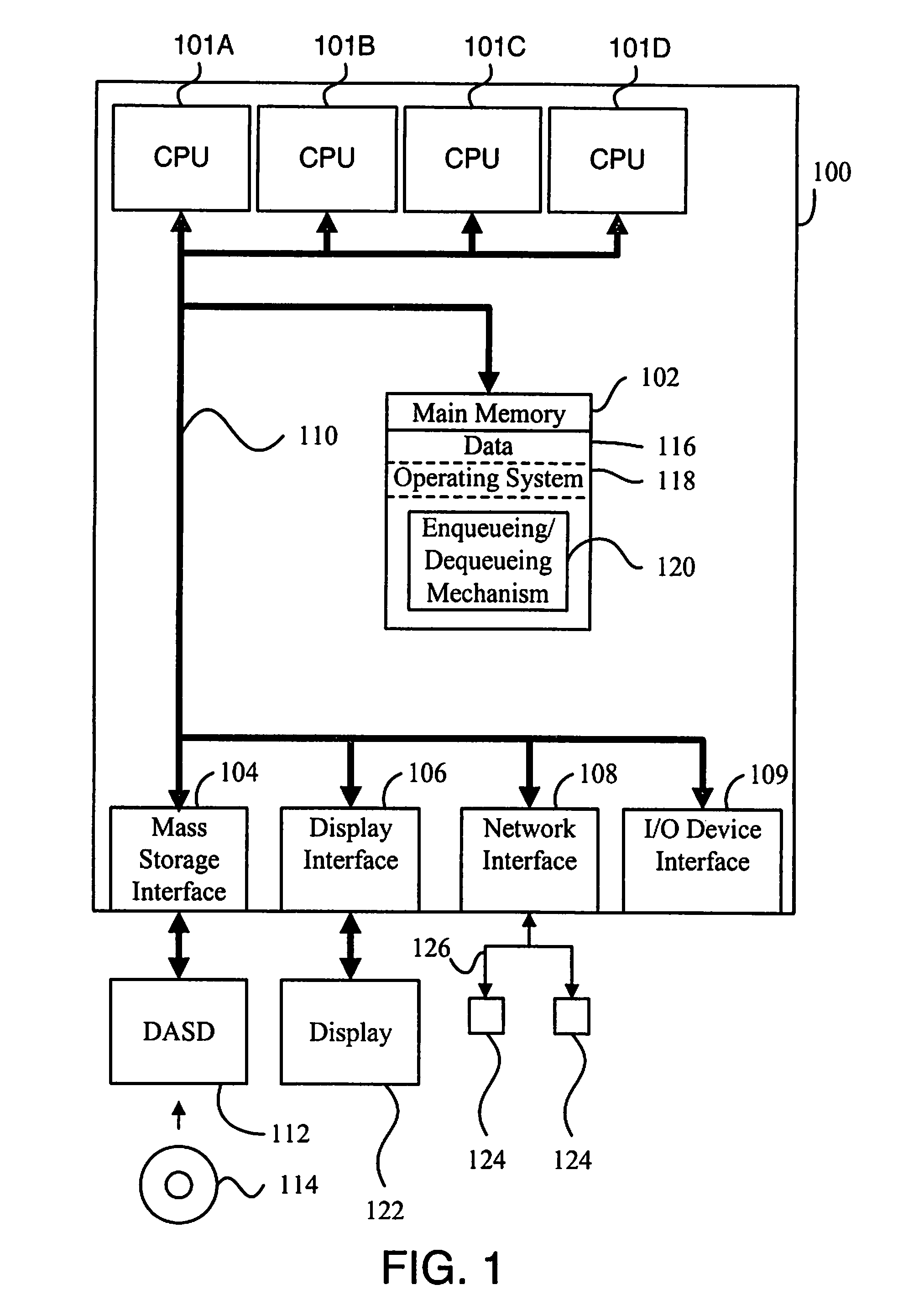

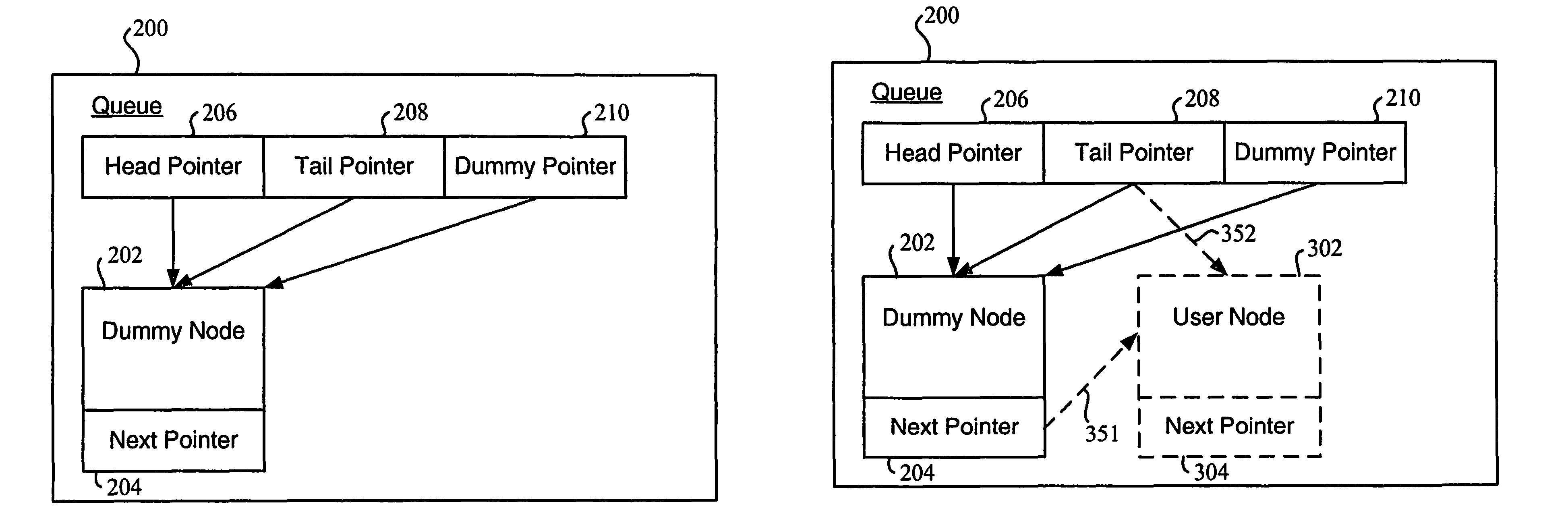

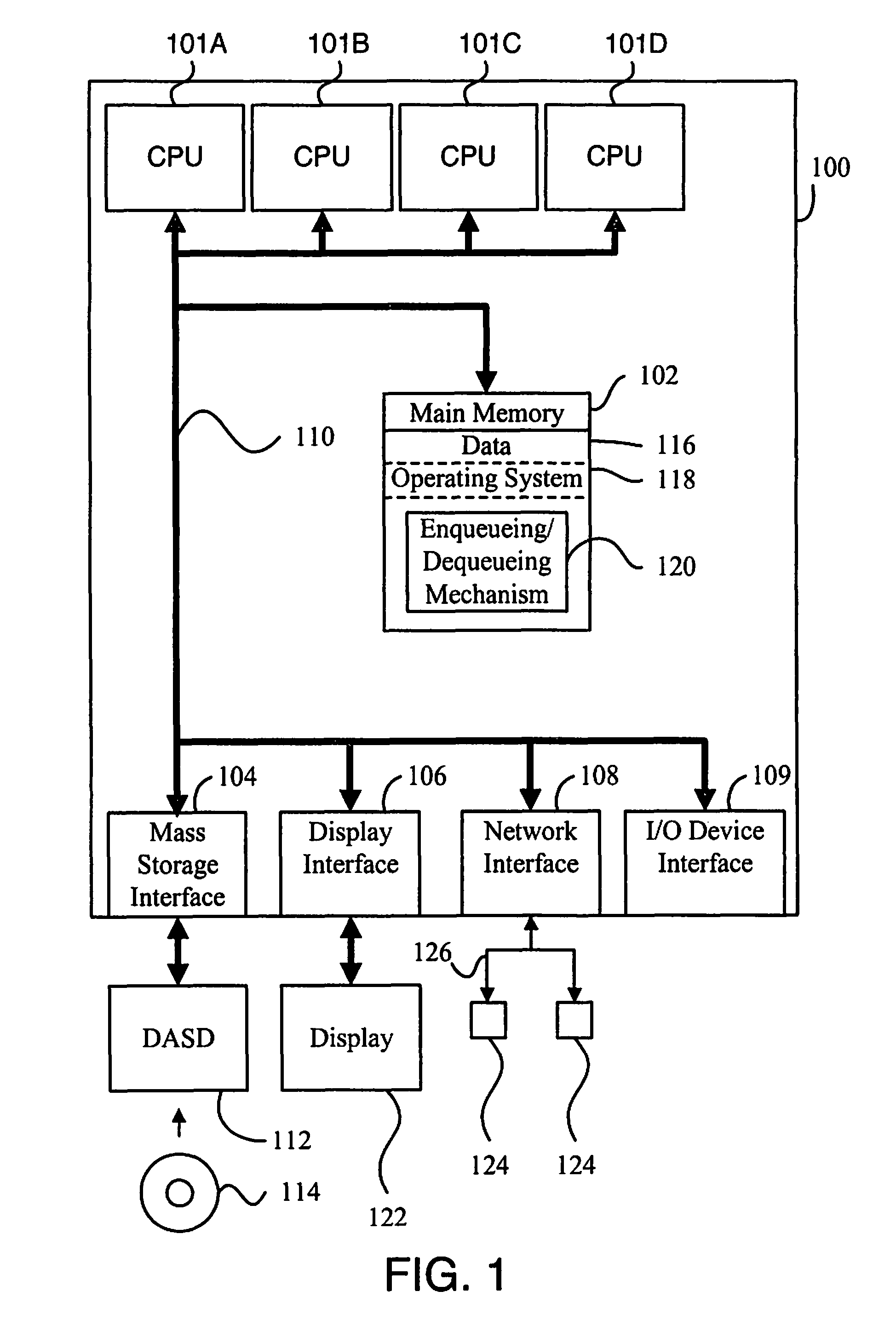

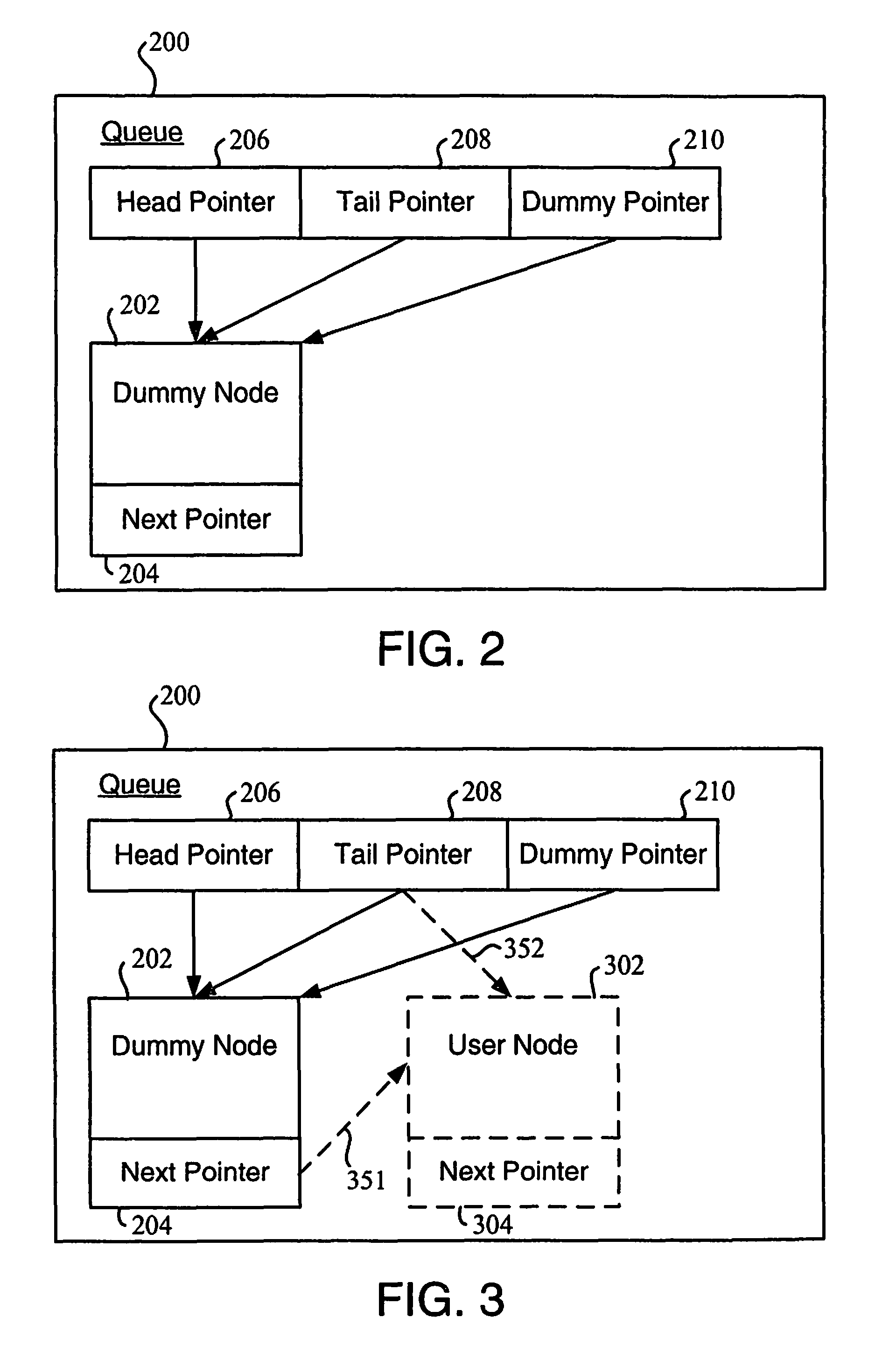

Concurrent, Non-Blocking, Lock-Free Queue and Method, Apparatus, and Computer Program Product for Implementing Same

InactiveUS20080112423A1Reduce overheadError preventionFrequency-division multiplex detailsLoad-link/store-conditionalFifo queue

A dummy node is enqueued to a concurrent, non-blocking, lock-free FIFO queue only when necessary to prevent the queue from becoming empty. The dummy node is only enqueued during a dequeue operation and only when the queue contains a single user node during the dequeue operation. This reduces overhead relative to conventional mechanisms that always keep a dummy node in the queue. User nodes are enqueued directly to the queue and can be immediately dequeued on-demand by any thread. Preferably, the enqueueing and dequeueing operations include the use of load-linked / store conditional (LL / SC) synchronization primitives. This solves the ABA problem without requiring the use a unique number, such as a queue-specific number, and contrasts with conventional mechanisms that include the use of compare-and-swap (CAS) synchronization primitives and address the ABA problem through the use of a unique number. In addition, storage ordering fences are preferably inserted to allow the algorithm to run on weakly consistent processors.

Owner:IBM CORP

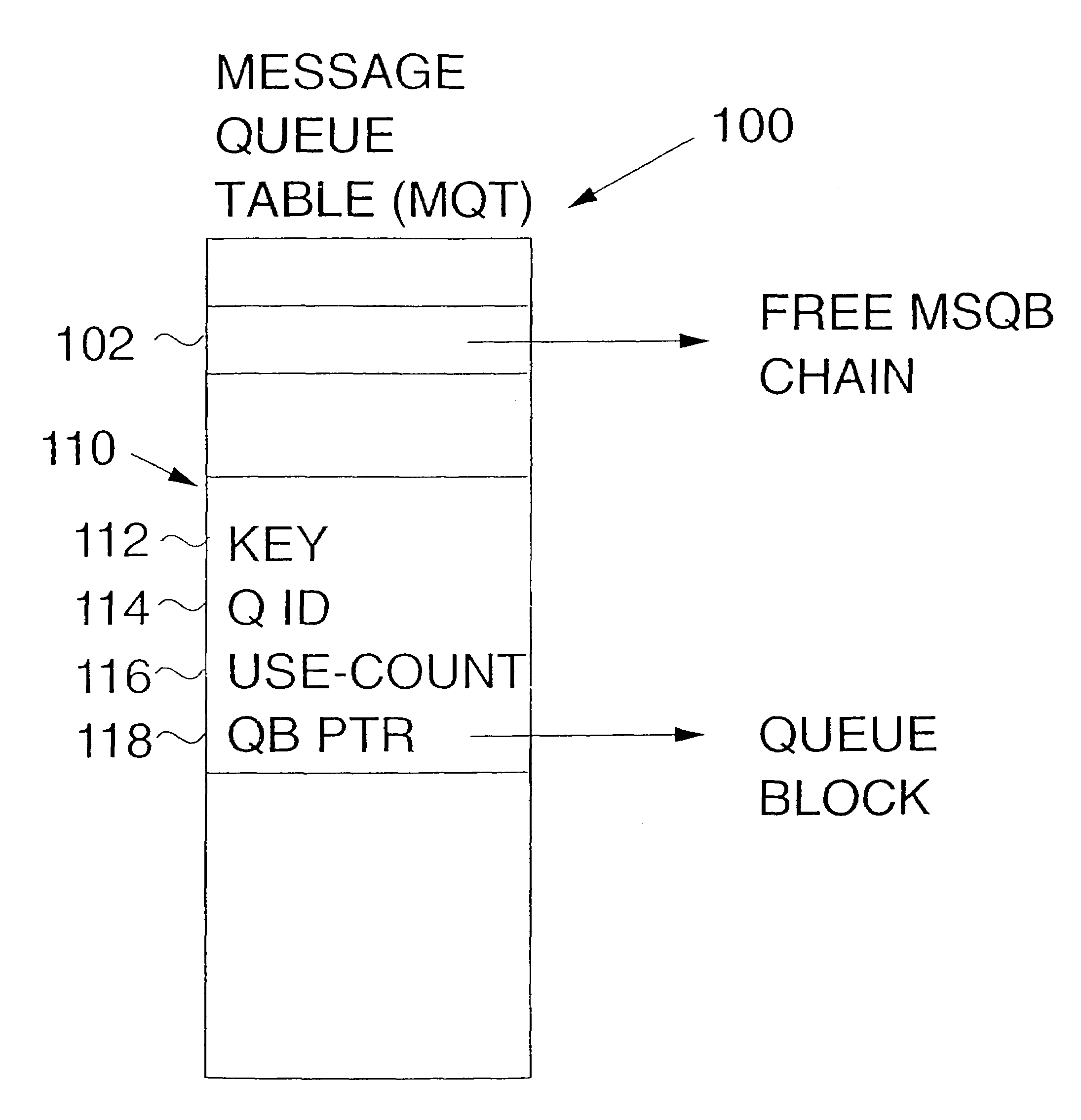

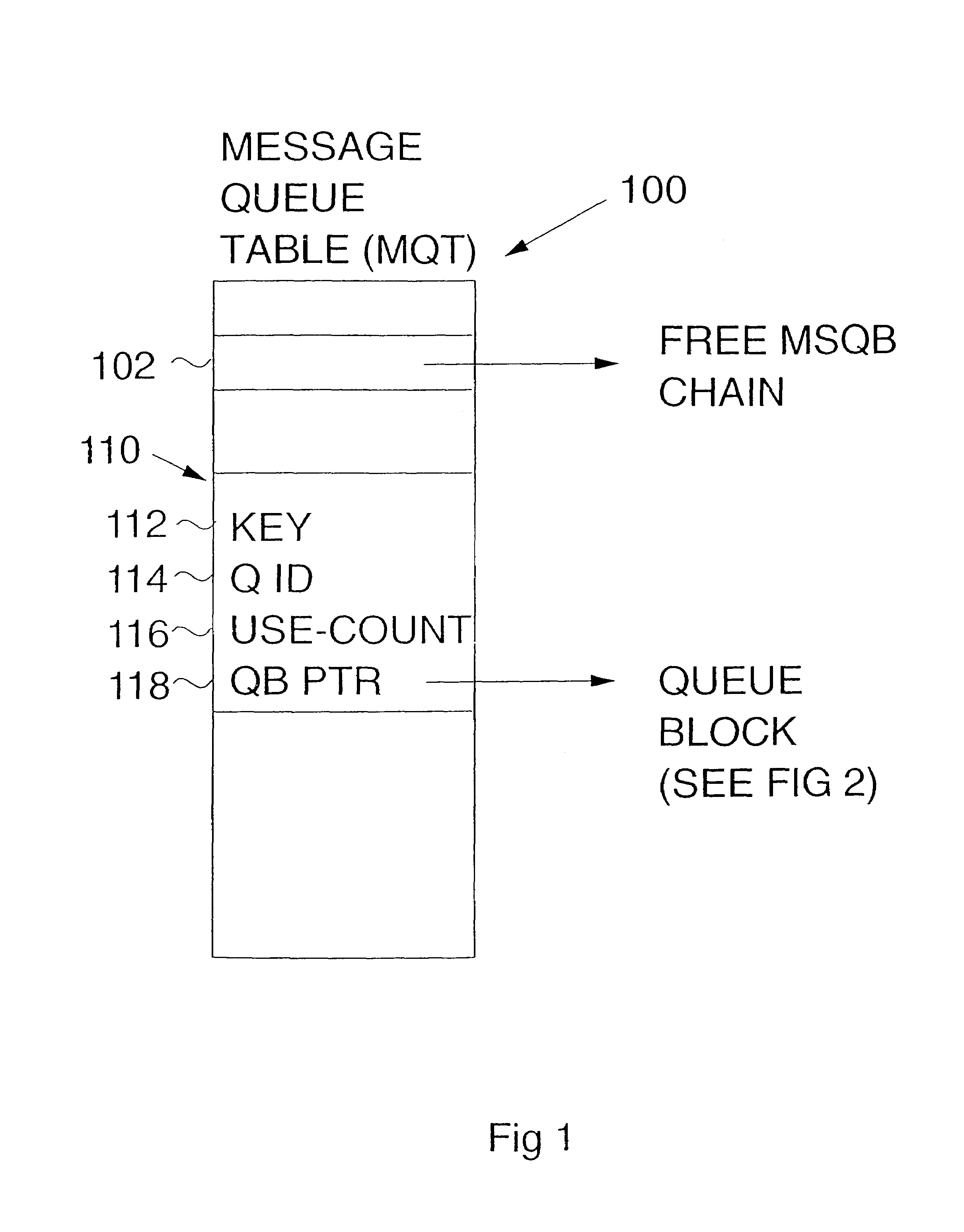

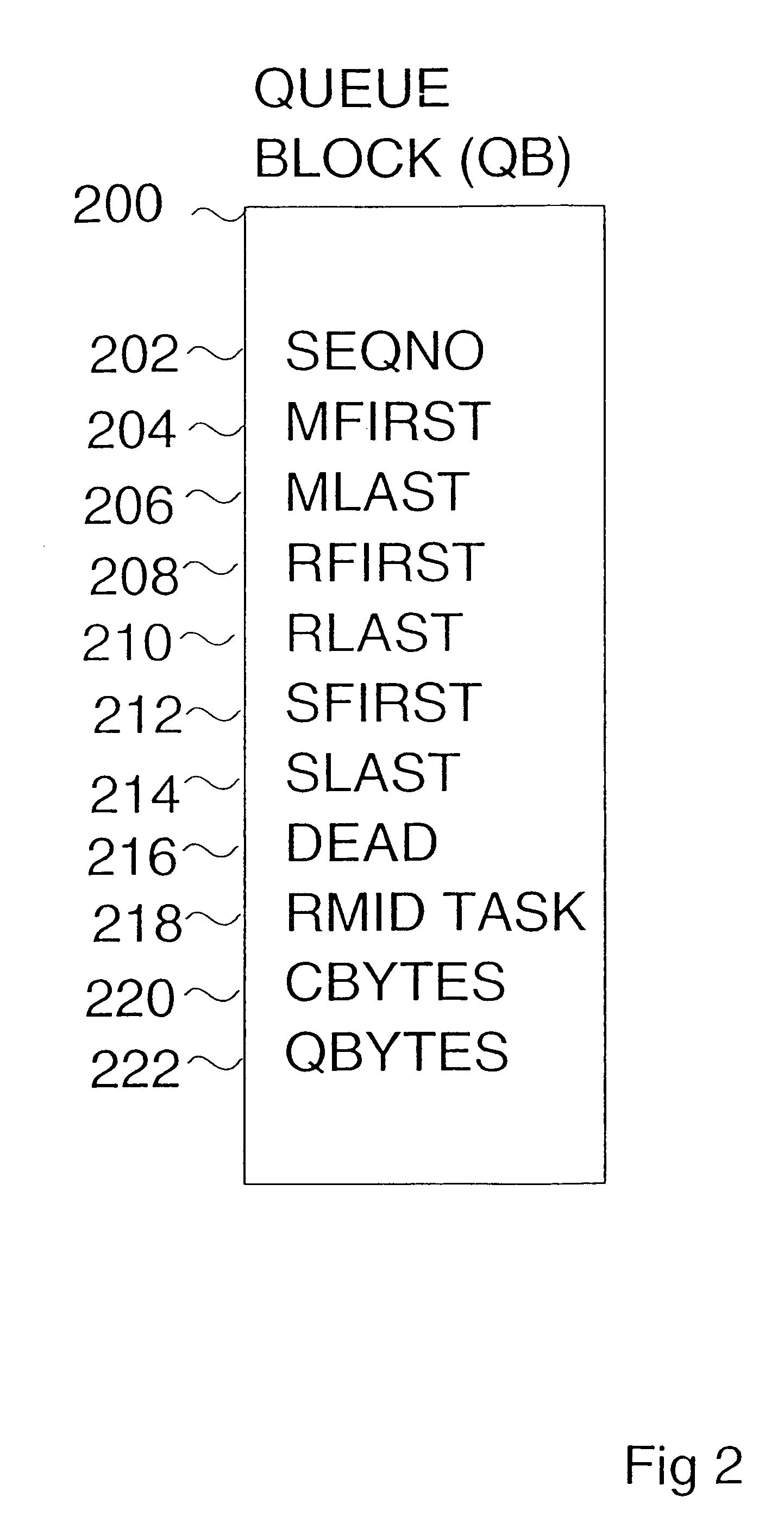

Method and apparatus for serializing a message queue in a multiprocessing environment

InactiveUS6976260B1Possible to recoverAvoid deletionMultiprogramming arrangementsInput/output processes for data processingFootprintingMessage queue

A single atomic instruction is used to change up to four disjoint areas in memory concurrently in an extended compare and swap operation, replacing traditional locks for serialization and providing recovery for all queue manipulations. Use count-based responsibility passing is employed so that any number of tasks can read the various message queue chains, concurrent with queue updates being made. A summary queue update sequence number is maintained to provide concurrent chain update detection, so that any number of tasks can add elements to the end, or remove elements from the middle (i.e. any where in the chain) concurrently. Concurrent footprinting is used with chain manipulation, so that all (or none) of the chaining indicators and a footprint are set with a single, non-interruptible instruction, making it possible for recovery to always take the correct action. One such use of concurrent footprinting is the concurrent footprinting of use count changes, while another is the transfer of ownership of message queue control blocks. In a preferred embodiment on an IBM S / 390 platform, the Perform Locked Operation (PLO) instruction is used to perform the extended compare and swap operations.

Owner:IBM CORP

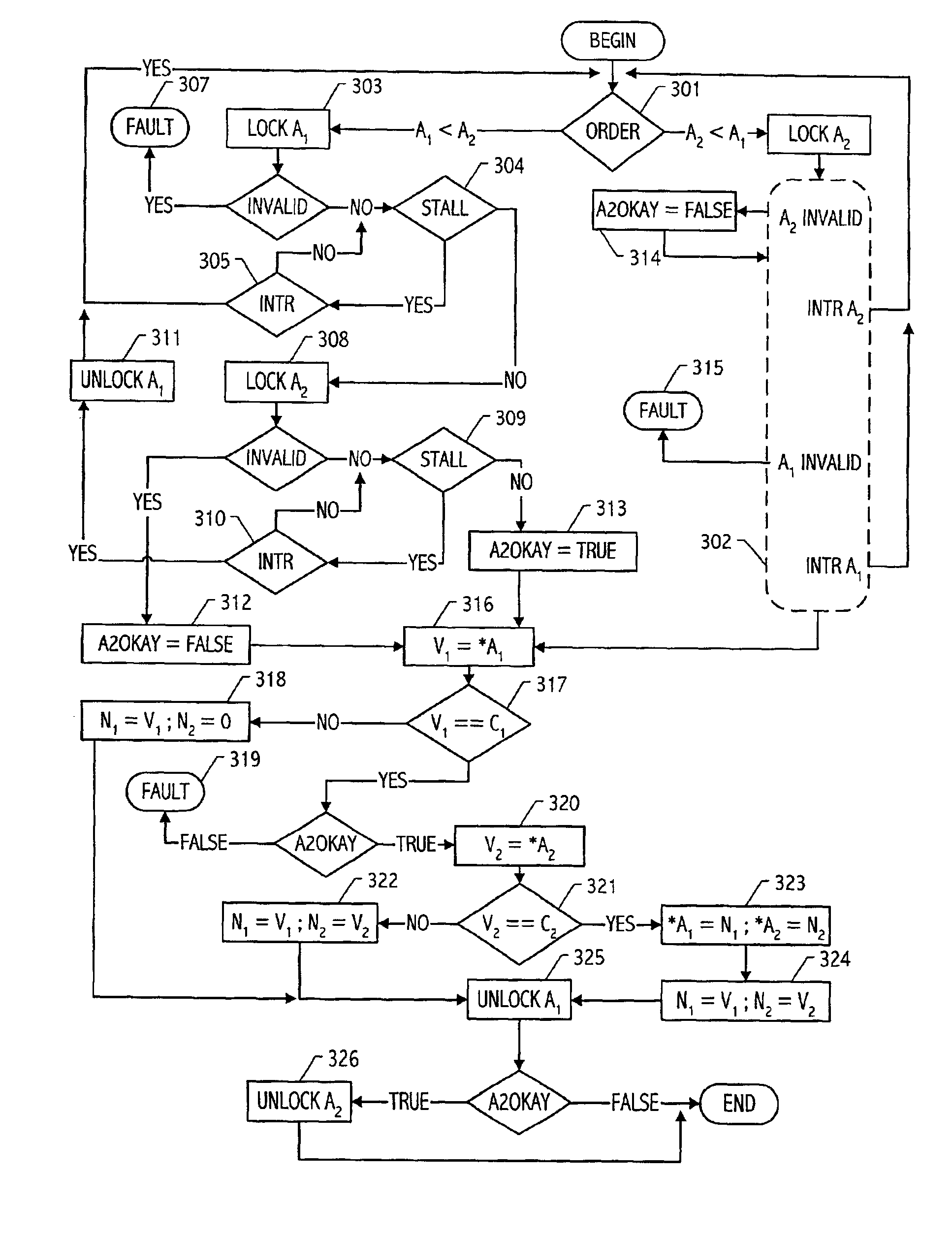

Selective signal of fault in compound compare-and-swap

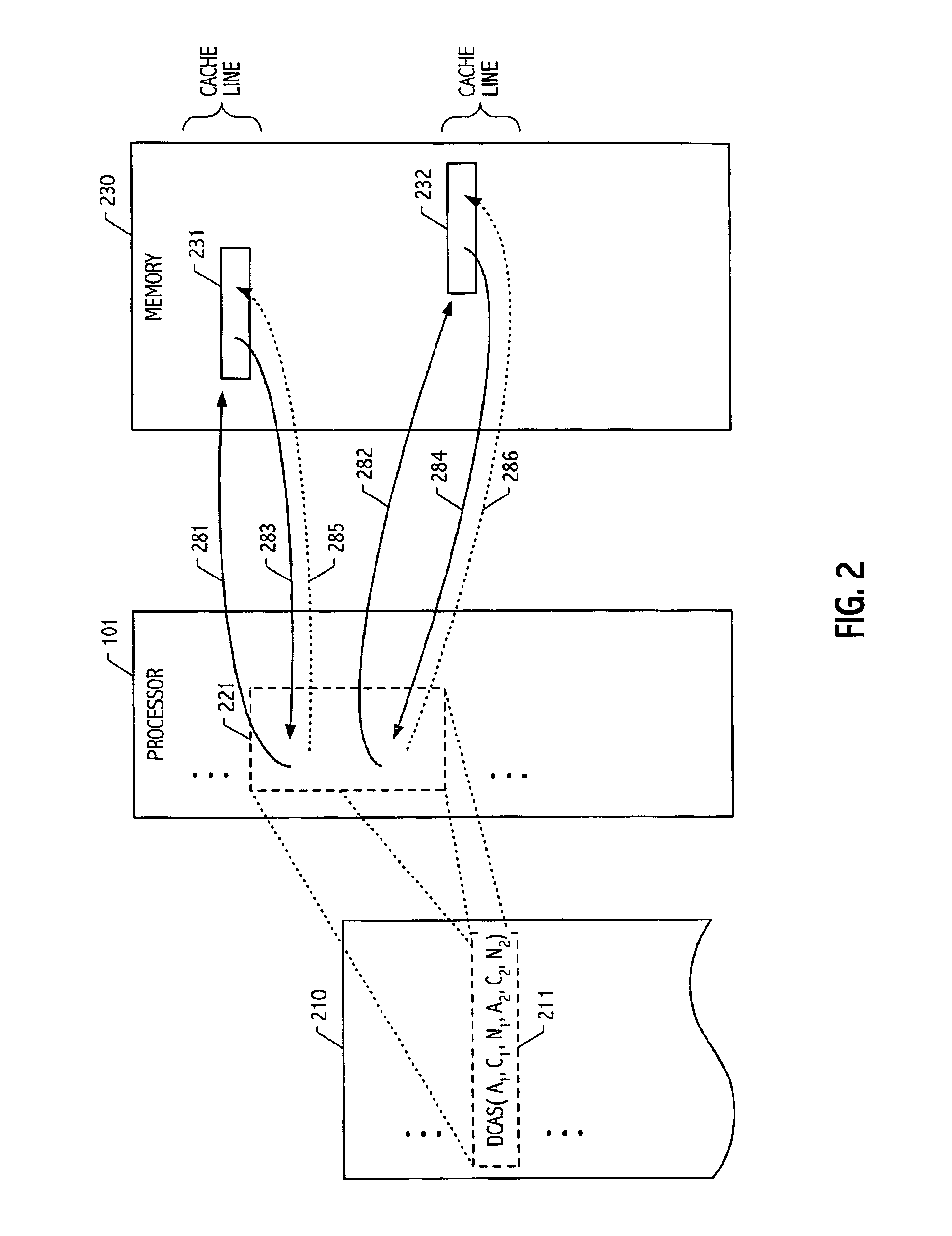

InactiveUS6880071B2Avoid deadlockDigital computer detailsUnauthorized memory use protectionDouble compare-and-swapMemory address

A sequentially performed implementation of a compound compare-and-swap (nCAS) operation has been developed. In one implementation, a double compare-and-swap (DCAS) operation does not result in a fault, interrupt, or trap in the situation where memory address A2 is invalid and the contents of memory address A1 are unequal to C1. In some realizations, memory locations addressed by a sequentially performed nCAS or DCAS instruction are reserved (e.g., locked) in a predefined order in accordance with a fixed total order of memory locations. In this way, deadlock between concurrently executed instances of sequentially performed nCAS instructions can be avoided. Other realizations defer responsibility for deadlock avoidance to the programmer.

Owner:ATOFINA +1

Lock-free concurrent object dictionary

ActiveUS8443155B2Reduce memory requirementsSave memoryProgram controlMemory systemsObject storage64-bit computing

Owner:META PLATFORMS INC

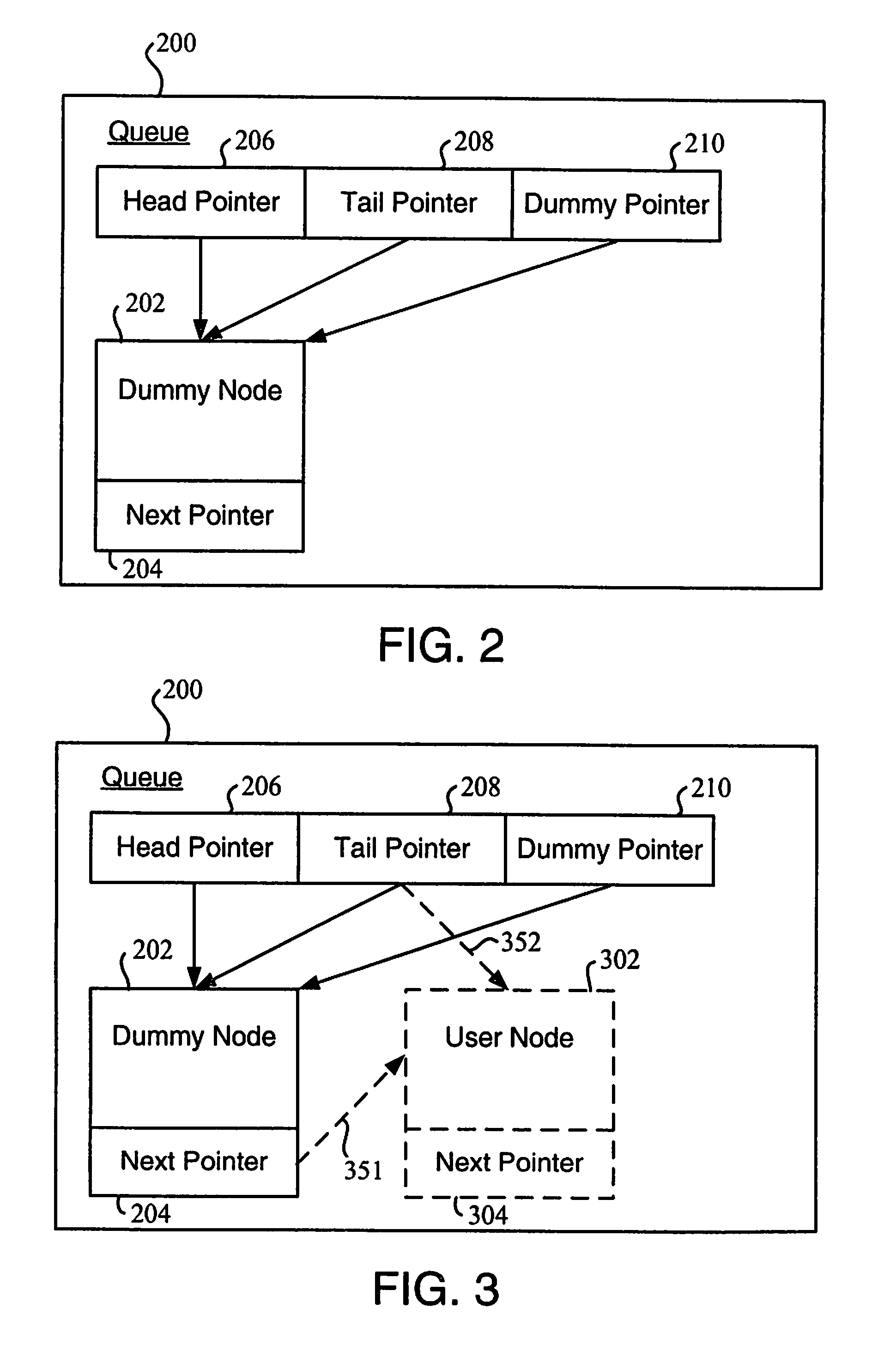

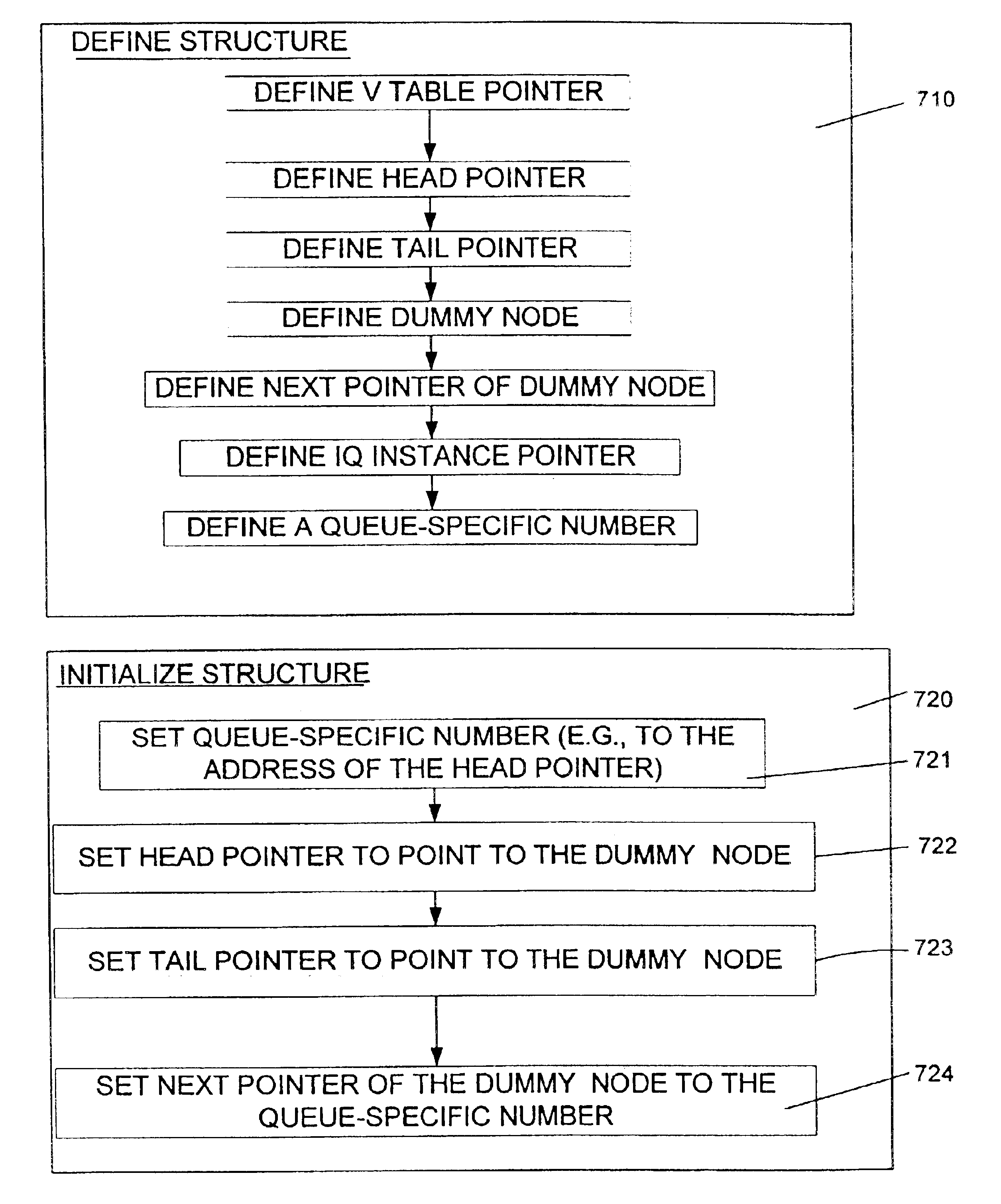

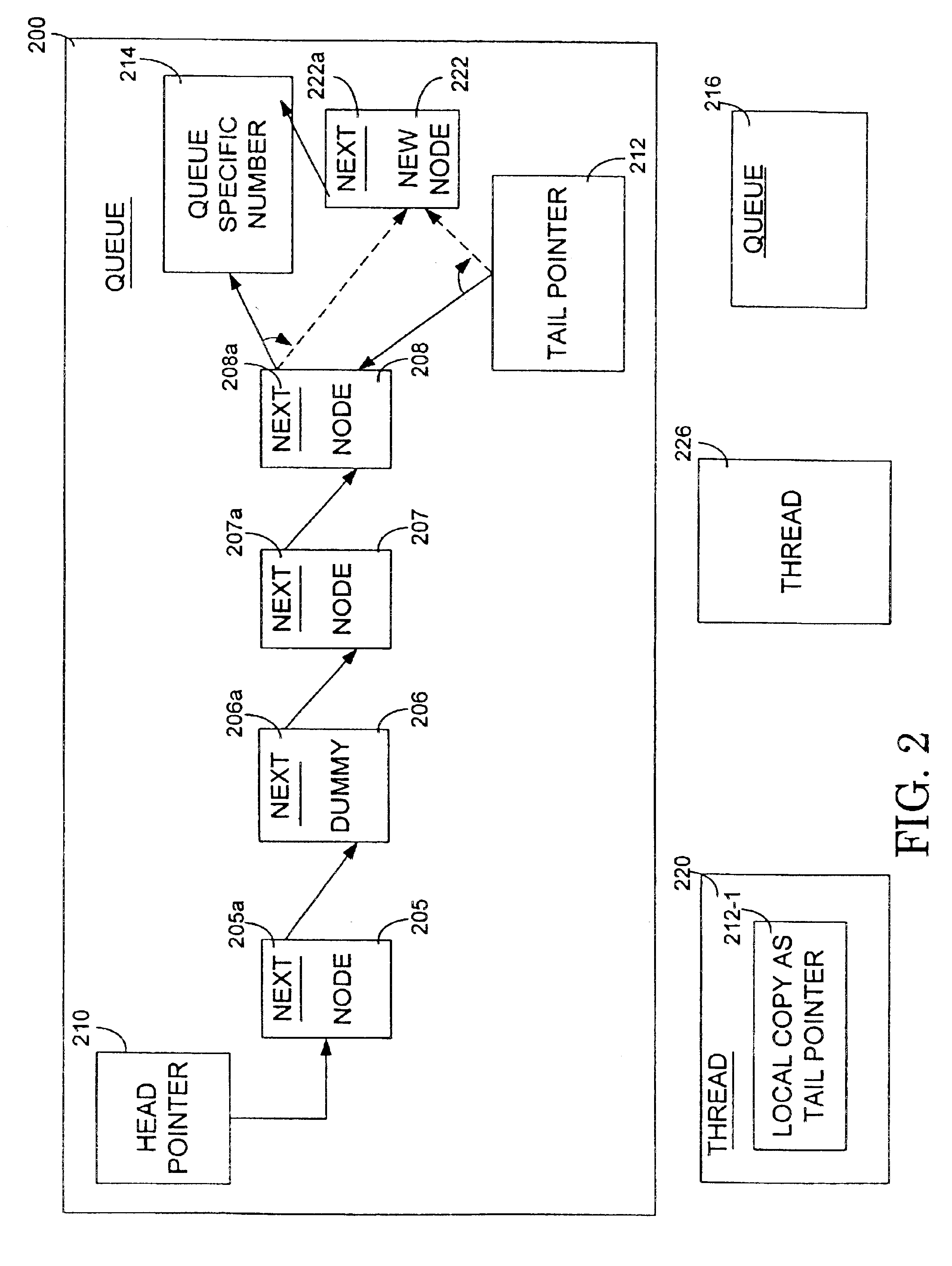

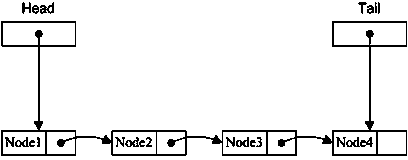

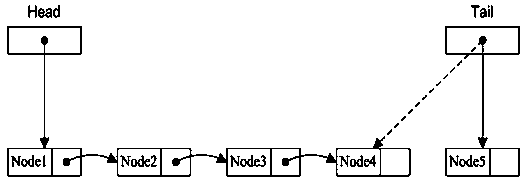

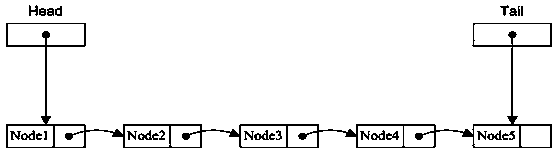

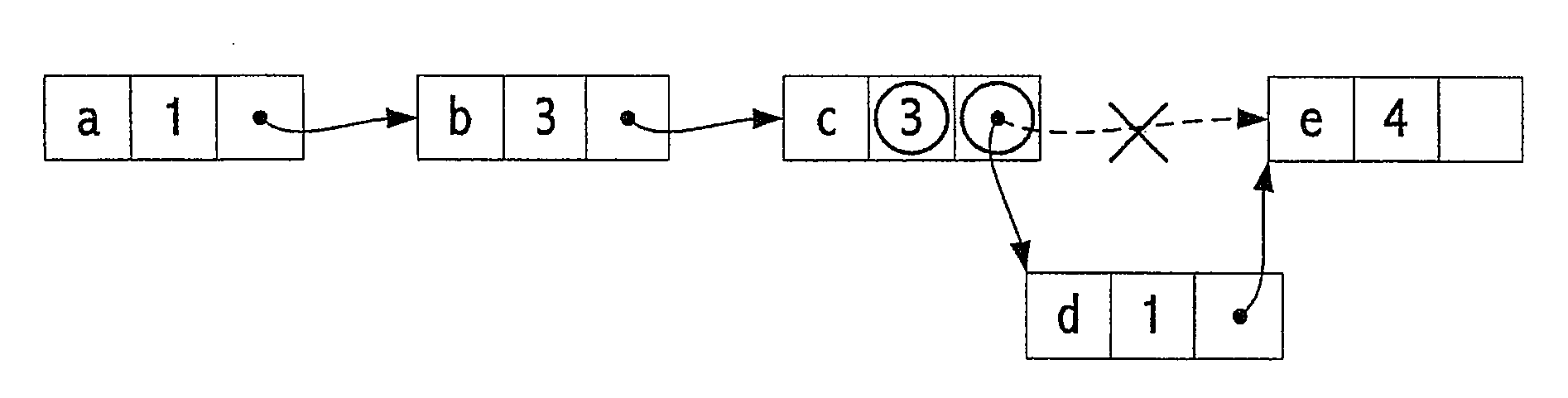

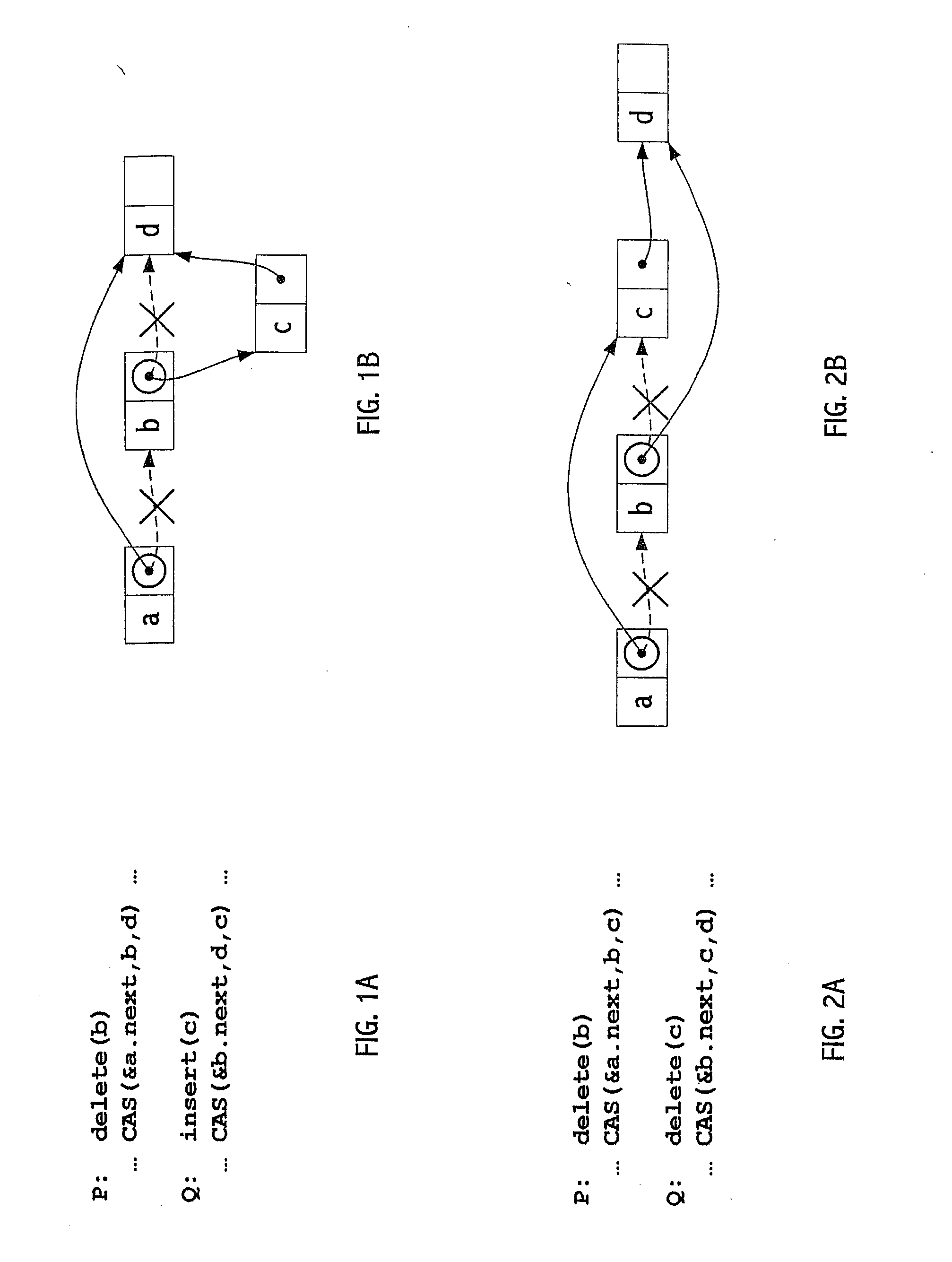

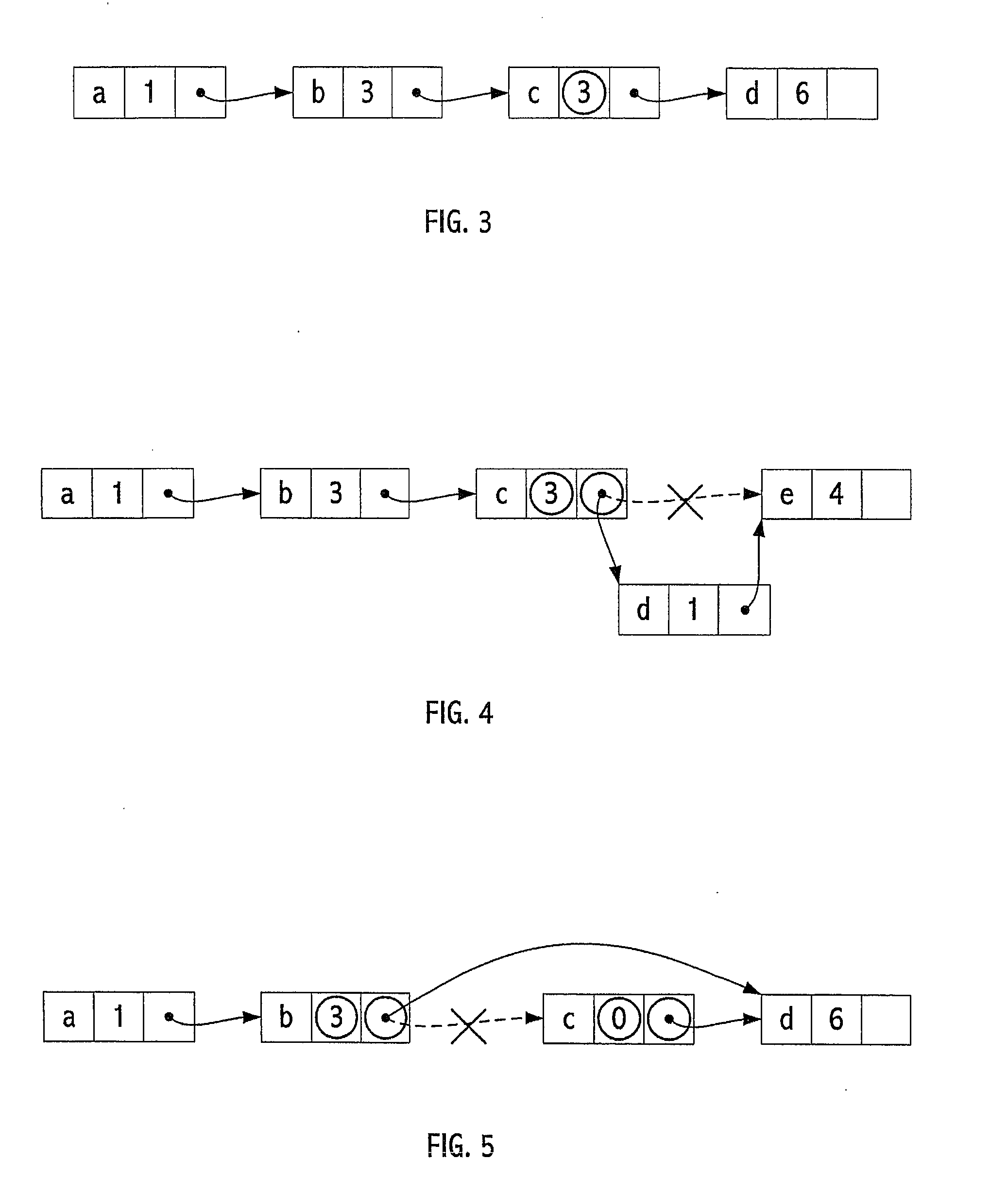

Non-blocking concurrent queues with direct node access by threads

InactiveUS6889269B2Memory systemsInput/output processes for data processingFifo queueApplication software

Multiple non-blocking FIFO queues are concurrently maintained using atomic compare-and-swap (CAS) operations. In accordance with the invention, each queue provides direct access to the nodes stored therein to an application or thread, so that each thread may enqueue and dequeue nodes that it may choose. The prior art merely provided access to the values stored in the node. In order to avoid anomalies, the queue is never allowed to become empty by requiring the presence of at least a dummy node in the queue. The ABA problem is solved by requiring that the next pointer of the tail node in each queue point to a “magic number” unique to the particular queue, such as the pointer to the queue head or the address of the queue head, for example. This obviates any need to maintain a separate count for each node.

Owner:MICROSOFT TECH LICENSING LLC

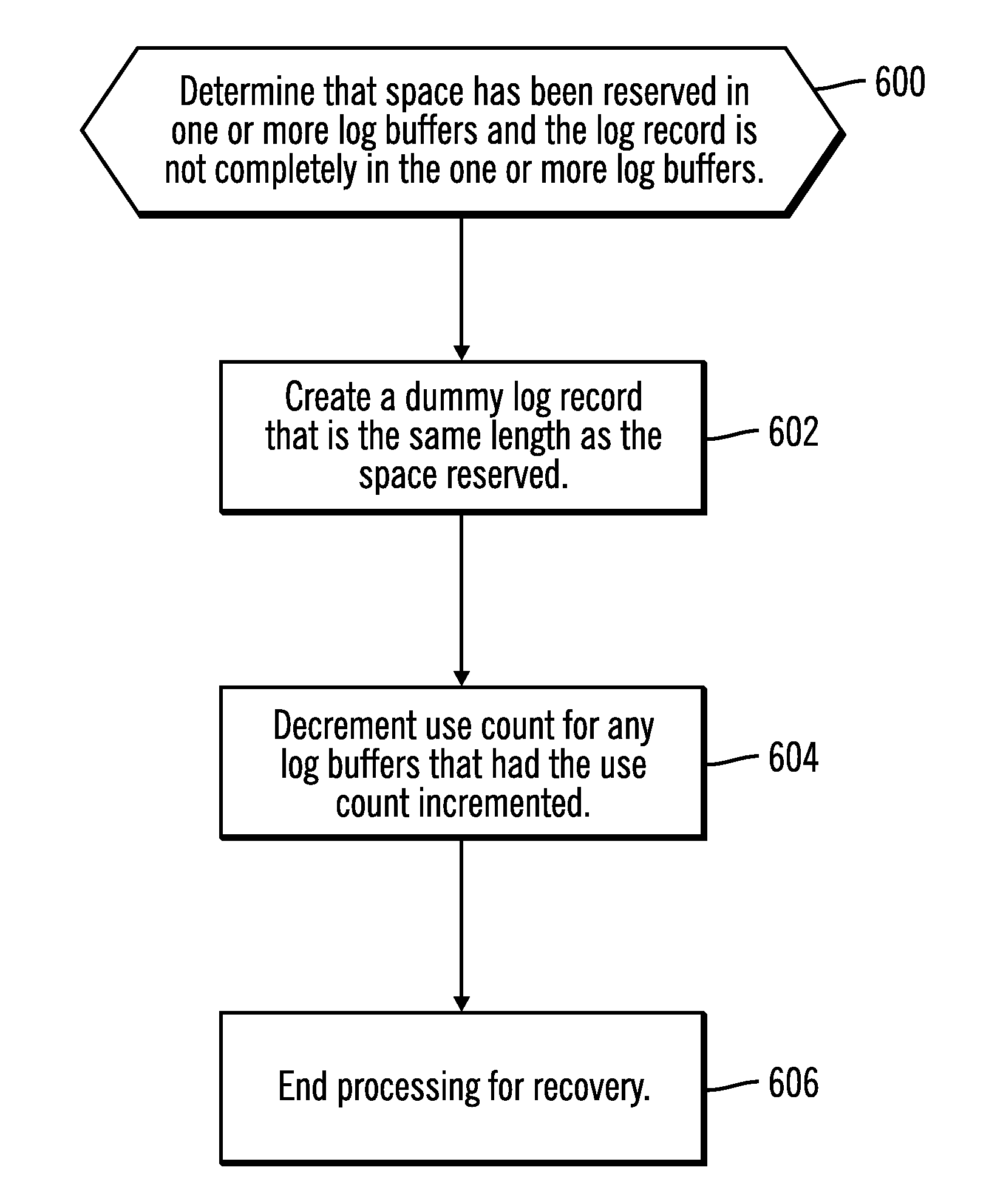

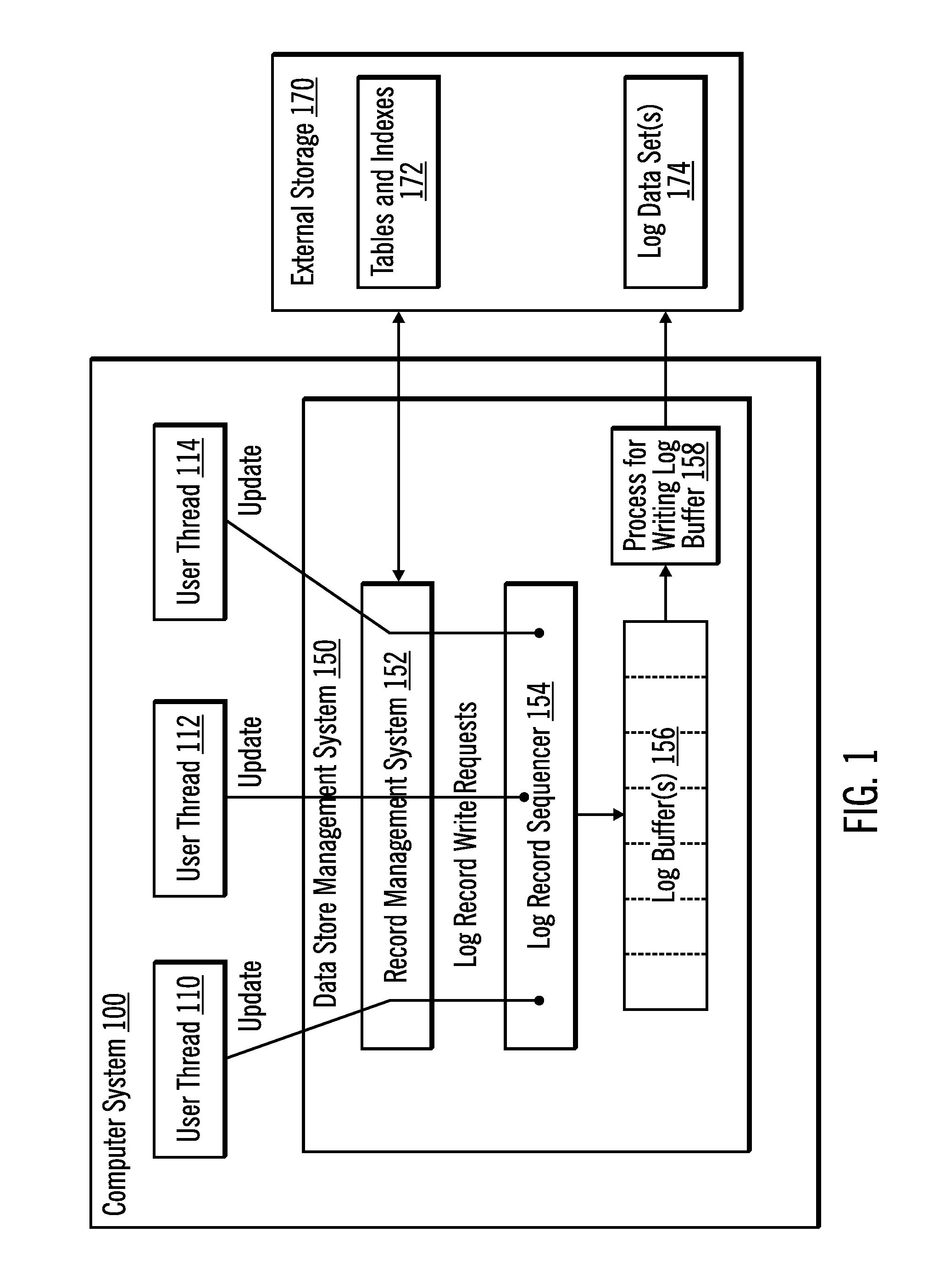

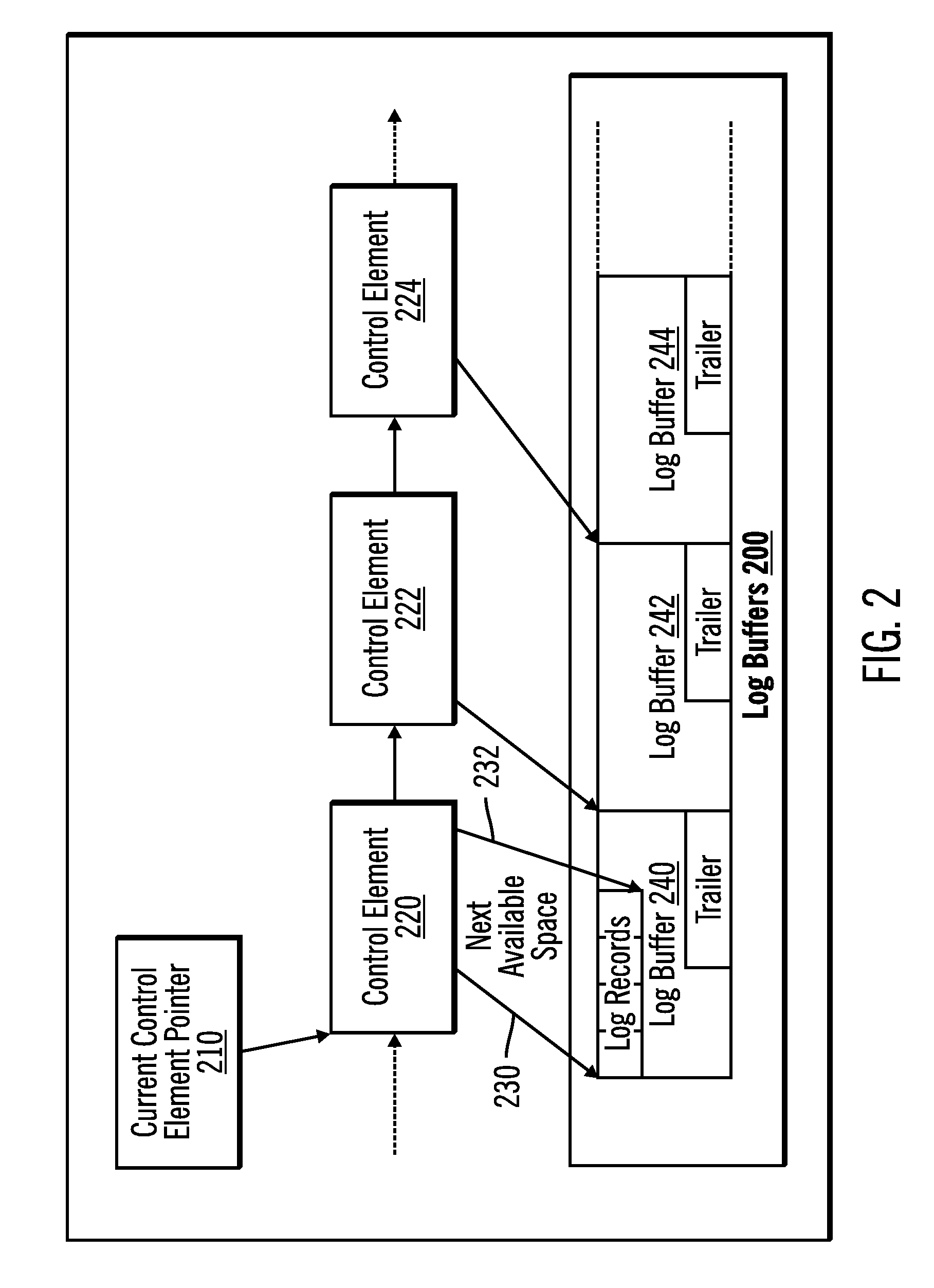

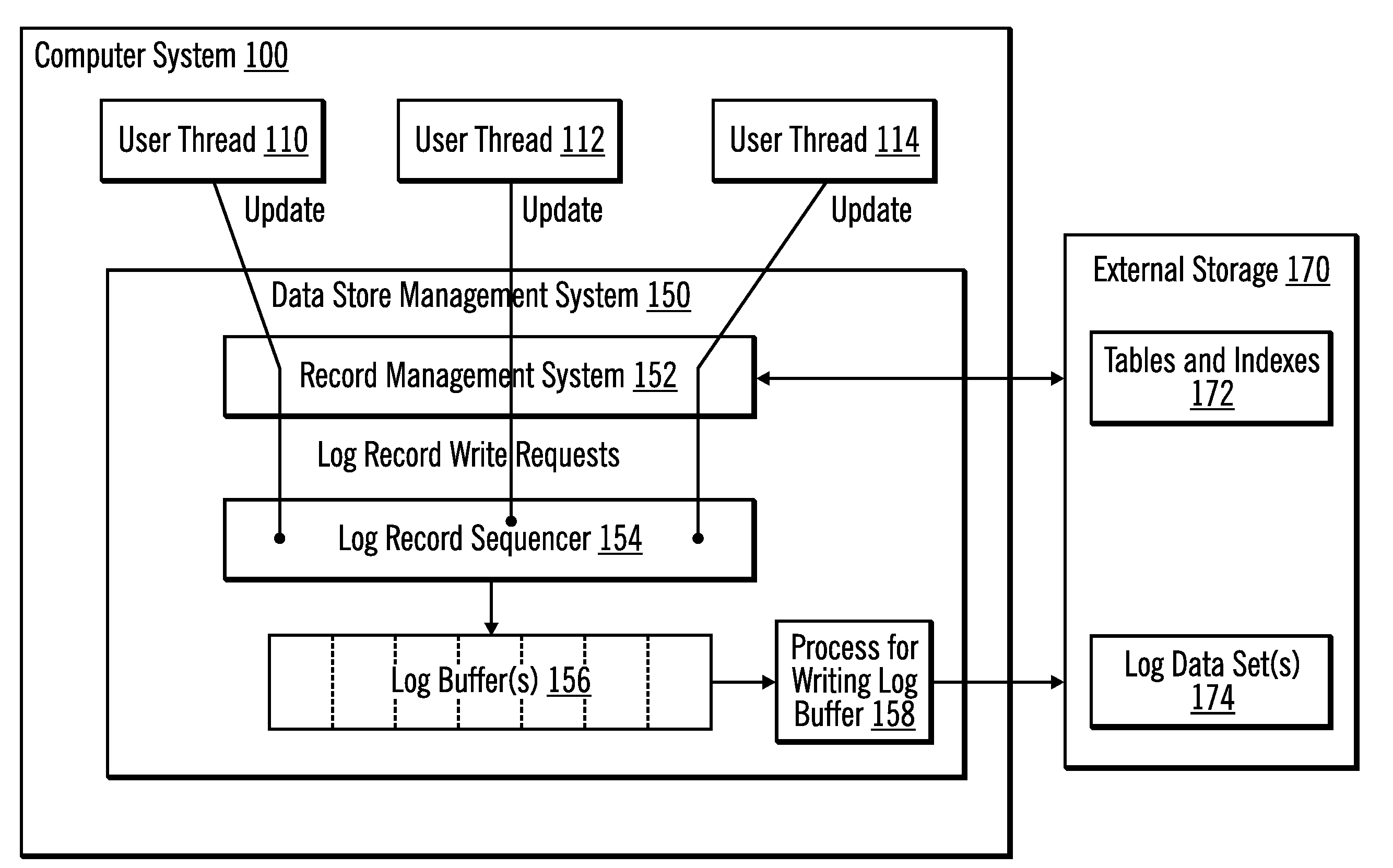

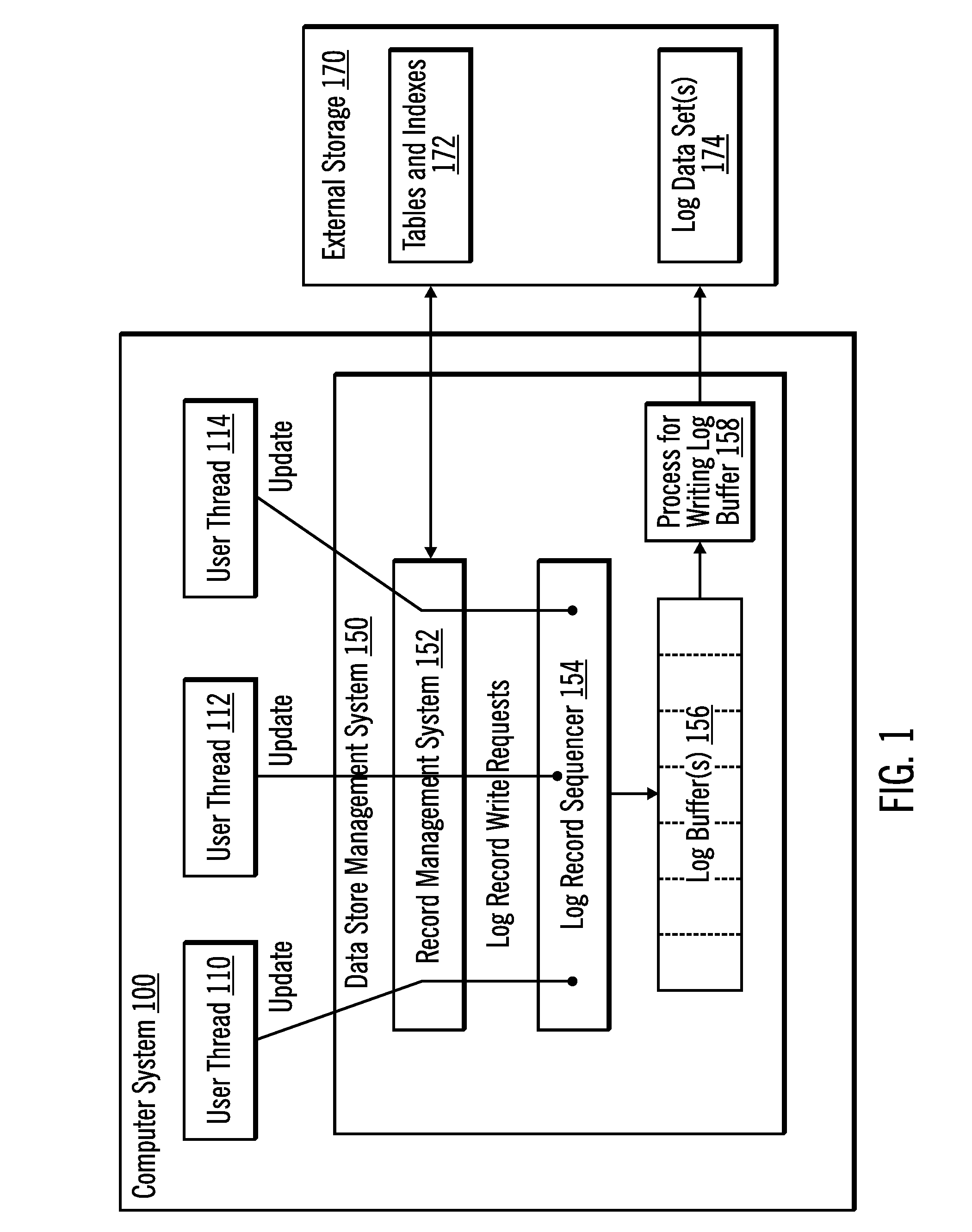

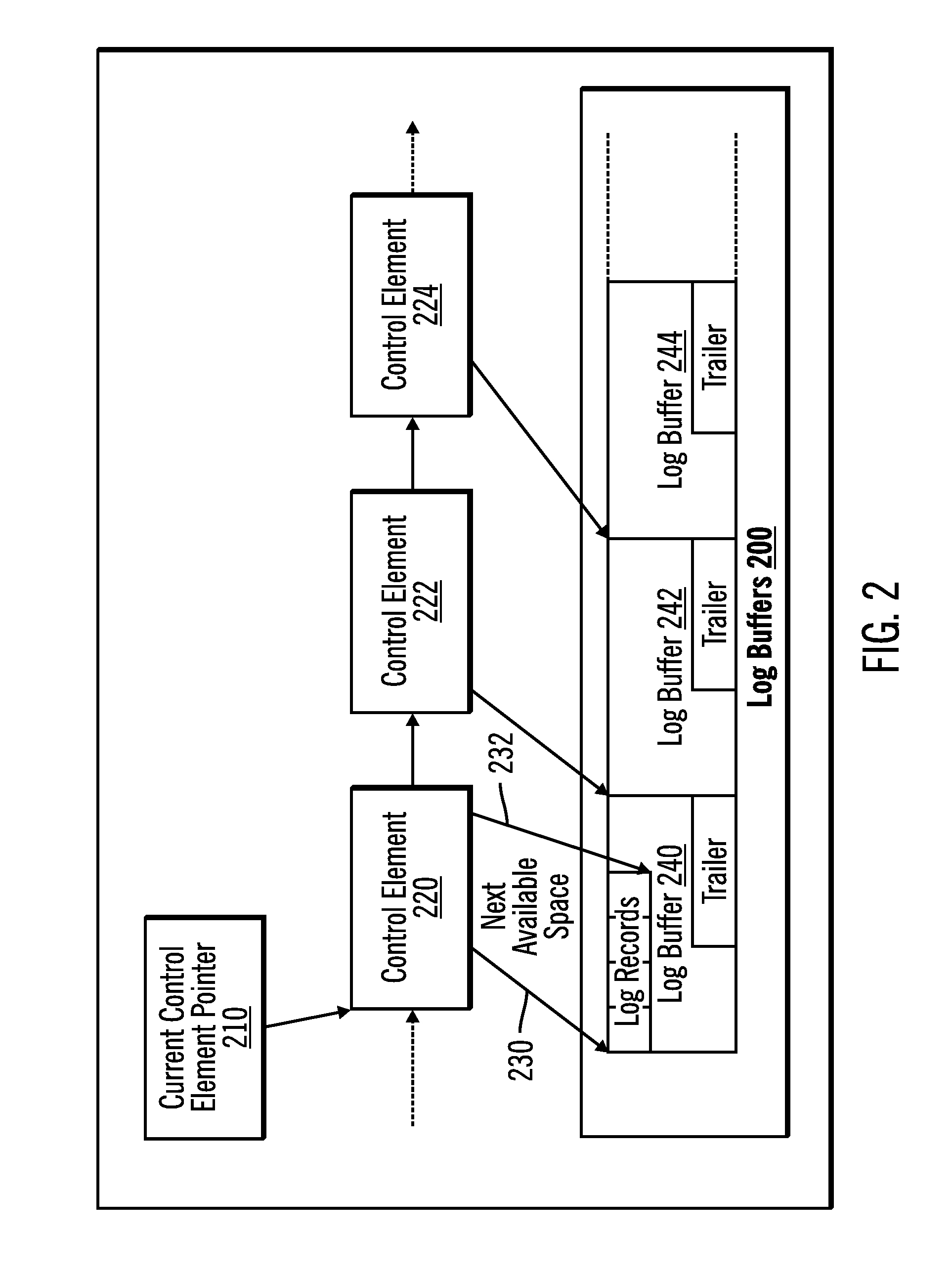

Creating and maintaining order of a log stream without use of a lock or latch

InactiveUS20120096055A1Digital data information retrievalSpecial data processing applicationsByte addressingByte

Provided are techniques for using a series of compare and swap operations to assign a Relative Byte Address (RBA) and a Logical Record Sequence Number (LRSN) to a log record. One or more log buffers for storing the log record are identified, and the log record is moved to the one or more log buffers.

Owner:IBM CORP

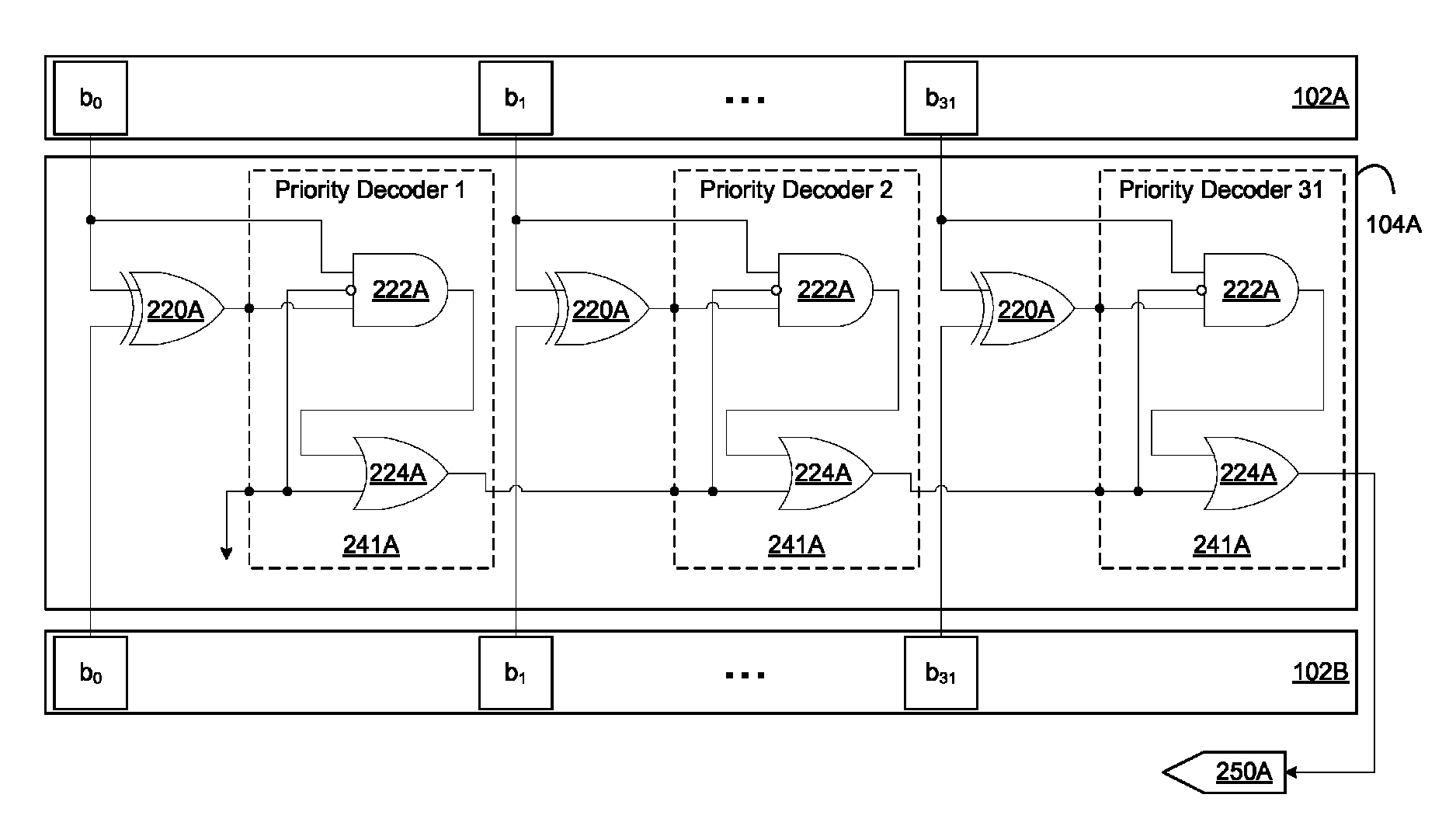

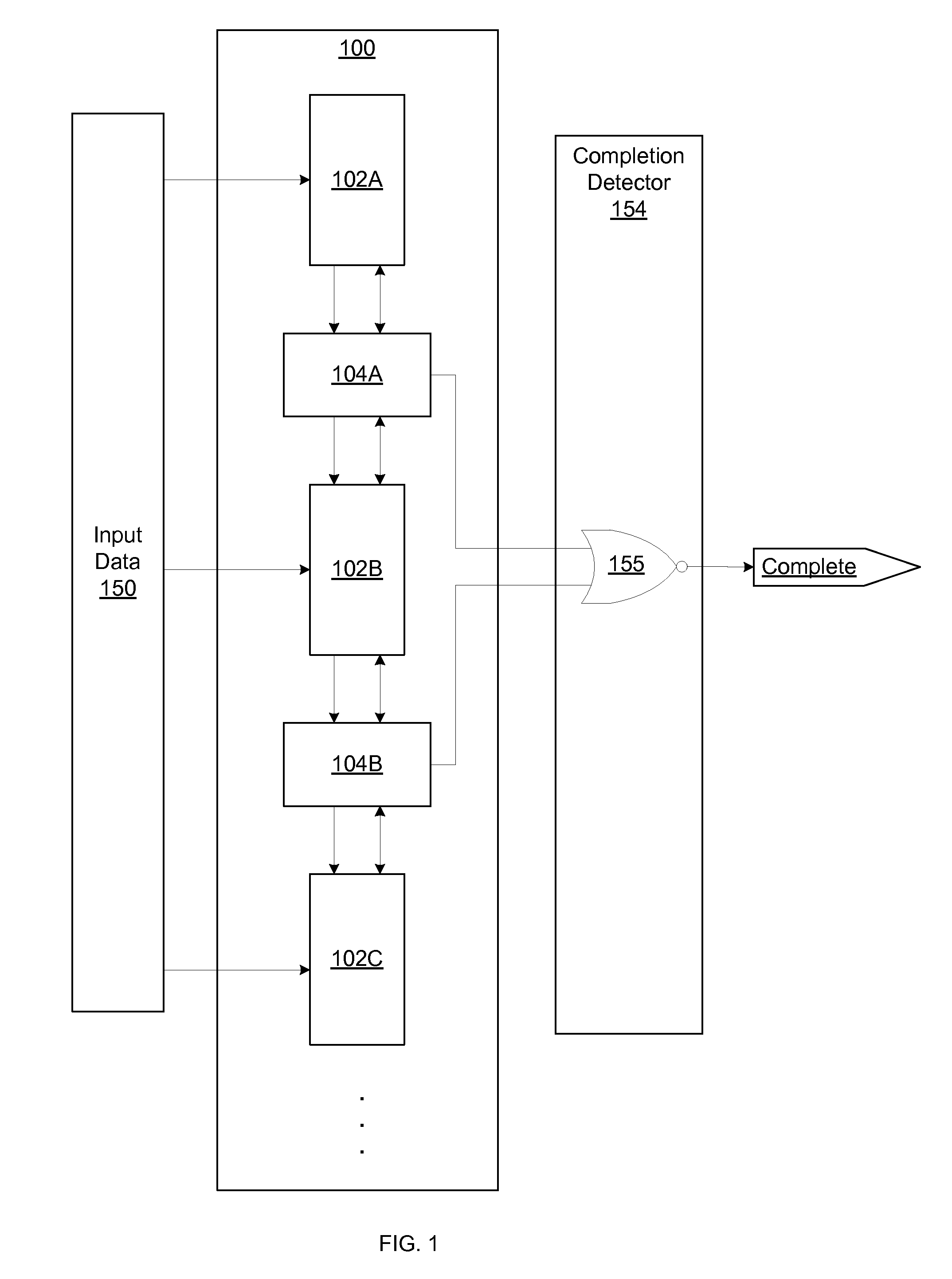

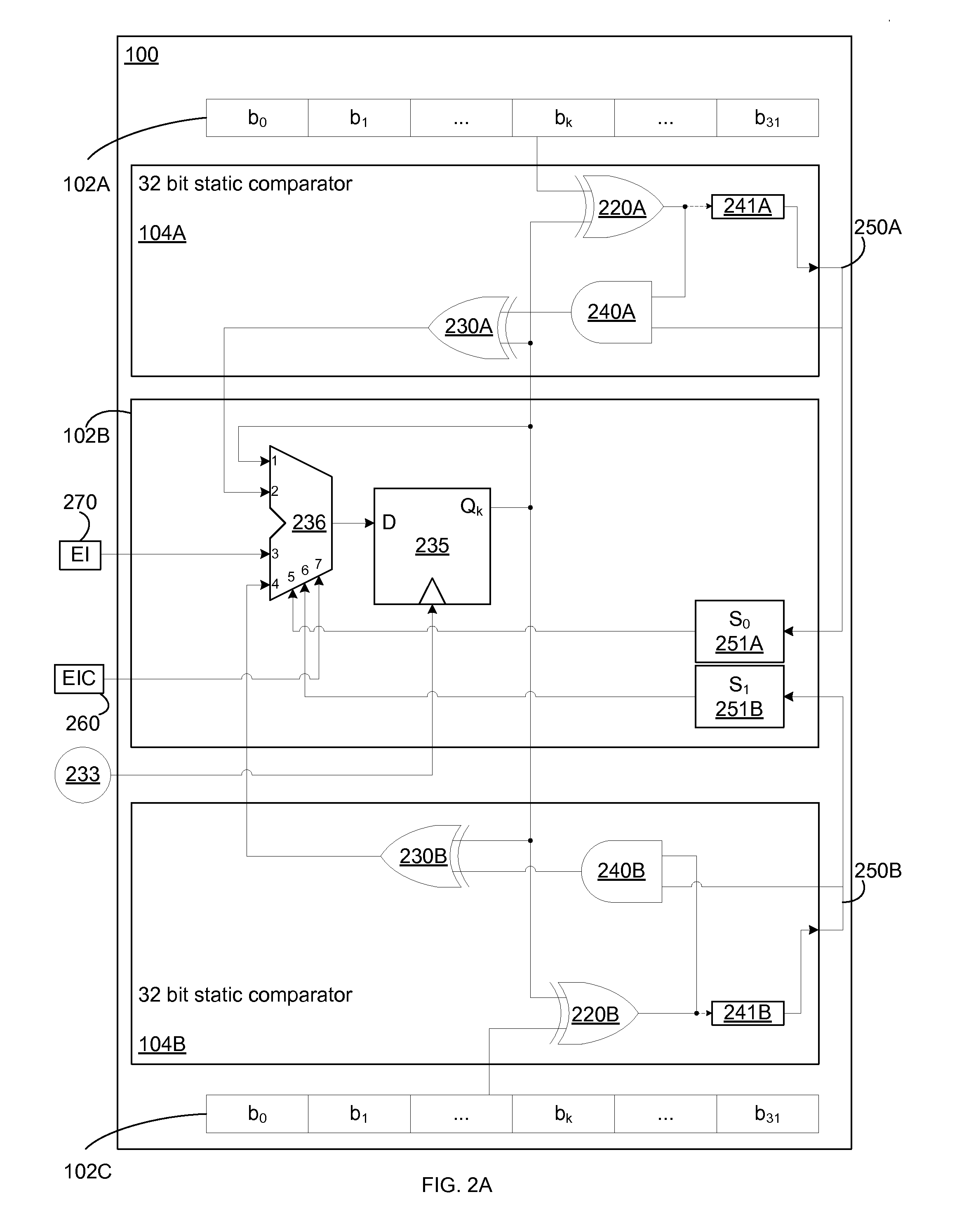

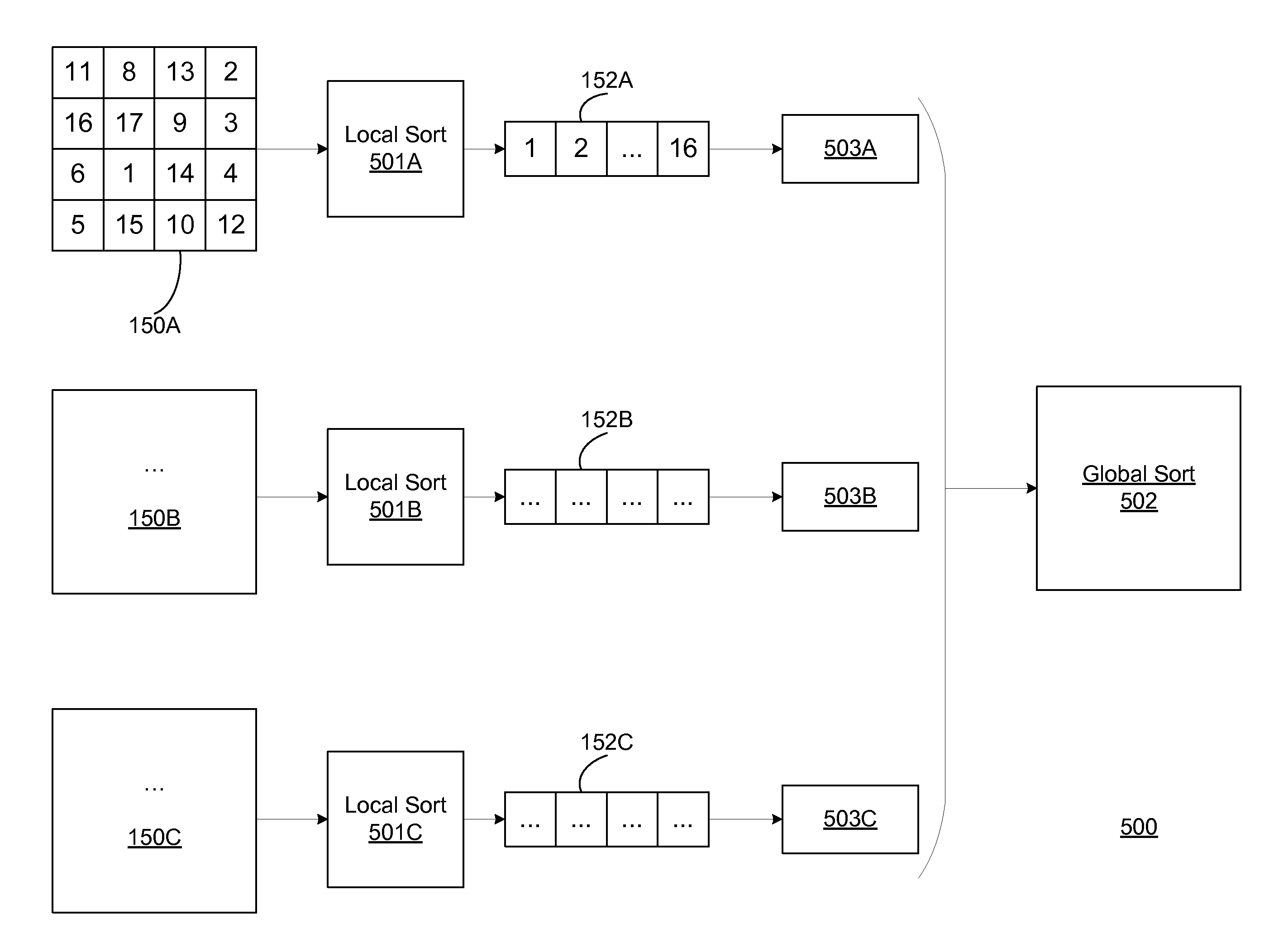

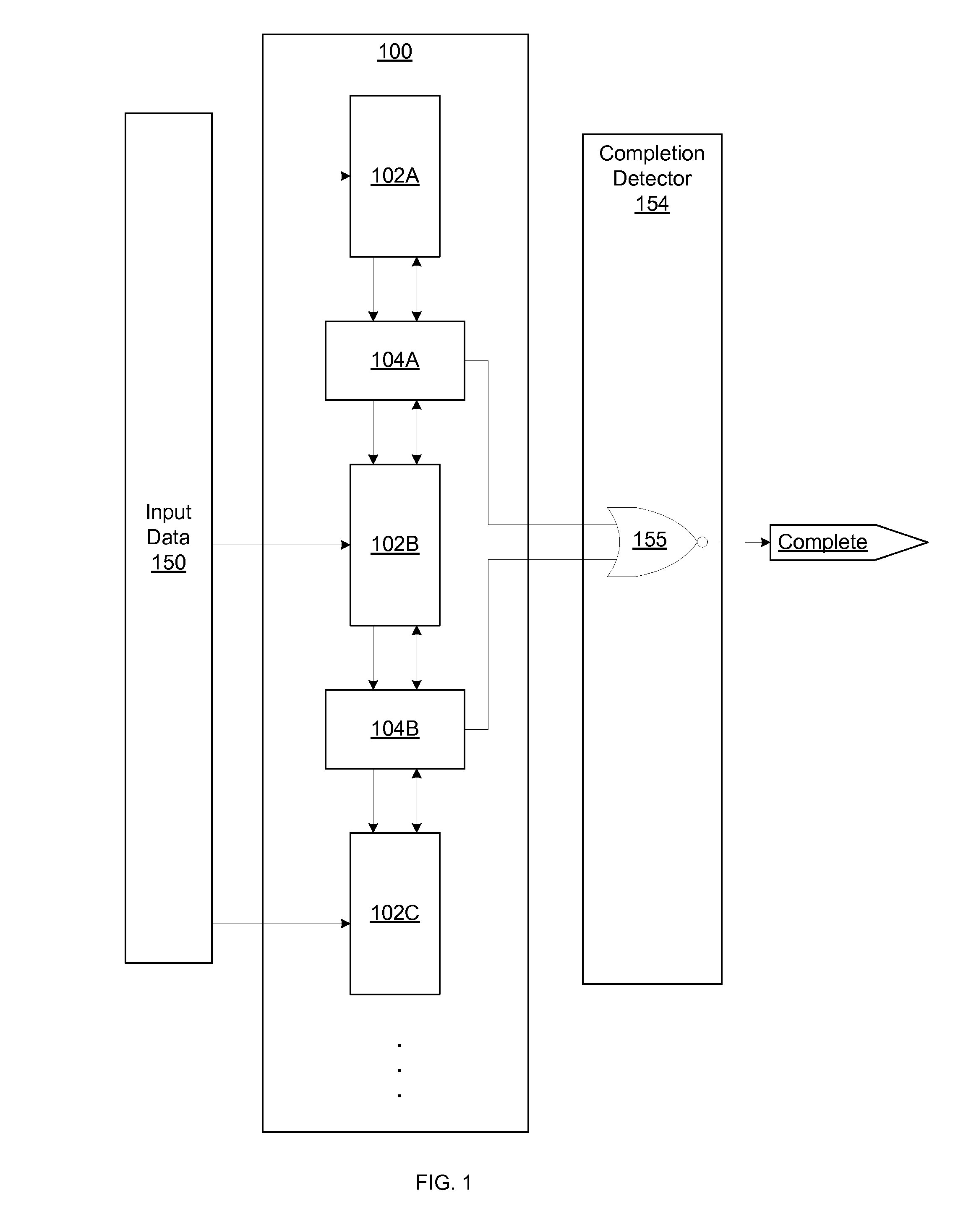

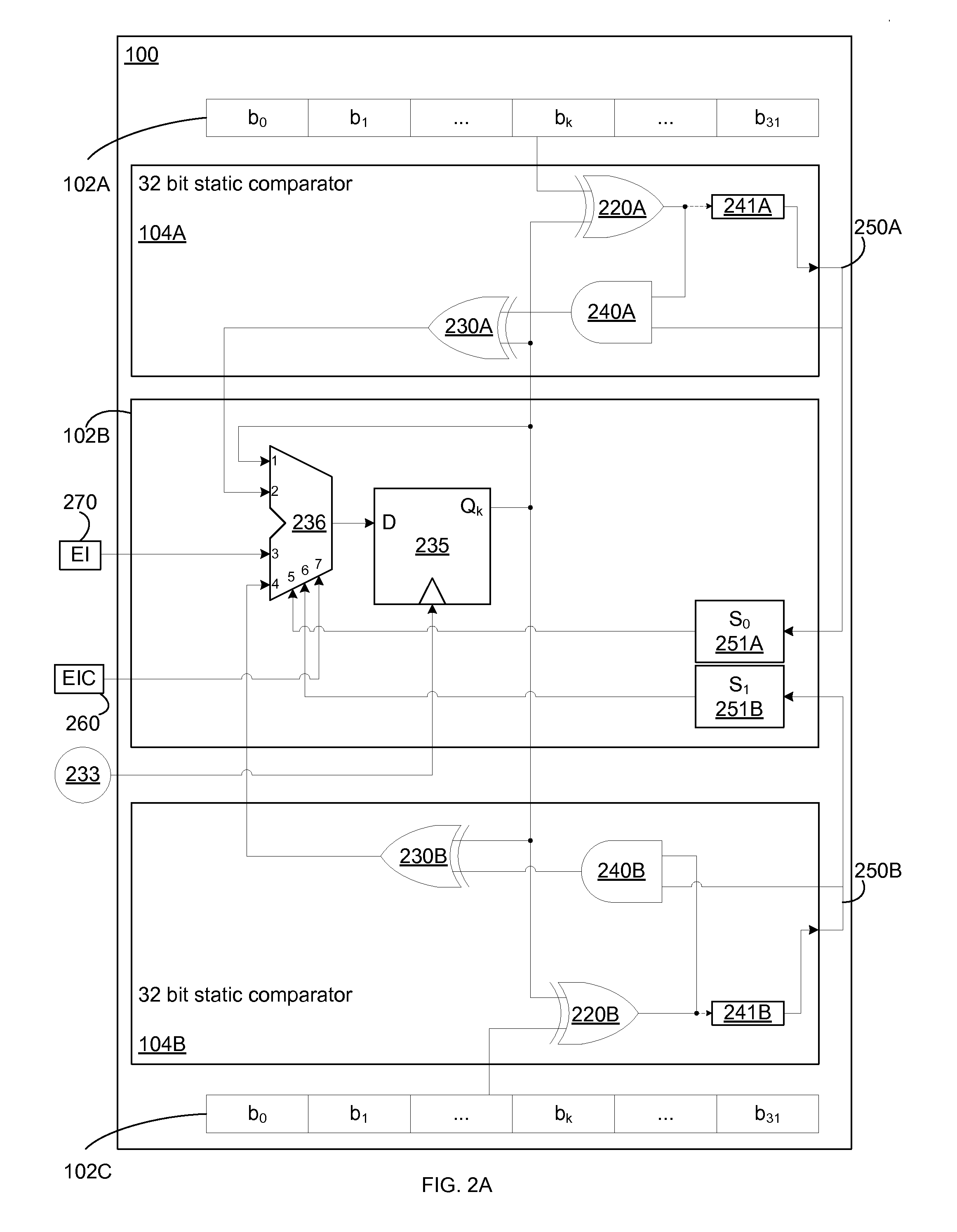

Hierarchical in-memory sort engine

InactiveUS9268863B2Increase speedLow costMemory architecture accessing/allocationMemory adressing/allocation/relocationSorting algorithmTournament sort

A local sorting module includes a set of storage elements storing binary vectors configured in a one-dimensional (1D) or two-dimensional (2D) array structure and separated by respective comparators configured to conditionally compare and sort the binary vectors. The comparators may perform a sort using a compare-and-flip or a compare-and-swap operation. Local sorting modules may be coupled with a global sorting module for enabling a tournament sort algorithm to output values stored in storage elements one at a time until all data is outputted in a predetermined sorting order.

Owner:IBM CORP

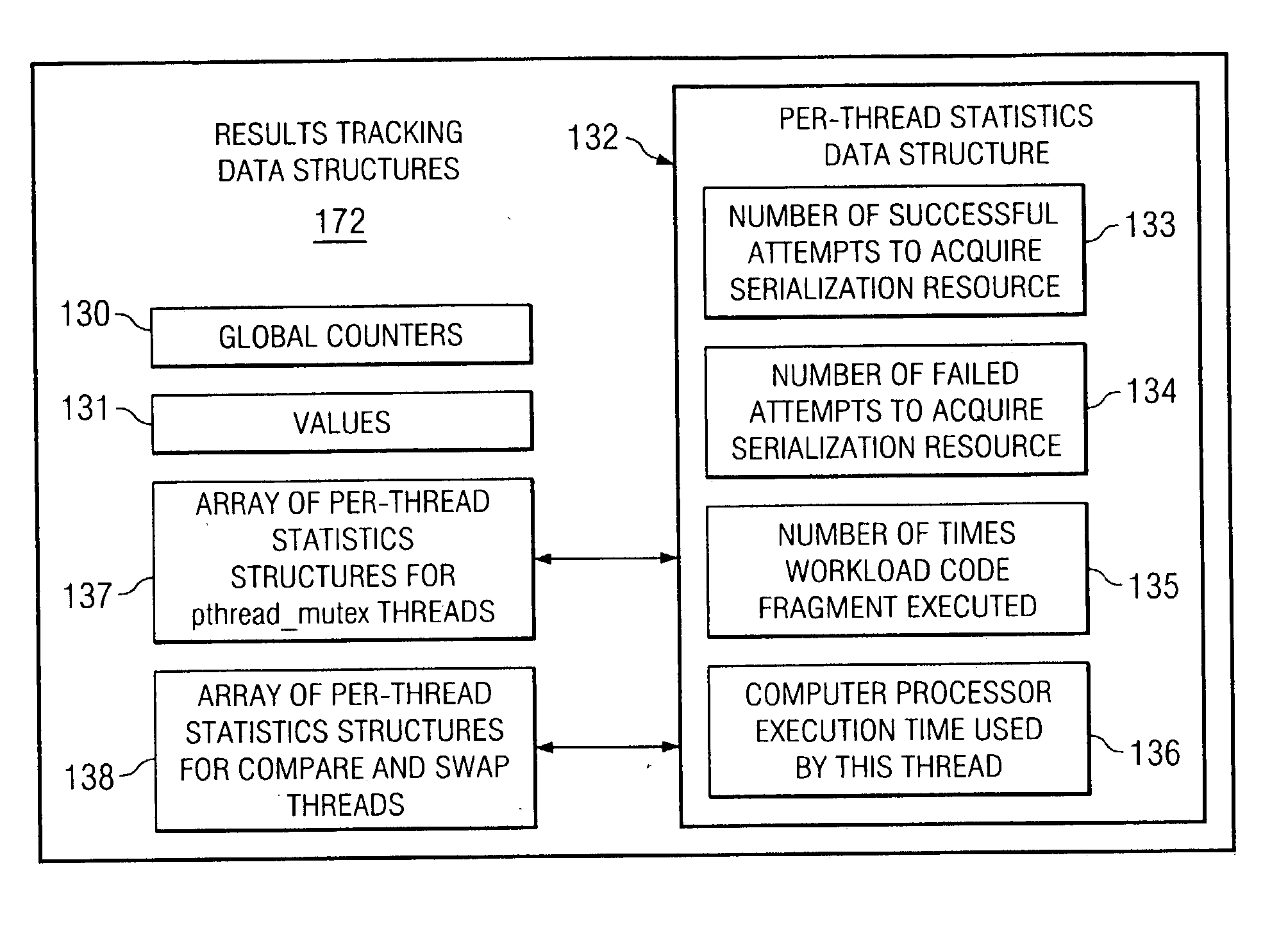

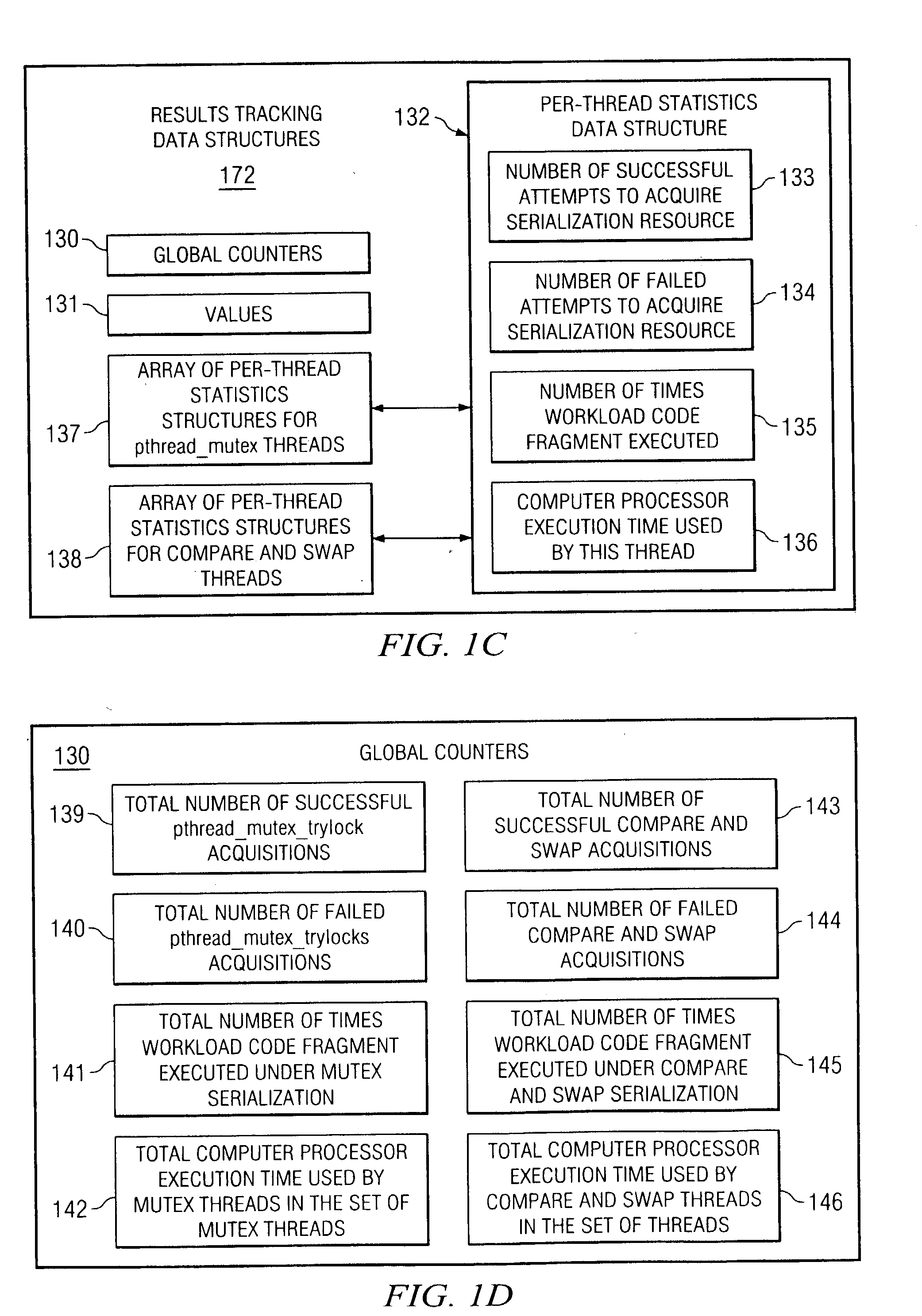

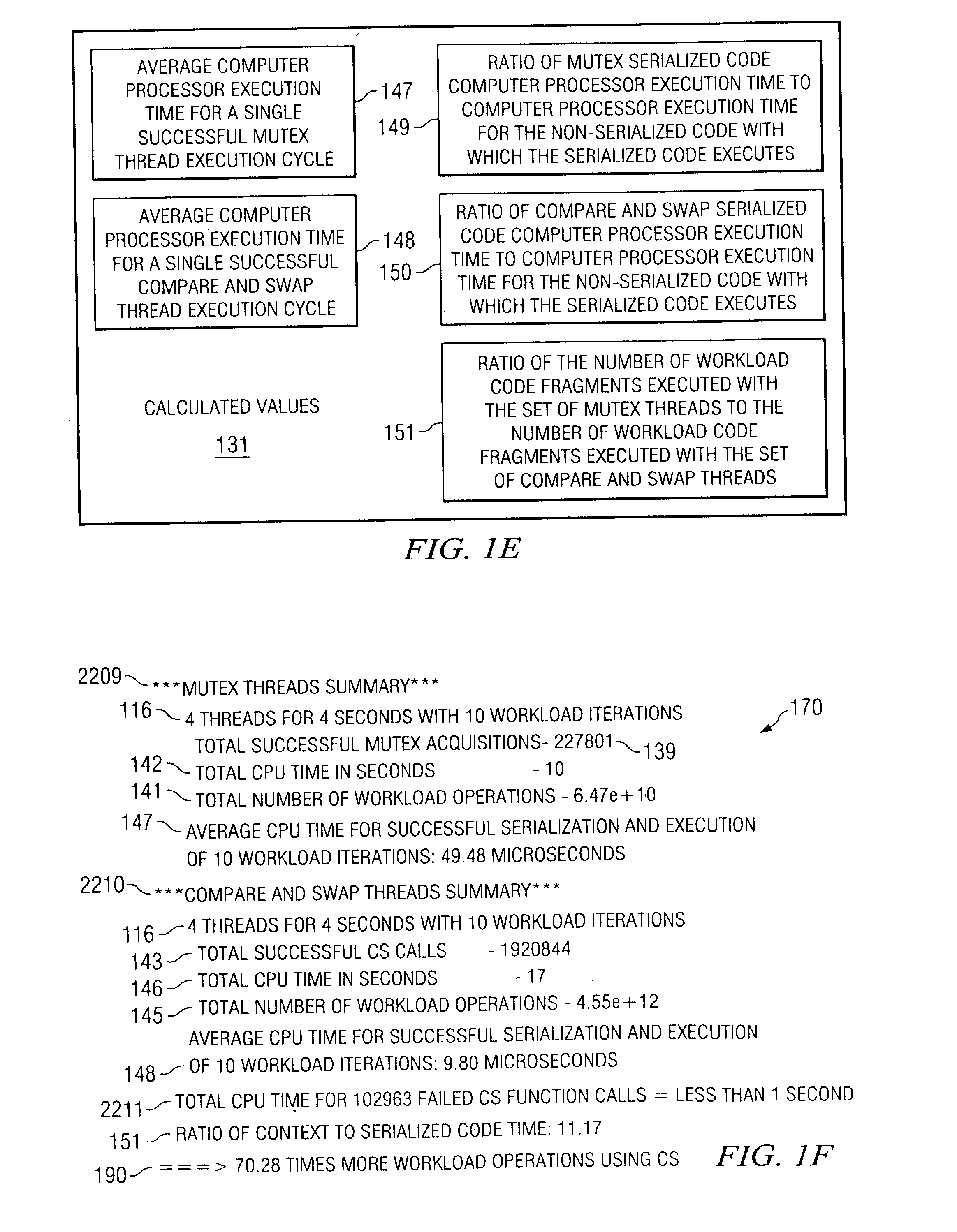

Systems, methods, and computer program products to optimize serialization when porting code to IBM S/390 UNIX system services from a UNIX system

InactiveUS20040103110A1Data processing applicationsDigital data processing detailsGeneral purposeUnix

Systems, methods, and computer products that determine how to optimize serialization code that has been ported from other computer systems to the OS / 390 UNIX system. General-purpose UNIX systems may not provide sufficient facilities; such as compiler run-time APIs like the Compare and Swap C Run-Time Library API, to accommodate the performance-related features of serialized code in complex applications. When porting a high-performance application from other UNIX platforms to IBM OS / 390 UNIX, serialized code performance of the application may be limited. The present invention may be implemented by advantageously determining when substitution of the Compare and Swap C Run-Time Library API calls for pthread_mutex calls will improve the execution of serialized code on the IBM OS / 390 UNIX system.

Owner:IBM CORP

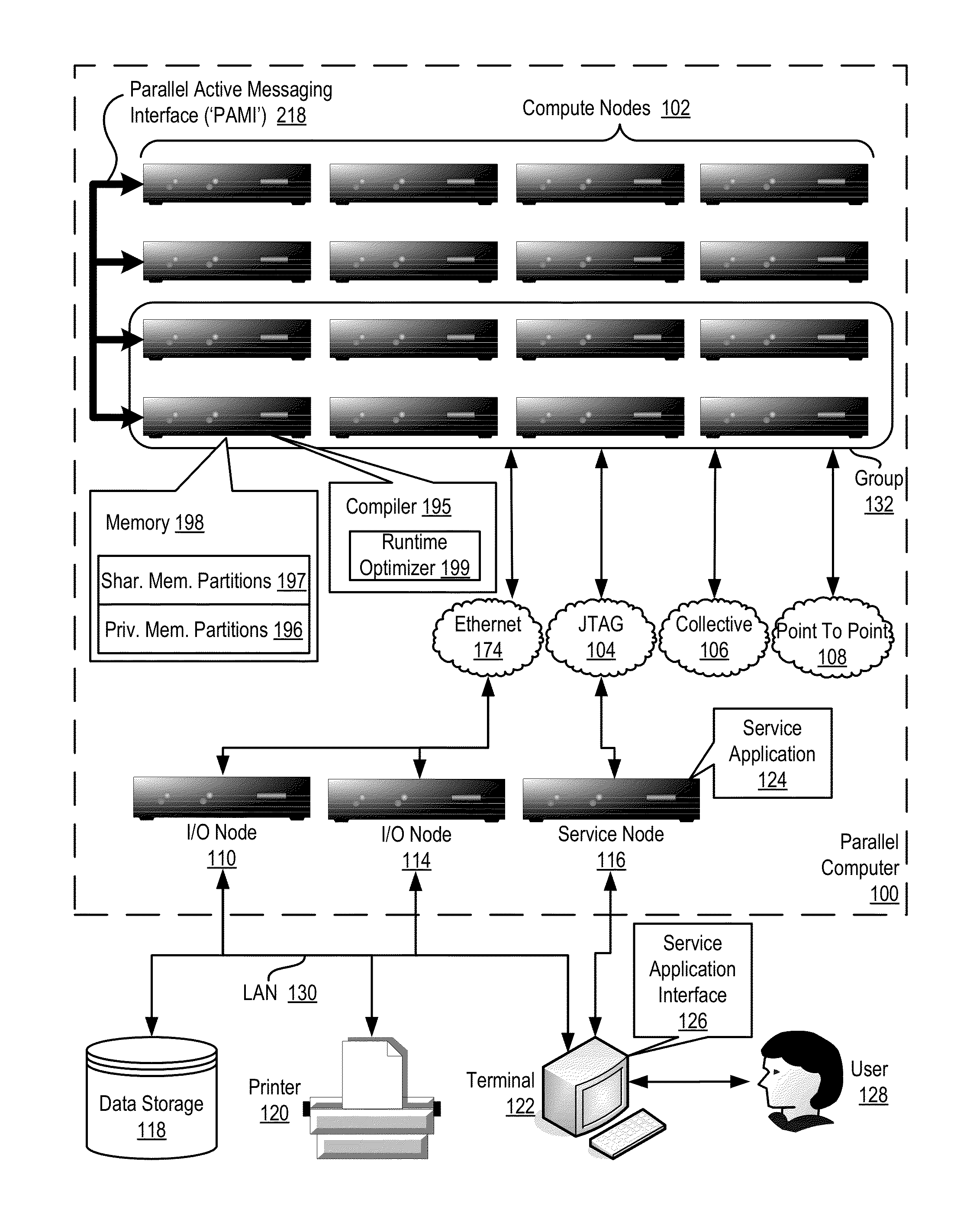

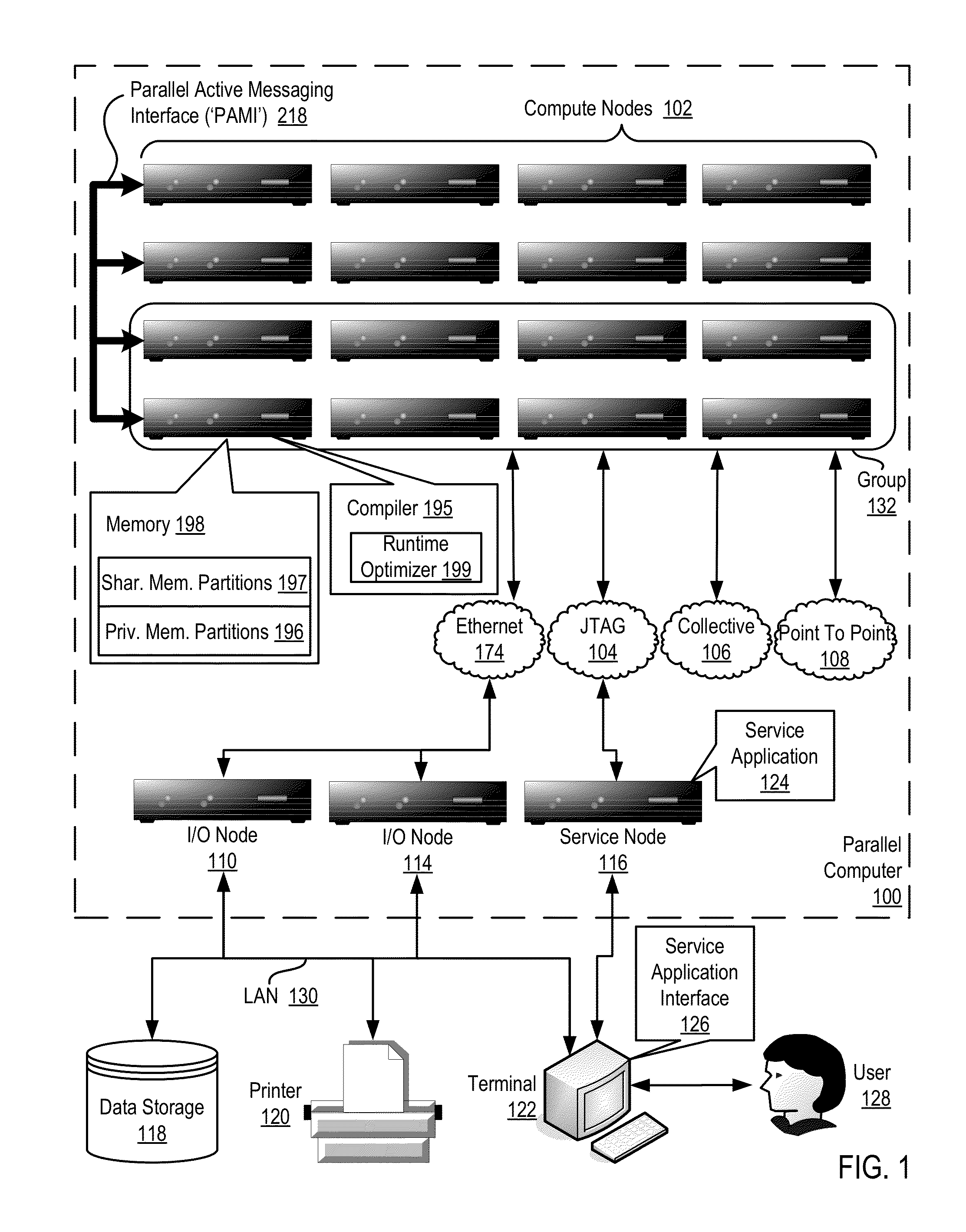

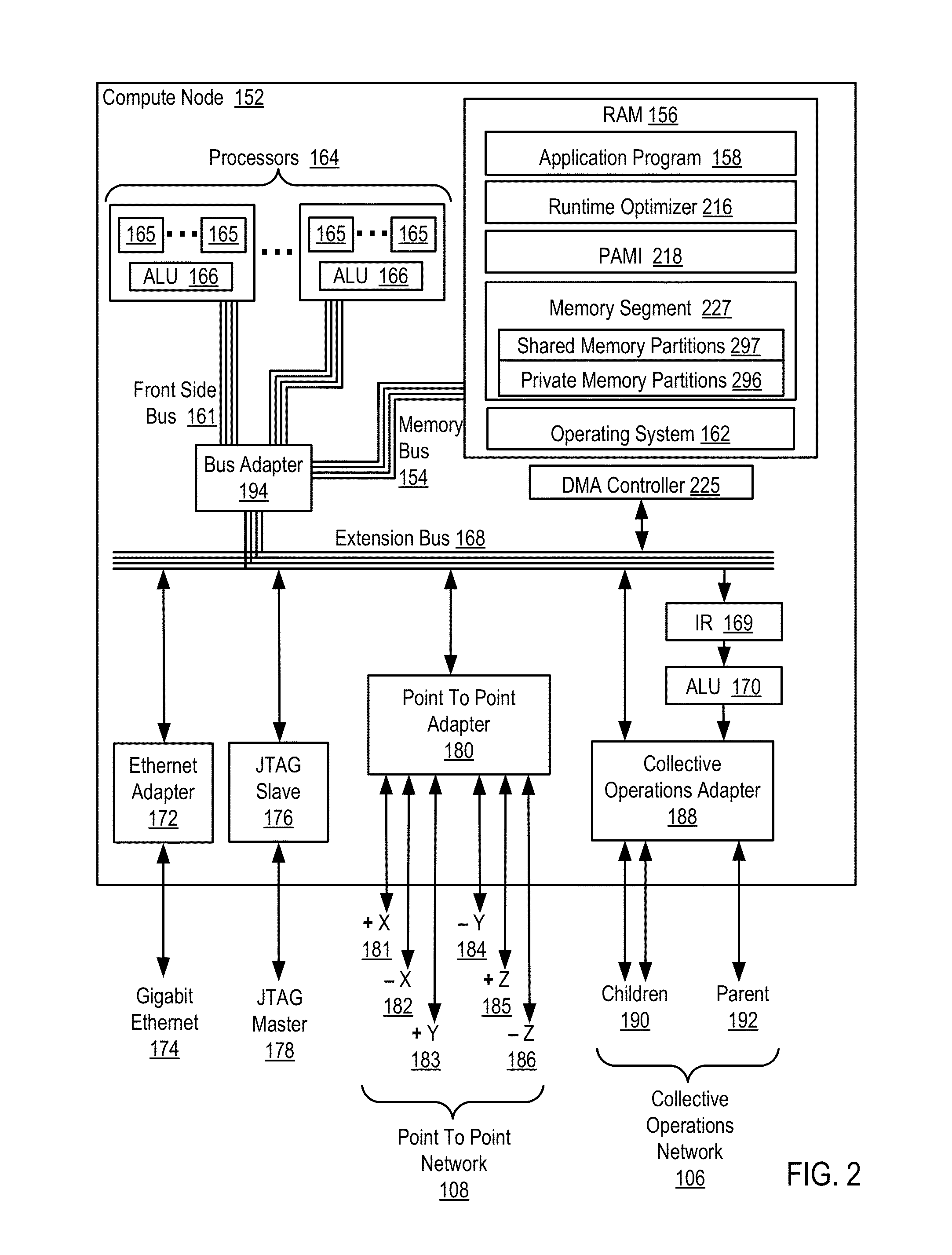

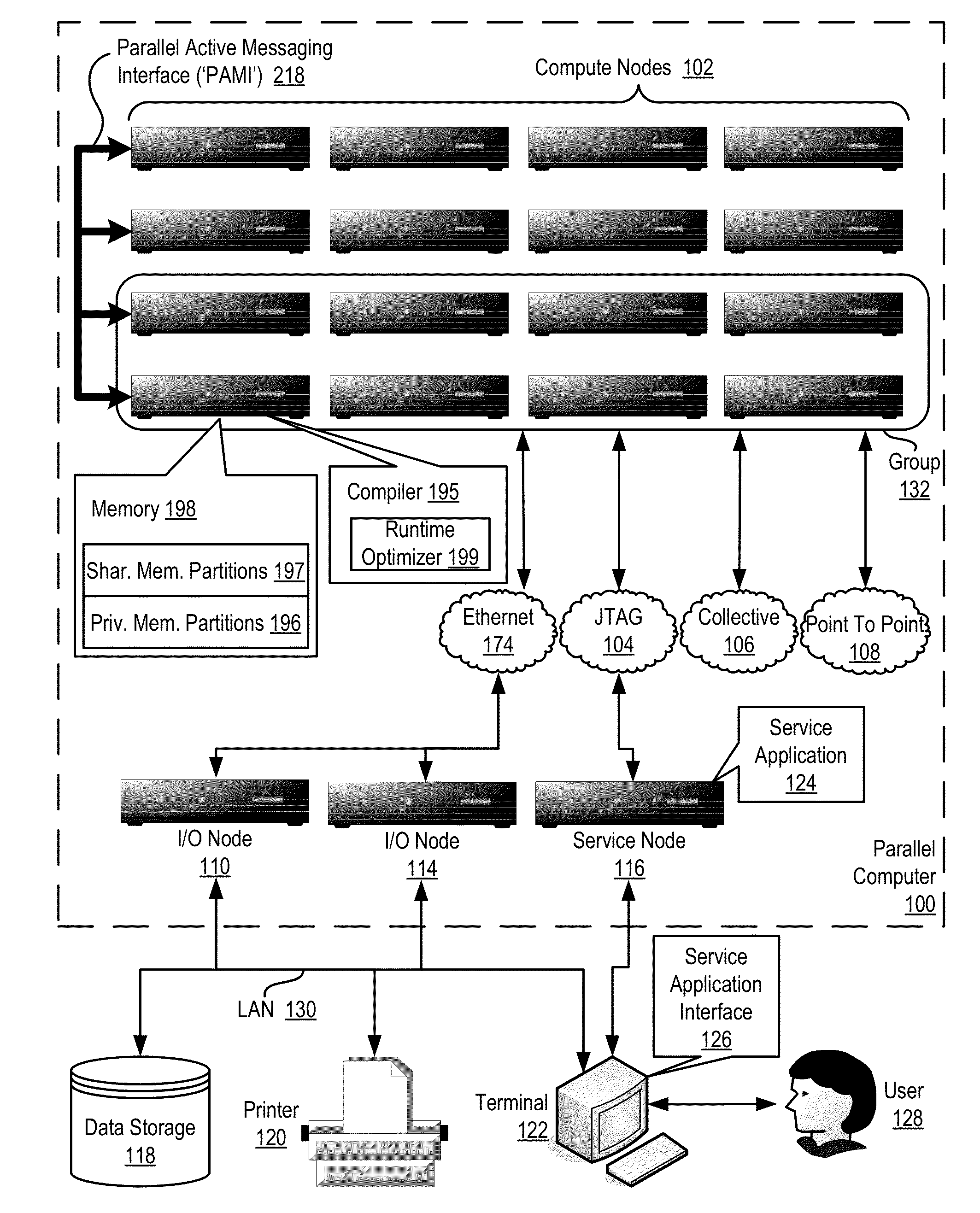

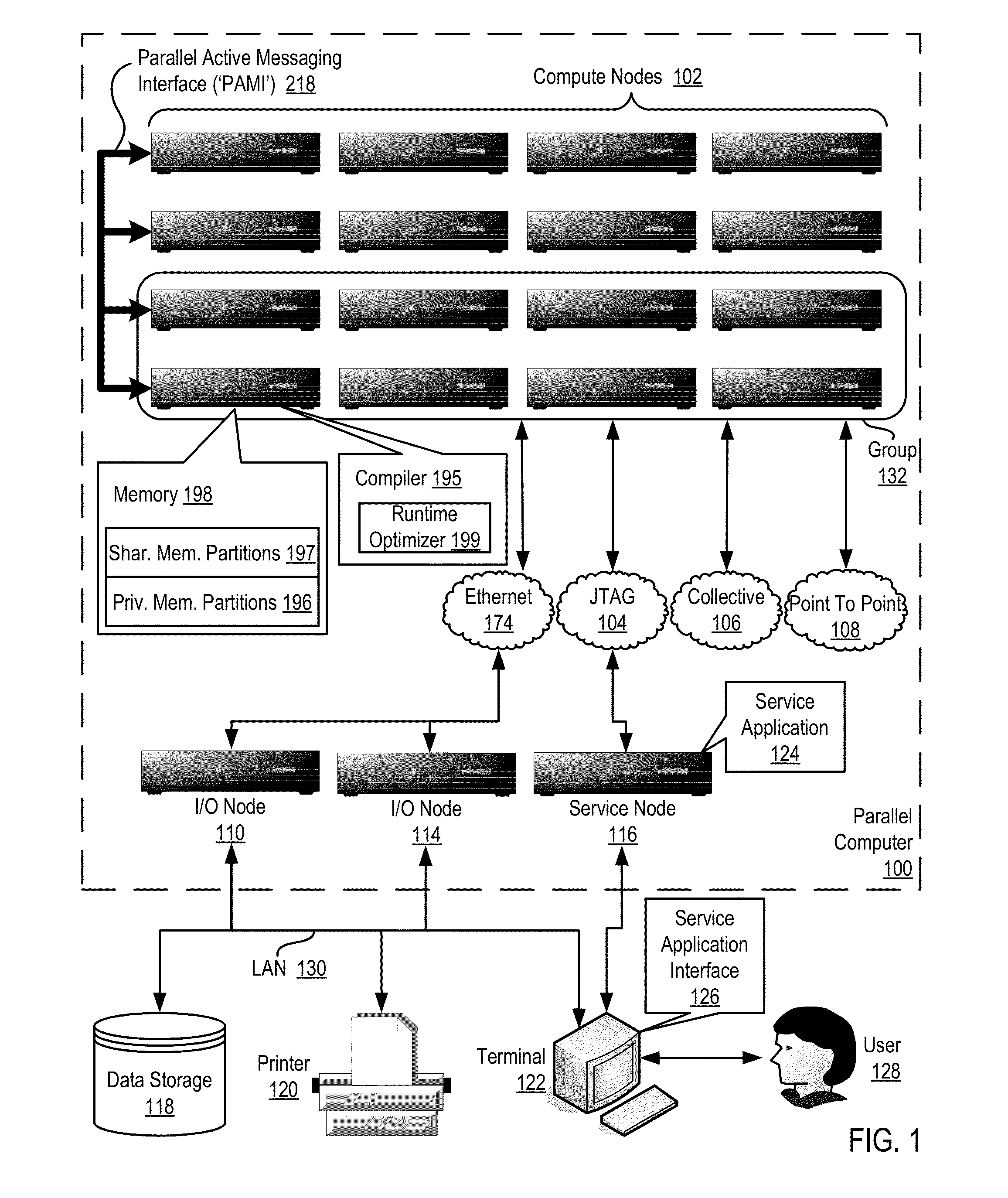

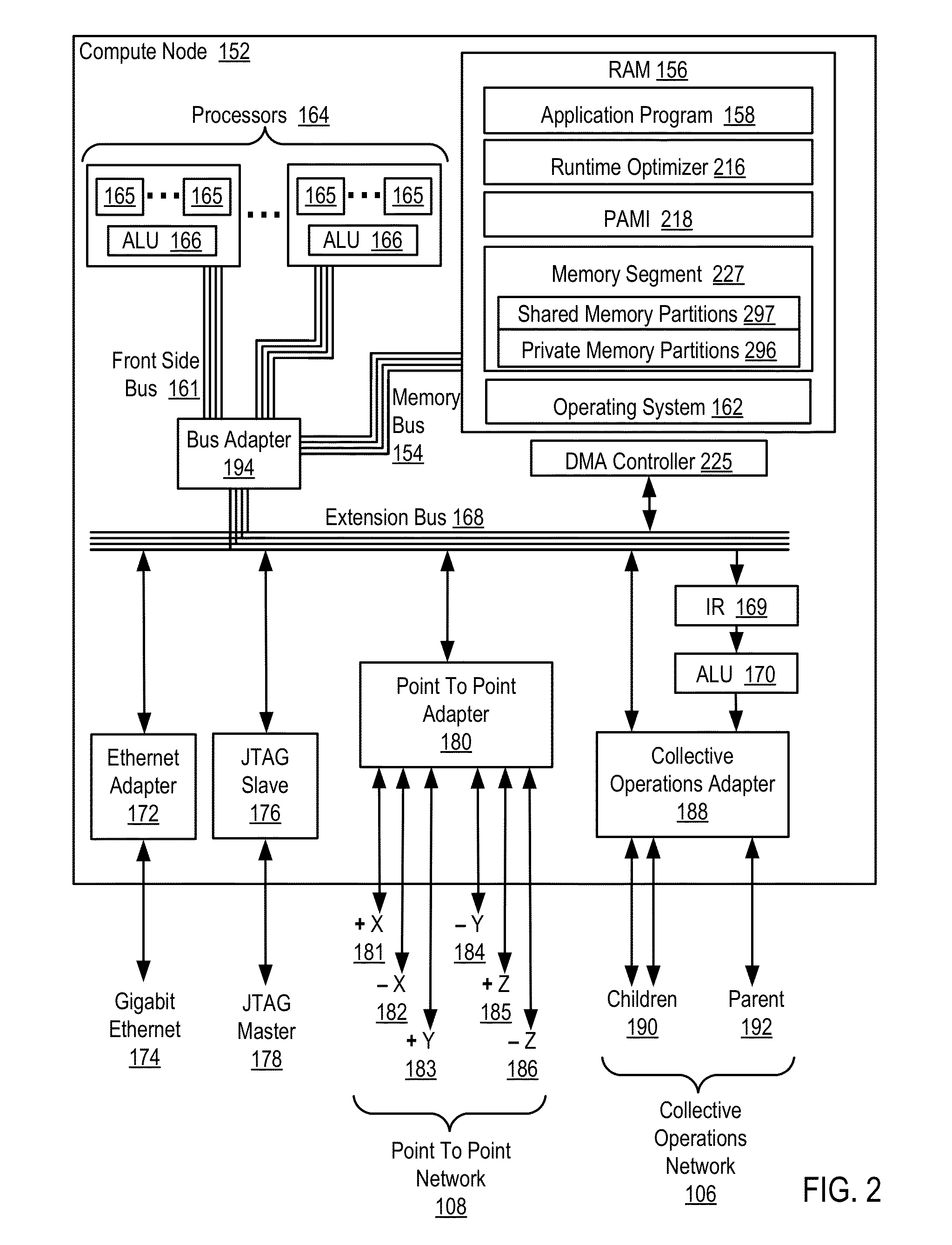

Analyzing update conditions for shared variable directory information in a parallel computer

InactiveUS20140173204A1Software engineeringMemory adressing/allocation/relocationParallel computingCompare-and-swap

Methods, parallel computers, and computer program products for analyzing update conditions for shared variable directory (SVD) information in a parallel computer are provided. Embodiments include a runtime optimizer receiving a compare-and-swap operation header. The compare-and-swap operation header includes an SVD key, a first SVD address, and an updated first SVD address. The first SVD address is associated with the SVD key in a first SVD associated with a first task. Embodiments also include the runtime optimizer retrieving from a remote address cache associated with the second task, a second SVD address indicating a location within a memory partition associated with the first SVD in response to receiving the compare-and-swap operation header. Embodiments also include the runtime optimizer determining whether the second SVD address matches the first SVD address and transmitting a result indicating whether the second SVD address matches the first SVD address.

Owner:IBM CORP

Hierarchical in-memory sort engine

InactiveUS20150347592A1Increase speedReduce overheadMemory architecture accessing/allocationMemory adressing/allocation/relocationSorting algorithmTournament sort

A local sorting module includes a set of storage elements storing binary vectors configured in a one-dimensional (1D) or two-dimensional (2D) array structure and separated by respective comparators configured to conditionally compare and sort the binary vectors. The comparators may perform a sort using a compare-and-flip or a compare-and-swap operation. Local sorting modules may be coupled with a global sorting module for enabling a tournament sort algorithm to output values stored in storage elements one at a time until all data is outputted in a predetermined sorting order.

Owner:IBM CORP

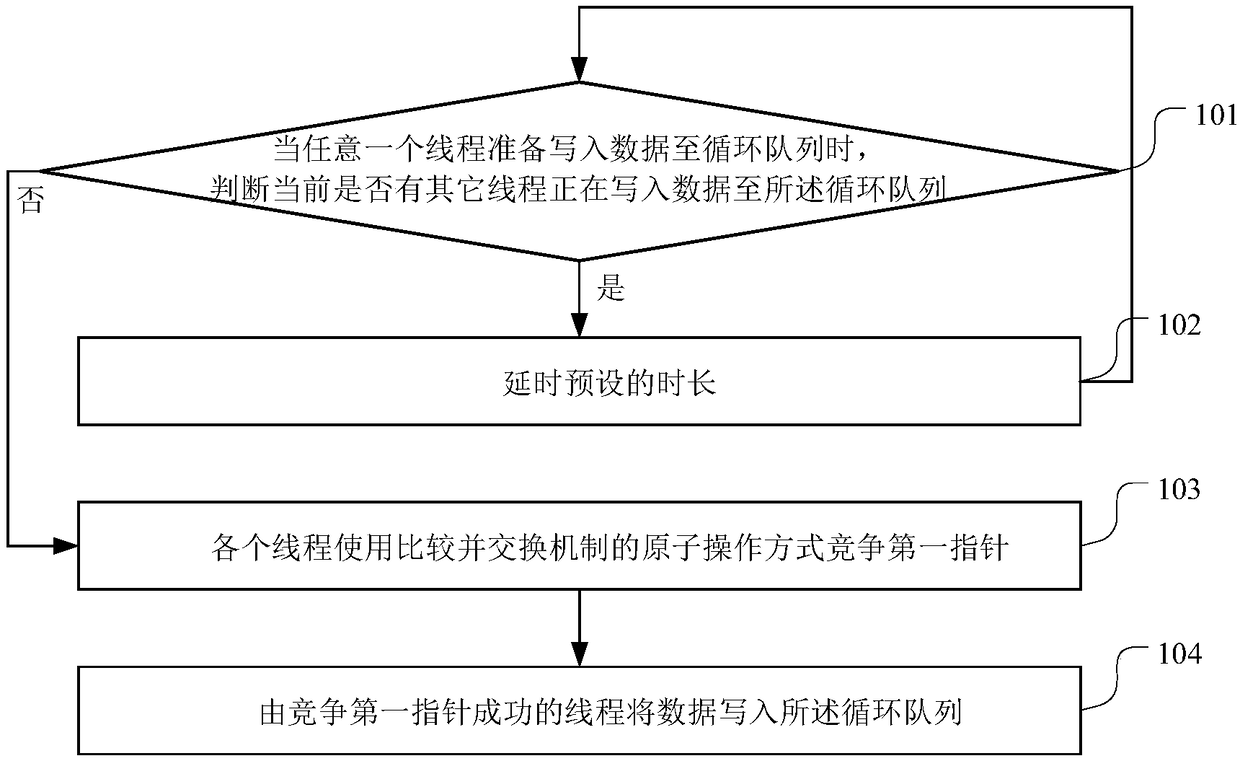

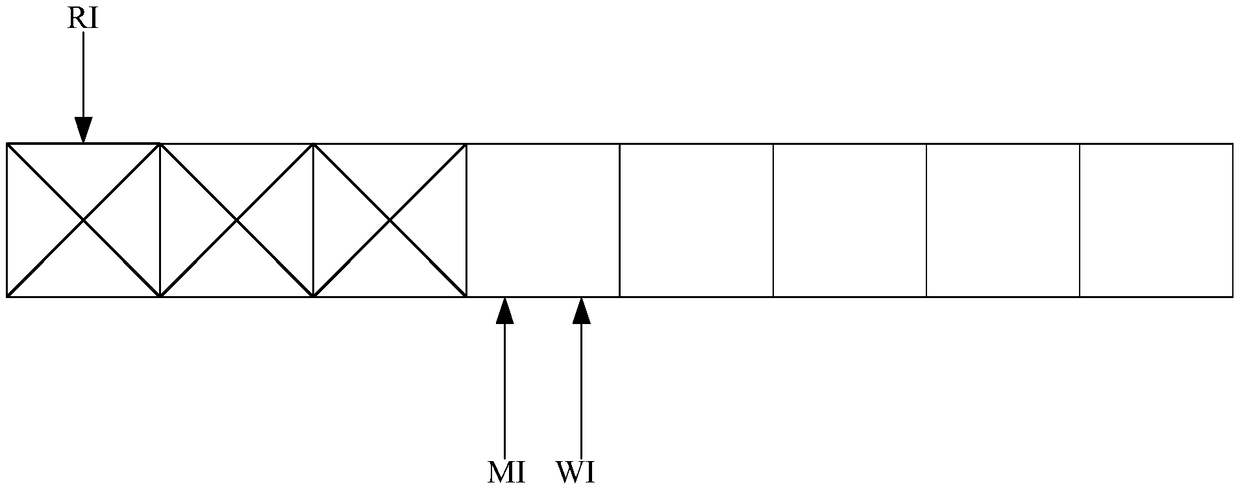

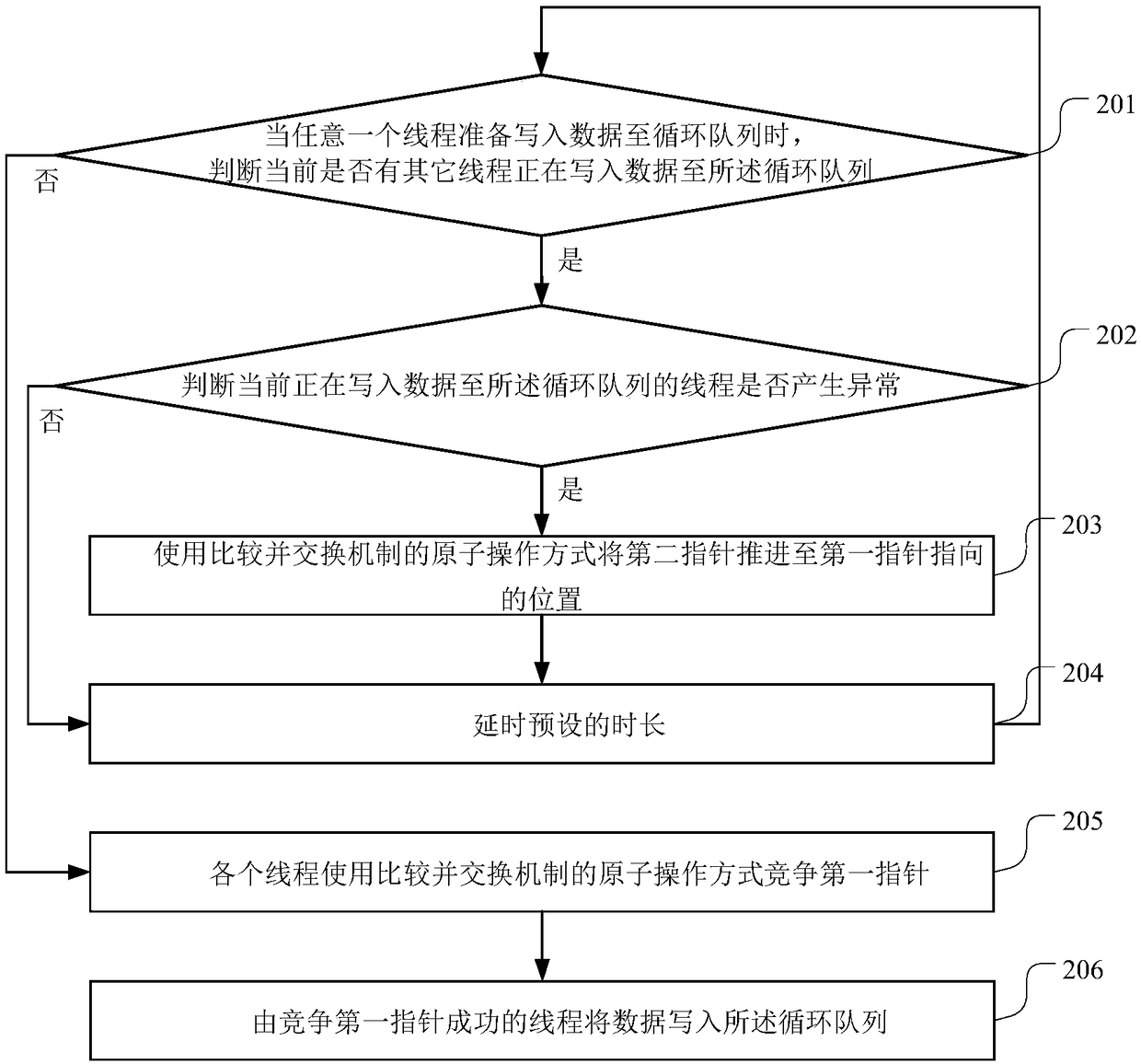

Data writing method, device, terminal device and computer storage medium of circular queue

ActiveCN108710531AImprove writing efficiencyProgram initiation/switchingInterprogram communicationTerminal equipmentComputer terminal

The invention relates to the technical field of data storage, and provides a data writing method, a device, a terminal device and a computer storage medium of a circular queue. The data writing methodcomprises the following steps: when any thread is ready to write data to a circulating queue, judging whether other threads are currently writing data to the circulating queue; If other threads are currently writing data to the circular queue, returning to the step of judging whether other threads are currently writing data to the circular queue and subsequent steps after the preset time length;If no other thread is currently writing data to the circular queue, each thread competing for a first pointer using atomic operation of a compare and swap mechanism, the first pointer pointing to thenext writable data location in the circular queue; and writing data to the circular queue by a thread that successfully competes for the first pointer. The method can effectively improve the data writing efficiency of the circulating queue.

Owner:SHENZHEN EXCELSECU DATA TECH

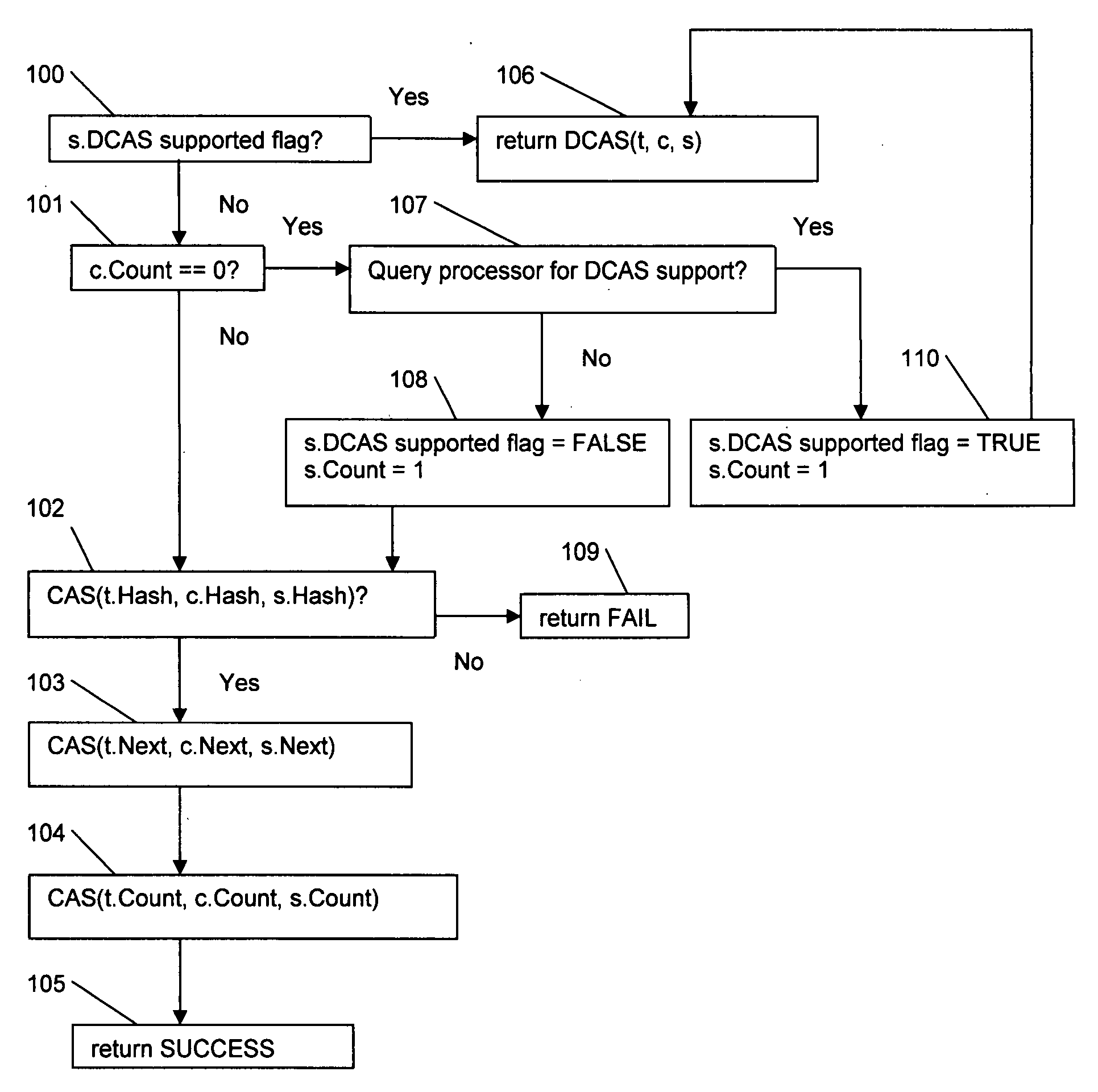

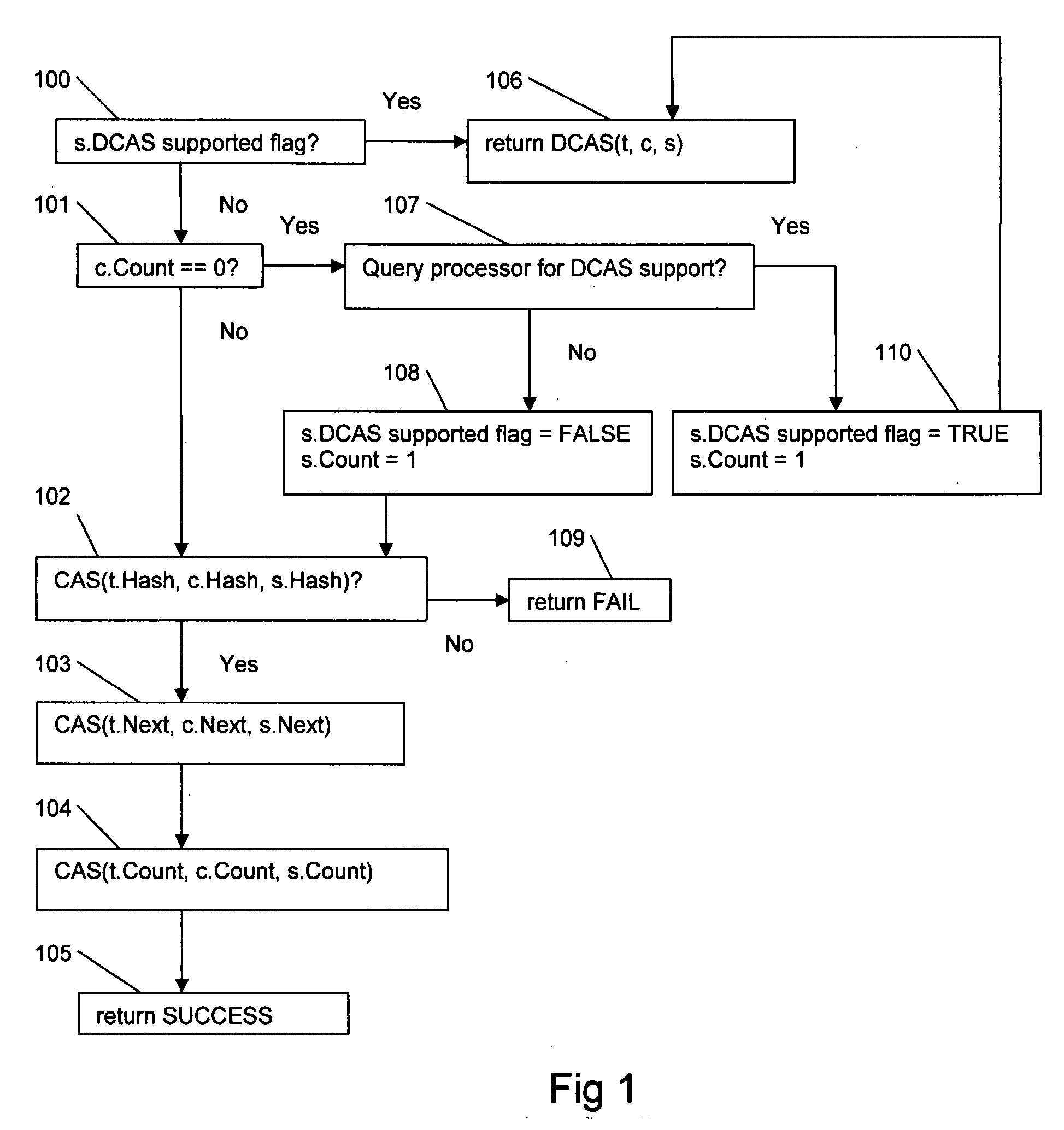

Double word compare and swap implemented by using triple single word compare and swap

InactiveUS20080228784A1Runtime instruction translationSpecial data processing applicationsComputer scienceSerial code

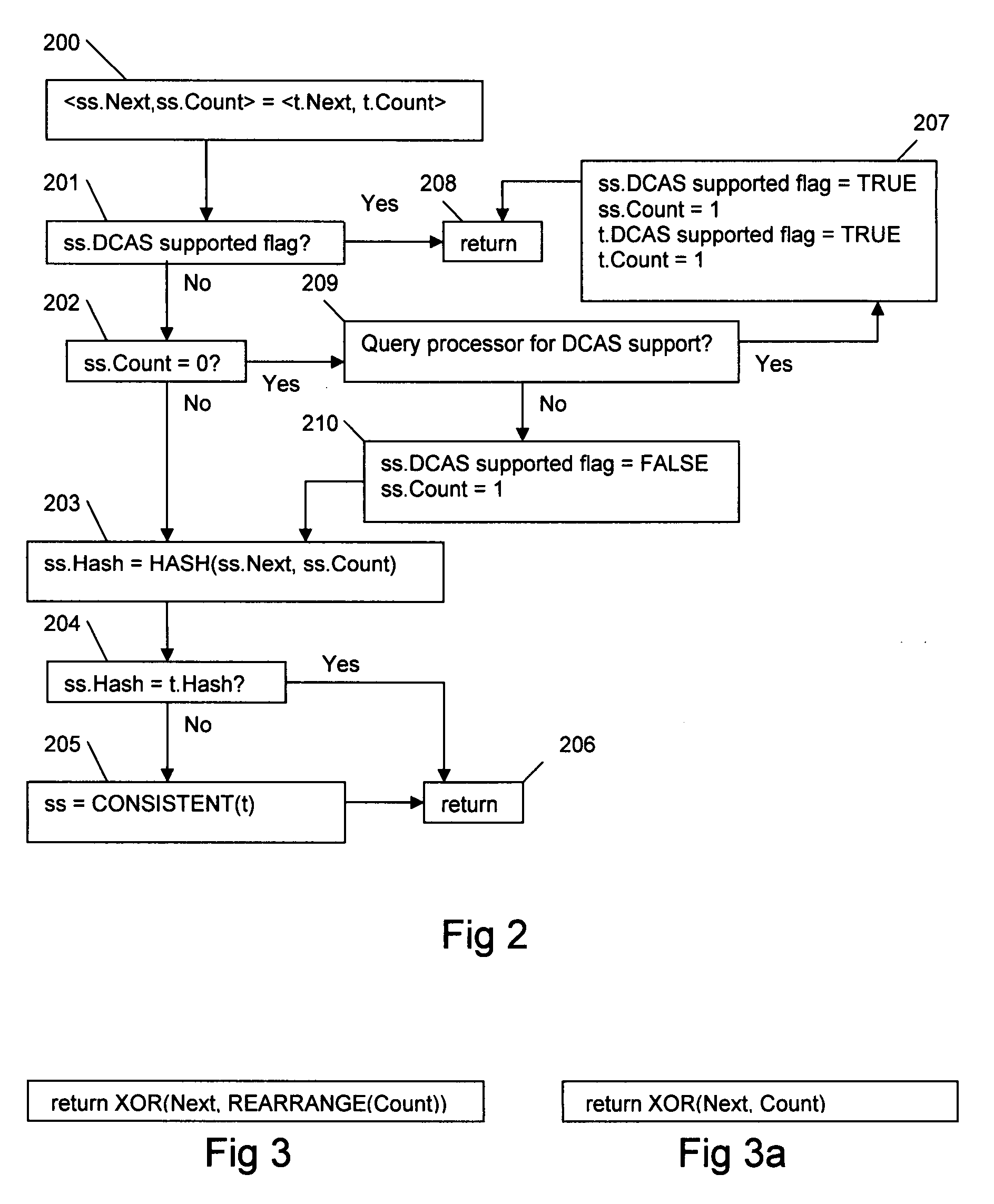

A Lock Free and Wait Free method of the appearance of an atomic double word compare and swap (DCAS) operation on a pointer and ABA avoidance sequence number pair of words while using atomic single word compare and swap (CAS) instructions. To perform this function an area of memory is used by this invention and described as a protected pointer. The protected pointer consists of three words, comprising of: a) a pointer to a memory location, such as a node in linked list, together with b) an ABA avoidance sequence number, and combined together with a third word containing c) a specially crafted hash code derived from the pointer and the ABA avoidance sequence number. The three words together are referred to as a three word protected pointer and are used by this invention for implementing a Lock-Free and Wait-Free method of simulating DCAS using three CAS instructions. The specially crafted hash code, when used in a manner as described in this invention, enable competing threads in a multithreaded environment to advance a partially completed method of the appearance of an atomic double word compare and swap (DCAS) operation on a pointer and ABA avoidance sequence number pair of words while using atomic single word compare and swap (CAS) instructions as partially executed by a different thread. The ability for any thread to complete a partially completed appearance of DCAS provides for wait free operation.

Owner:DEMPSEY JAMES G

Equipment IO queue method based on atomic operation

ActiveCN104615445ASpeed up input and outputSave resourcesSpecific program execution arrangementsControl powerComputer science

The invention relates to an equipment IO queue method based on atomic operation. A queue is composed of an owner pointer, a tail pointer, data nodes and temporary nodes. The enqueue operation can be simultaneously carried out by a plurality of producers, and the dequeue operation can only be carried out by a consumer. The dequeue operation needs one temporary node to participate, and the first data node in the queue is replaced and taken out. In the process, the atomic compare-and-swap (CAS) operation is used to judge whether the tail pointer points to the first data node or not; if yes, the tail pointer points to the temporary node. The queue further comprises control power releasing operation, and the control power releasing operation is as follows: the first node is removed, and the atomic compare-and-swap (CAS) operation is used to judge whether the tail pointer points to the first node or not; if yes, the tail pointer is changed to a null pointer; if the first node is removed, so that the queue is emptied, the control power is released.

Owner:CHANGSHA XINHONG SOFTWARE

Concurrent, non-blocking, lock-free queue and method, apparatus, and computer program product for implementing same

InactiveUS7802032B2Reduce overheadProgram control using stored programsTransmissionLoad-link/store-conditionalFifo queue

A dummy node is enqueued to a concurrent, non-blocking, lock-free FIFO queue only when necessary to prevent the queue from becoming empty. The dummy node is only enqueued during a dequeue operation and only when the queue contains a single user node during the dequeue operation. This reduces overhead relative to conventional mechanisms that always keep a dummy node in the queue. User nodes are enqueued directly to the queue and can be immediately dequeued on-demand by any thread. Preferably, the enqueueing and dequeueing operations include the use of load-linked / store conditional (LL / SC) synchronization primitives. This solves the ABA problem without requiring the use a unique number, such as a queue-specific number, and contrasts with conventional mechanisms that include the use of compare-and-swap (CAS) synchronization primitives and address the ABA problem through the use of a unique number. In addition, storage ordering fences are preferably inserted to allow the algorithm to run on weakly consistent processors.

Owner:INT BUSINESS MASCH CORP

Efficient Non-Blocking K-Compare-Single-Swap Operation

ActiveUS20080034166A1Simple nonblocking manipulationEfficient and flexible nonblocking manipulationData processing applicationsProgram synchronisationTheoretical computer scienceLoad-link/store-conditional

Owner:ORACLE INT CORP

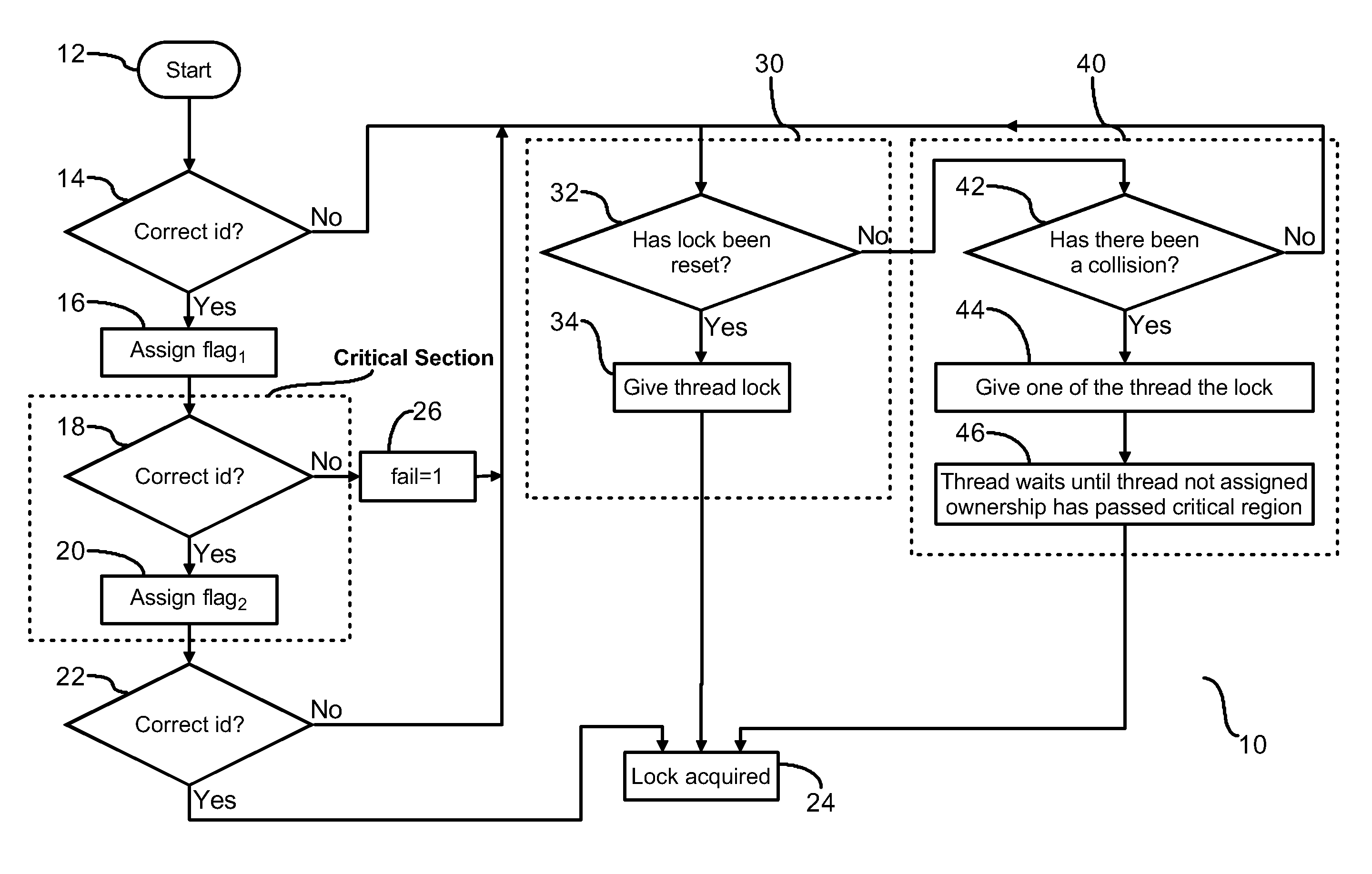

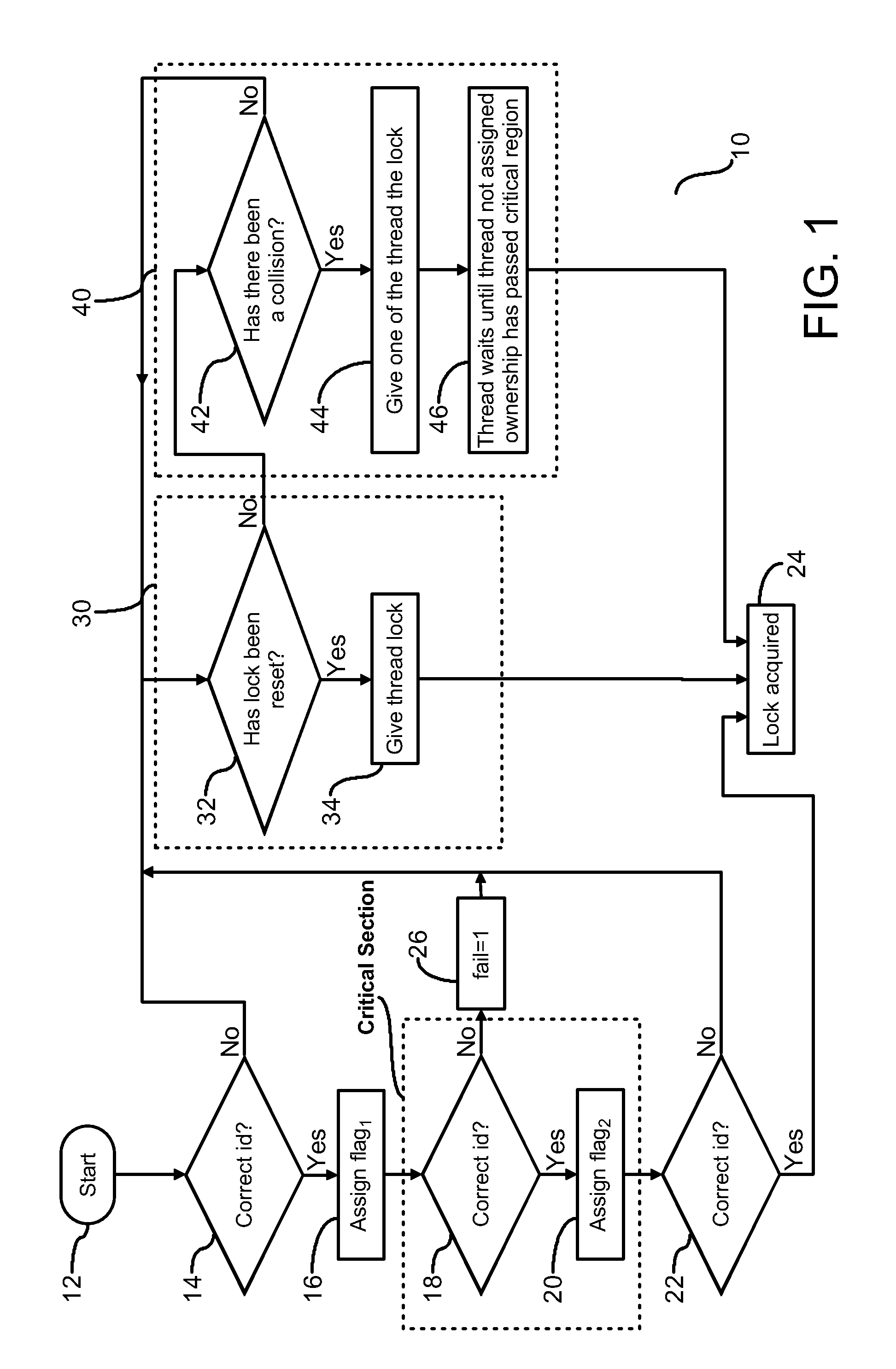

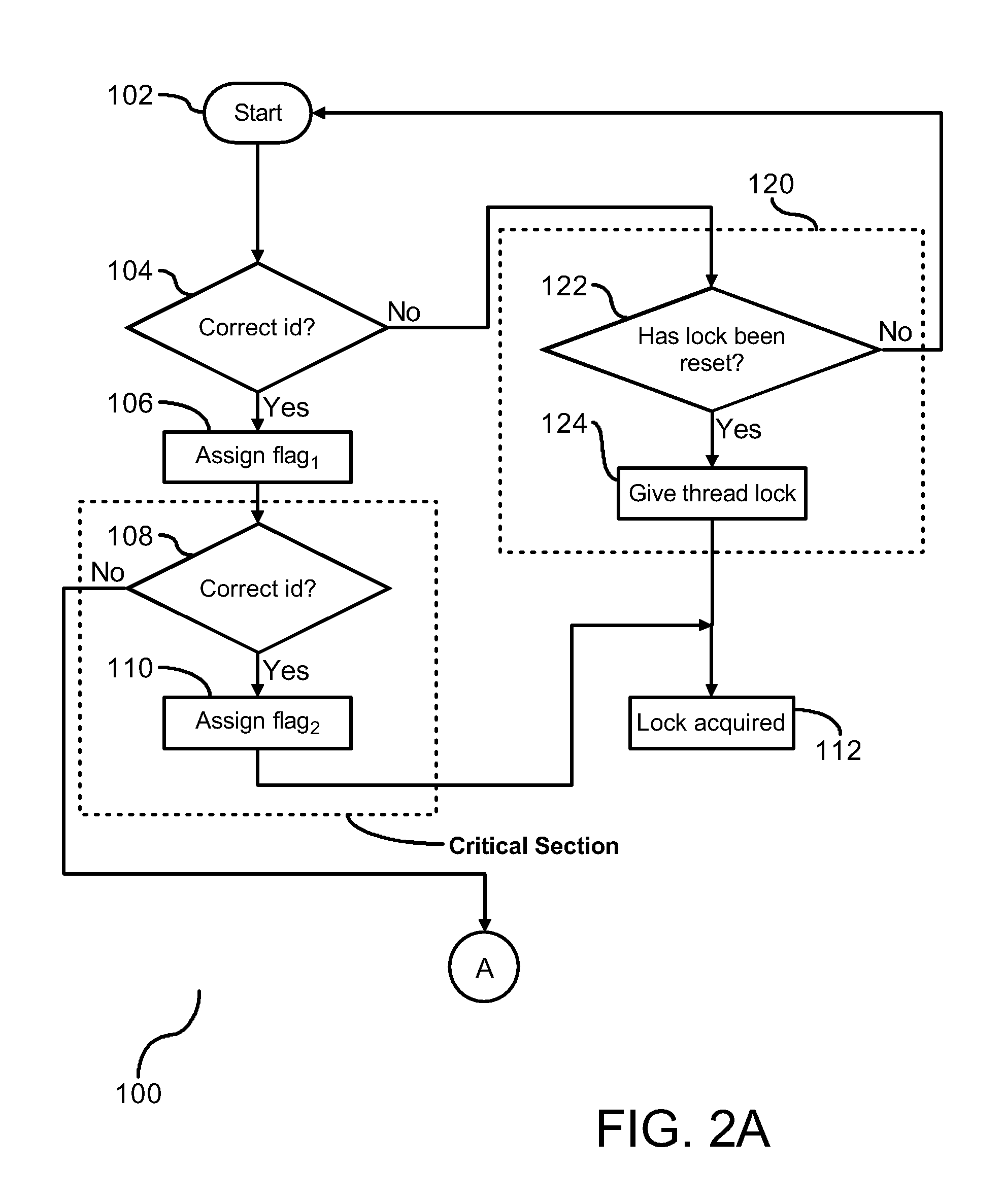

Method and System for Speeding Up Mutual Exclusion

InactiveUS20080276256A1Program synchronisationSpecific program execution arrangementsMulti processorCompare-and-swap

In a multiprocessor computer system, a lock operation is maintained with a thread using non-atomic instructions. Identifiers are assigned to each thread. Flags in conjunction with the thread identifiers are used to determine the continuity of the lock with a thread. However, in the event continuity of the lock with the thread ceases, a compare-and-swap operation is executed to reset the lock with the same thread or another thread. Similarly, in the event there has been a collision between two or more threads requesting the lock, a compare-and-swap operation is executed to assign the lock to one of the requesting threads. Accordingly, prolonged ownership of a lock operation by a thread is encouraged to mitigate use of atomic operations in granting of the lock to a non-owning thread.

Owner:IBM CORP

Analyzing update conditions for shared variable directory information in a parallel computer

InactiveUS20140173205A1Software engineeringMemory adressing/allocation/relocationParallel computingRunning time

Methods, parallel computers, and computer program products for analyzing update conditions for shared variable directory (SVD) information in a parallel computer are provided. Embodiments include a runtime optimizer receiving a compare-and-swap operation header. The compare-and-swap operation header includes an SVD key, a first SVD address, and an updated first SVD address. The first SVD address is associated with the SVD key in a first SVD associated with a first task. Embodiments also include the runtime optimizer retrieving from a remote address cache associated with the second task, a second SVD address indicating a location within a memory partition associated with the first SVD in response to receiving the compare-and-swap operation header. Embodiments also include the runtime optimizer determining whether the second SVD address matches the first SVD address and transmitting a result indicating whether the second SVD address matches the first SVD address.

Owner:IBM CORP

Creating and maintaining order of a log stream without use of a lock or latch

InactiveUS20120203805A1Digital data information retrievalSpecial data processing applicationsByte addressingByte

Provided are techniques for using a series of compare and swap operations to assign a Relative Byte Address (RBA) and a Logical Record Sequence Number (LRSN) to a log record. One or more log buffers for storing the log record are identified, and the log record is moved to the one or more log buffers.

Owner:INT BUSINESS MASCH CORP

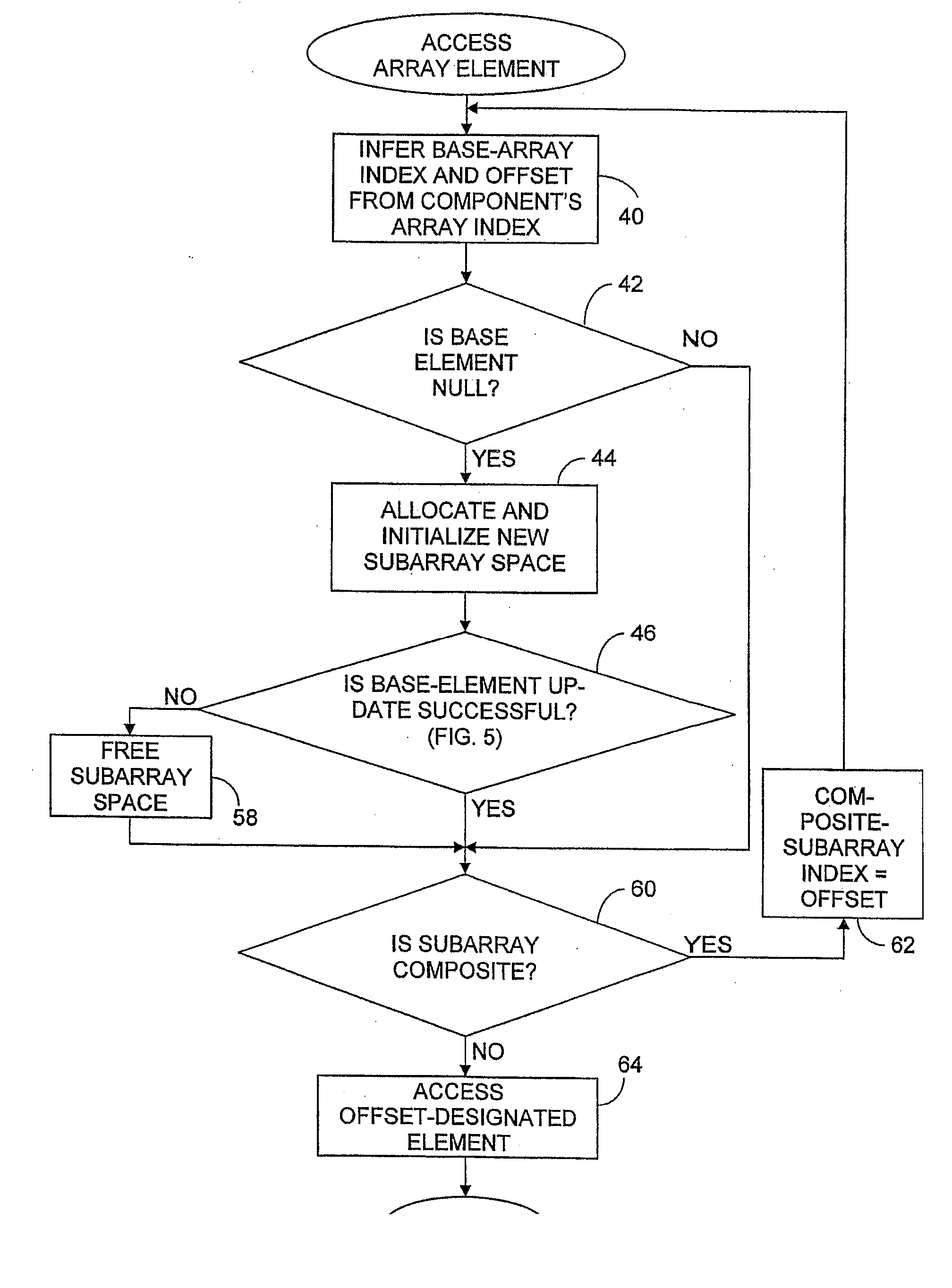

Non-Blocking Growable Arrays

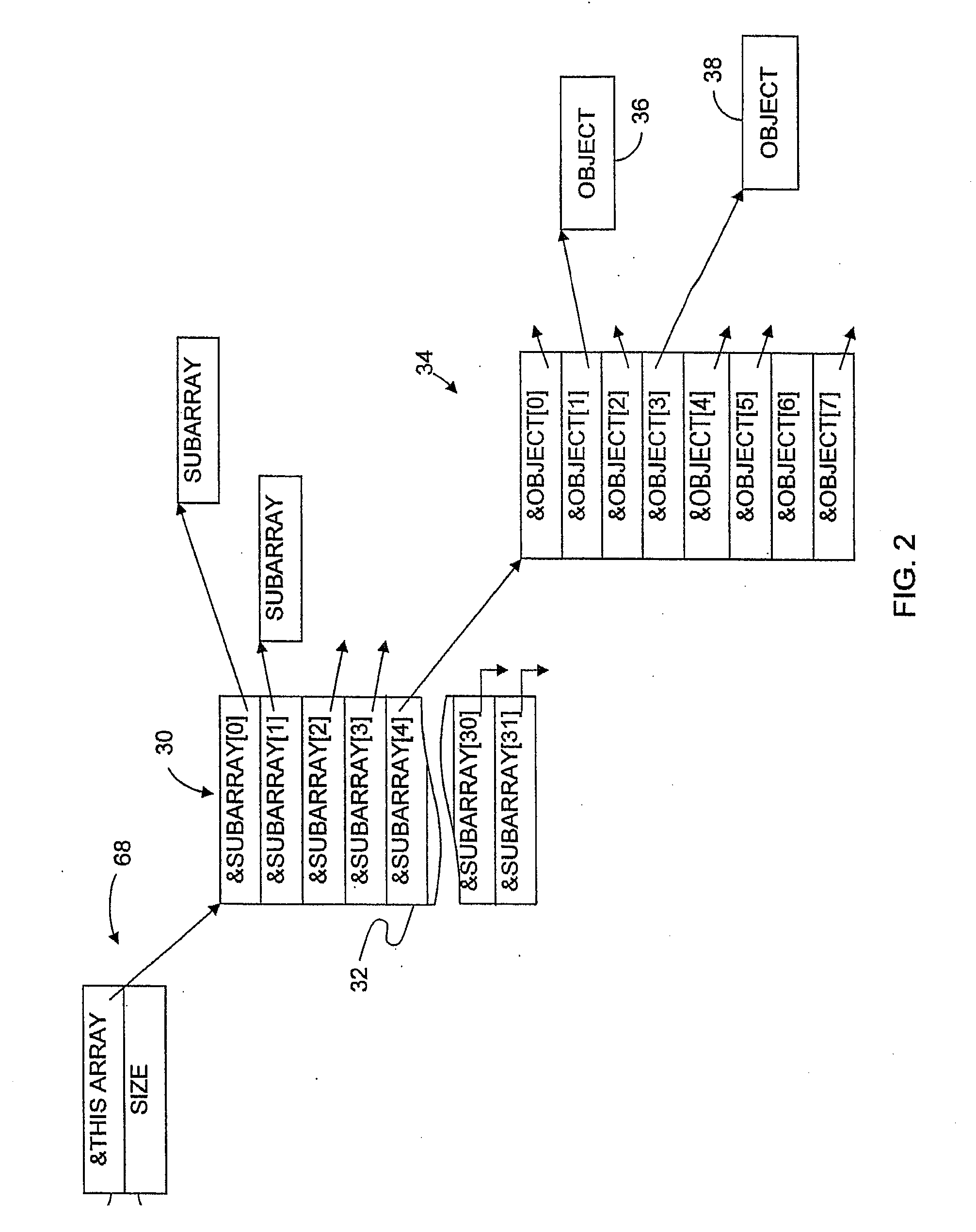

ActiveUS20070174577A1Avoid approachingMemory systemsMicro-instruction address formationArray elementData element

A computer system stores a dynamically sized array as a base array that contains references to subarrays in which the (composite) array's data elements reside. Each of the base-array elements that thus refers to a respective subarray is associated with a respective subarray size. Each base-array index is thereby at least implicitly associated with a cumulative base value equal to the sum of all preceding base indexes' associated subarray sizes. In response to a request for access to the element associated with a given (composite-array) index, the array-access system identifies the base index associated with the highest cumulative base value not greater than the composite-array index and performs the access to the subarray identified by the element associated with that base index. Composite-array expansion can be performed in a multi-threaded environment without locking, simply by employing a compare-and-swap or similar atomic operation.

Owner:SUN MICROSYSTEMS INC

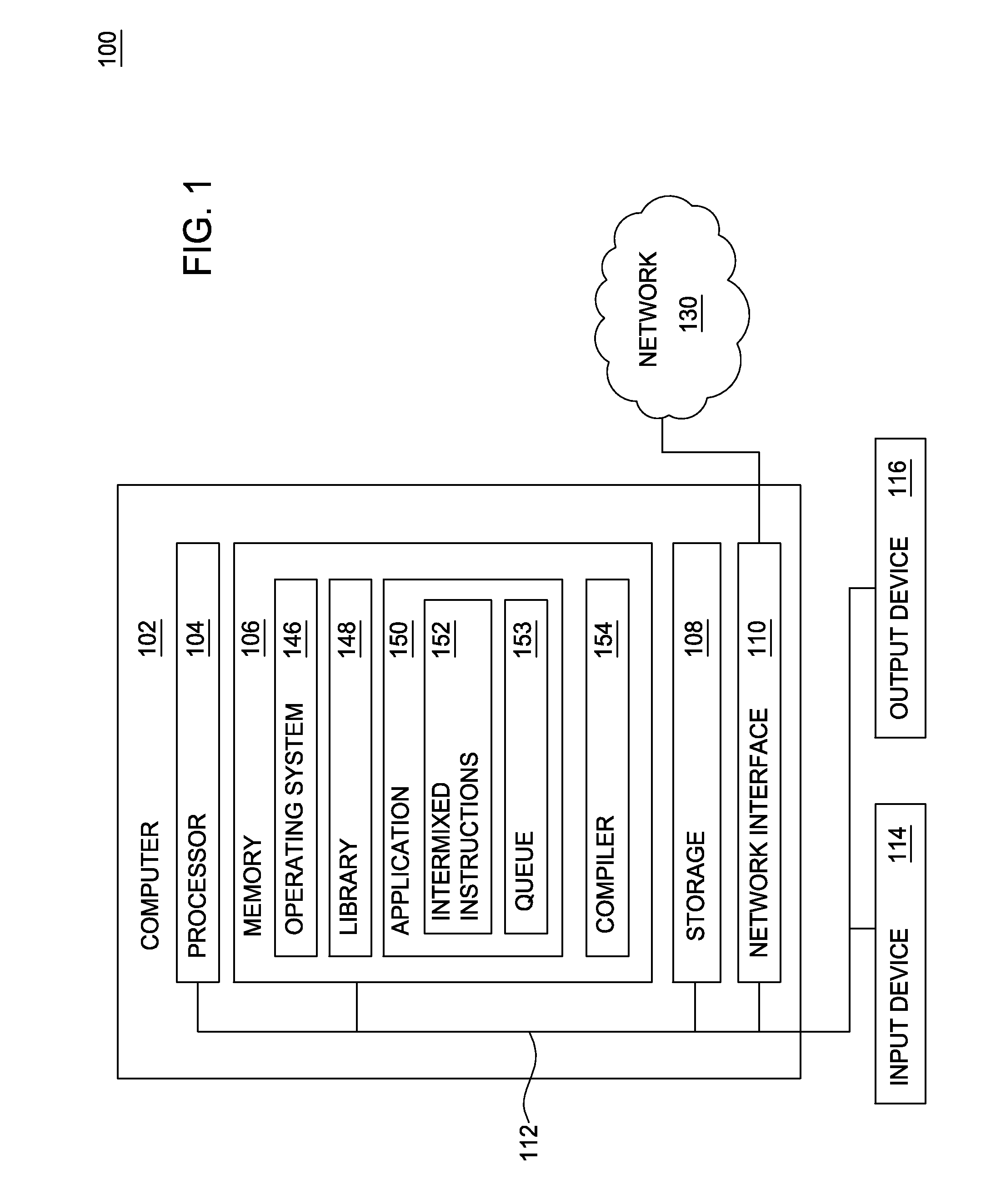

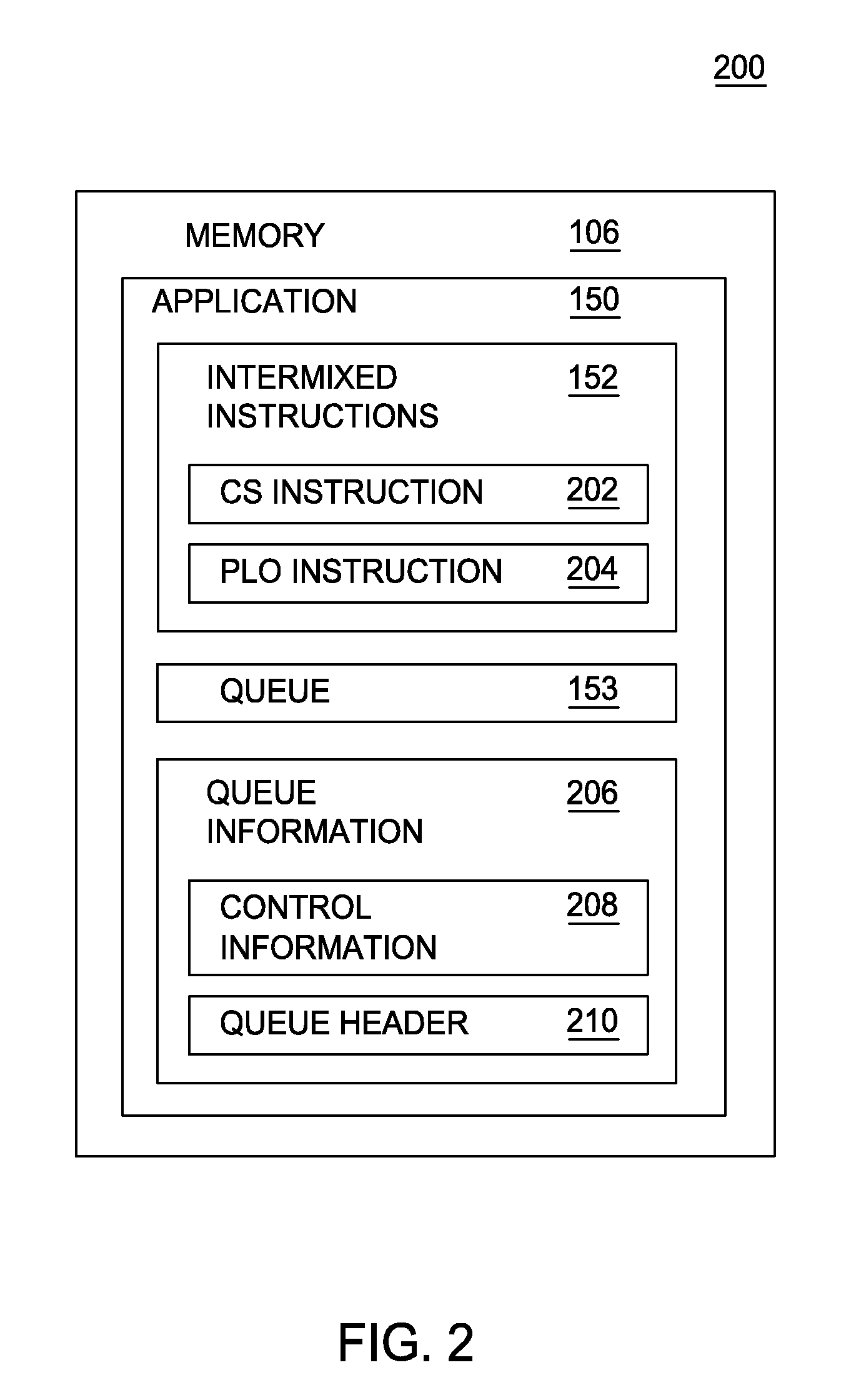

Hybrid compare and swap/perform locked operation queue algorithm

ActiveUS20110320780A1Digital computer detailsSpecific program execution arrangementsMachine instructionDistributed computing

Systems, methods, and computer program products are disclosed for intermixing different types of machine instructions. One embodiment of the invention provides a protocol for intermixing the different types of machine instructions. By adhering to the protocol, different types of machine instructions may be intermixed to concurrently update data structures without leading to unpredictable results.

Owner:IBM CORP

Cell processor atomic compare and swap using dedicated synergistic processor element

An atomic compare and swap operation that can be implemented in processor system having a power processor element (PPE) and a synergistic processor element (SPE) that have different sized memory transfer capabilities. The PPE notifies an SPE to perform a compare and swap operation on an address in main memory. The address has a size less than or equal to a maximum memory transfer size for the SPE and greater than a maximum memory transfer size for the PPE. The SPE atomically performs the compare and swap operation and notifies the PPE of the success or failure of the compare and swap operation.

Owner:SONY COMPUTER ENTERTAINMENT INC

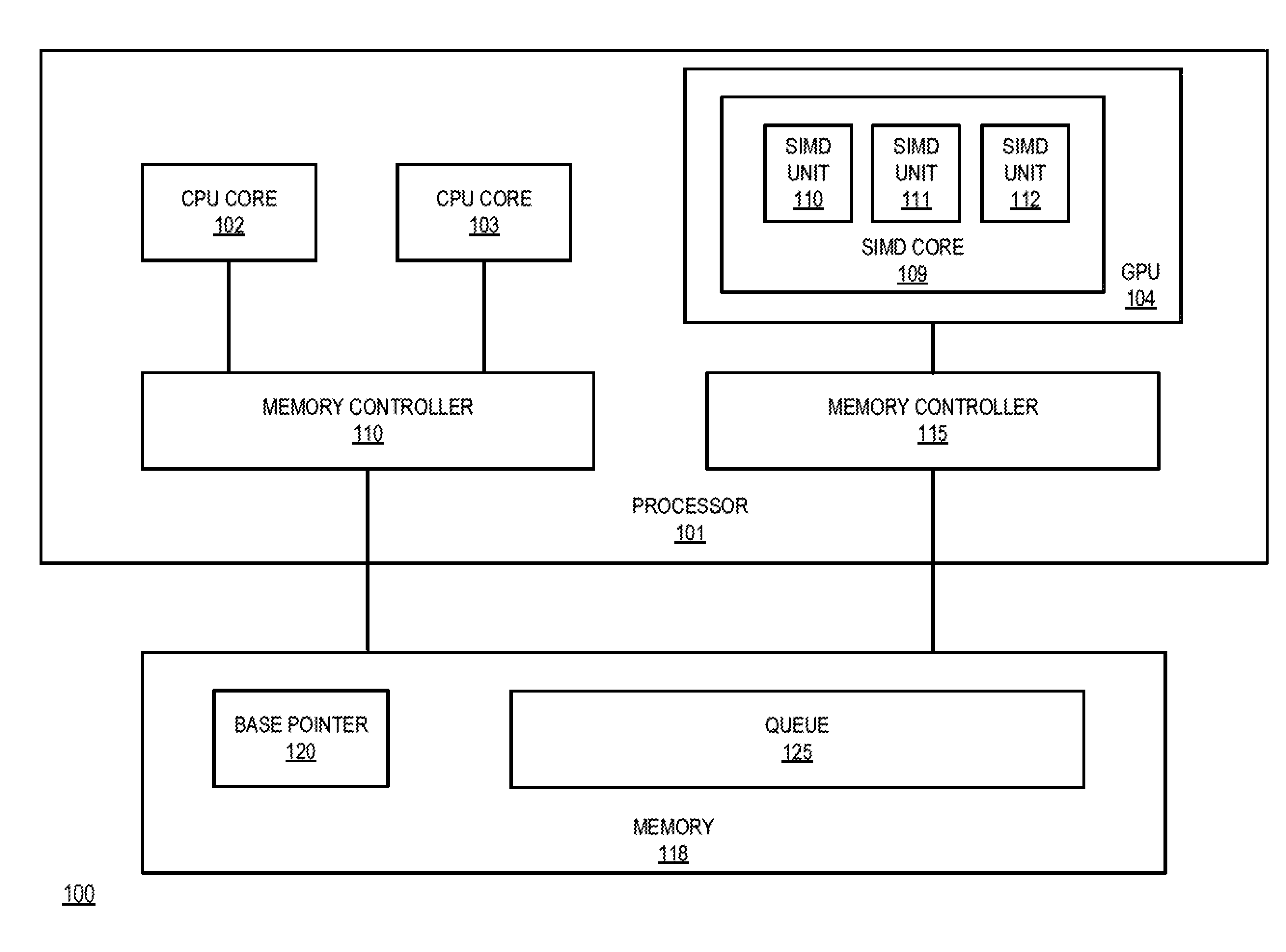

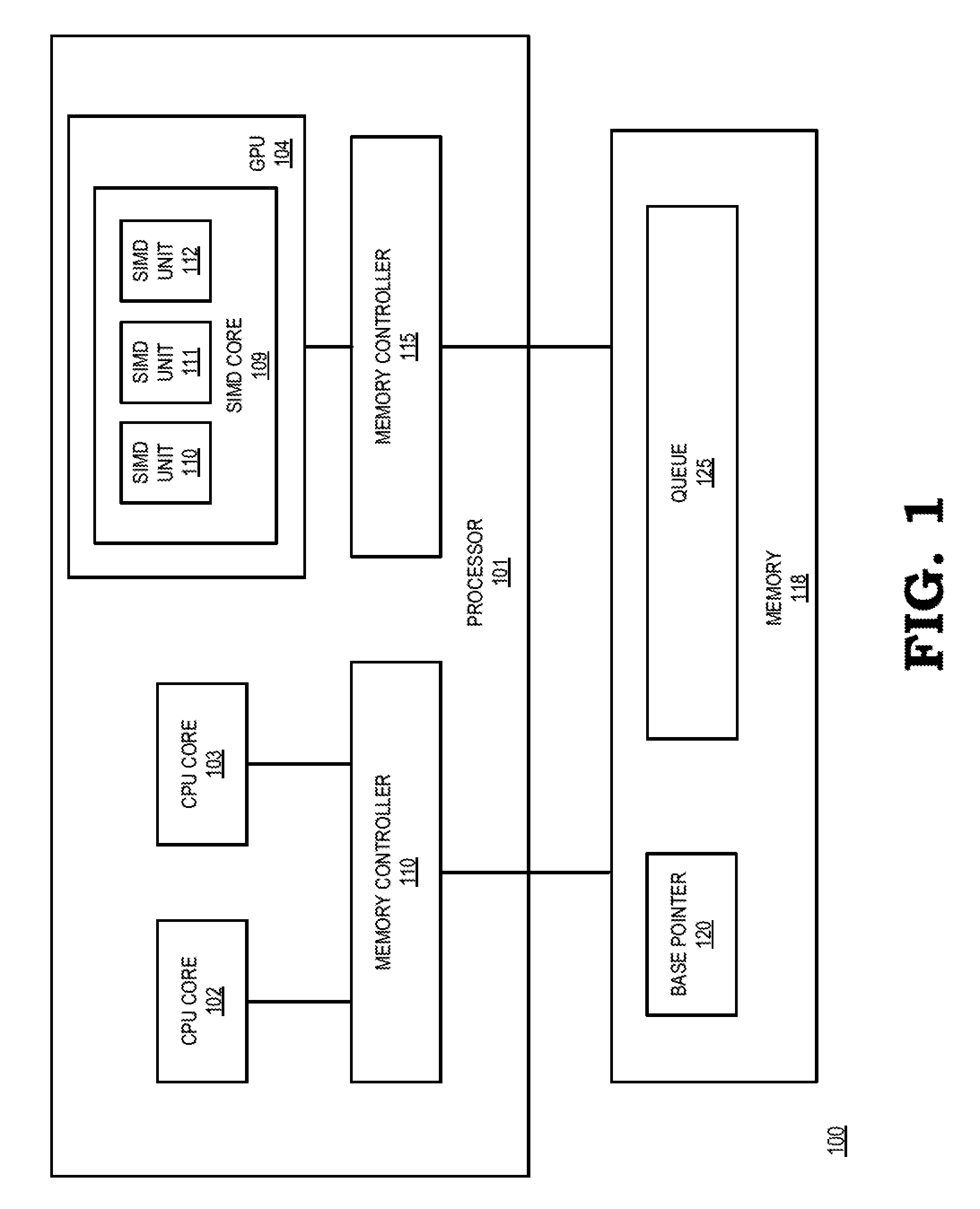

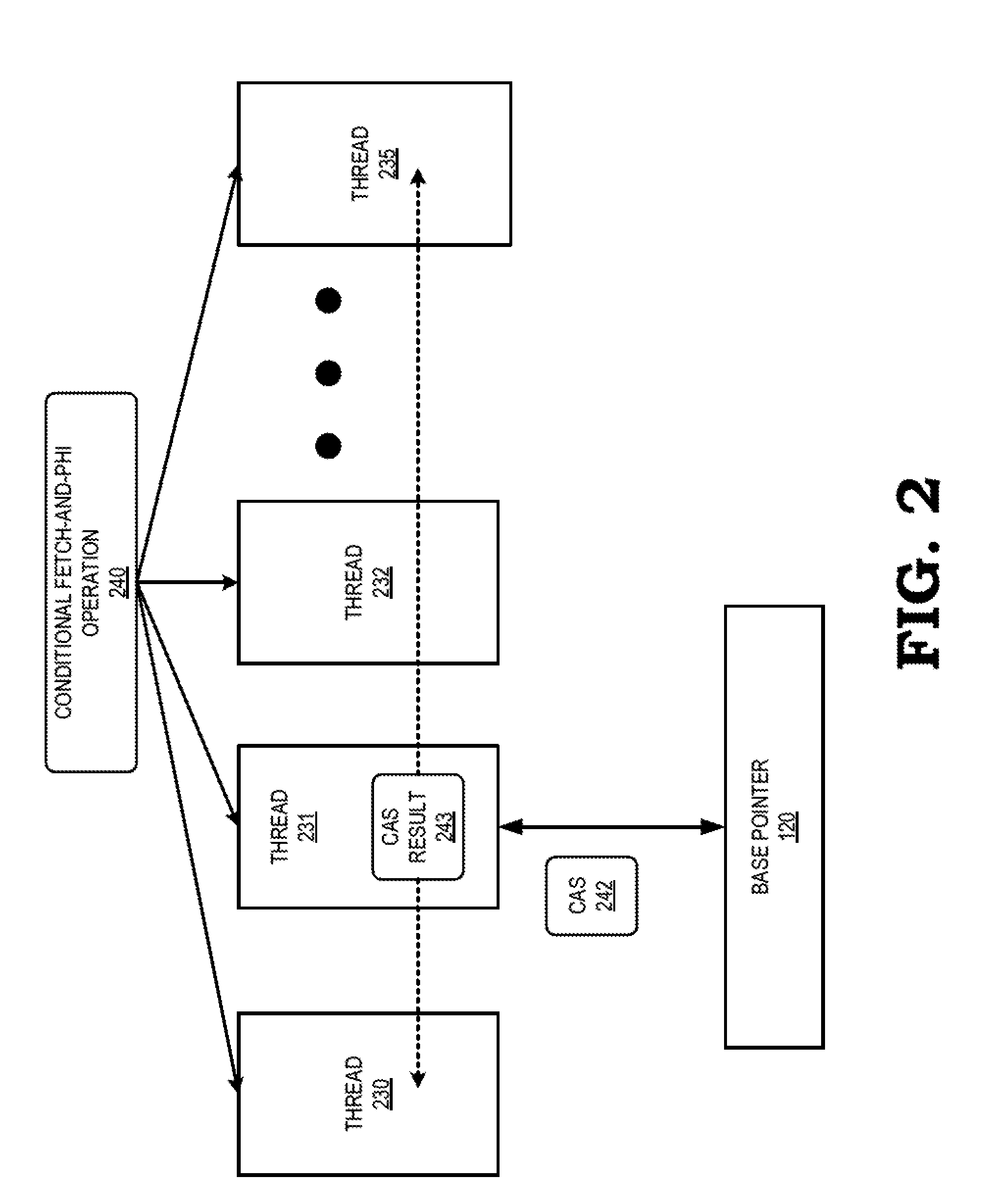

Conditional atomic operations at a processor

ActiveUS20160357551A1Program synchronisationMachine execution arrangementsWavefrontAtomic operations

A conditional fetch-and-phi operation tests a memory location to determine if the memory locations stores a specified value and, if so, modifies the value at the memory location. The conditional fetch-and-phi operation can be implemented so that it can be concurrently executed by a plurality of concurrently executing threads, such as the threads of wavefront at a GPU. To execute the conditional fetch-and-phi operation, one of the concurrently executing threads is selected to execute a compare-and-swap (CAS) operation at the memory location, while the other threads await the results. The CAS operation tests the value at the memory location and, if the CAS operation is successful, the value is passed to each of the concurrently executing threads.

Owner:ADVANCED MICRO DEVICES INC

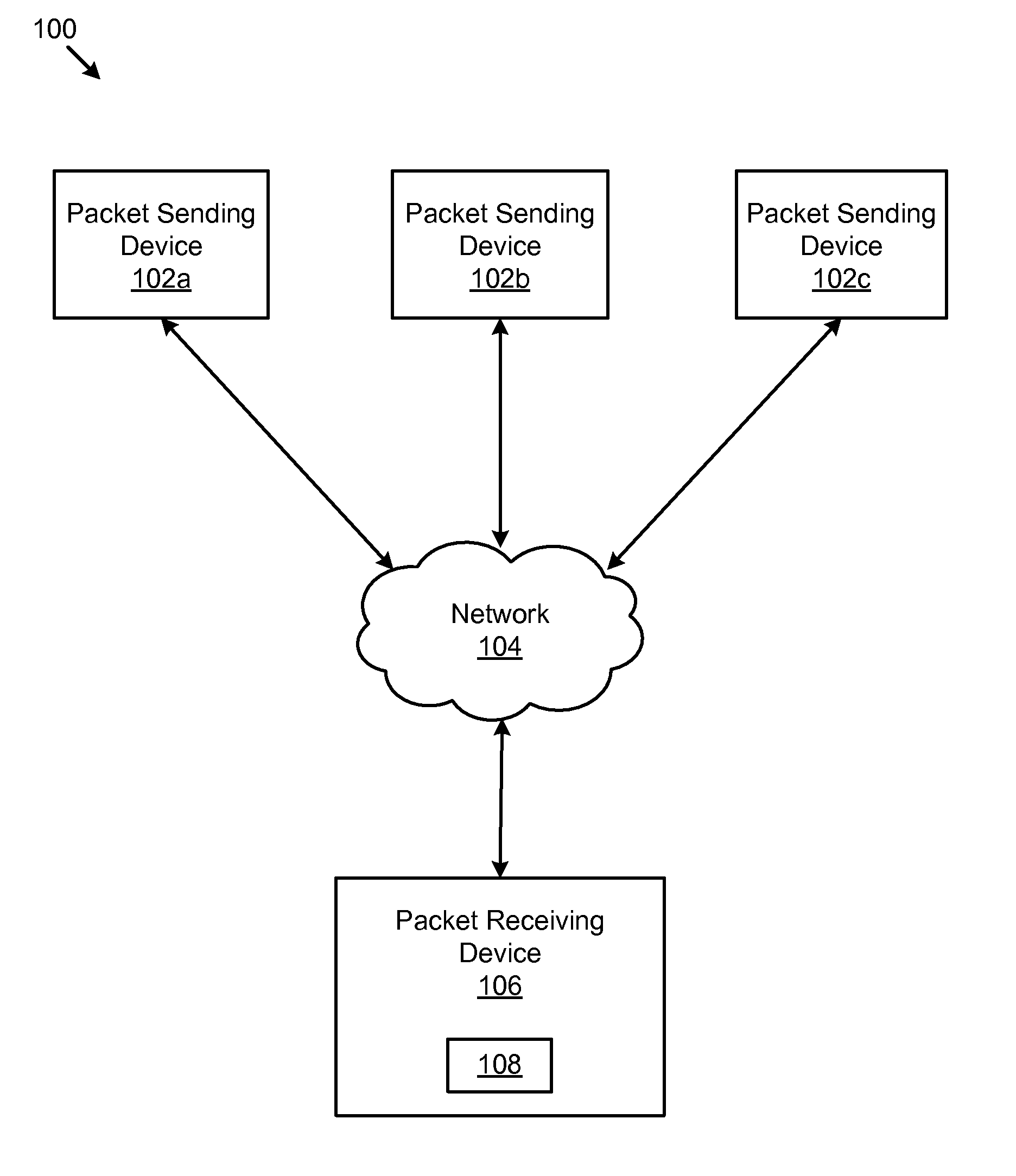

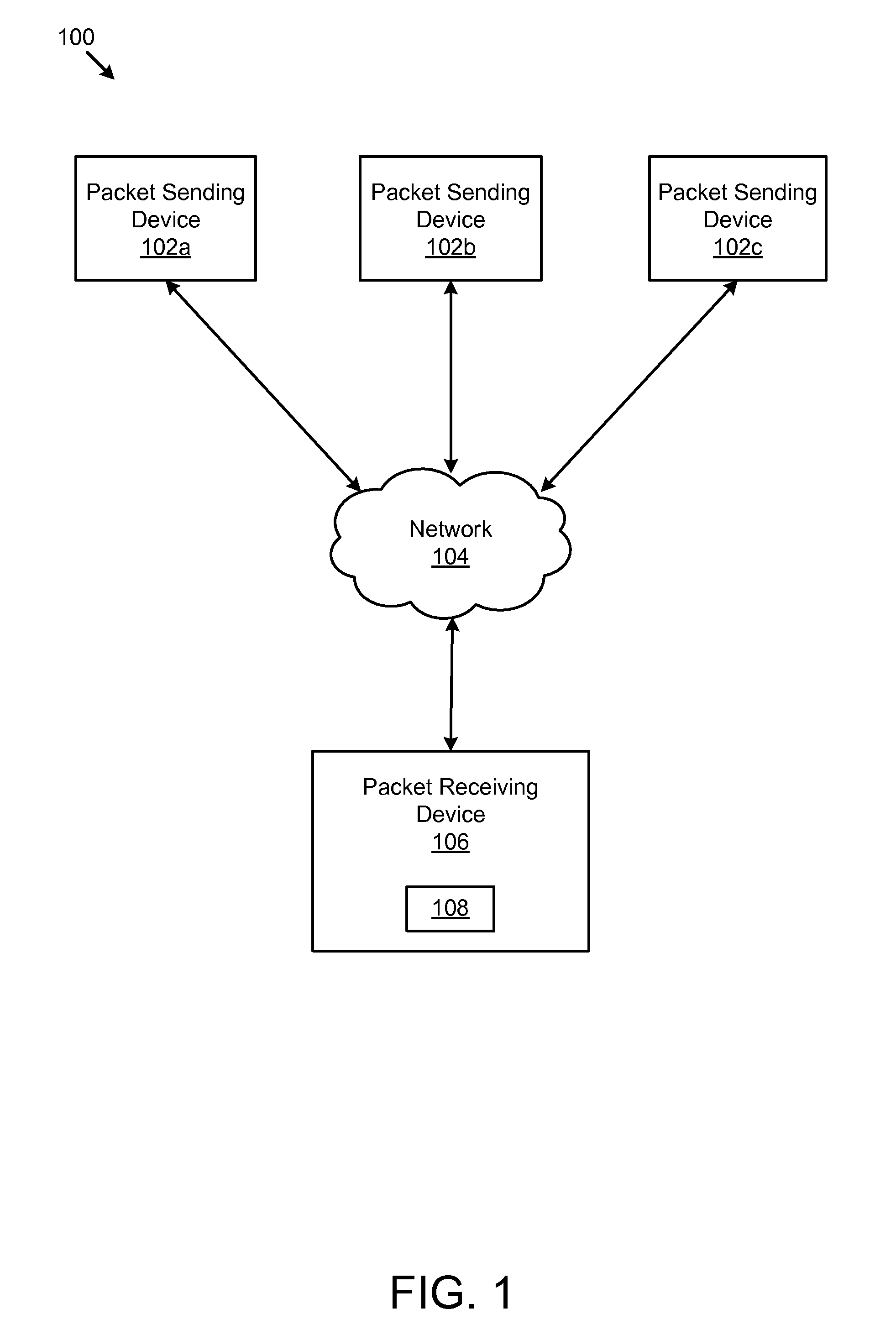

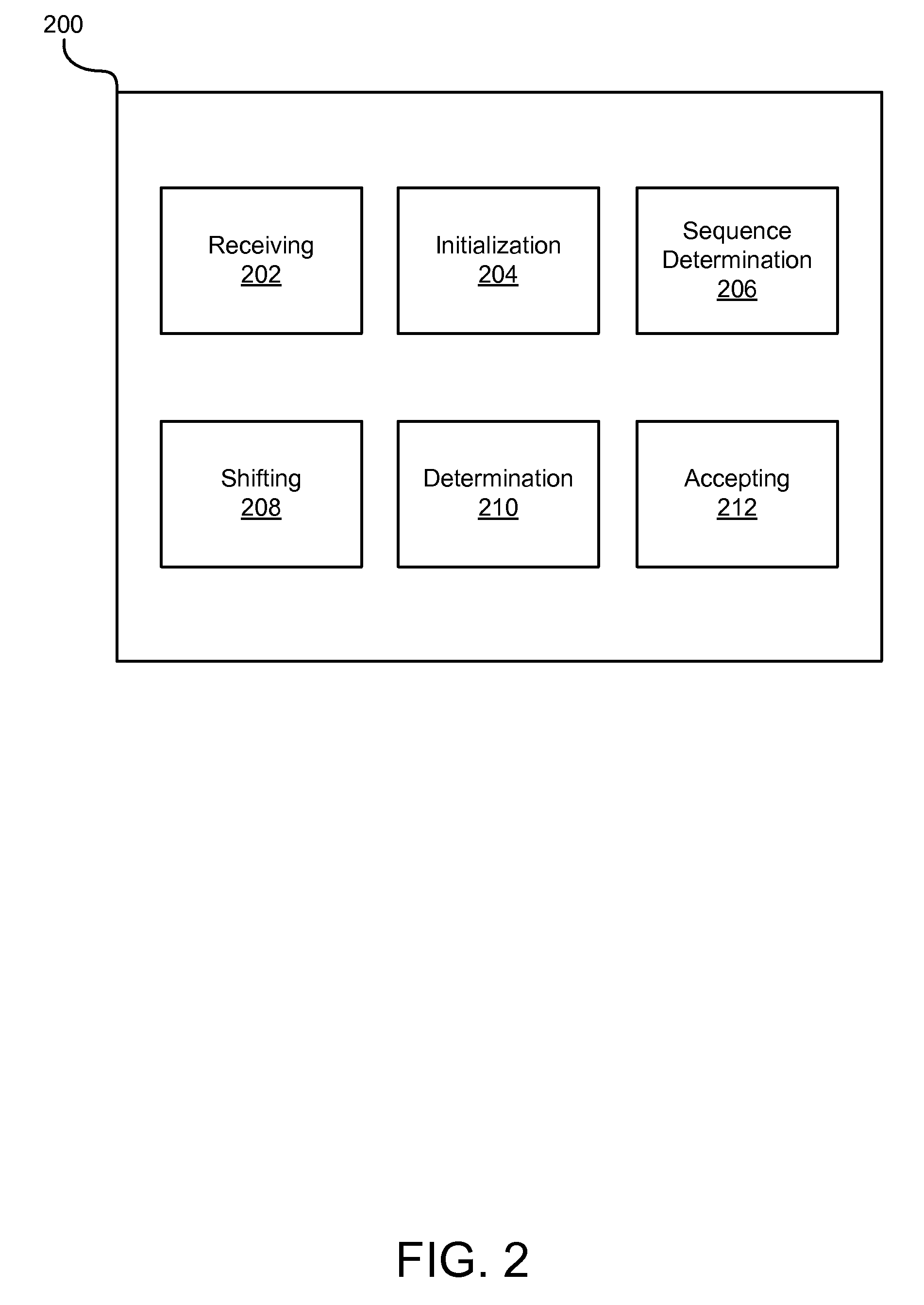

Efficient synchronization of a sliding buffer window to prevent packet re-injection in an internet protocol (IP) network

ActiveUS20090245290A1Effective synchronizationError preventionTime-division multiplexDouble compare-and-swapCircular buffer

An apparatus, system, and method are disclosed for efficient synchronization of a sliding buffer window to prevent packet re-injection in an IP network. The steps of the method include receiving a data packet which comprises a packet sequence number. The method initializes a replay counter, an update counter, and a circular buffer window. The circular buffer window may comprise at least one window bank and the circular buffer window may also comprise a current window bank. Furthermore, the method may include determining that the packet sequence number is greater than a maximum current bank value. In response, the method may define shifting the circular buffer window such that a current window bank position is incremented. The method may then include determining that the packet sequence number is inside the current window bank and accepting the data packet. Furthermore, a Double Compare and Swap (DCS) operation may update the bit indicator and increment the update counter and replay counter. Also, a Compare and Swap and Store (CSST) operation may increment the update counter and replay counter and set a shifted window bank. Therefore, DCS and CSST operation may still be used without having to resort to traditional locks with higher overhead. In addition, the buffer window may be an arbitrary size and is not limited to the machine architecture limit for compare and swap operations.

Owner:IBM CORP