Patents

Literature

60 results about "Byte addressing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Byte addressing refers to hardware architectures which support accessing individual bytes of data rather than only larger units called words, which would be word-addressable. Such computers are sometimes called byte machines (in contrast to word machines).

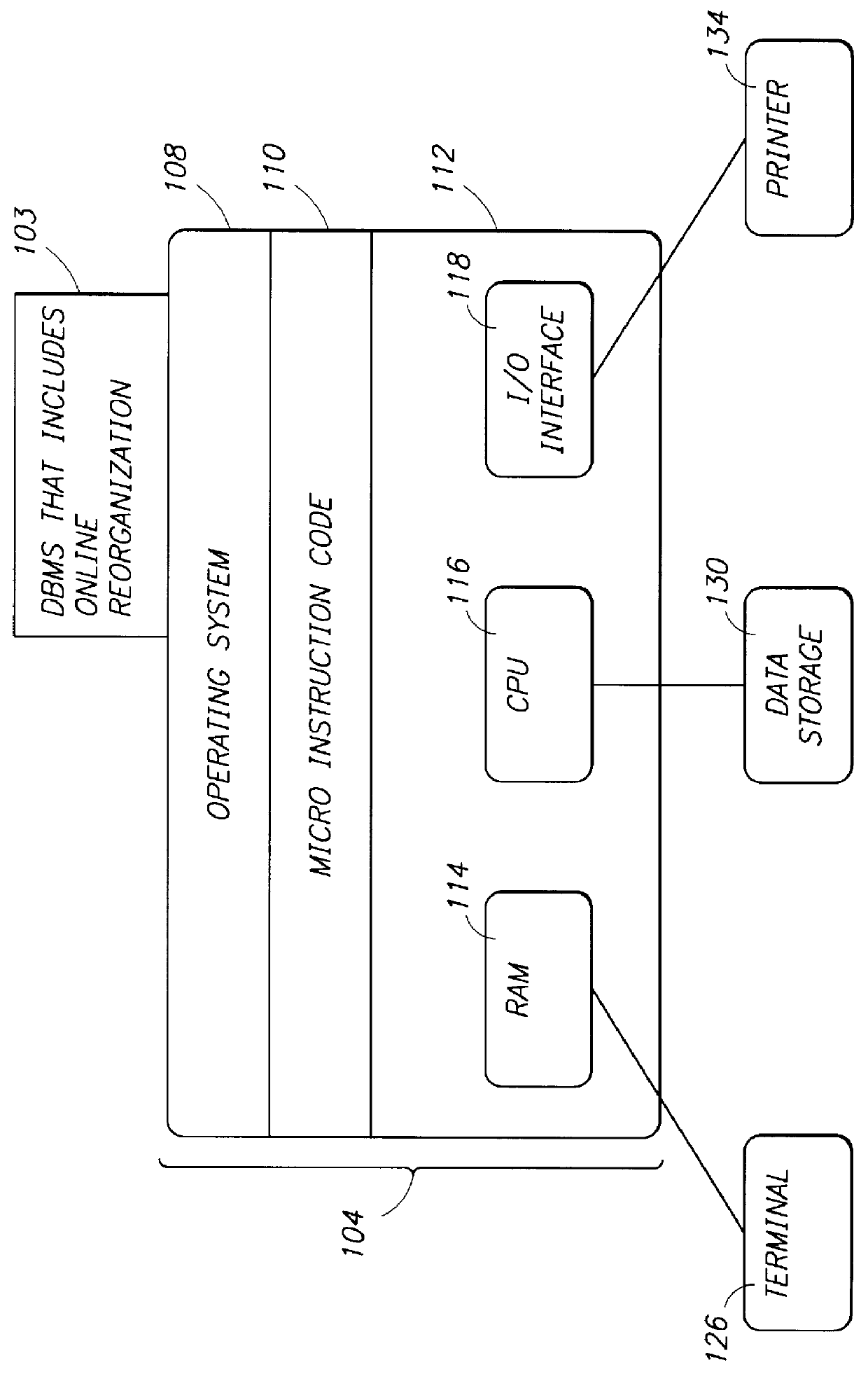

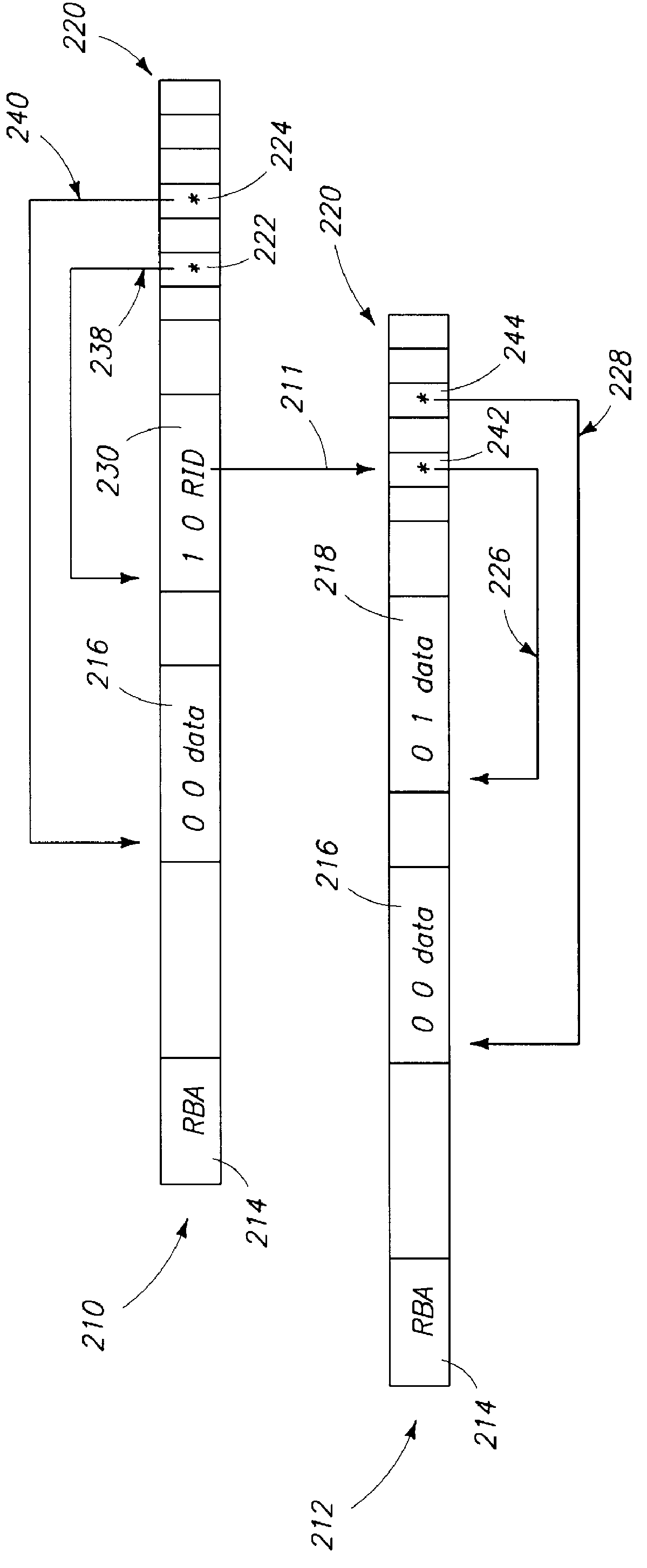

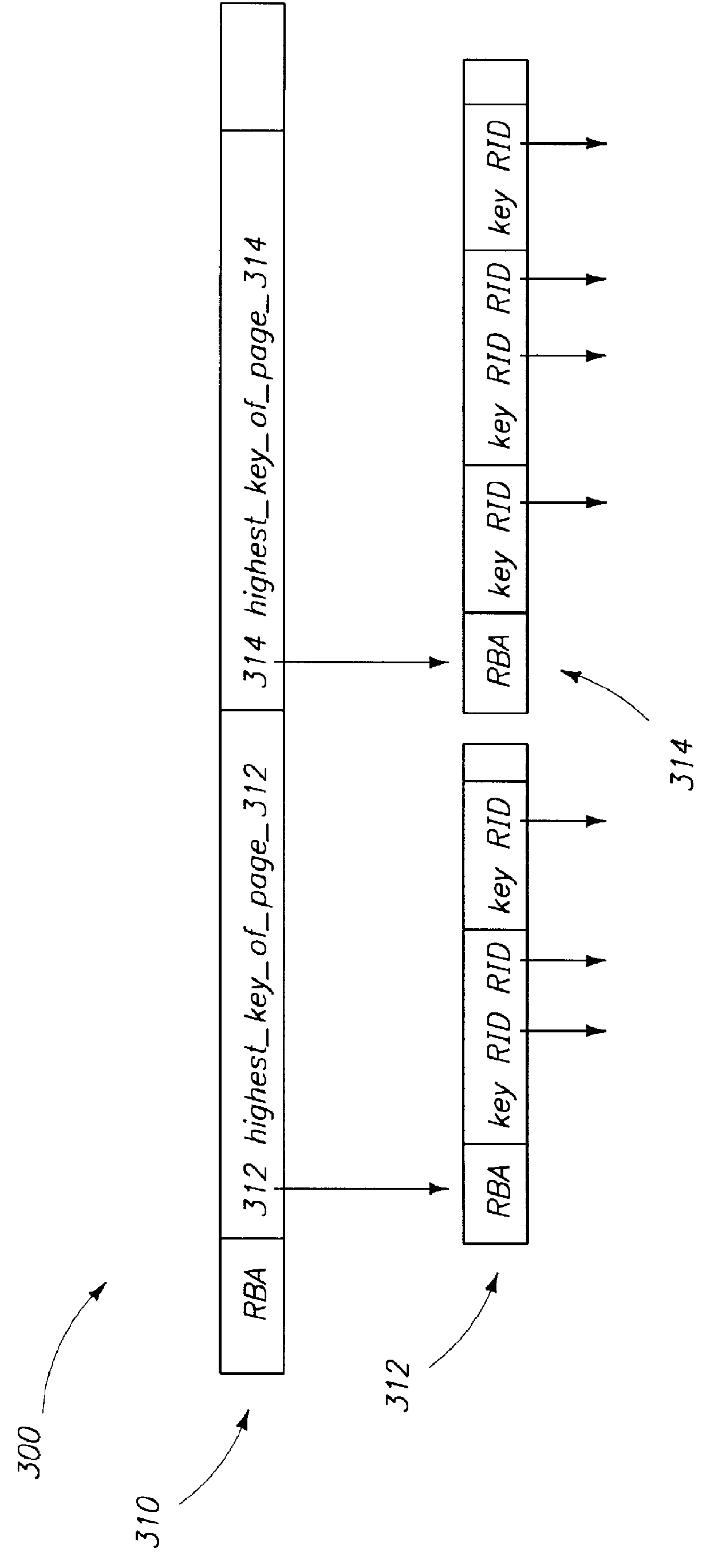

Interaction between application of a log and maintenance of a table that maps record identifiers during online reorganization of a database

InactiveUS6026412AImproves locality of reference (and thus speed)Delay detectionData processing applicationsDigital data information retrievalByte addressingByte

The present invention includes reorganization of a Database Management System (DBMS). The reorganization of the present invention is implemented by recording a first current Relative Byte Address (RBA). Then, data is copied from the old area in the table space to a new area in the table space in reorganized form. In the present invention, throughout most of reorganization a user maintains access to the DBMS's normal facilities to read and write to the old area. The DBMS uses its normal facilities to record writing, which occurs during reorganization, in a log. The reorganization in accordance with the present invention reads the log (that has been written to during reorganization) and processes the log to the new area to bring the new area up to date. This process is performed with the use of a RID mapping table. Finally, at the end of reorganization, the user's access is switched from the old area to the new area.

Owner:IBM CORP

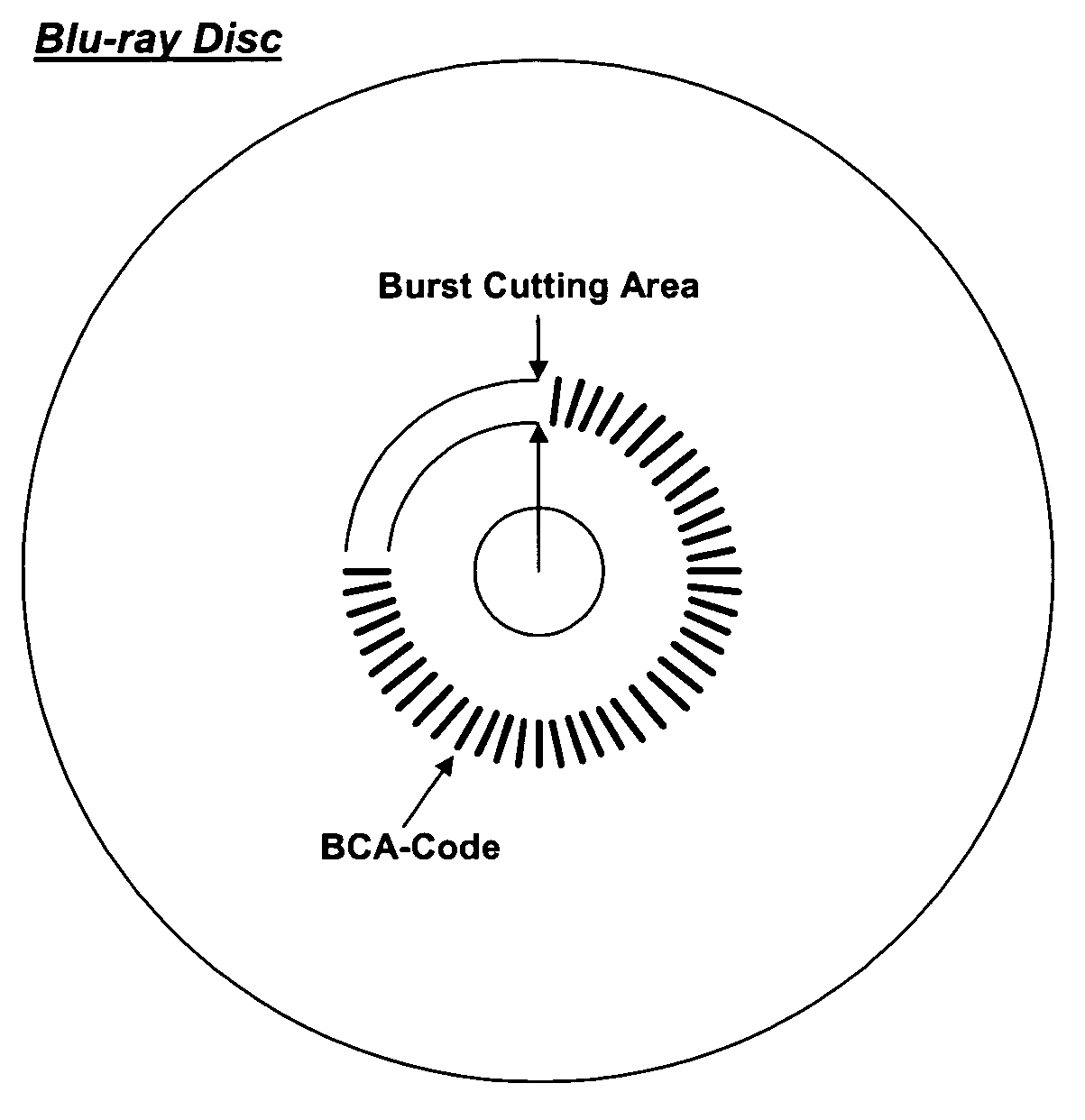

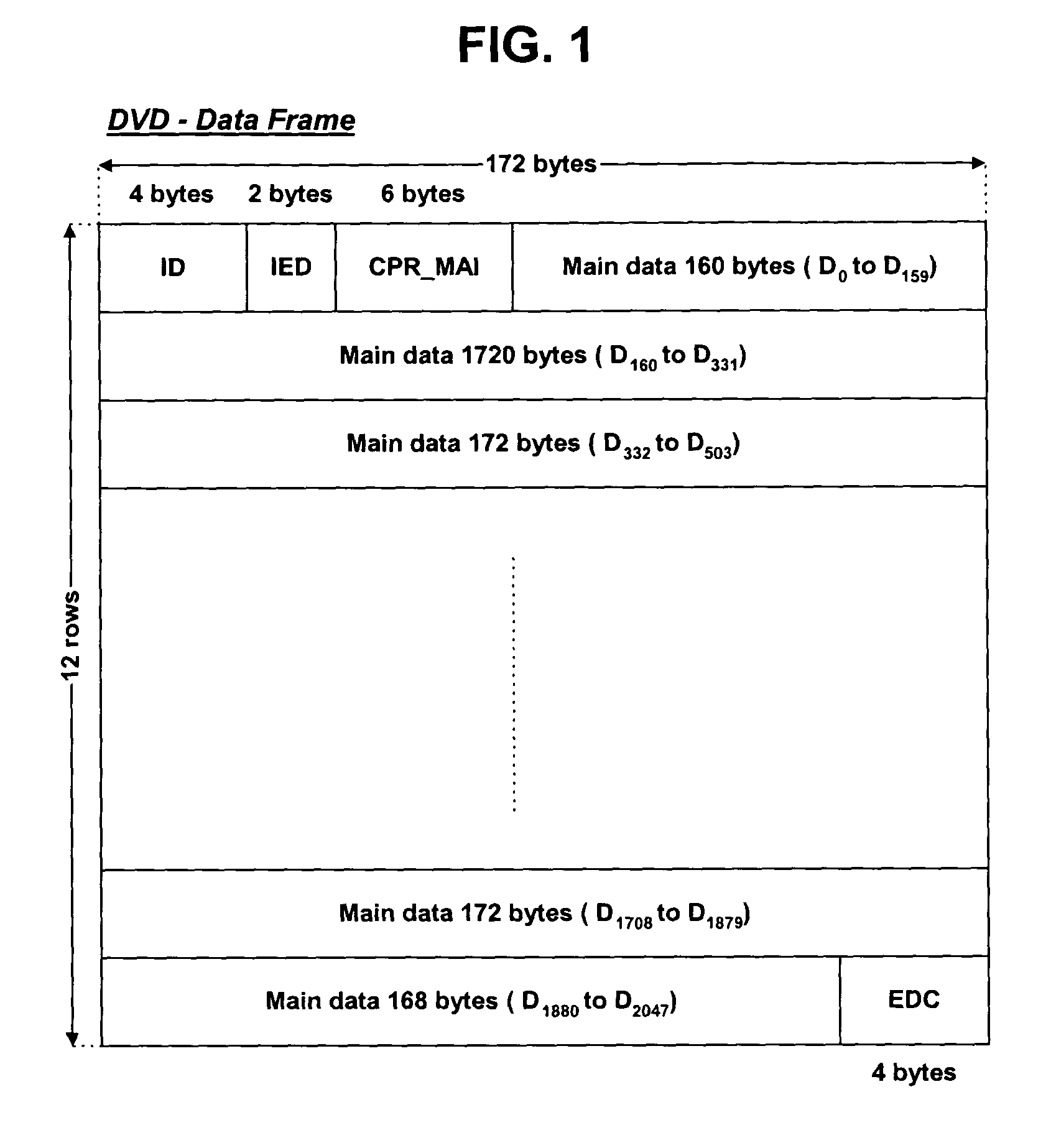

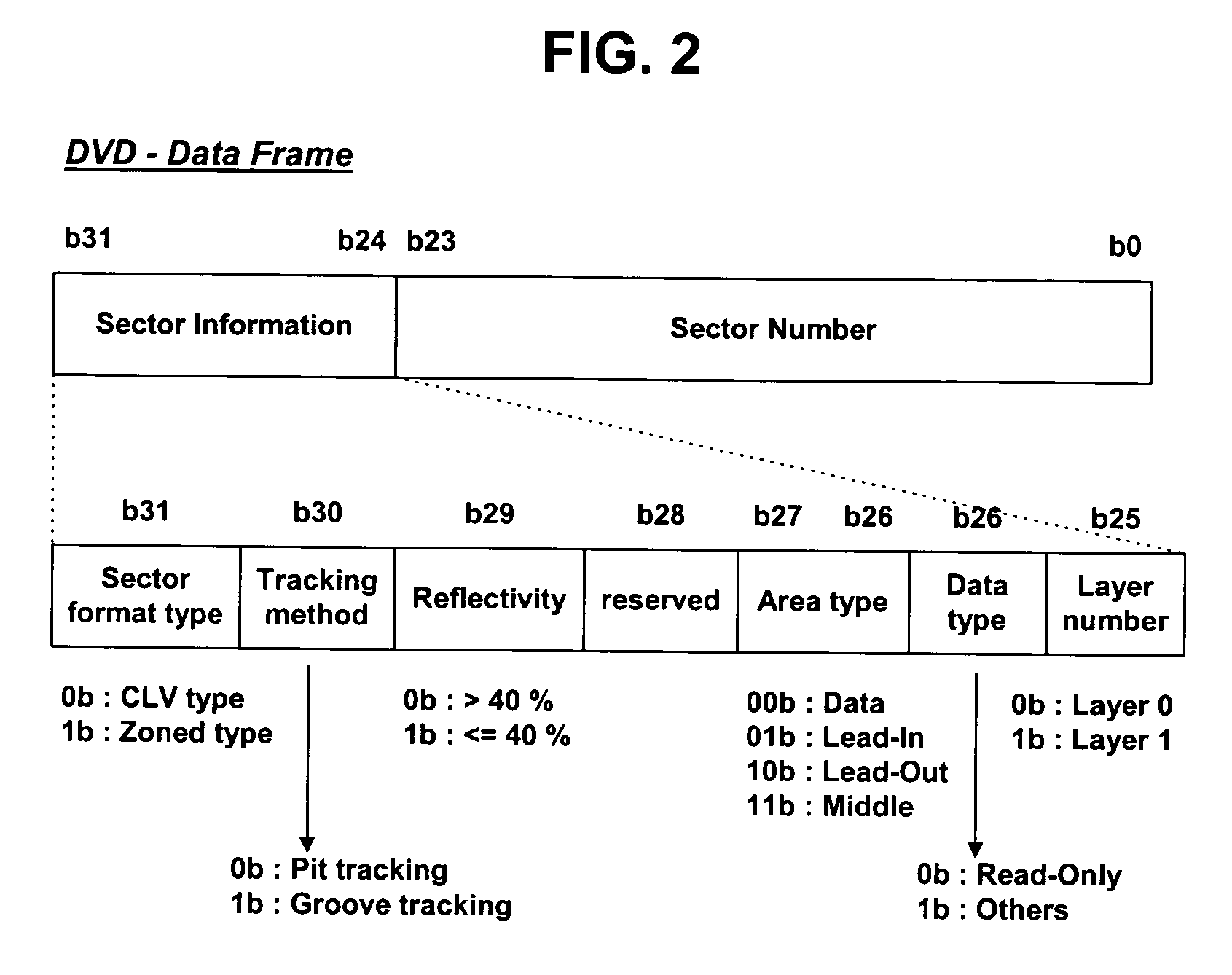

High-density optical disc and recording/reproducing method thereof

ActiveUS20050099916A1Valid recordTelevision system detailsFilamentary/web record carriersHigh densityOptical power

A high-density optical disc such as BD-RE (Blu-ray Disc Rewritable) or BD-ROM, and a recording / reproducing method thereof are disclosed. Diverse additional information such as disc reflectivity information, disc layer information or disc type information is efficiently recorded in a particular information field included in a data unit recorded on the burst cutting area of a high-density optical disc or a particular 1-byte address field included in an address unit recorded on the high-density optical disc so that it can be read when the high-density optical disc is loaded in an optical disc apparatus or when a data recording or reproducing operation for the high-density optical disc is carried out. Accordingly, it is possible to achieve optimal optical power control and automatic gain control or identification of a current position, while enabling a normal data recording or reproducing operation corresponding to the type of the optical disc.

Owner:LG ELECTRONICS INC

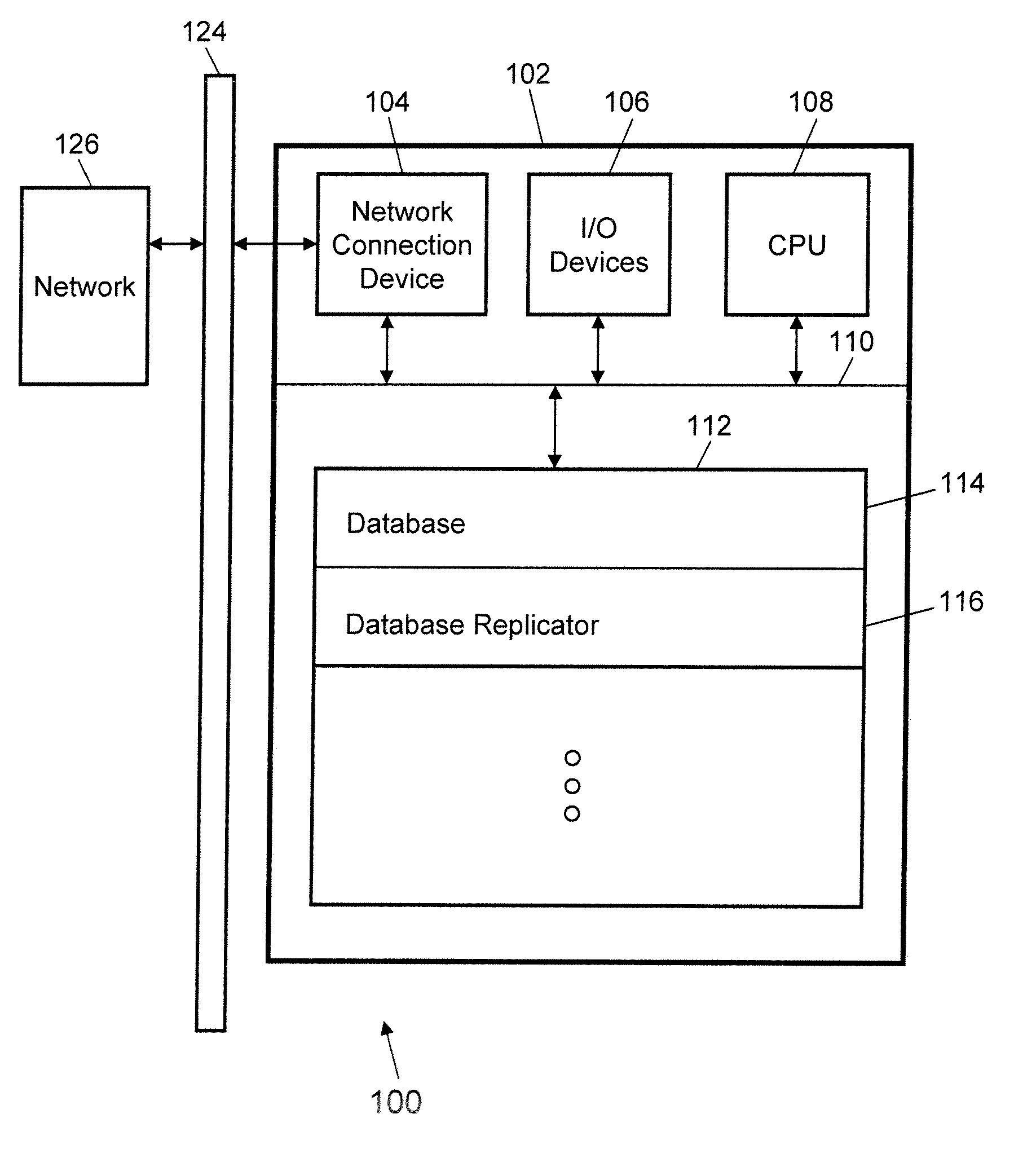

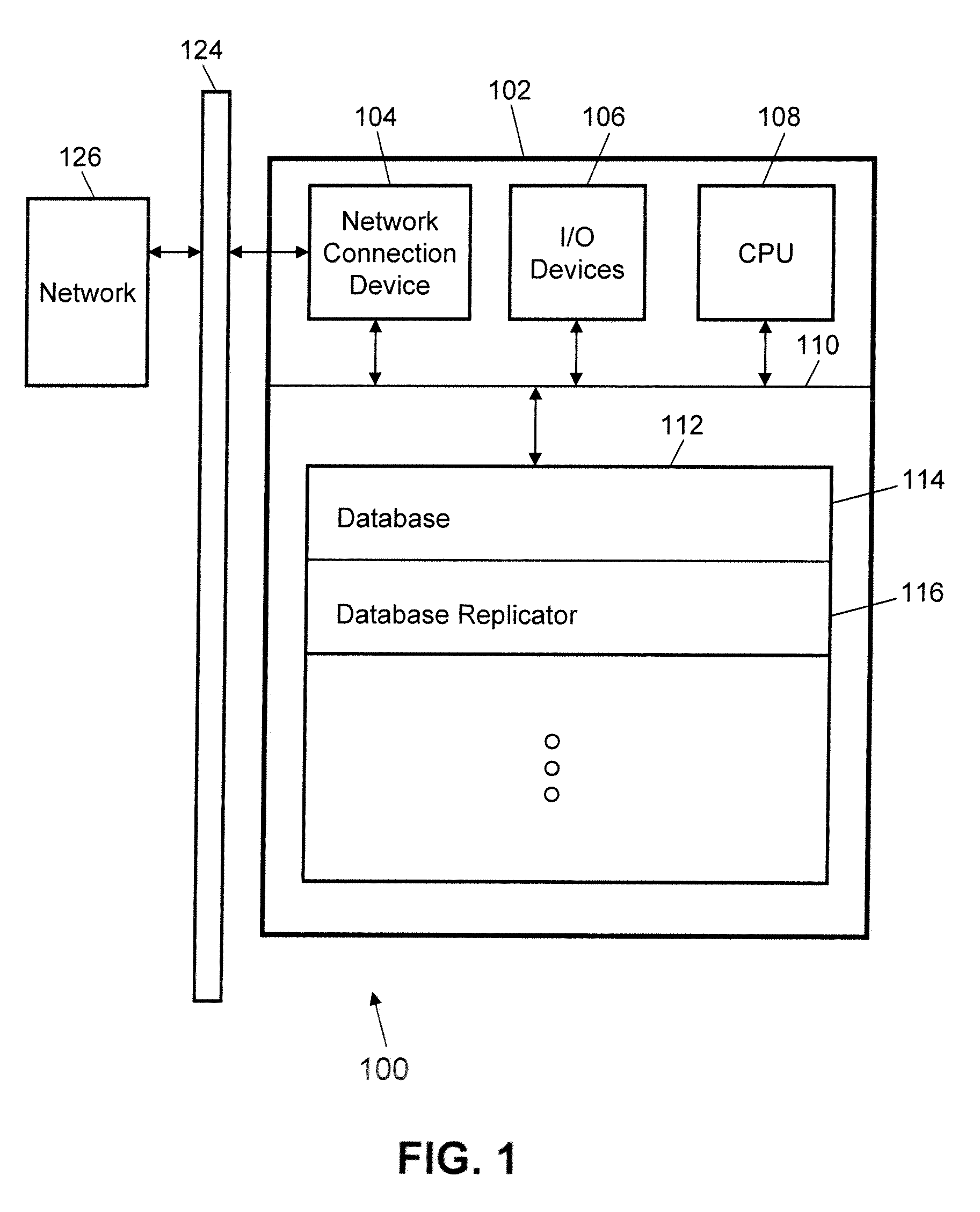

Apparatus and method for creating a real time database replica

ActiveUS20070100912A1Error detection/correctionDigital data processing detailsByte addressingData mining

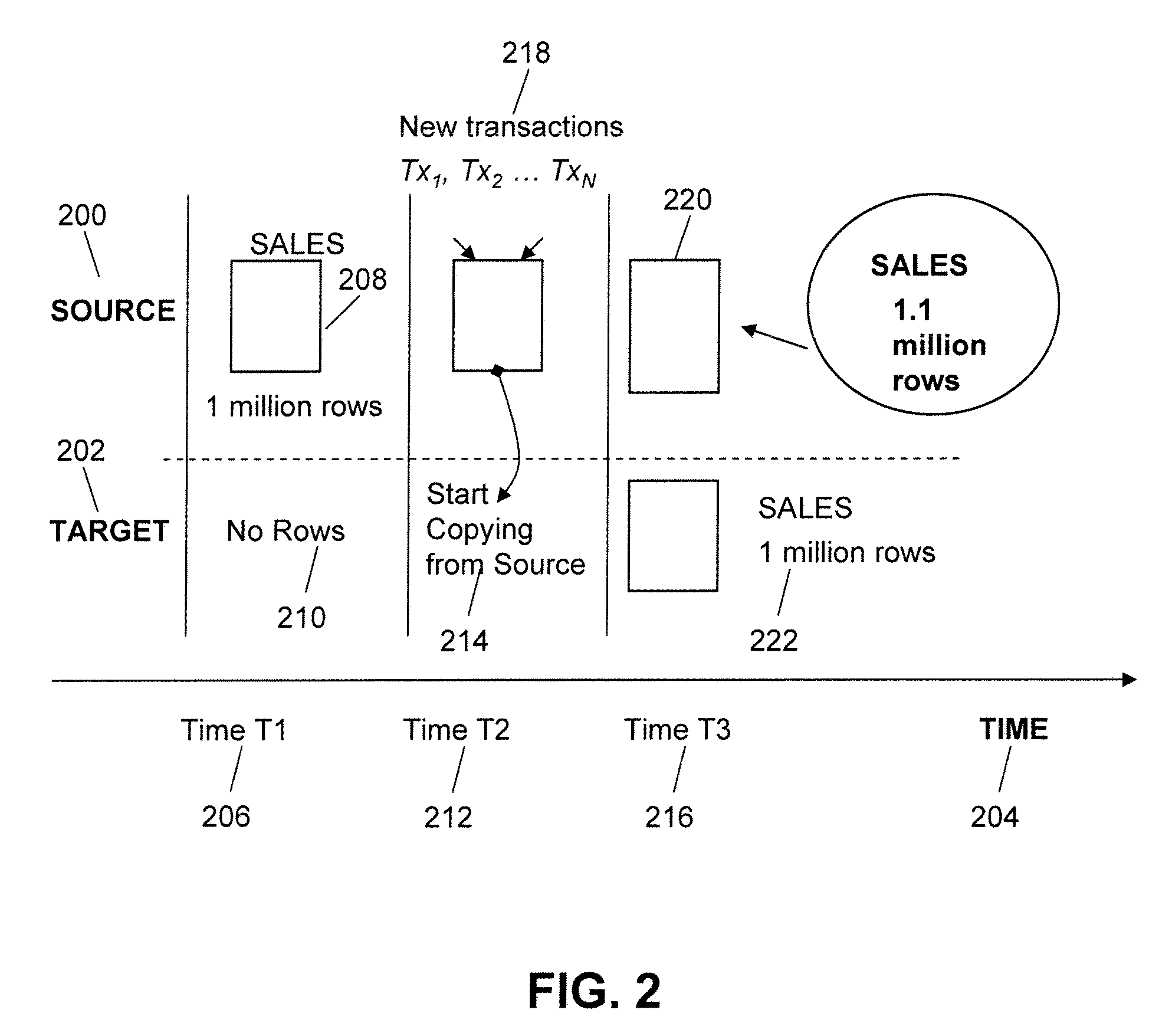

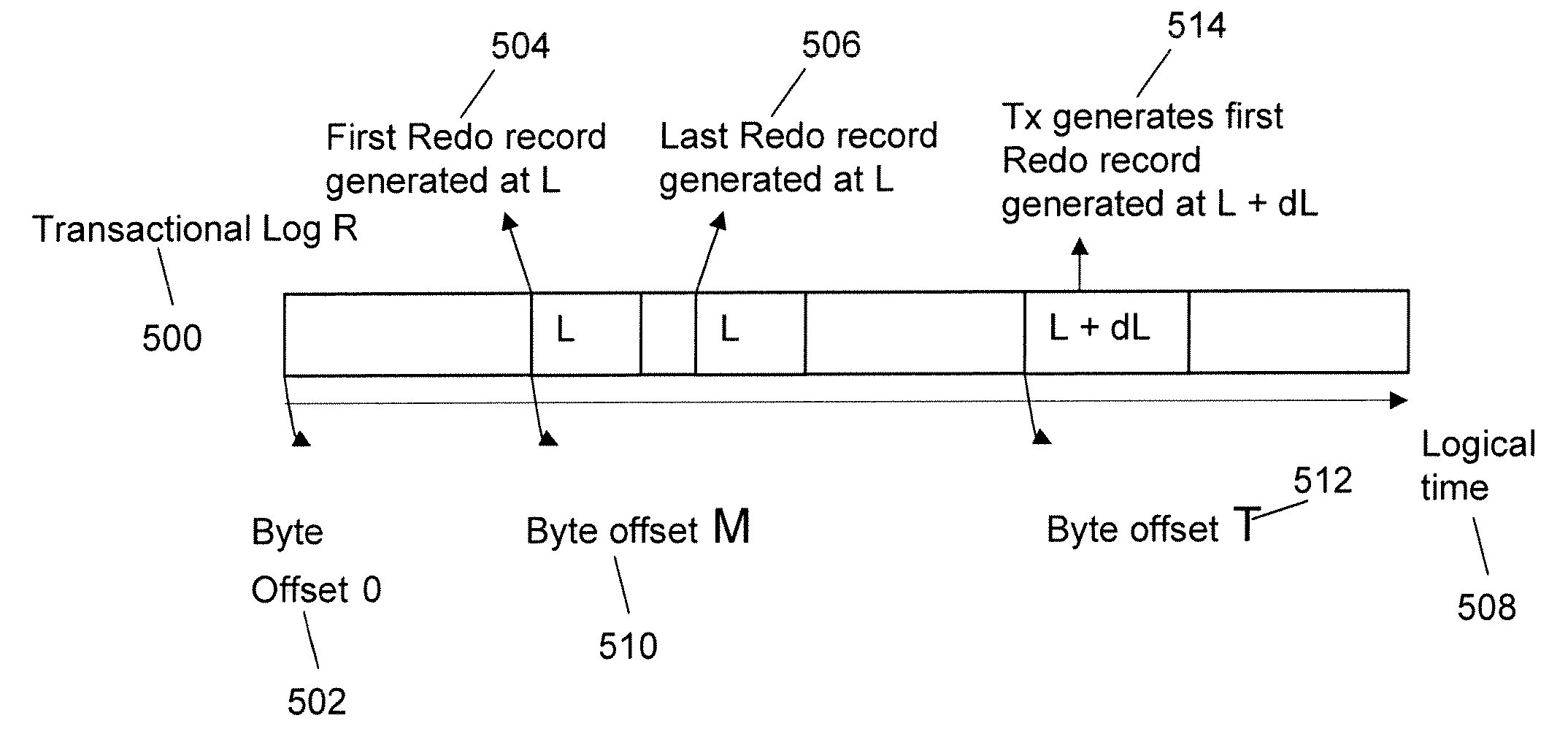

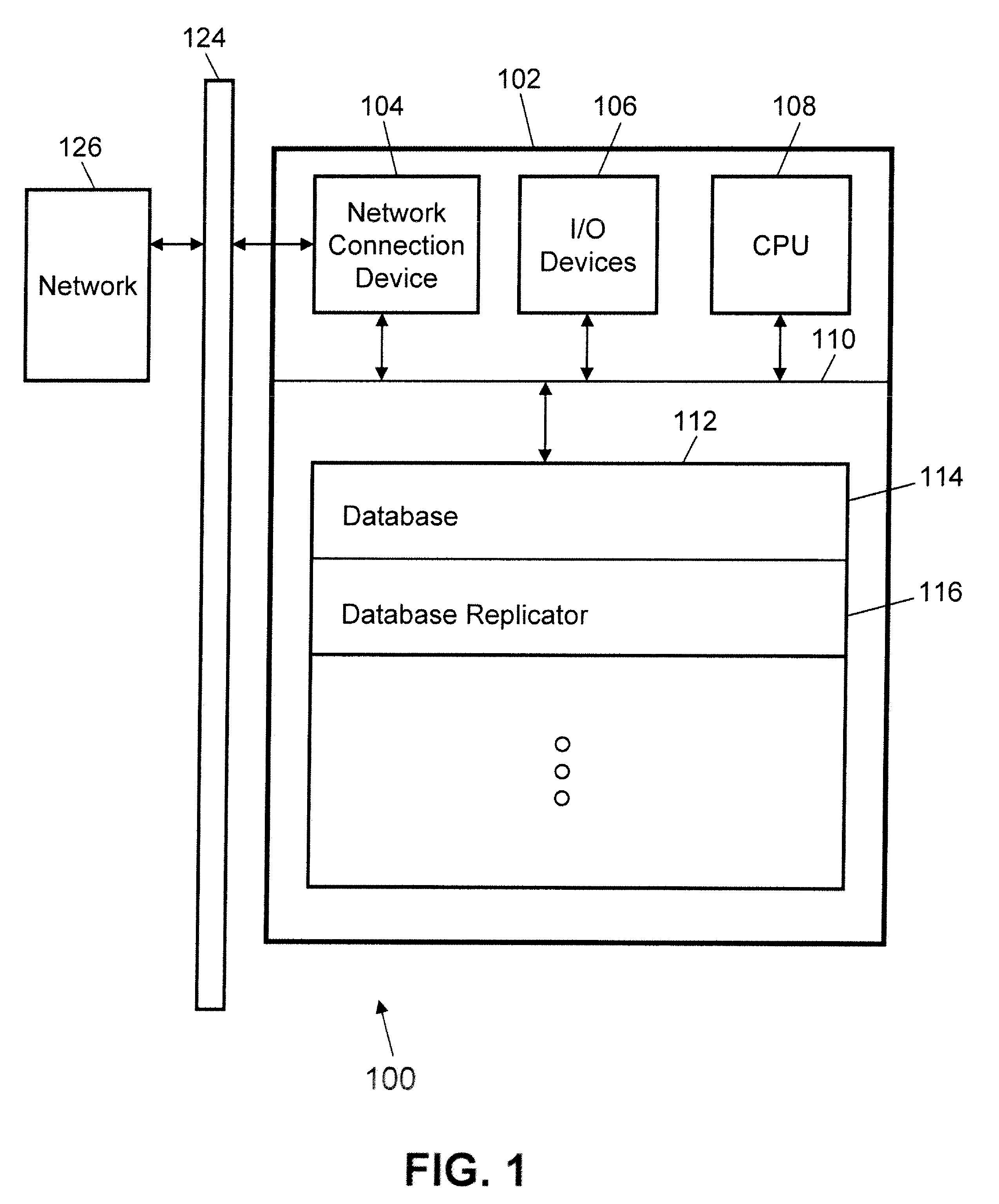

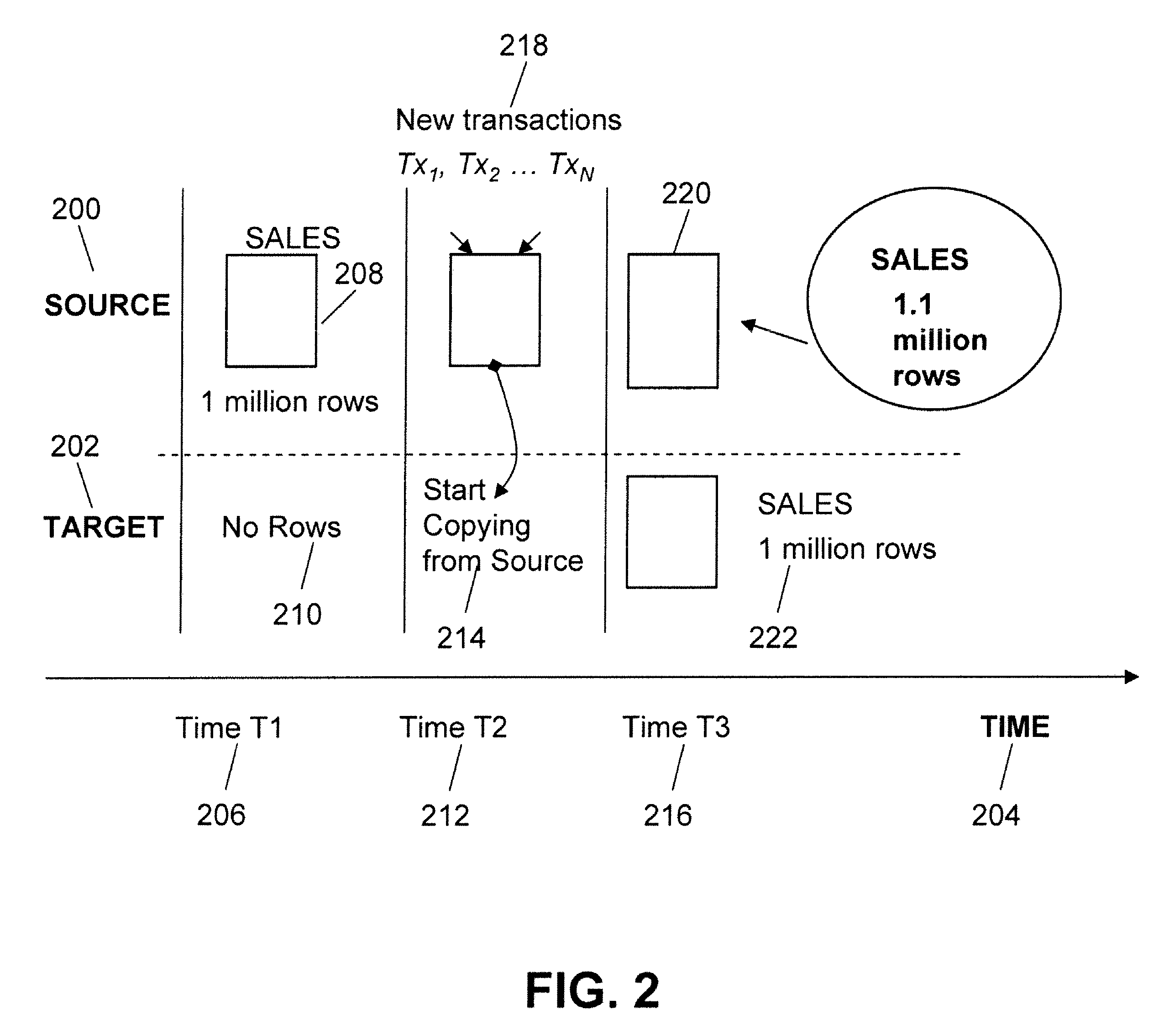

A method of processing data includes identifying a capture redo byte address, initiating a capture process at the capture redo byte address, creating a clone of a source database to a logical change number, and initiating an apply process at a target database.

Owner:ORACLE INT CORP

Apparatus and method for creating a real time database replica

A method of processing data includes identifying a capture redo byte address, initiating a capture process at the capture redo byte address, creating a clone of a source database to a logical change number, and initiating an apply process at a target database.

Owner:ORACLE INT CORP

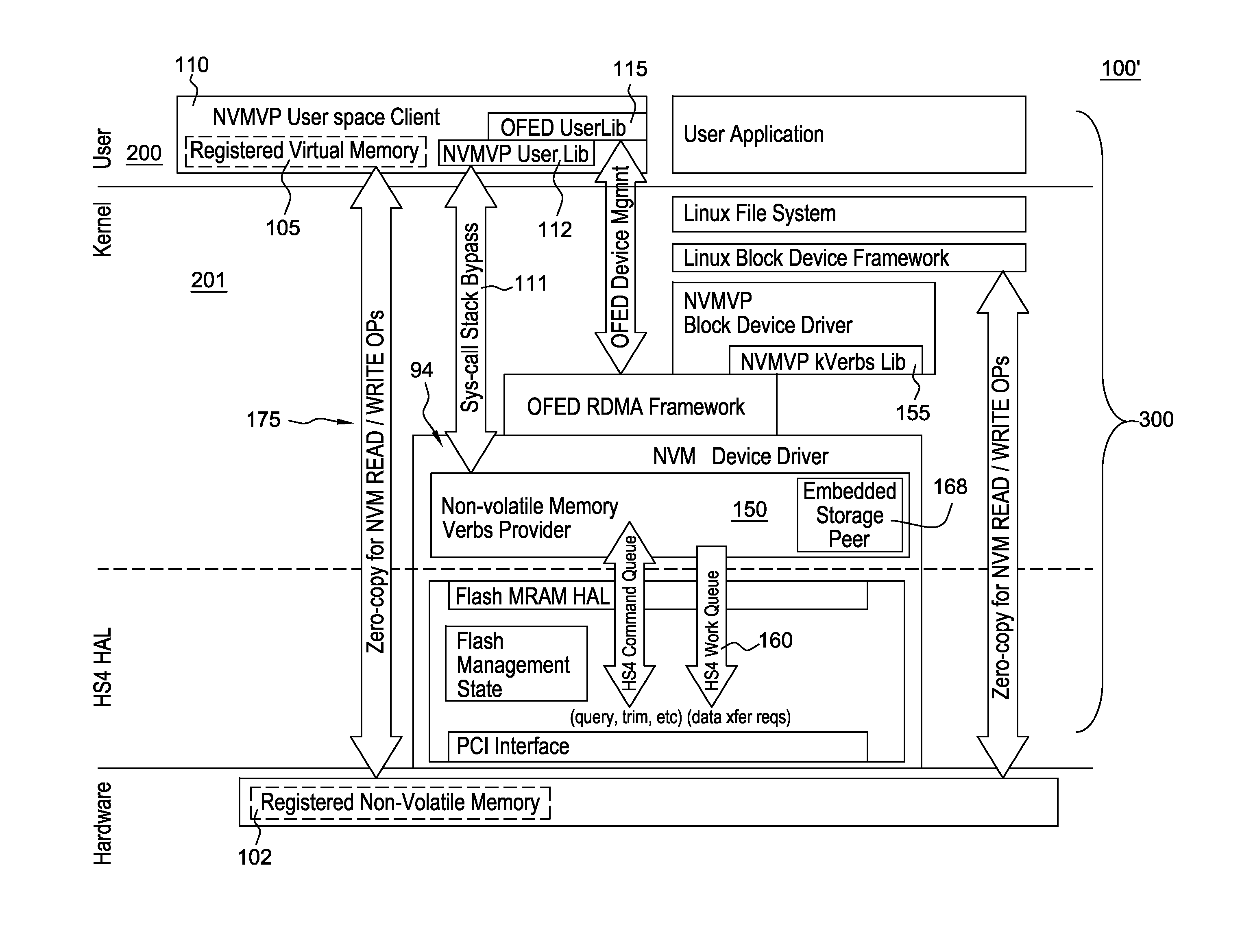

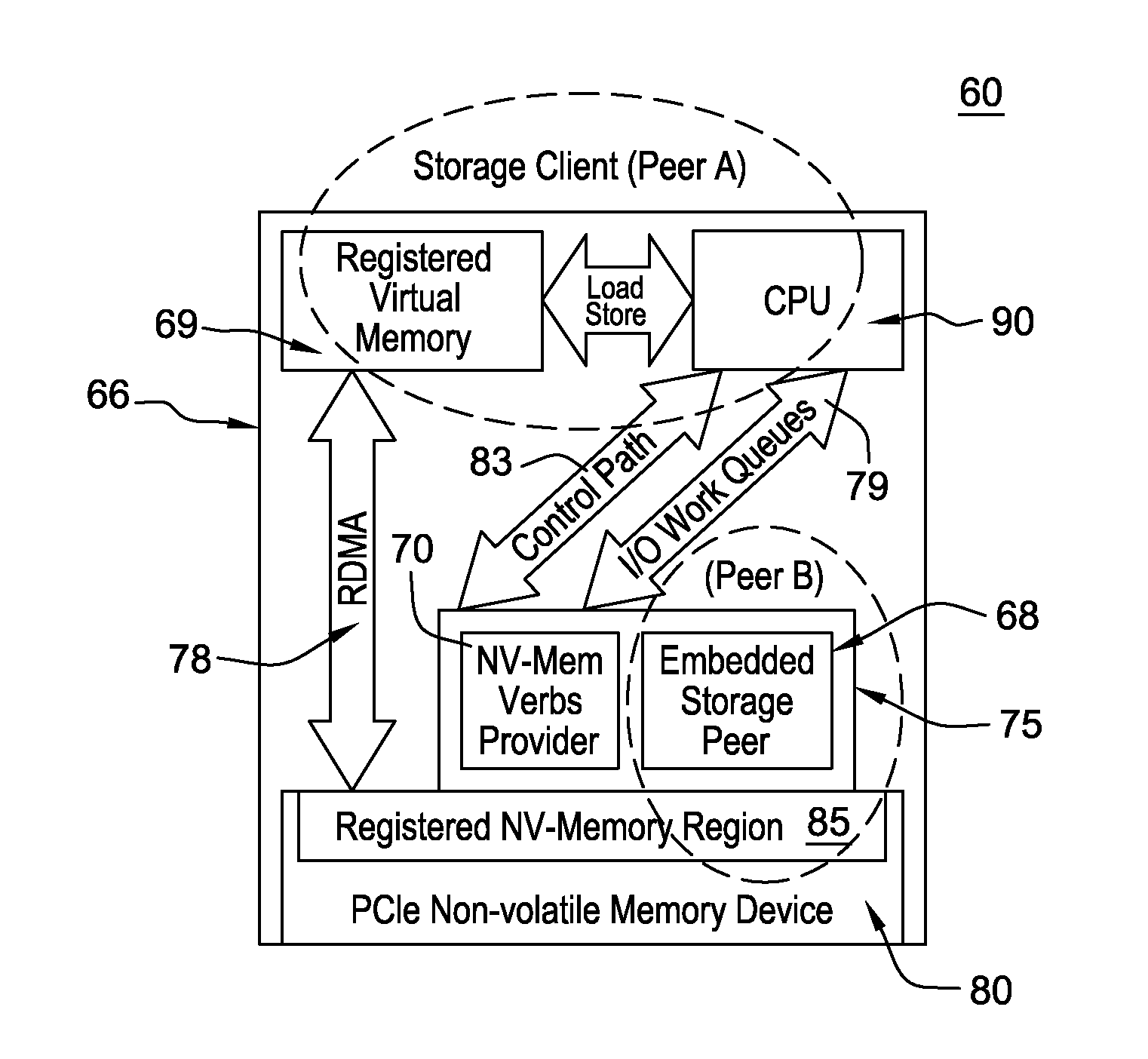

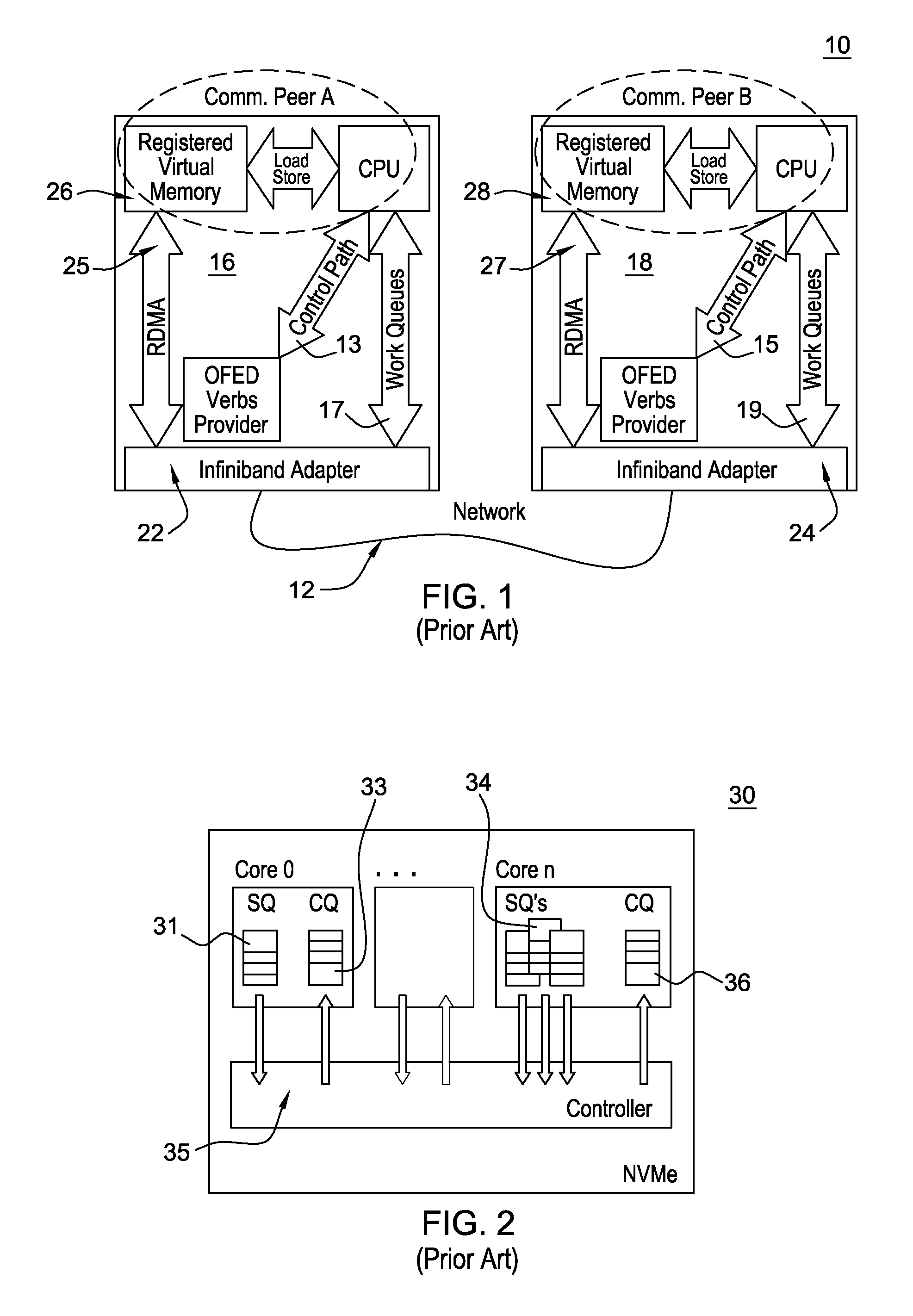

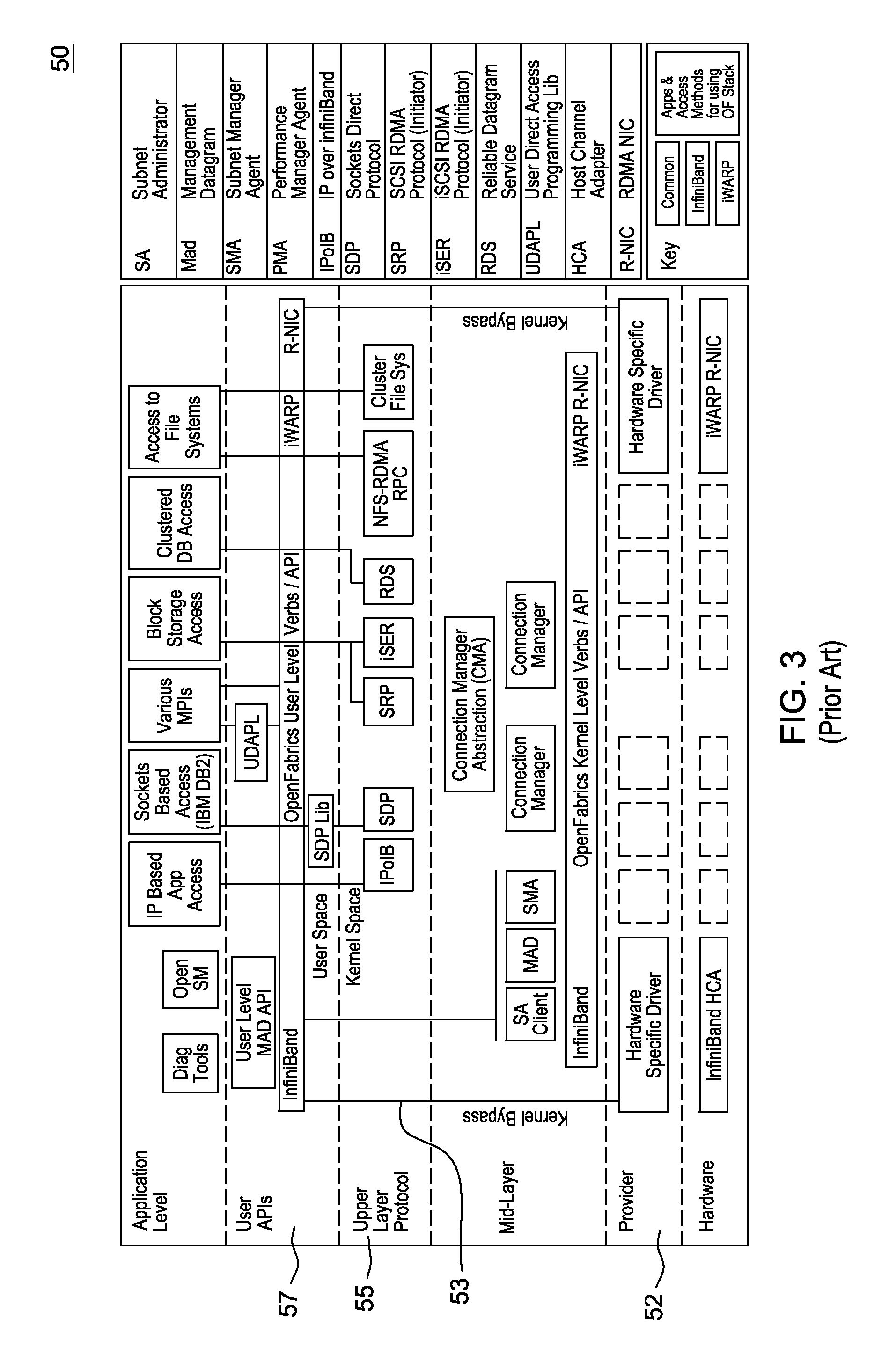

Local direct storage class memory access

ActiveUS20140317336A1Reduce the burden onEasy accessMemory adressing/allocation/relocationTransmissionZero-copyGranularity

A queued, byte addressed system and method for accessing flash memory and other non-volatile storage class memory, and potentially other types of non-volatile memory (NVM) storage systems. In a host device, e.g., a standalone or networked computer, having attached NVM device storage integrated into a switching fabric wherein the NVM device appears as an industry standard OFED™ RDMA verbs provider. The verbs provider enables communicating with a ‘local storage peer’ using the existing OpenFabrics RDMA host functionality. User applications issue RDMA Read / Write directives to the ‘local peer (seen as a persistent storage) in NVM enabling NVM memory access at byte granularity. The queued, byte addressed system and method provides for Zero copy NVM access. The methods enables operations that establish application private Queue Pairs to provide asynchronous NVM memory access operations at byte level granularity.

Owner:GLOBALFOUNDRIES US INC

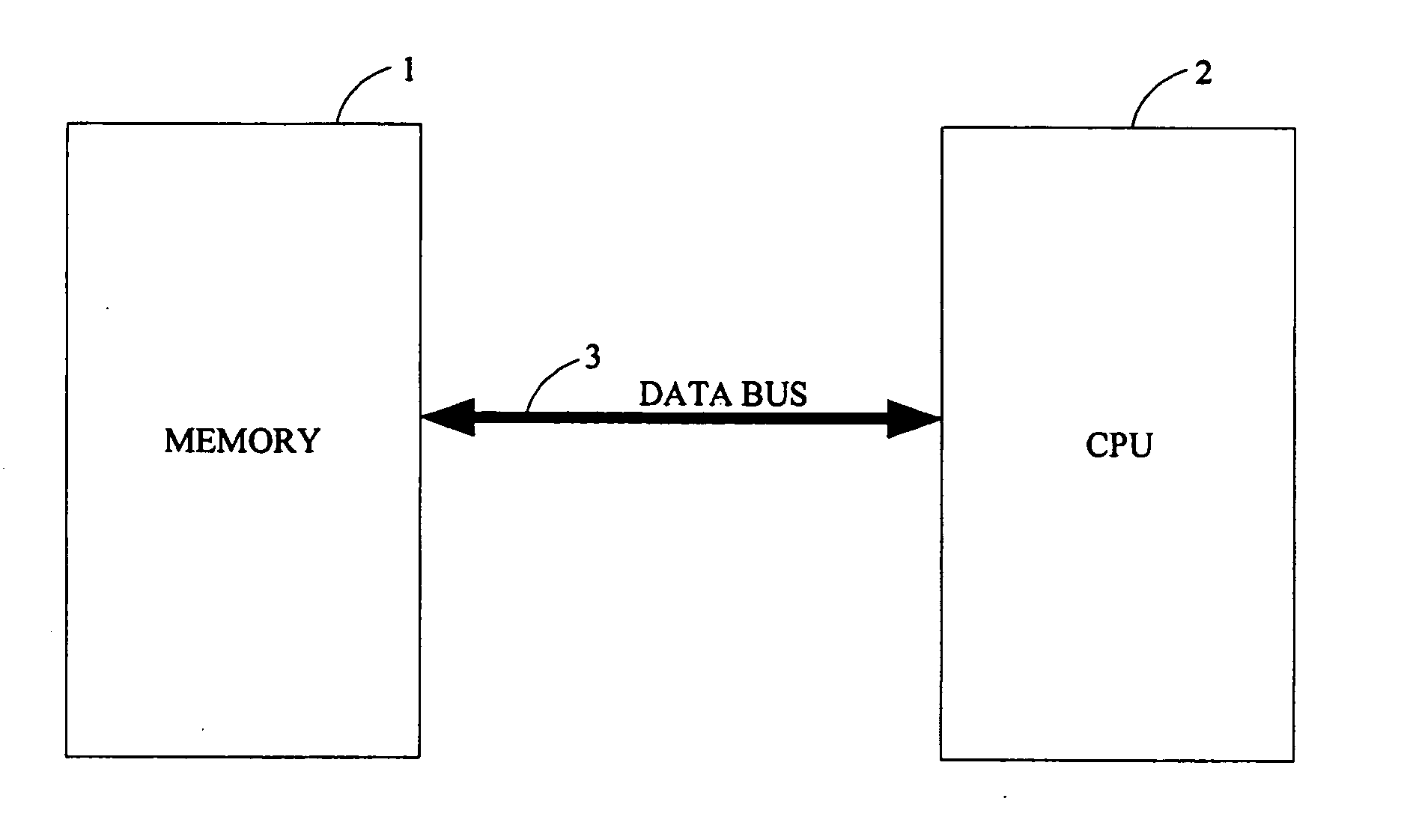

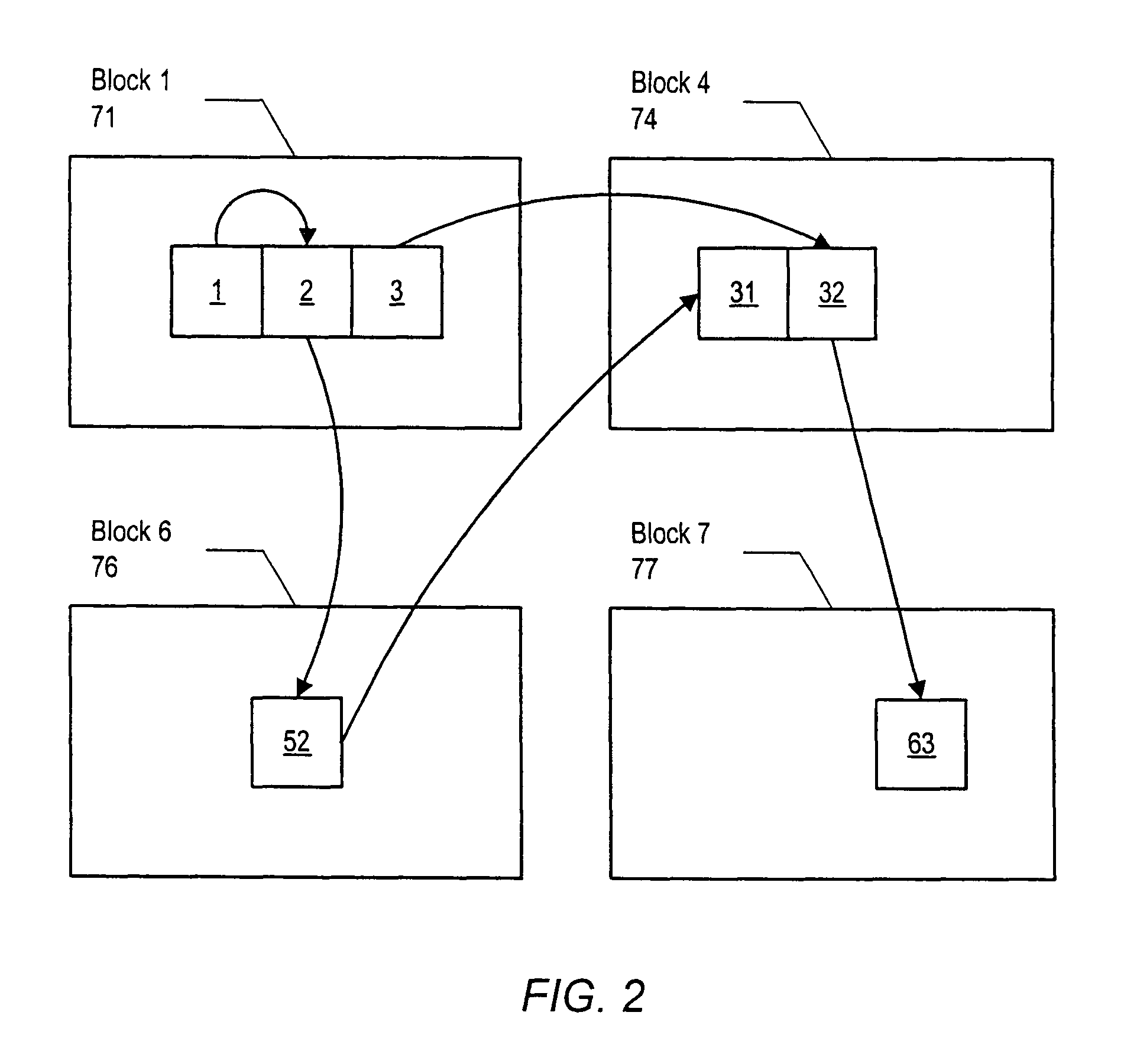

System and method for securely storing data in a memory

InactiveUS20050091569A1Ensure correctnessEnsure completenessCode conversionCoding detailsByte addressingTerm memory

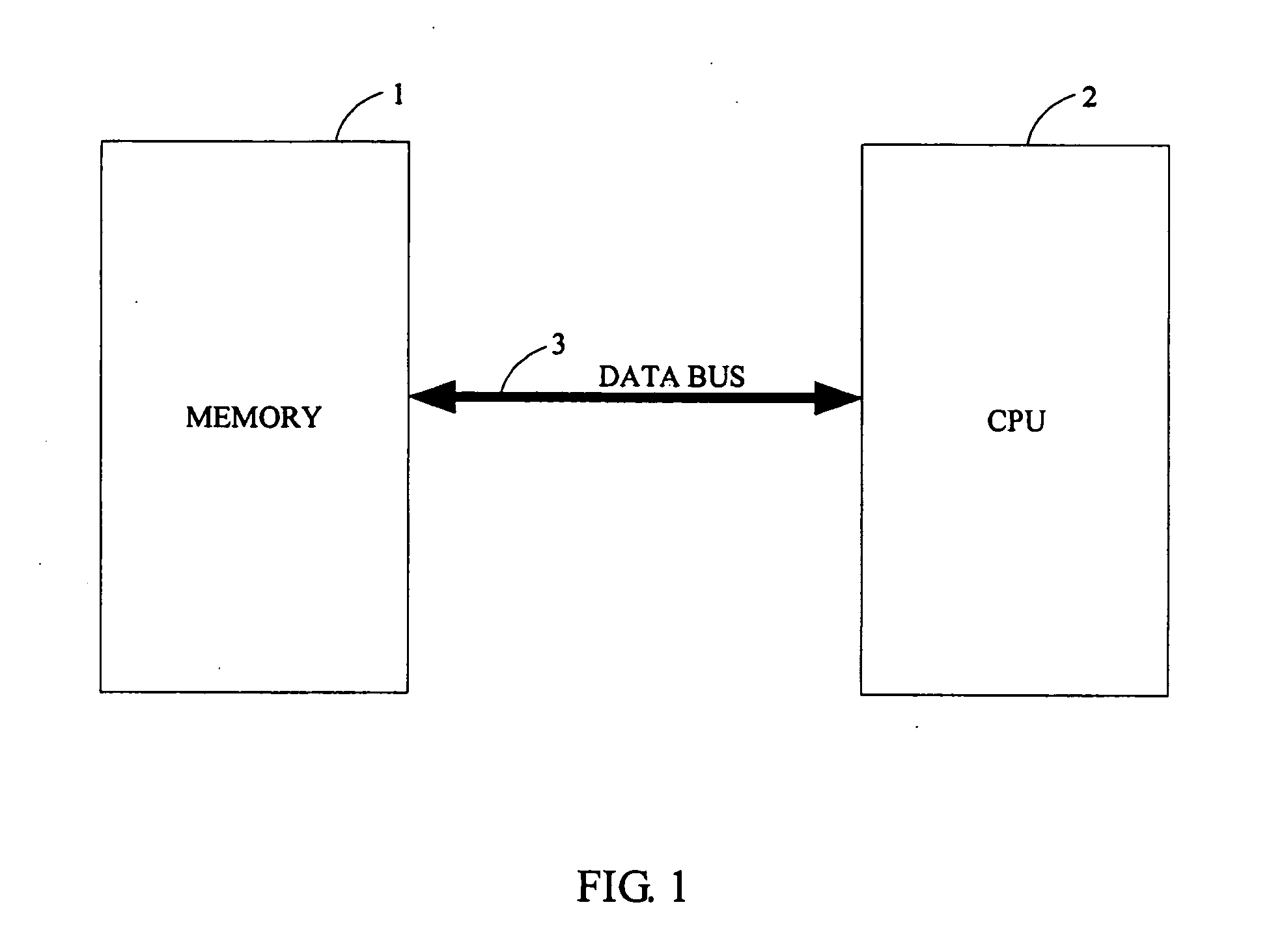

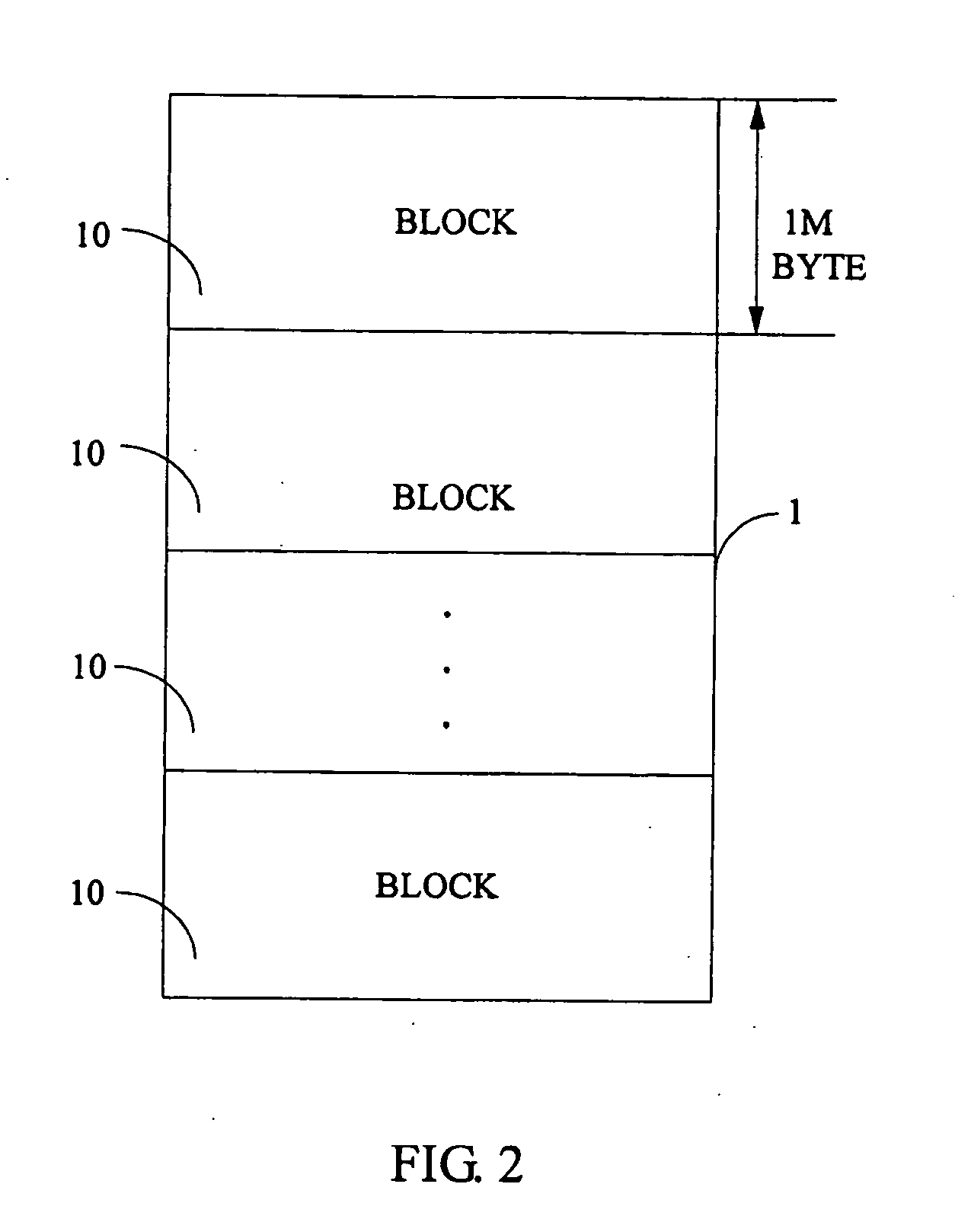

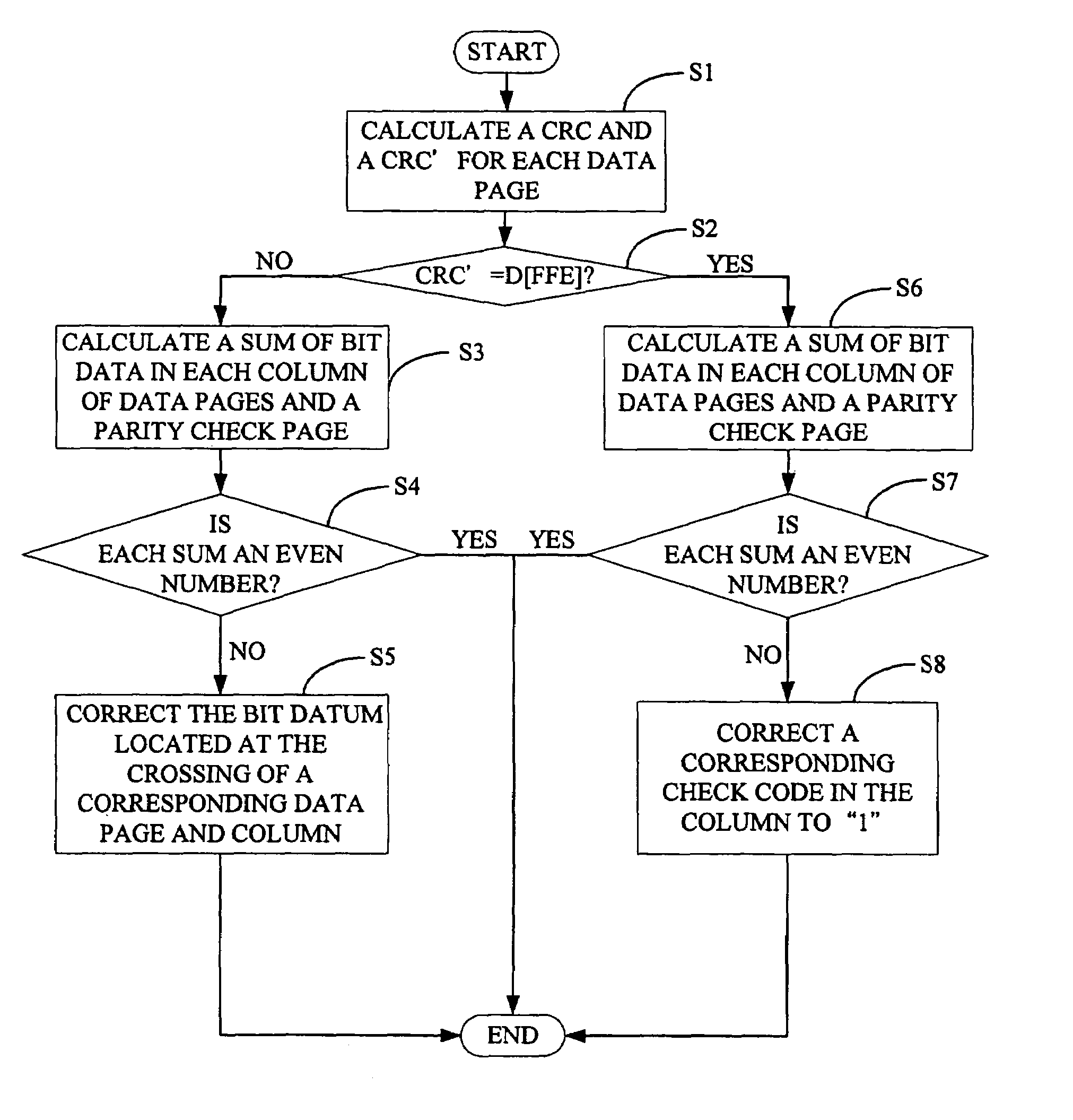

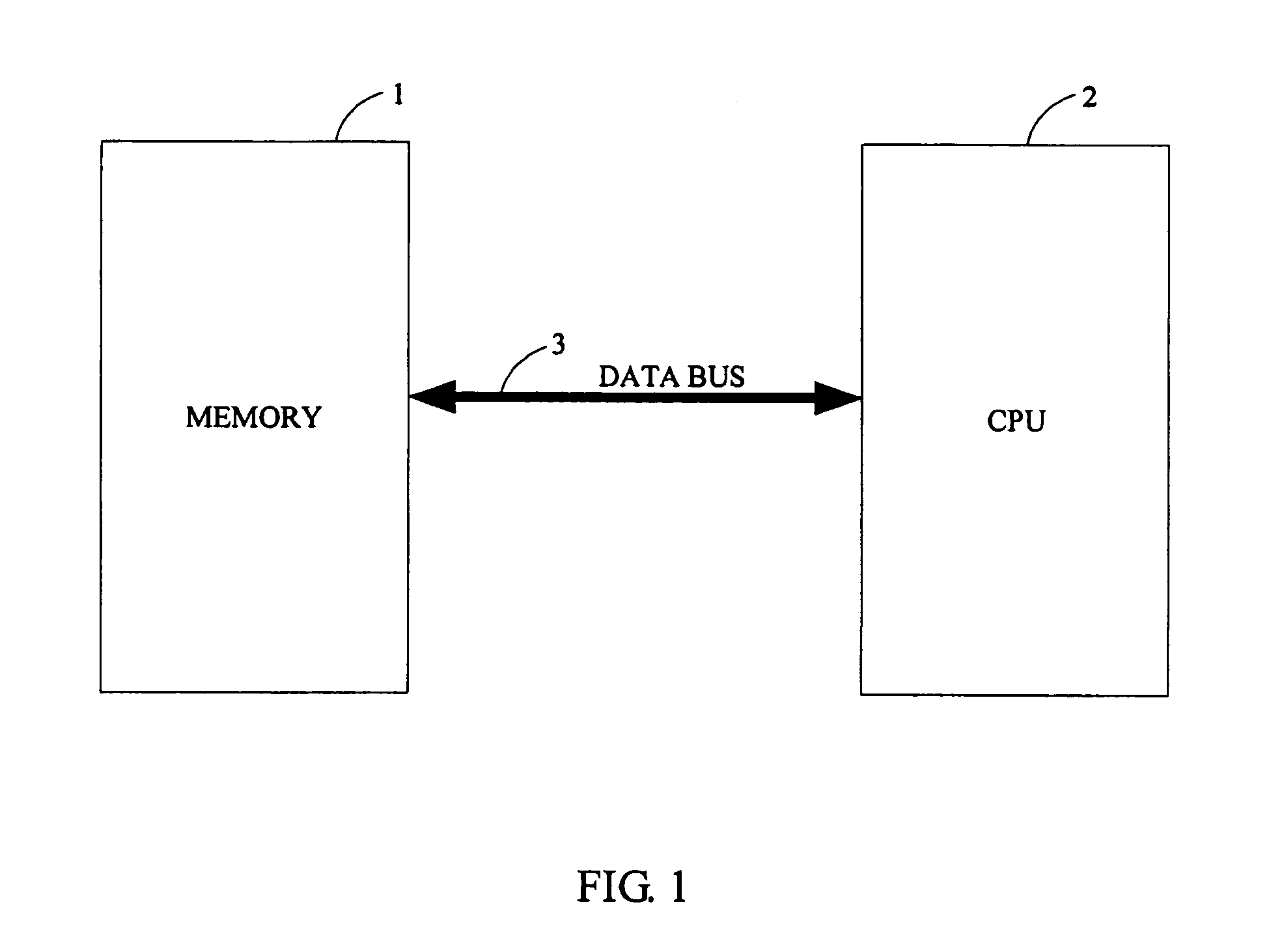

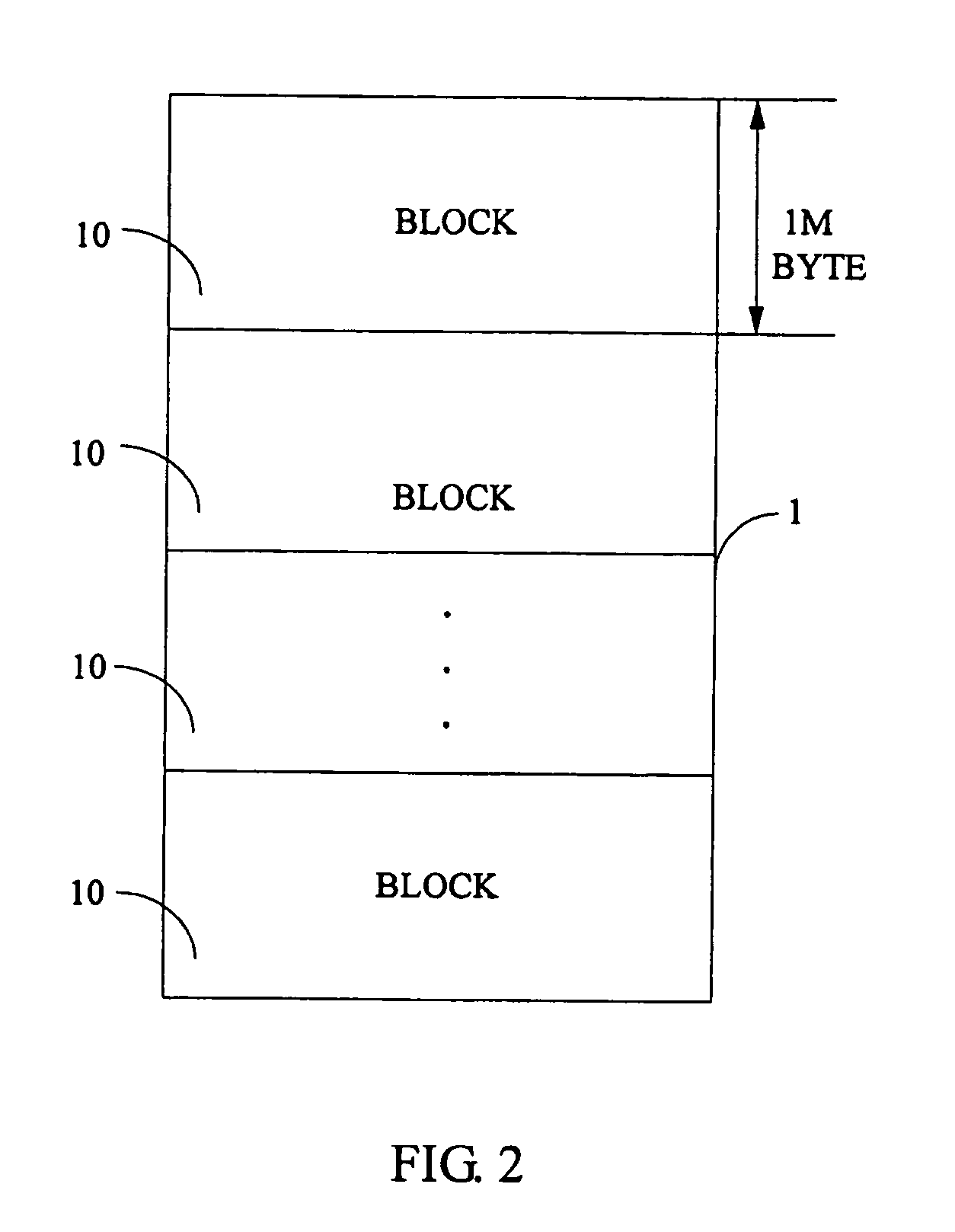

A system for securely storing data in a memory includes a memory (1) and a CPU (Central Processing Unit) (2). The memory is divided into a plurality of fixed-size blocks (10) for storing data. Each block includes a plurality of data pages (101), and a parity check page (102) storing check codes for checking and recovering byte data. Each data page includes a plurality of byte addresses for storing byte data including a CRC (Cyclic Redundancy Check), and a complement of the CRC in the hexadecimal system expressed as CRC′. The CPU is for calculating a CRC for each data page according to byte data of the data page, calculating a CRC′ based on the CRC of the data page, and for identifying and correcting any incorrect bit data. A related method is also disclosed.

Owner:CLOUD NETWORK TECH SINGAPORE PTE LTD

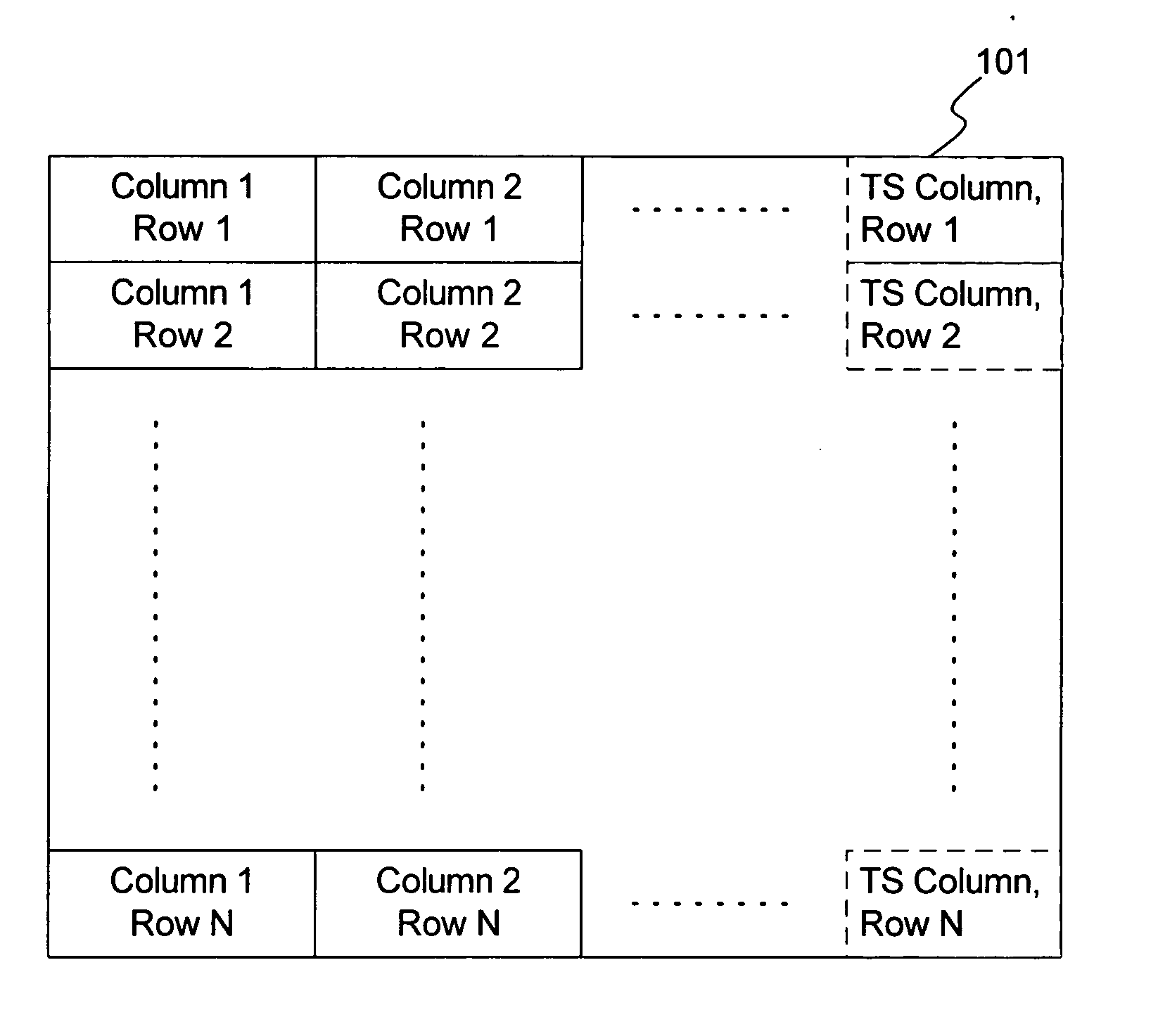

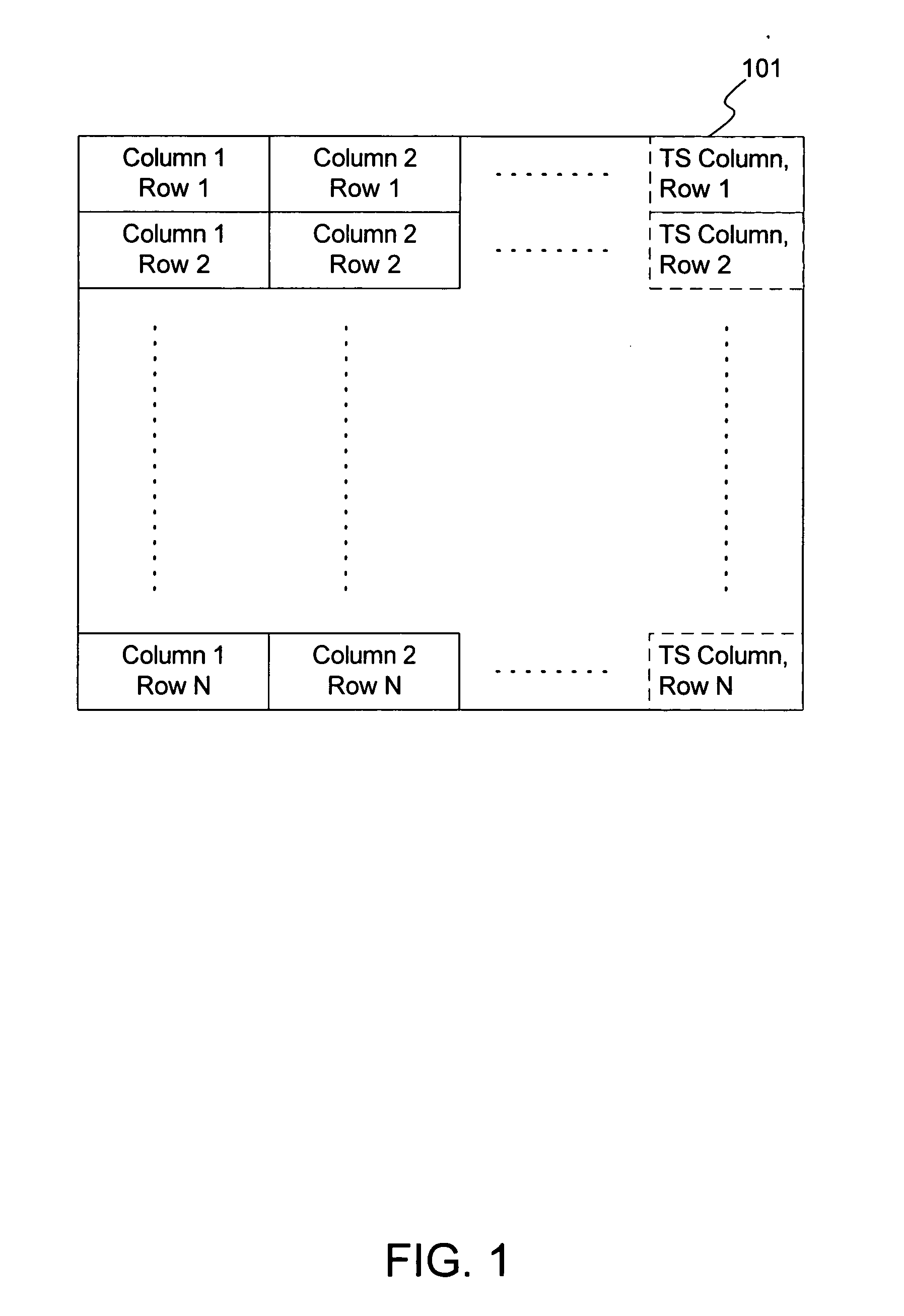

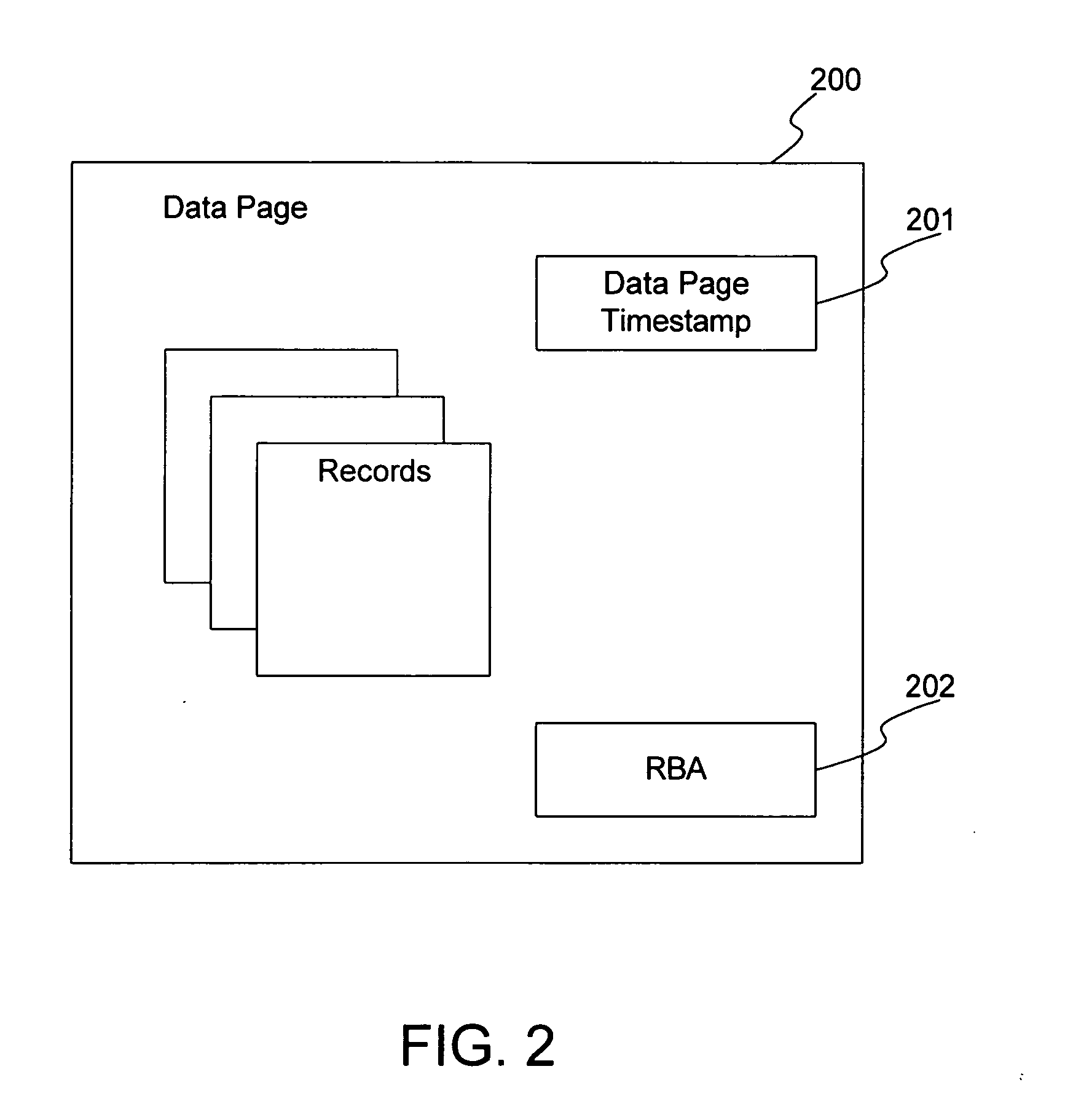

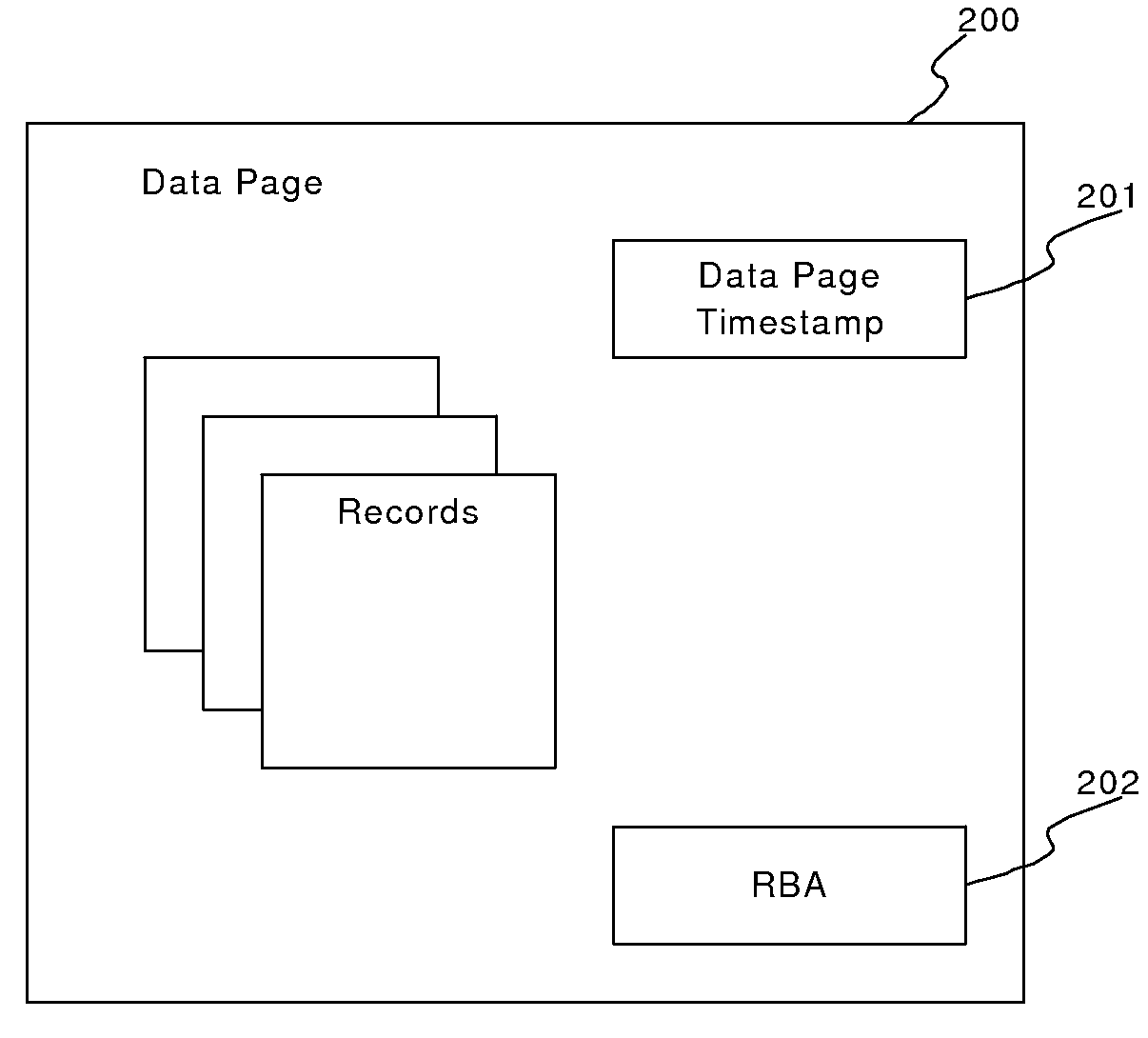

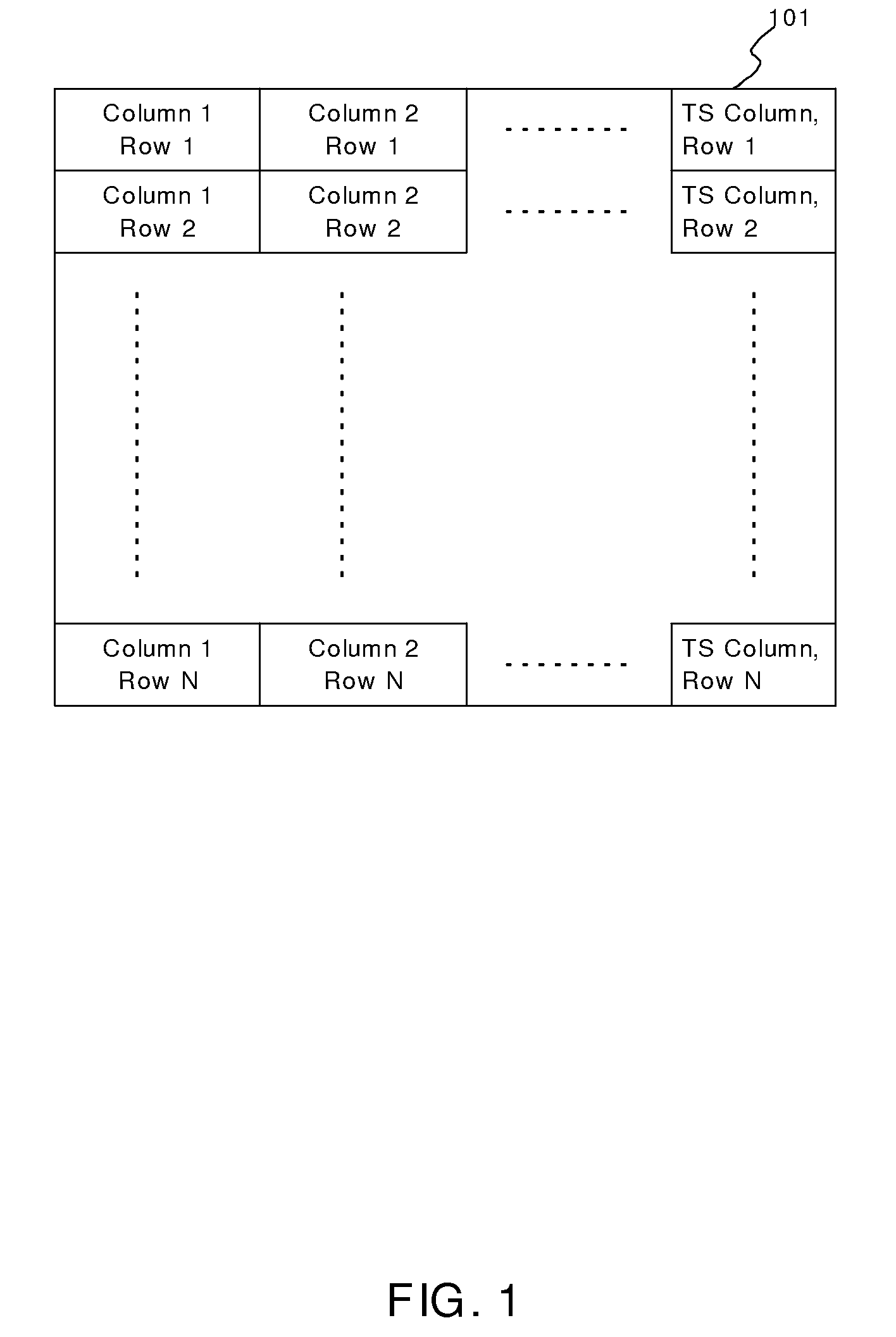

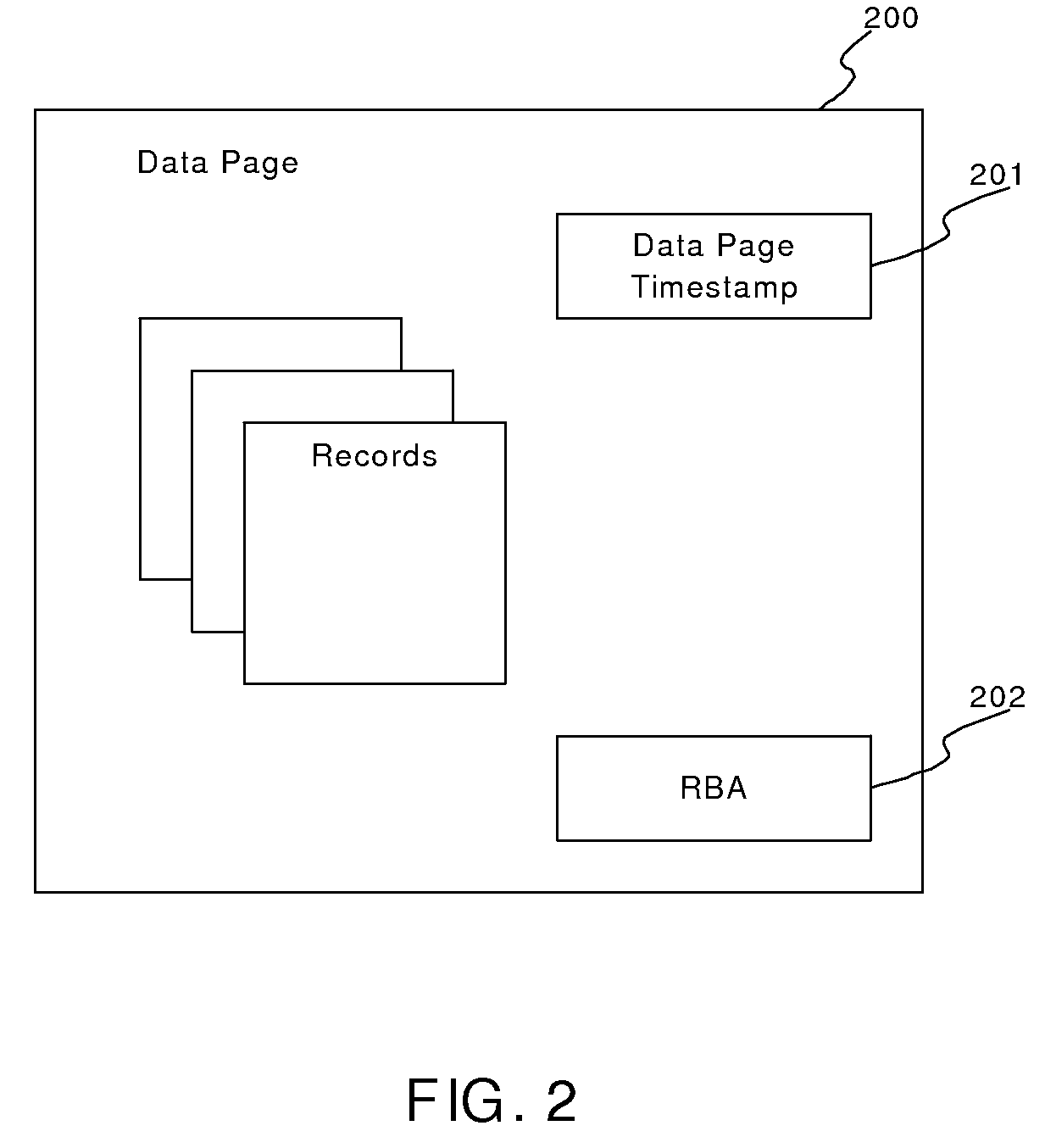

Low-overhead built-in timestamp column for relational database systems

InactiveUS20050177590A1Ensure availabilityUseful or even desirableRelational databasesSpecial data processing applicationsTimestampRelational database

An improved automatically updated timestamp for database systems is disclosed. The automatically updated timestamp can be provided in a hidden timestamp column for a table, where the value of the timestamp column can be retrieved with a query that calls the column by name. Optionally, the timestamp column can be provided for each table in the database system to ensure its availability to applications. For cases where a timestamp for each row in a table is not desired, an automatically updated timestamp can be provided for a data page. This timestamp can be retrieved from an update timestamp recorded on disk and in the buffer pool or from a log relative byte address. Although this is a page-level timestamp, its use may be desirable for infrequently updated tables or where space on the disk and buffer pool is at a premium.

Owner:IBM CORP

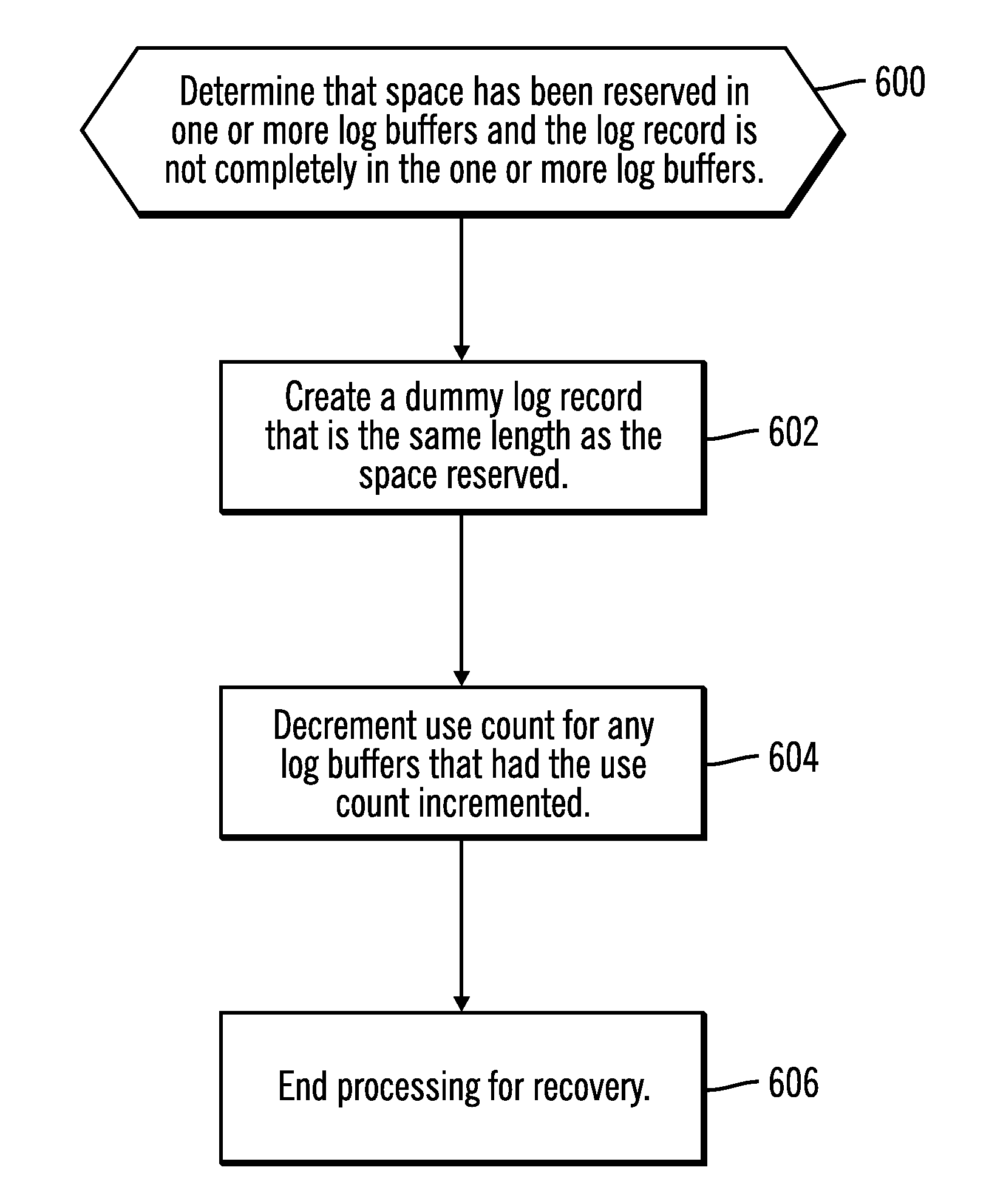

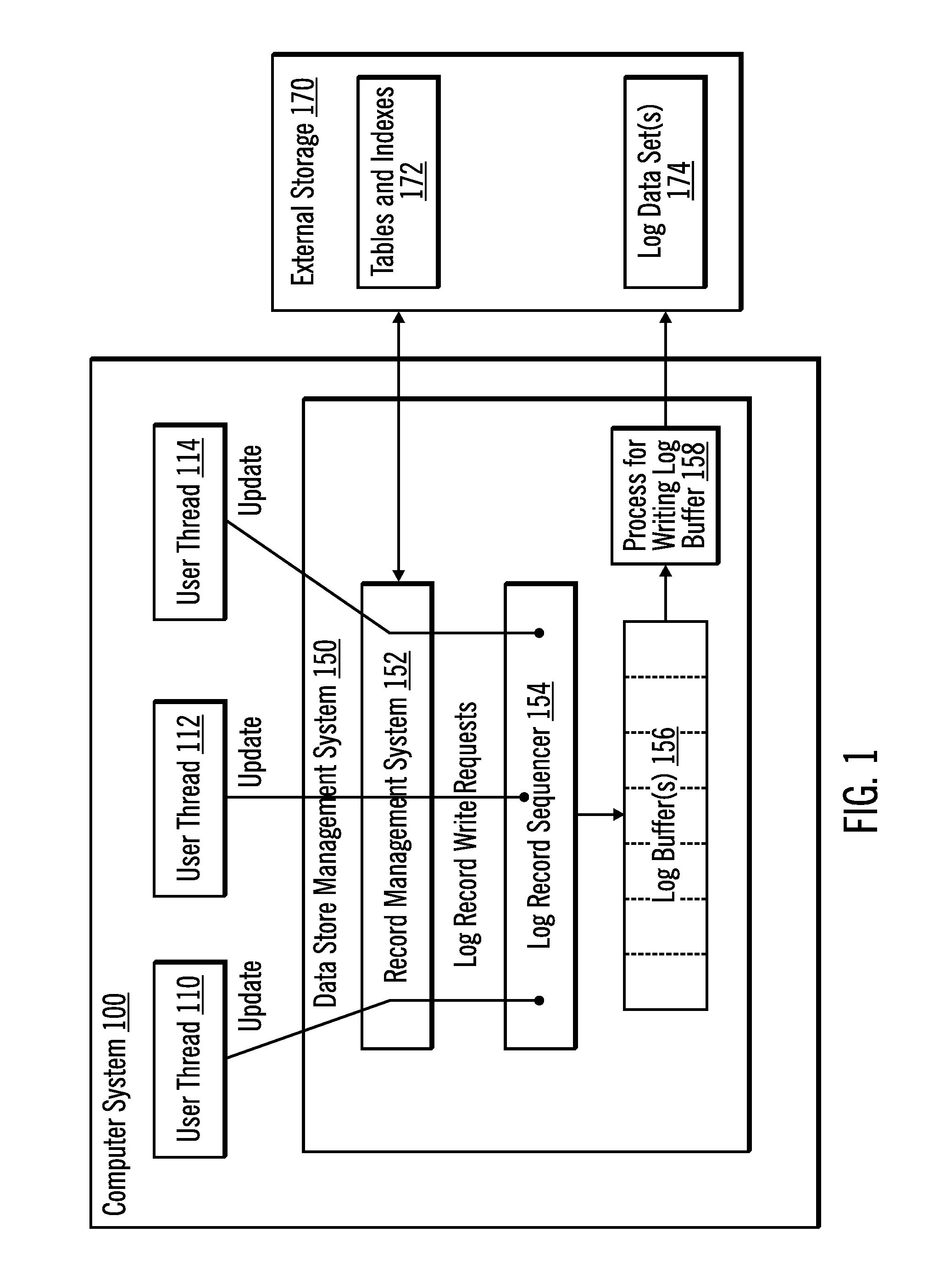

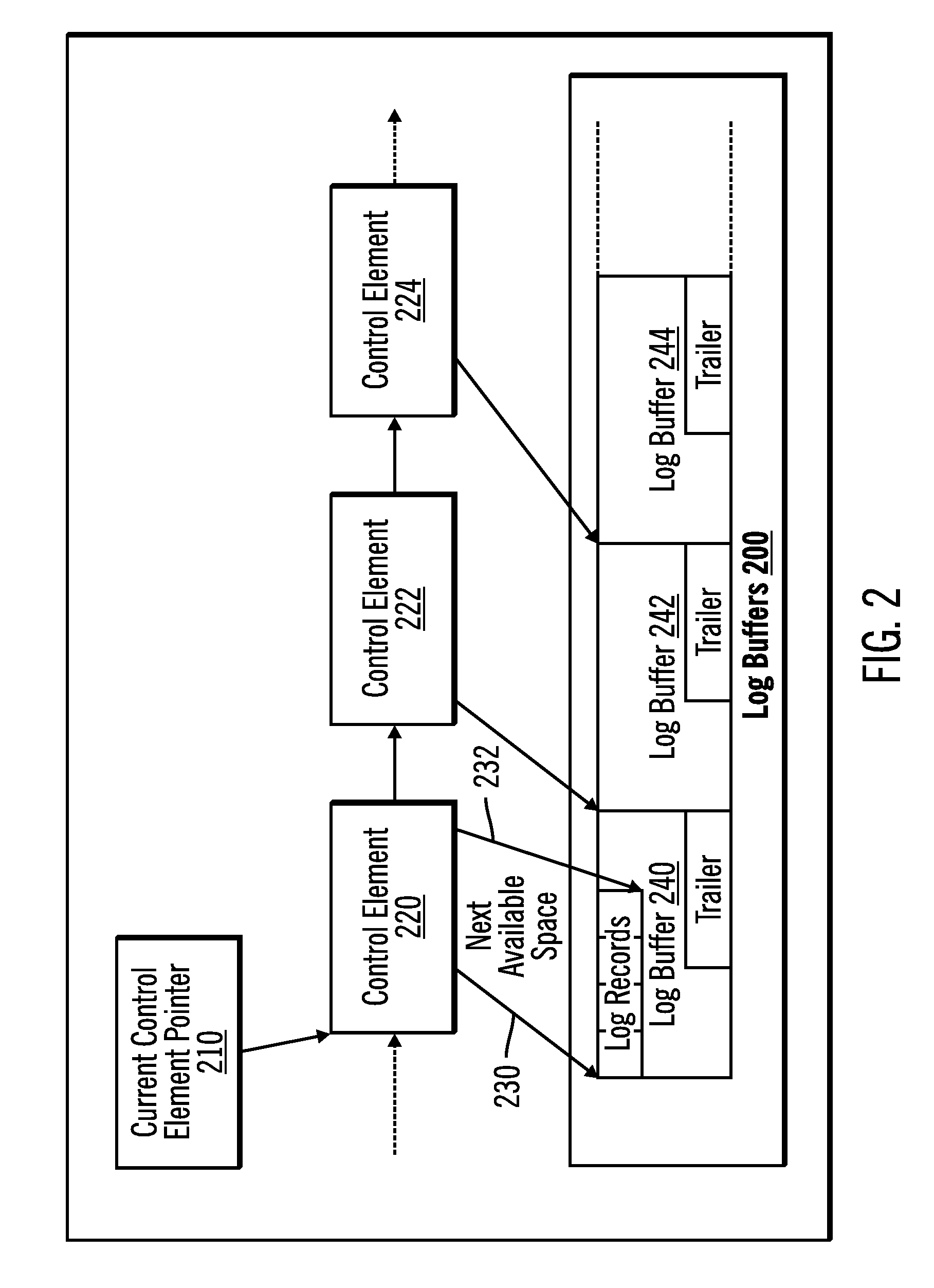

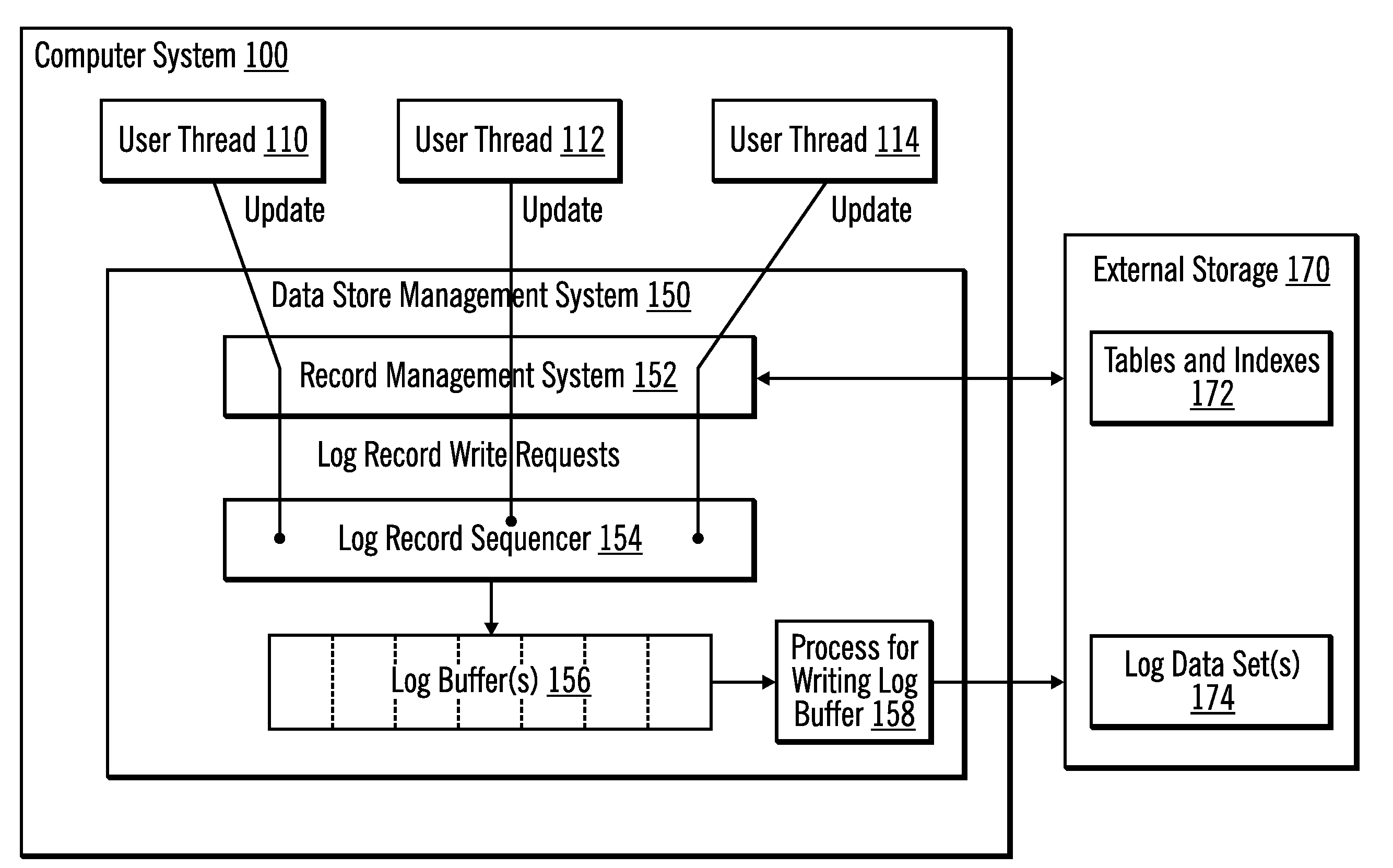

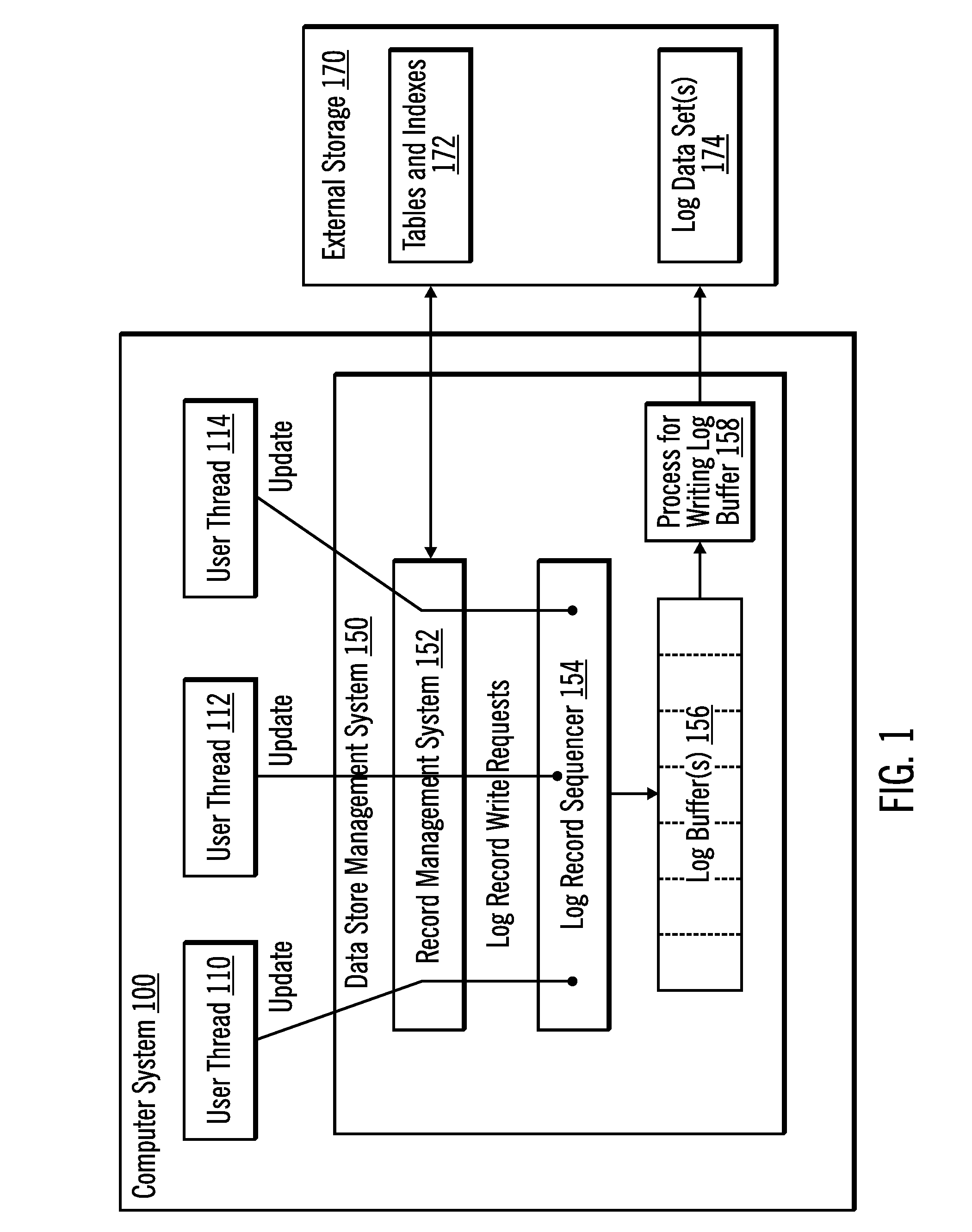

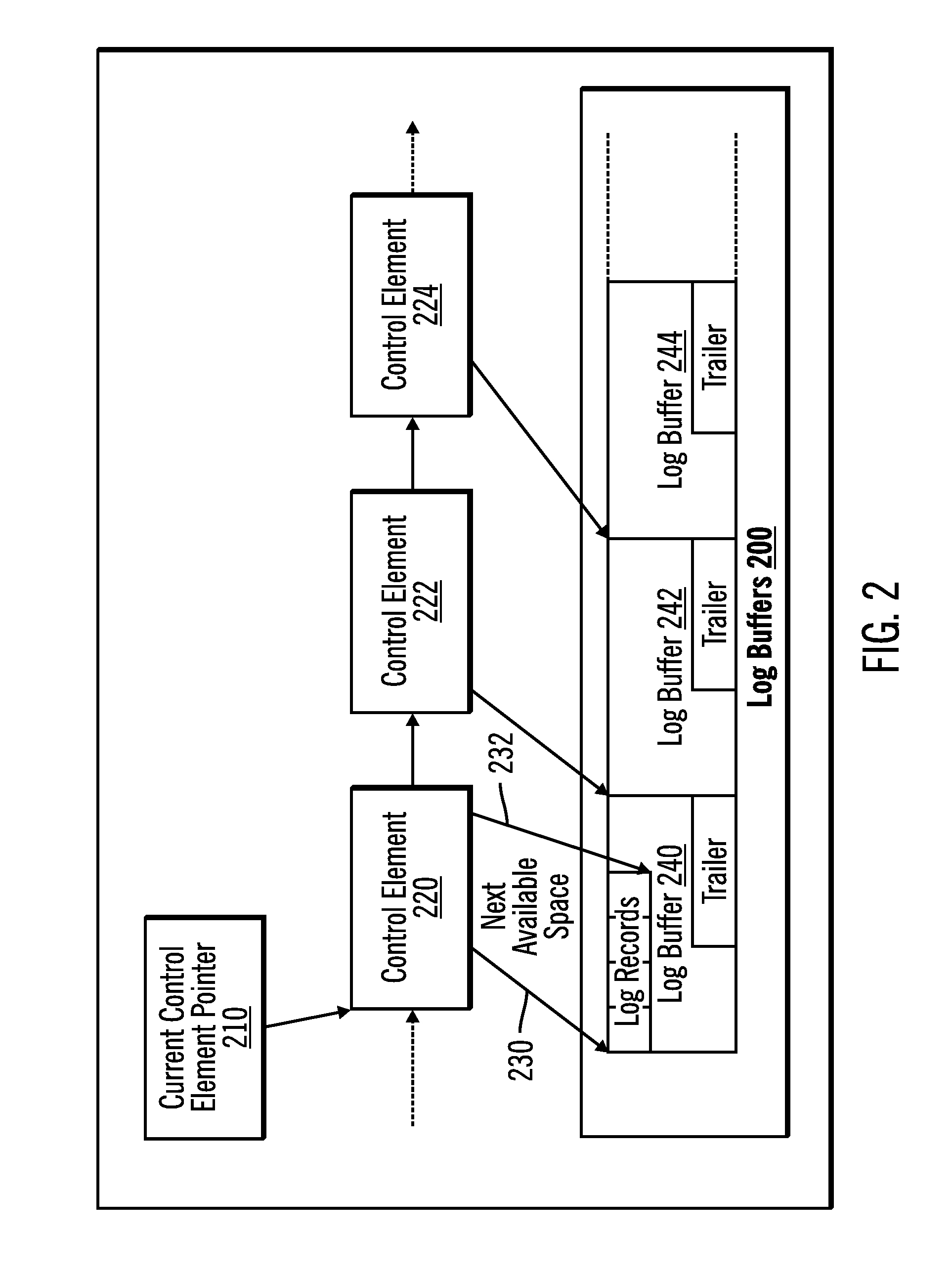

Creating and maintaining order of a log stream without use of a lock or latch

InactiveUS20120096055A1Digital data information retrievalSpecial data processing applicationsByte addressingByte

Provided are techniques for using a series of compare and swap operations to assign a Relative Byte Address (RBA) and a Logical Record Sequence Number (LRSN) to a log record. One or more log buffers for storing the log record are identified, and the log record is moved to the one or more log buffers.

Owner:IBM CORP

System and method for securely storing data in a memory

InactiveUS7213191B2Ensure correctnessEnsure completenessCode conversionError correction/detection by combining multiple code structuresByte addressingByte

A system for securely storing data in a memory includes a memory (1) and a CPU (Central Processing Unit) (2). The memory is divided into a plurality of fixed-size blocks (10) for storing data. Each block includes a plurality of data pages (101), and a parity check page (102) storing check codes for checking and recovering byte data. Each data page includes a plurality of byte addresses for storing byte data including a CRC (Cyclic Redundancy Check), and a complement of the CRC in the hexadecimal system expressed as CRC′. The CPU is for calculating a CRC for each data page according to byte data of the data page, calculating a CRC′ based on the CRC of the data page, and for identifying and correcting any incorrect bit data. A related method is also disclosed.

Owner:CLOUD NETWORK TECH SINGAPORE PTE LTD

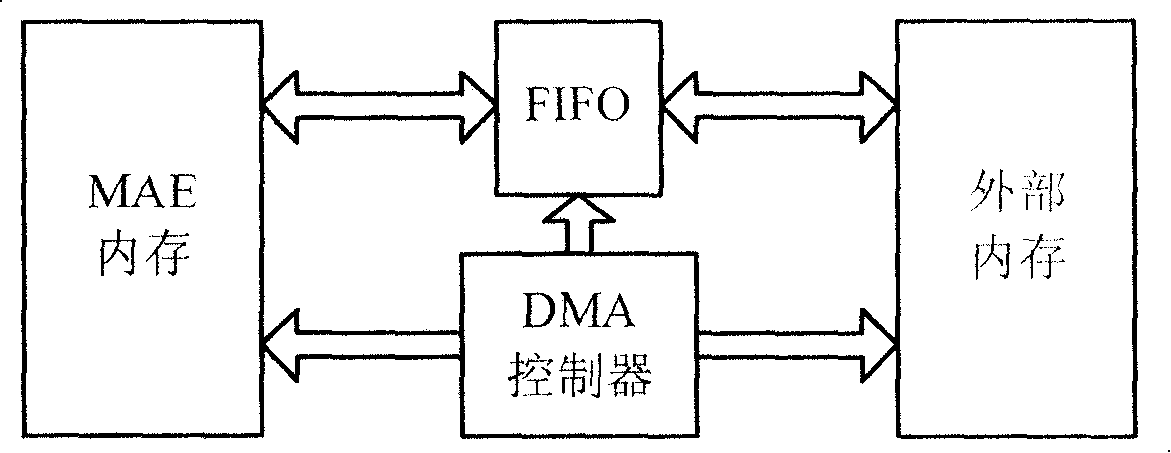

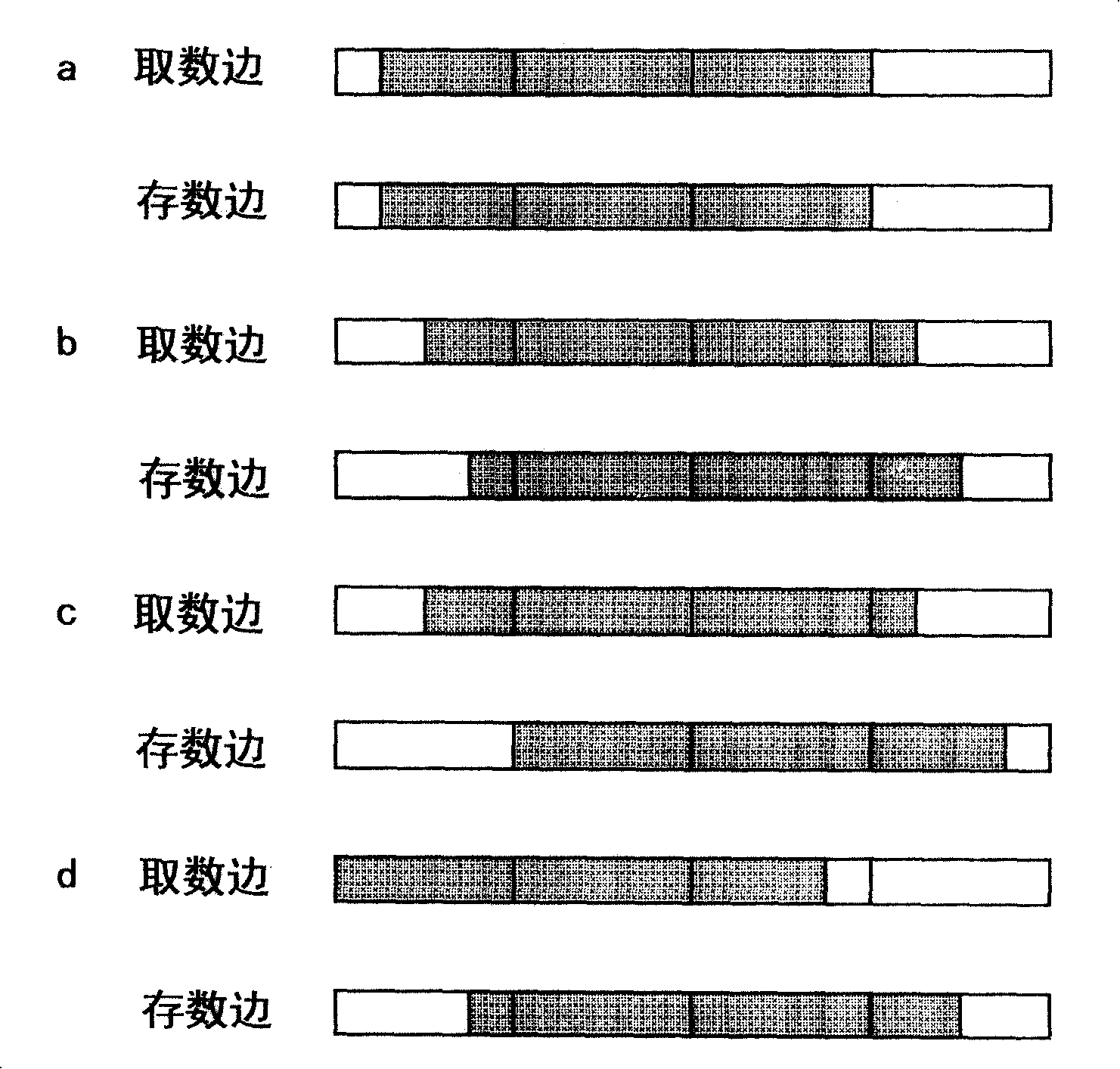

Optimized two-dimension DMA transmission method especially for access to image block

InactiveCN101196860AGuaranteed correctnessFast transmissionElectric digital data processingAccess timeData access

The invention discloses a two-dimensional DMA method special for data optimization of MAE access image block, which can obviously accelerate the transmission speed of the image block when processing byte alignment and automatically fill up the subimage block data beyond the image boundary. The method mainly comprises the following steps: (1) gaining the initial work address of the actual poke and access of poke edge and access edge according to the leading byte addresses of the poke edge and the access edge; (2) gaining poke times of the poke edge and access times of the access edge according to the leading byte addresses of poke edge and access edge and transmit data in each row; (3) initializing the row counting value and line counting value of the poke edge and access edge; (4) reading data of poke edge and writing in adaptive FIFO; (5) writing data in the adaptive FIFO; (6) continuing to transmit the data in next row if the adaptive FIFO is not full. The method can increase the transmission speed by four times and ensure the accuracy of data access.

Owner:无锡翔劲计算机科技有限公司

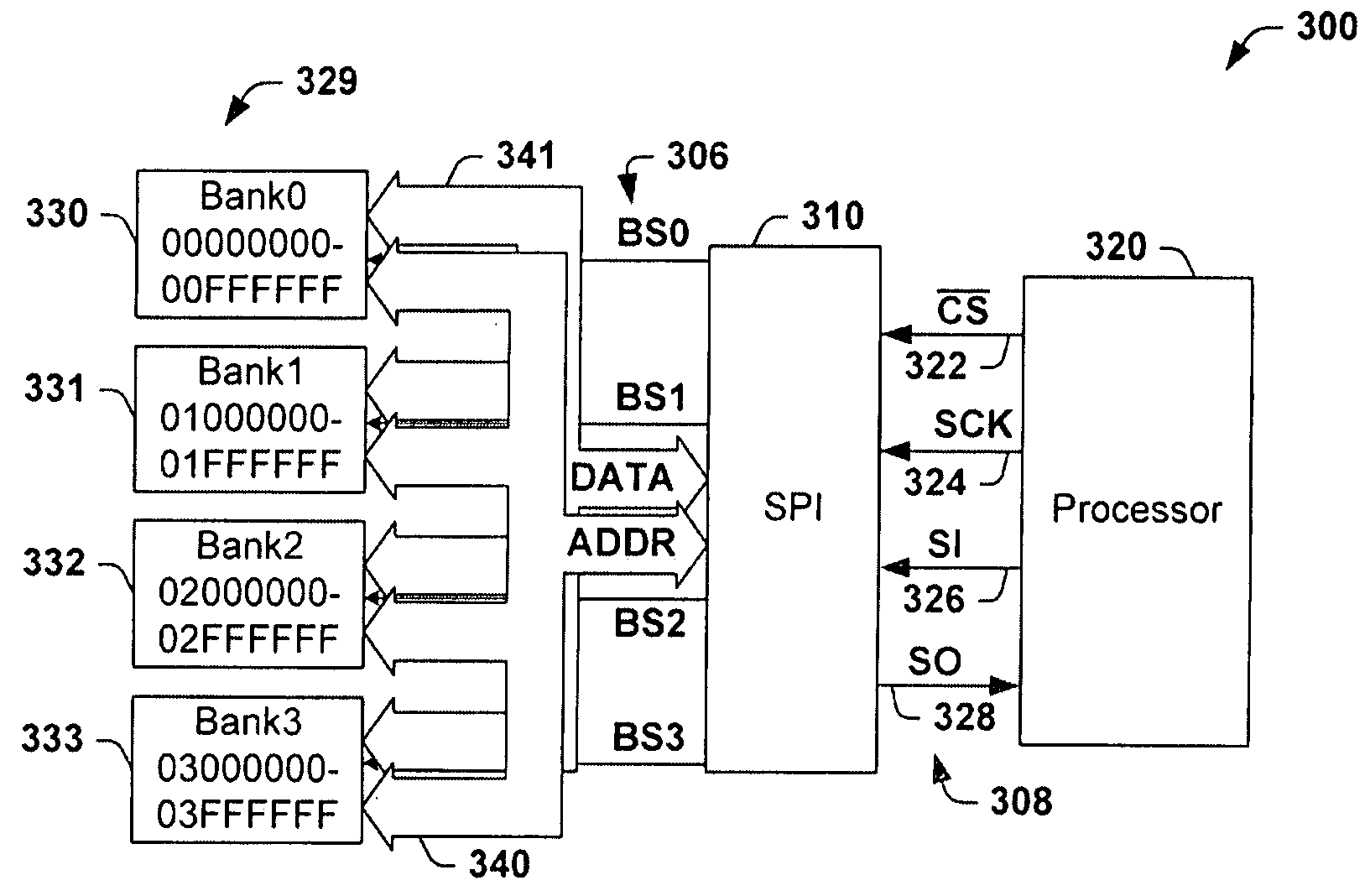

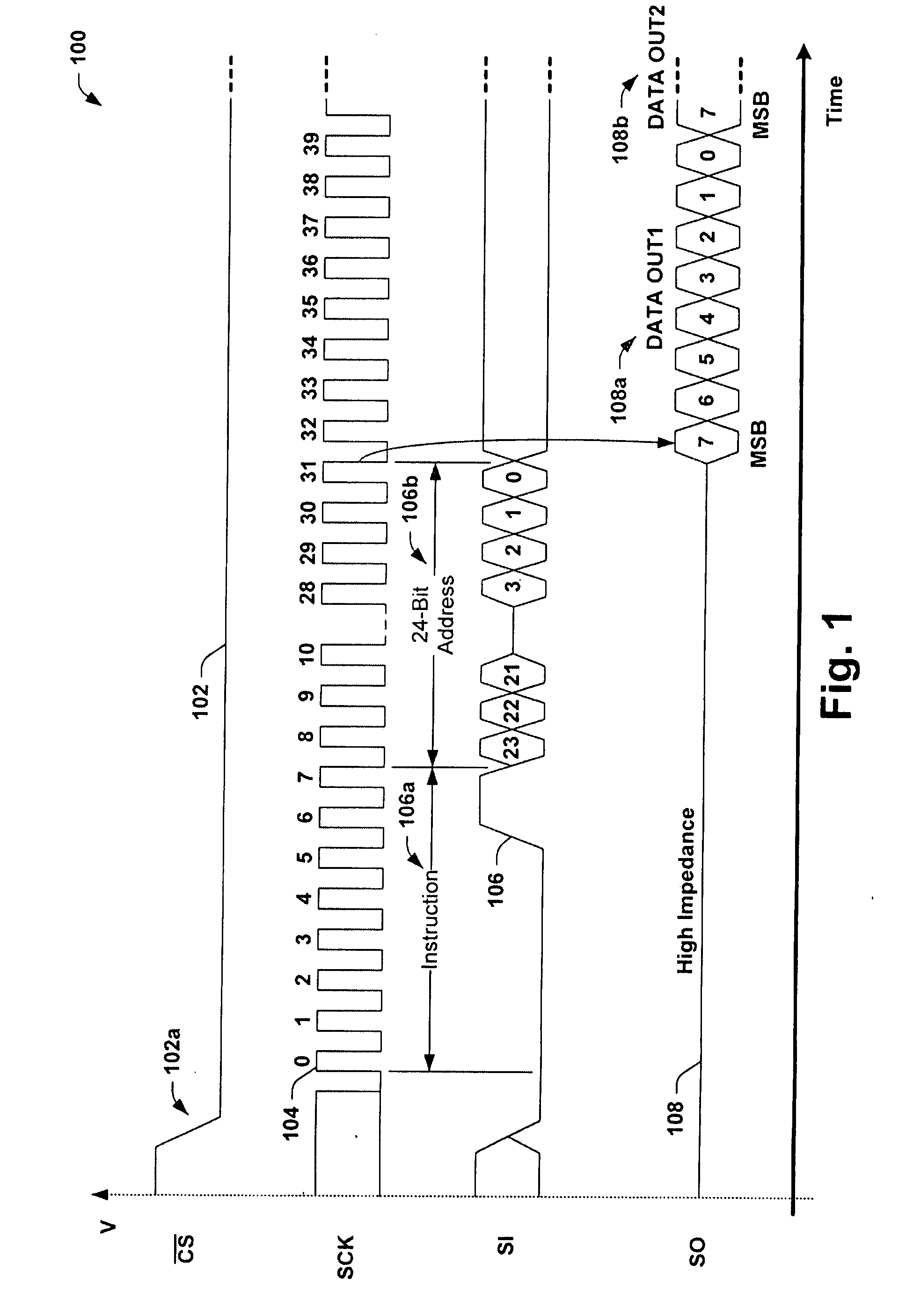

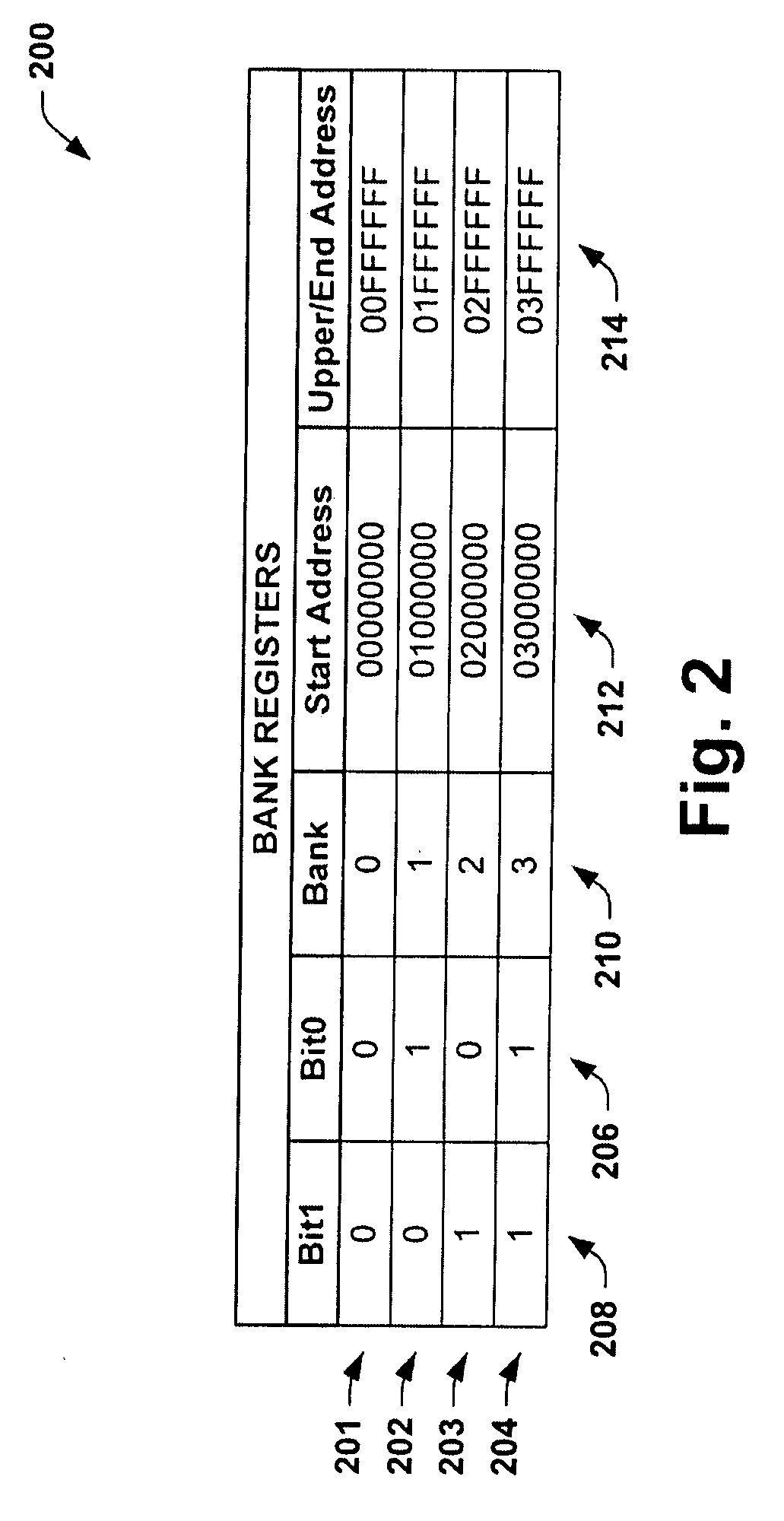

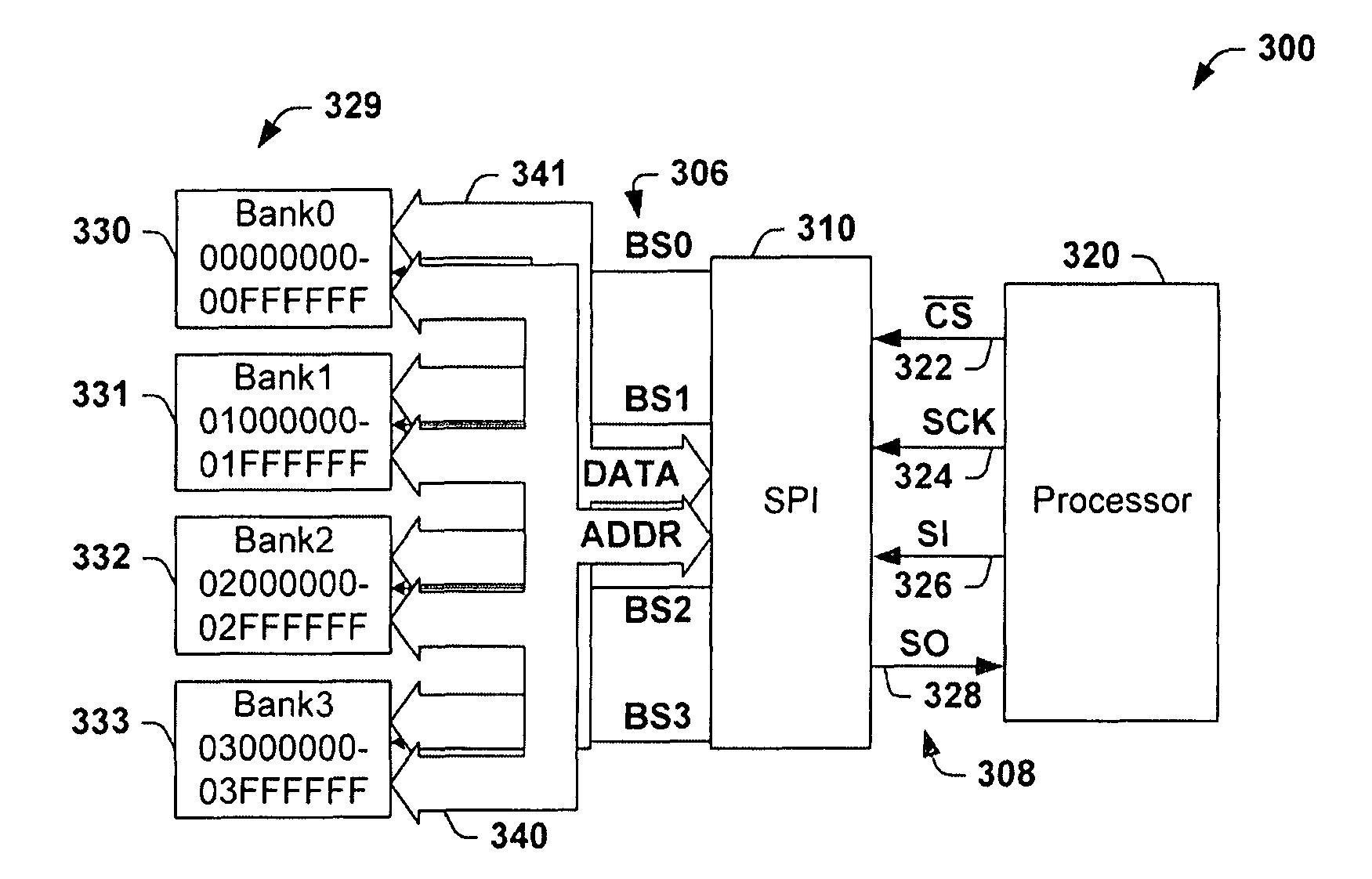

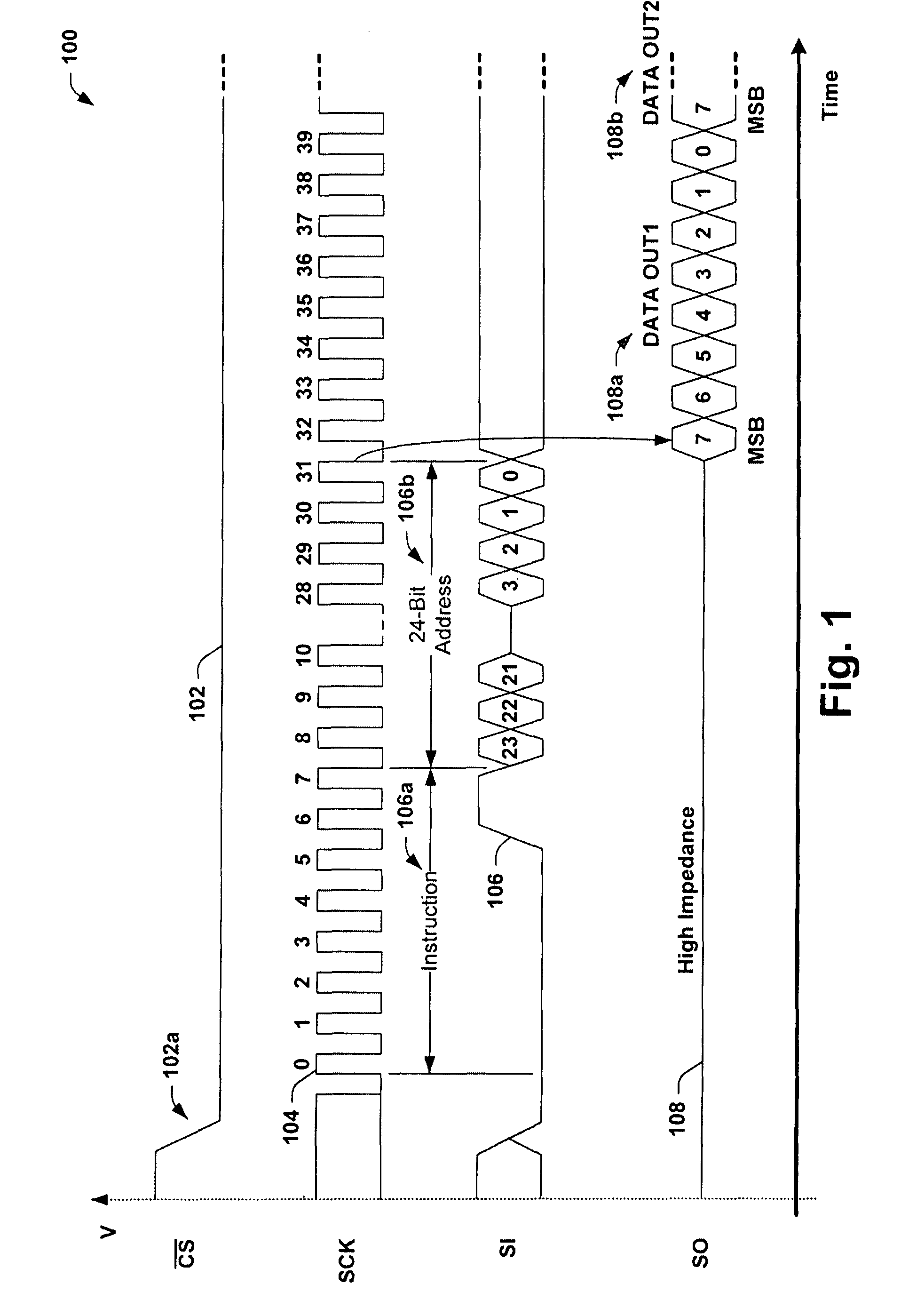

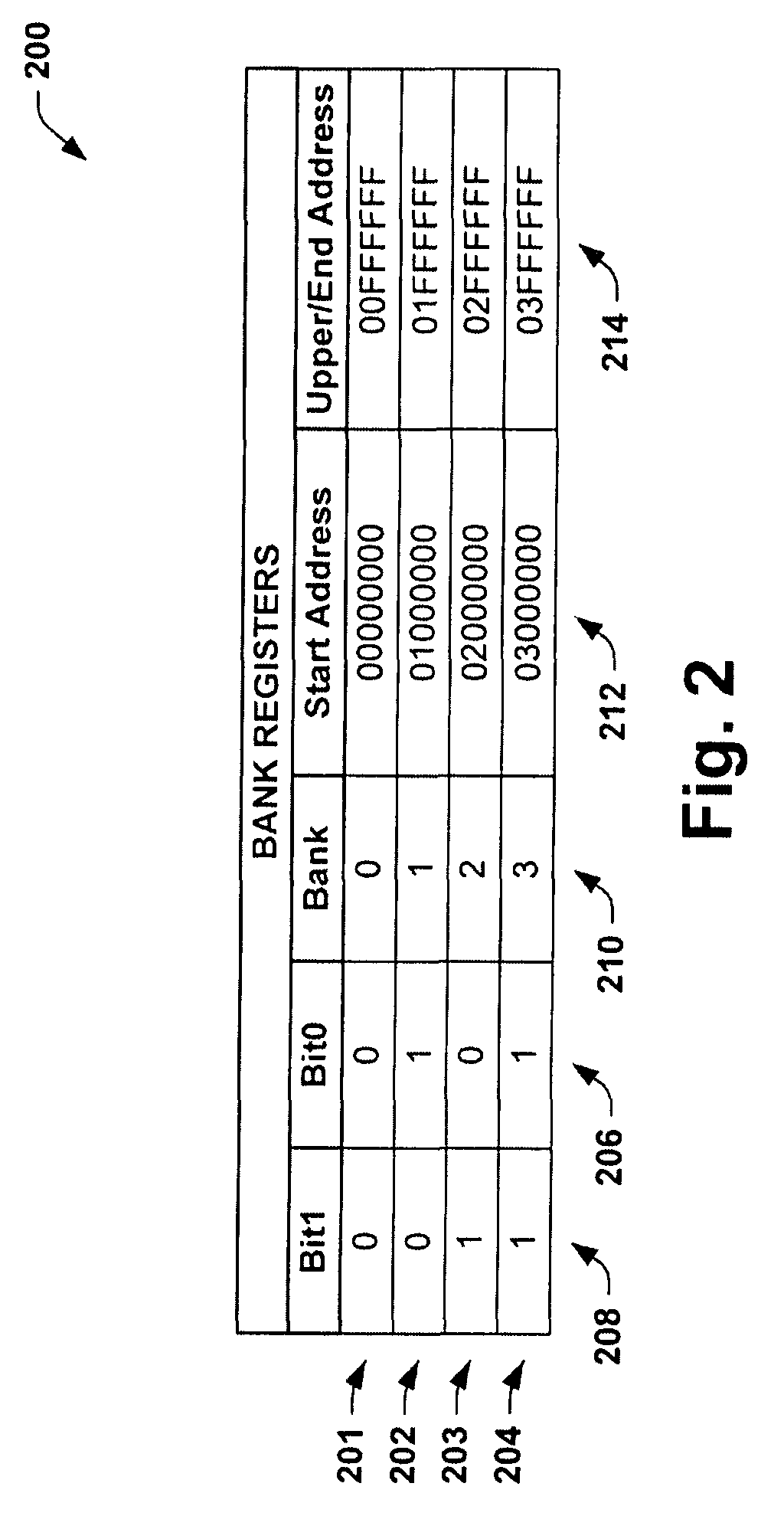

SPI BANK ADDRESSING SCHEME FOR MEMORY DENSITIES ABOVE 128Mb

ActiveUS20090138626A1Without costly and time-consume redesignMemory architecture accessing/allocationMemory adressing/allocation/relocationMemory bankByte addressing

Systems and methods of addressing two or more banks of memory utilizing a single-bank serial peripheral interface and an at least three-byte address protocol are provided. In one embodiment, a serial peripheral interface comprises a serial processing component configured to address one of the memory banks using the three-byte addressing scheme, and to write data to or read data from the addressed bank, and a bank register pointer component coupled to the serial processing component, the pointer component comprising two or more bank register pointers associated with respective memory banks, and configured to select one of the memory banks based on the two or more bank register pointers, wherein the bank register pointer component selects one of the two or more memory banks, and the serial processing component writes data to or reads data from the selected bank of memory according to the three-byte addressing scheme.

Owner:MONTEREY RES LLC

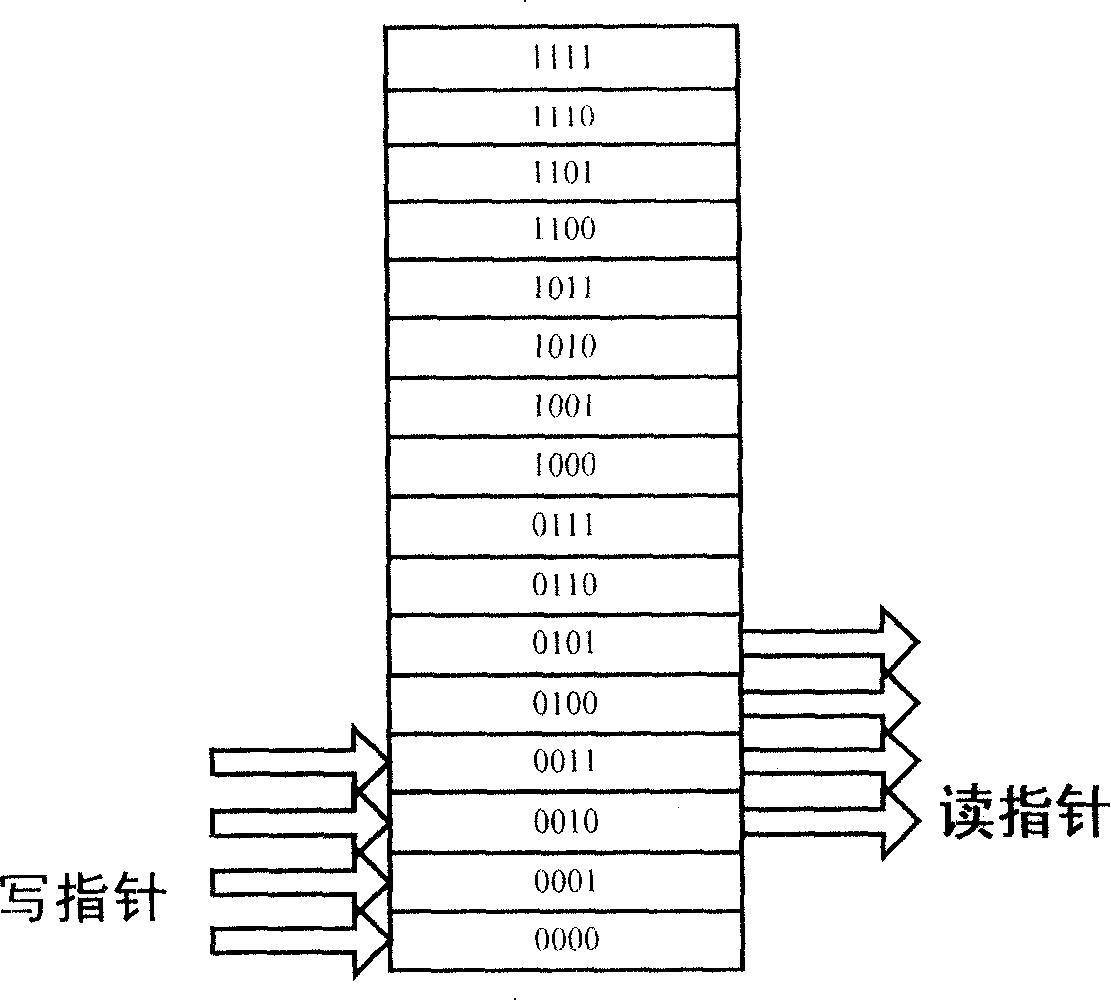

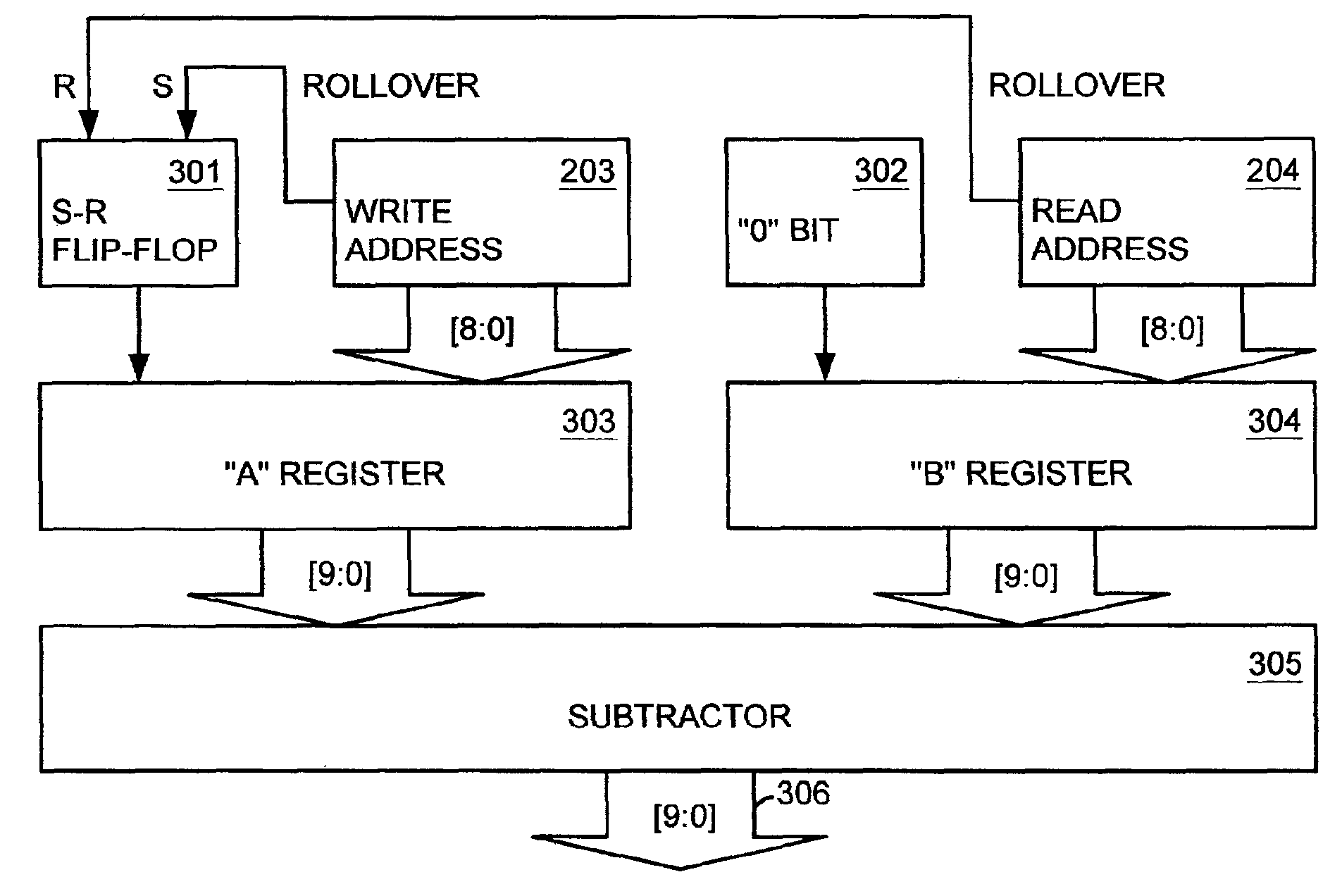

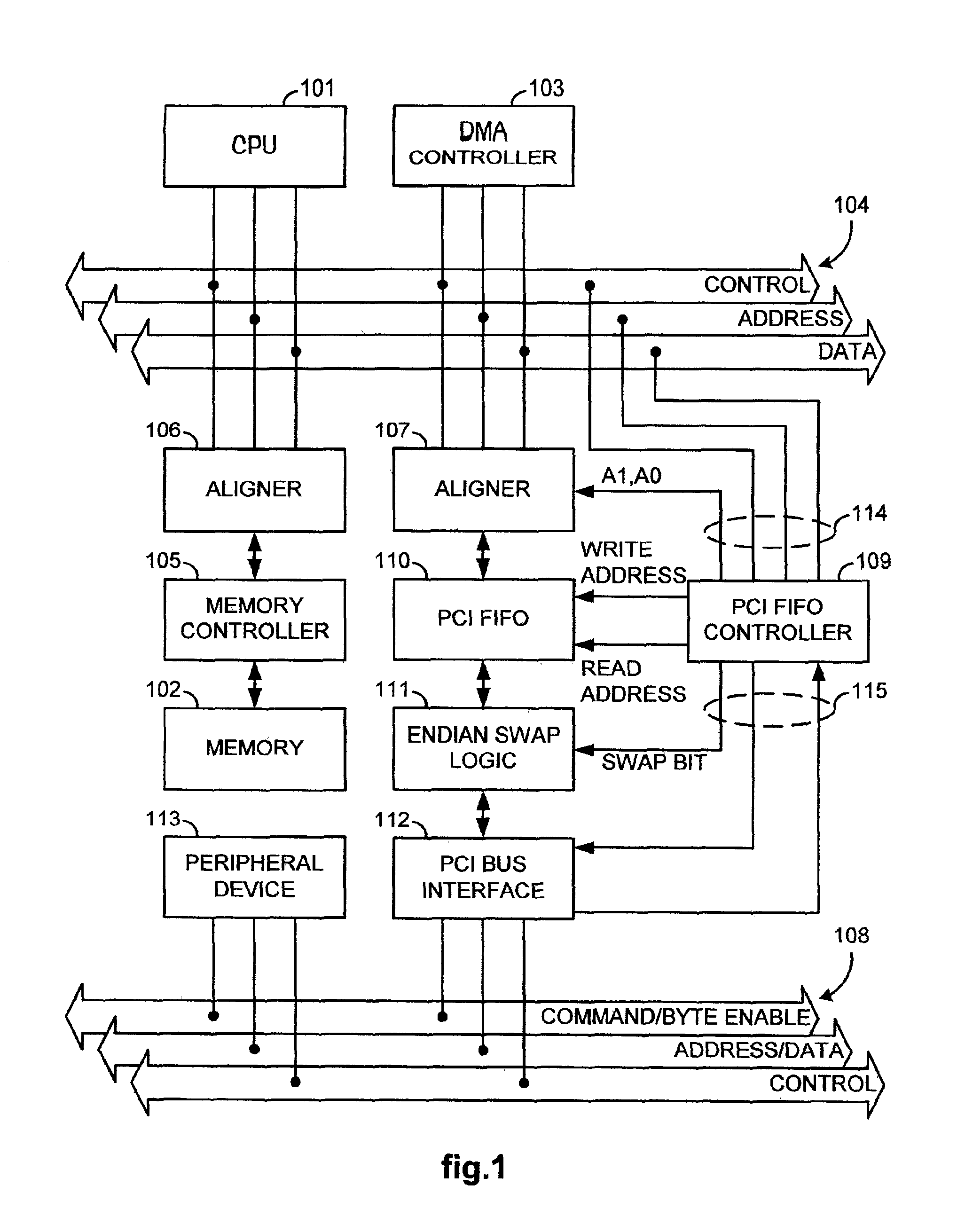

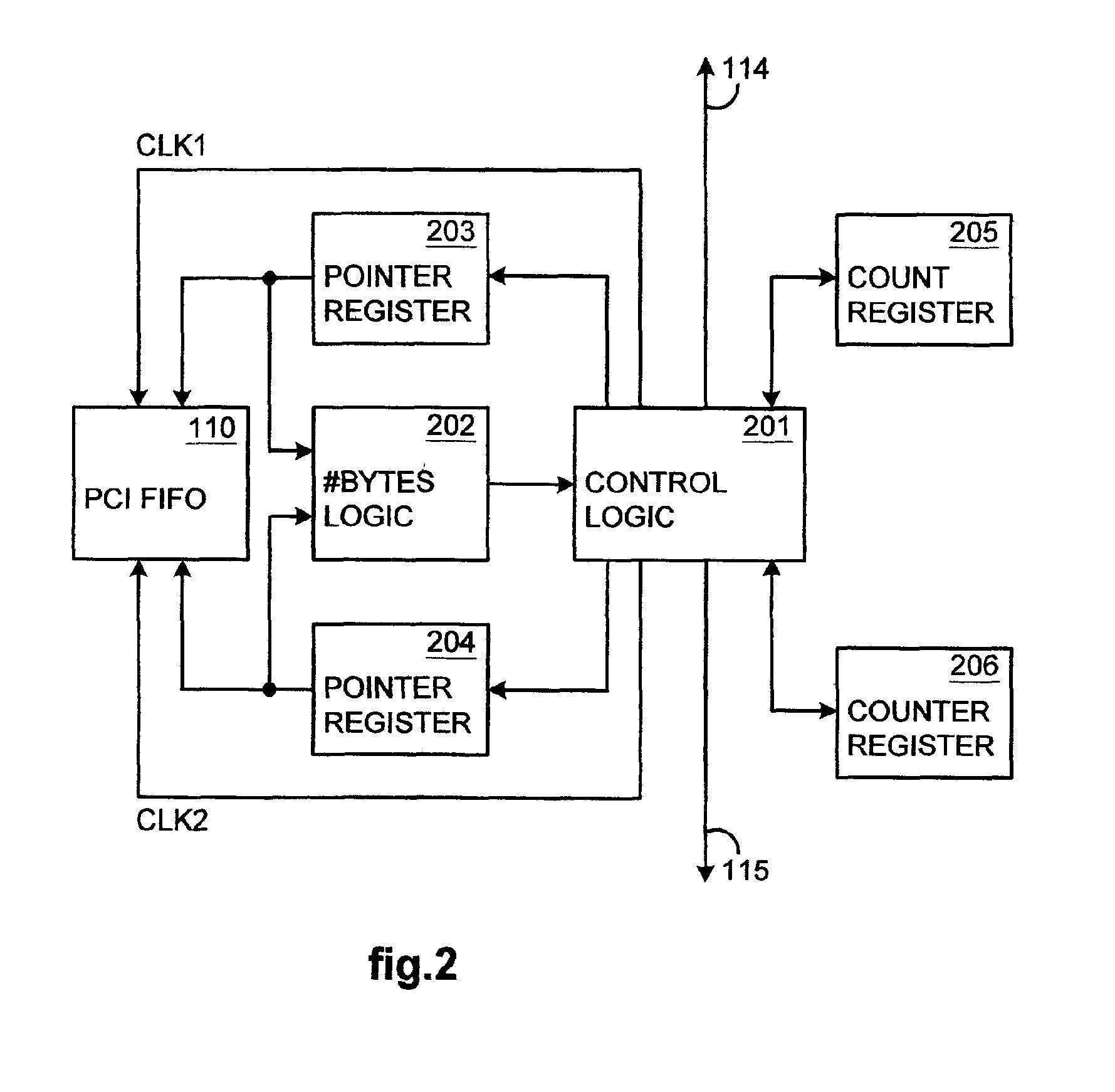

Apparatus and method for transferring multi-byte words in a fly-by DMA operation

InactiveUS6865638B1Improve efficiencyImprove simplicityDigital data processing detailsMemory systemsMemory busByte addressing

An apparatus and method for transferring multi-byte words having arbitrary start and end byte addresses are described. Data transfers between a memory and a PCI-bus pass through a PCI-side aligner unit, PCI FIFO, Endian swap logic, and PCI-bus interface unit under the control of a PCI FIFO controller. The PCI-side aligner unit properly aligns the data while communicating data with the memory's bus on a word-at-a-time basis, and communicating data with the PCI FIFO managed on a byte-at-a-time basis synchronous with a clock signal provided by the memory's bus. The Endian swap logic properly orients the data in big or little Endian orientation. The PCI-bus interface unit communicates data with the PCI-bus on a word-at-a-time basis, and communicates data with the PCI FIFO managed on a byte-at-a-time basis synchronous with a clock signal provided by the PCI-bus. To keep track of unread stored data in the PCI FIFO, the PCI FIFO controller includes a #Bytes logic unit that automatically accounts for wrap-around of write and read pointers for the PCI FIFO.

Owner:SK HYNIX INC

Local direct storage class memory access

ActiveUS9311230B2Reduce the burden onEasy accessMemory adressing/allocation/relocationDigital computer detailsZero-copyGranularity

A queued, byte addressed system and method for accessing flash memory and other non-volatile storage class memory, and potentially other types of non-volatile memory (NVM) storage systems. In a host device, e.g., a standalone or networked computer, having attached NVM device storage integrated into a switching fabric wherein the NVM device appears as an industry standard OFED™ RDMA verbs provider. The verbs provider enables communicating with a ‘local storage peer’ using the existing OpenFabrics RDMA host functionality. User applications issue RDMA Read / Write directives to the ‘local peer (seen as a persistent storage) in NVM enabling NVM memory access at byte granularity. The queued, byte addressed system and method provides for Zero copy NVM access. The methods enables operations that establish application private Queue Pairs to provide asynchronous NVM memory access operations at byte level granularity.

Owner:GLOBALFOUNDRIES U S INC

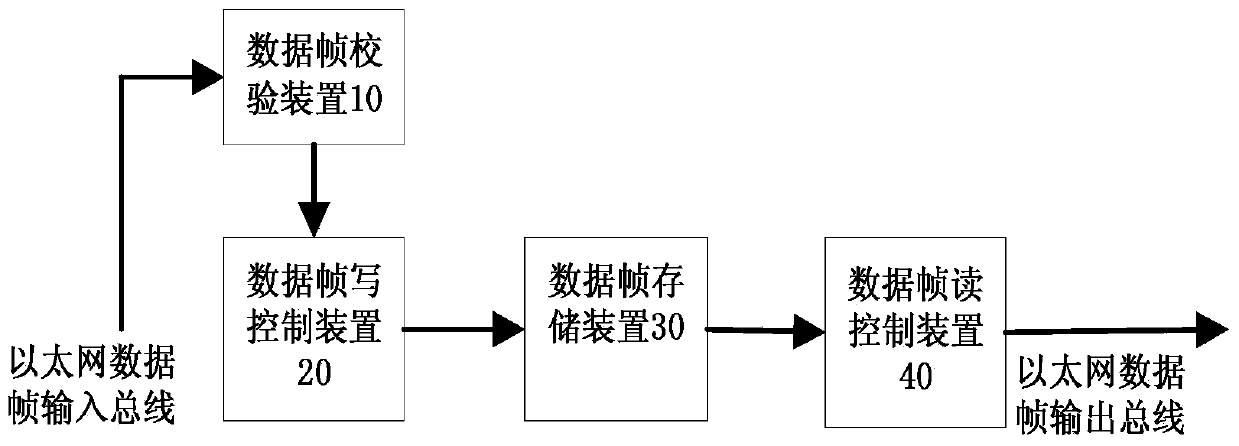

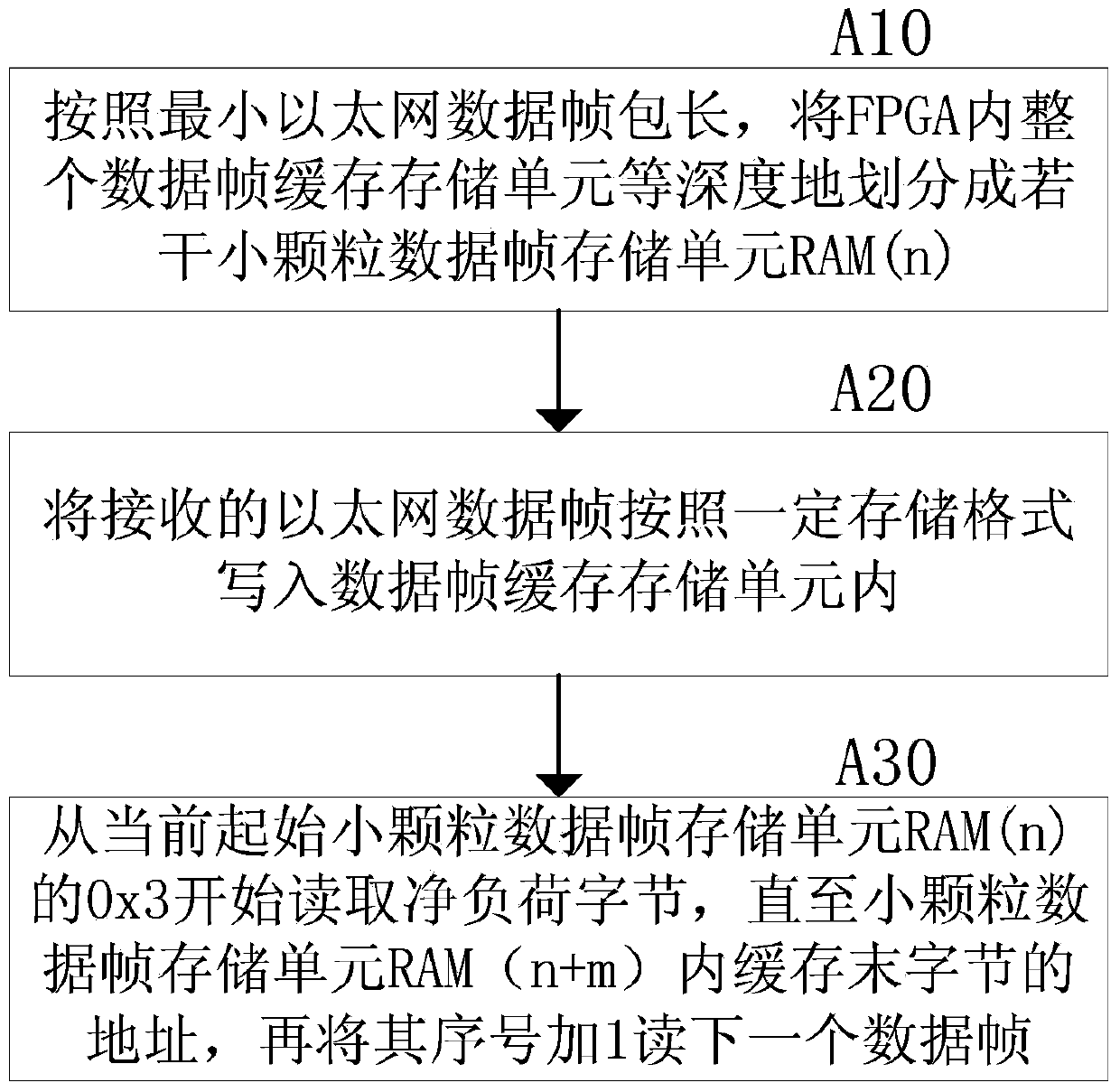

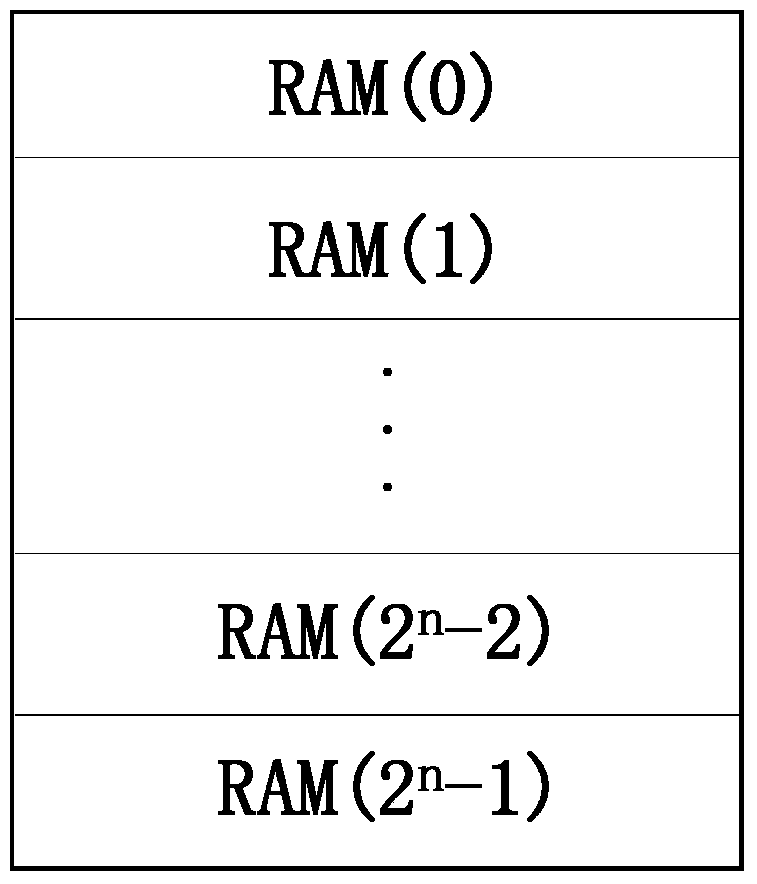

Method and device for caching and transmitting of Ethernet data frames in FPGA (field programmable gate array)

ActiveCN104199783AImplement cachingRealize forwardingMemory adressing/allocation/relocationData switching networksRandom access memoryStructure of Management Information

The invention discloses a method and a device for caching and transmitting of Ethernet data frames in FPGA (field programmable gate array). The method includes according to the minimum Ethernet data frame package length, deeply dividing a data frame caching and storing unit and the like into a plurality of small-particle data frame storing units; writing the Ethernet data frame into the data frame caching and storing unit, particularly storing identifiers of Ethernet data frame in a 0*0 address of an initial small-particle data frame storing unit RAM (random access memory) (n), storing sequence numbers and addresses of an initial small-particle data frame storing unit RAM (n+m) where a last byte of the Ethernet data frame existing in a 0 *1 address and a 0*2 address, and sequentially storing data frame net load byte from a 0*3 address; sequentially reading the cached data frame net load byte from the 0*3 address of the current initial small-particle data frame storing unit RAM (n) to the last byte address of the small-particle data frame storing unit RAM (n+m), and adding 1 to the sequence number n+m to read the next data frame. By the use of the method and the device, caching and transmitting of the Ethernet data frame is achieved, use ratio of RAM in the FPGA, and stability of the whole structure during the caching and transmitting is guaranteed.

Owner:FENGHUO COMM SCI & TECH CO LTD

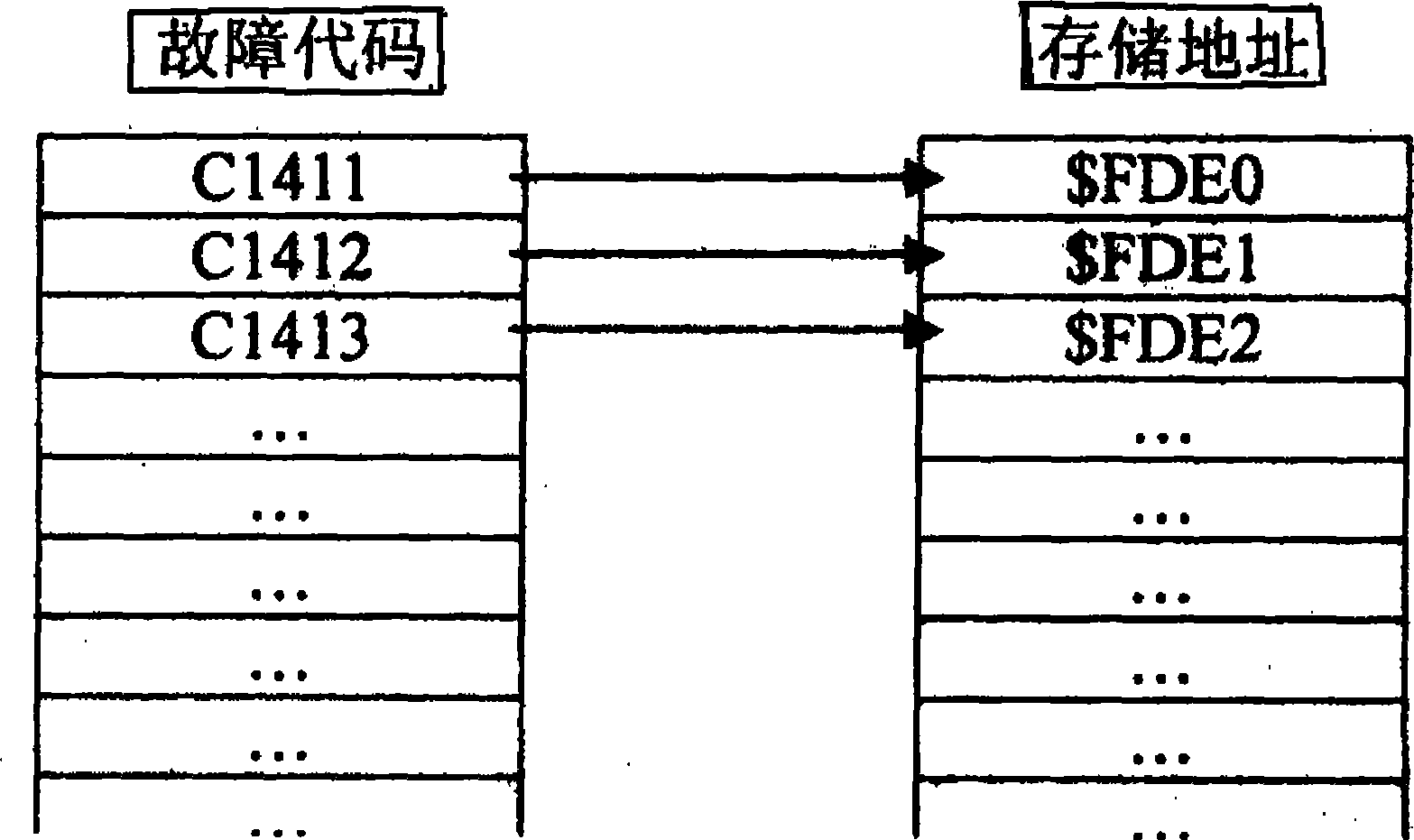

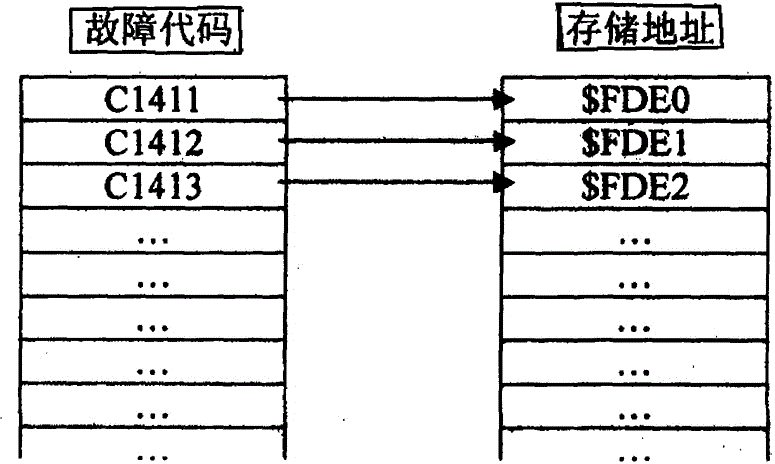

Fault code storage management method for automobile active stabilization control system

InactiveCN101510095AImprove reliabilityImprove efficiencyElectric testing/monitoringSafety management systemsControl system

The invention belongs to a method for storing and managing the fault codes by an automotive active stability control system in the field of vehicle driving safety management system. The automotive active stability control system uses an automotive electronic stability program (ESP) for storing and managing the fault codes; the automotive ESP fault code storage and management is a way that an ESP fault diagnosis system defines, stores and reads the fault codes; firstly the ESP defines the fault codes according to the fault type, leads each fault code to be corresponding to each byte address in a designated storage unit one by one; the storage of the fault codes is carried out in a mode of changing the mark bit of a corresponding storage byte thereof; the fault diagnosis results are stored in chronological sequence from the high bit to the low bit of the corresponding bytes in sequence, thereby ensuring the characteristics of non-volatility, historicity, simple algorithm, high efficiency, and short operating cycle for the fault diagnosis result data storage of the system, guaranteeing the vehicle driving stability and greatly improving the driving safety of the vehicle.

Owner:CHINA AGRI UNIV

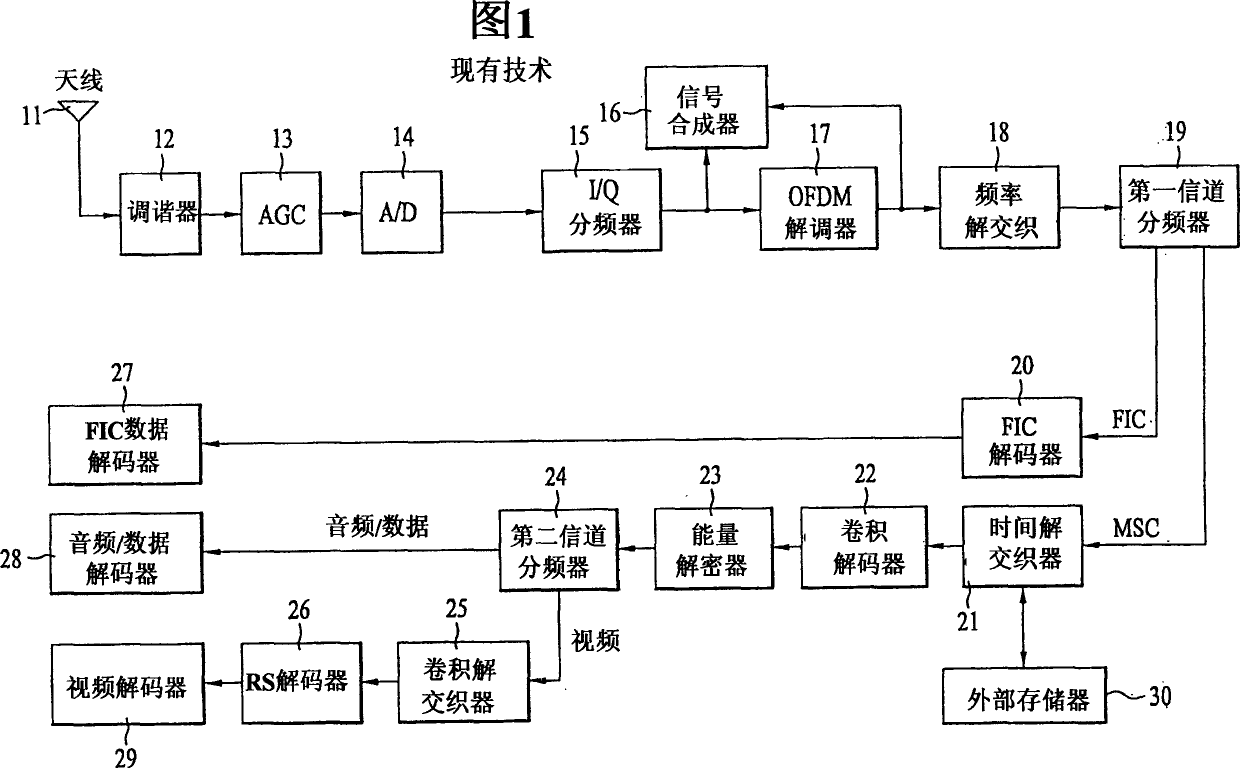

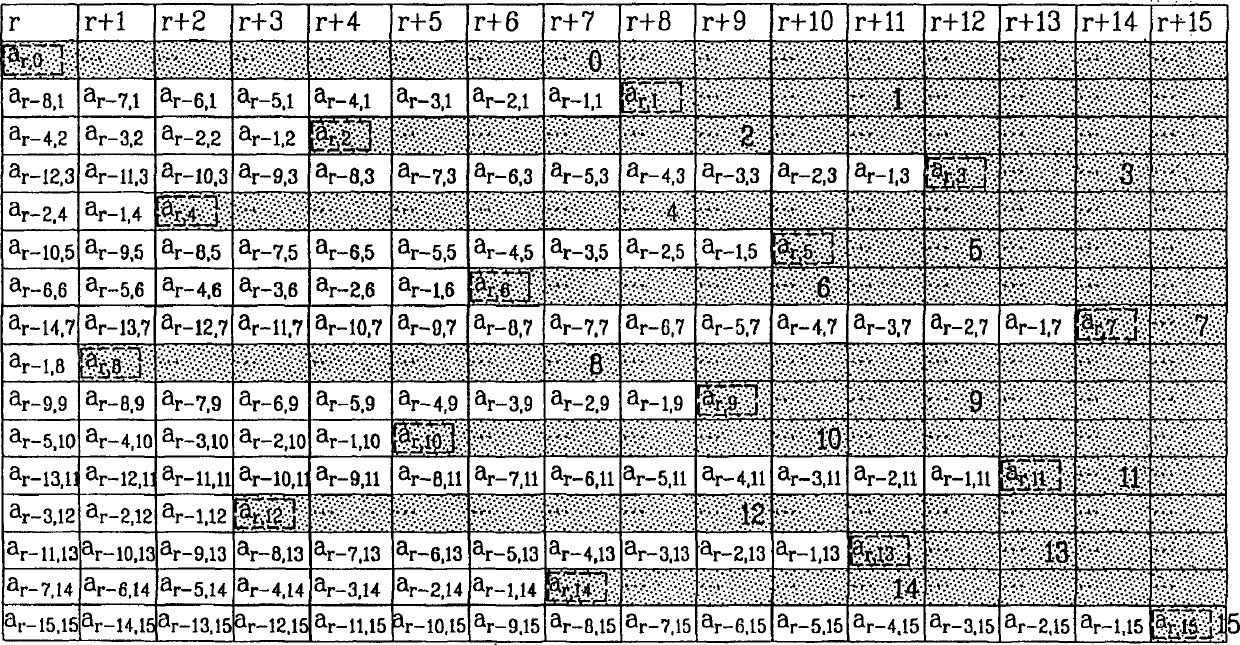

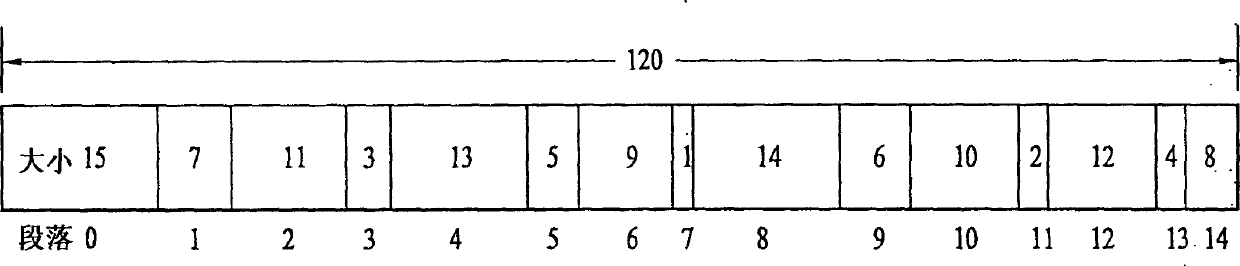

Memory control method for time deinterleaving in DMB receiver

Provided is a method for controlling a memory for time deinterleaving in a DMB receive by using byte addressing. The memory control method includes the steps of constructing the memory by the several segments so as to store only sample data used for actual time deinterleaving during a time period corresponding to M+1 frames from a time point r through a time point r+M; storing a plurality of sample data at one memory address by accessing the memory on a segment basis through byte addressing; and generating a byte-based memory address according to a time deinterleaving rule determined by the i value, and reading one of the sample data stored at the memory address and masking and another sample data stored at the memory address according to what order sample data is to be read from the memory address, thereby making it possible to greatly reduce the complexity of a memory address decoder in the memory.

Owner:LG ELECTRONICS INC

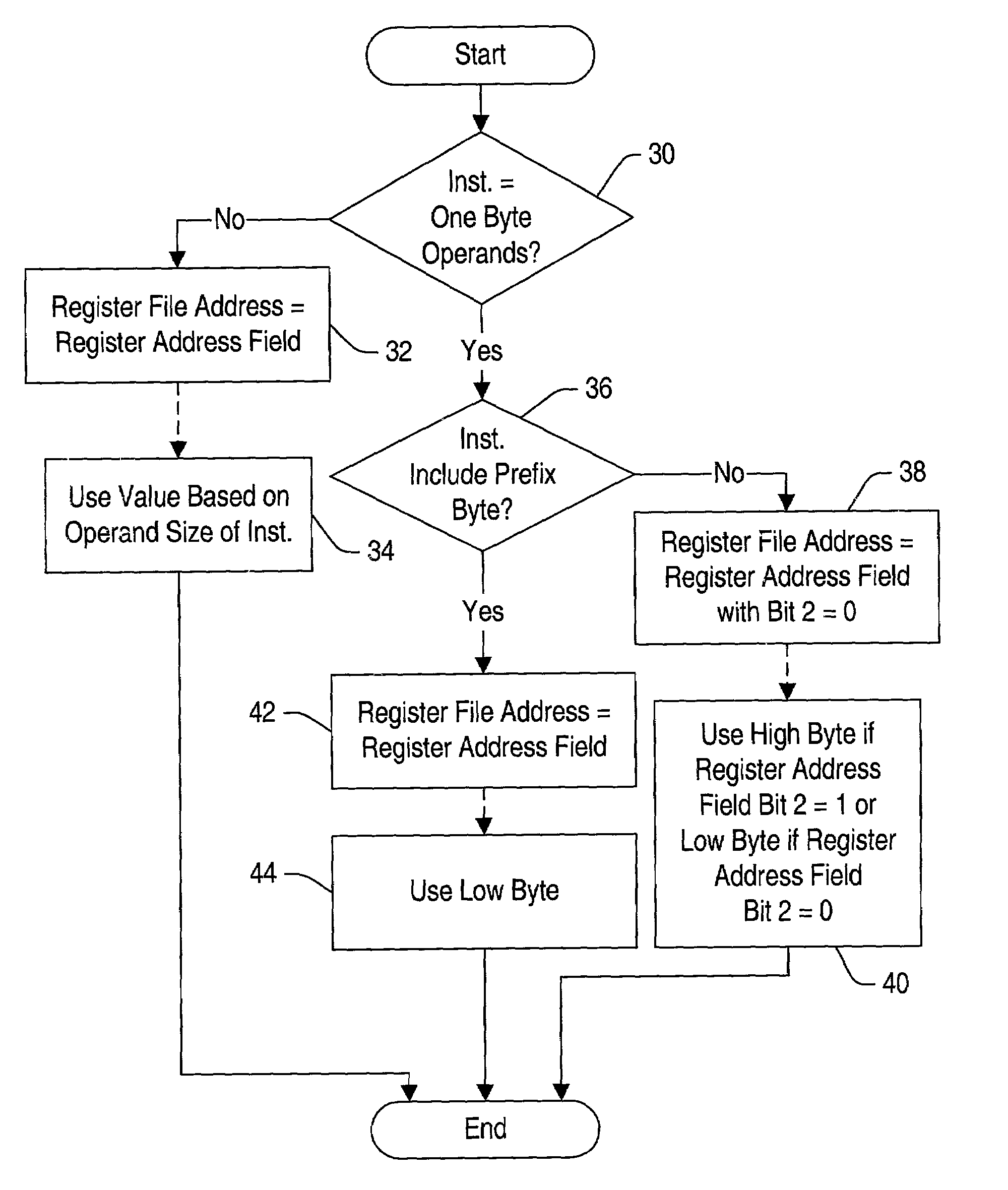

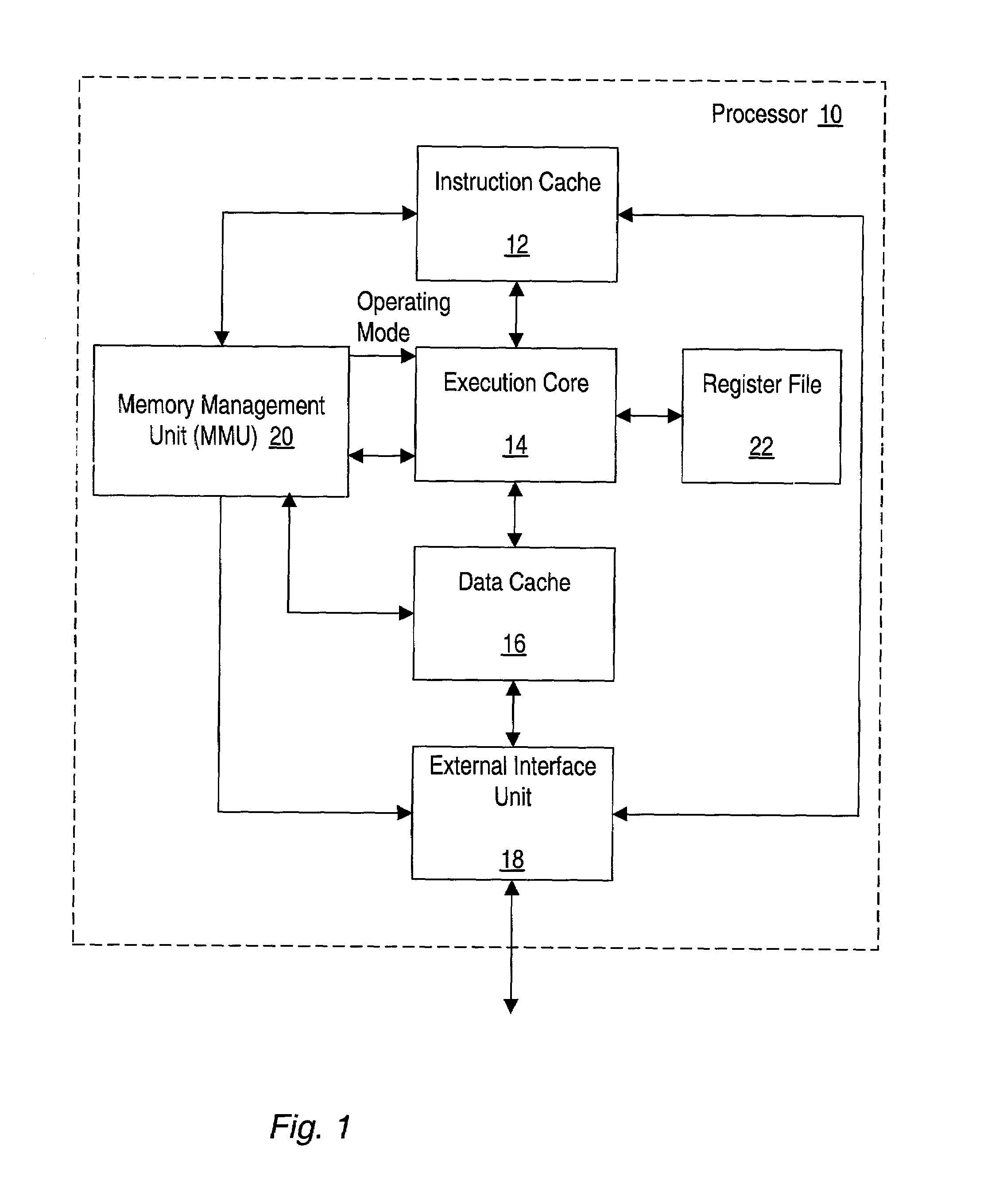

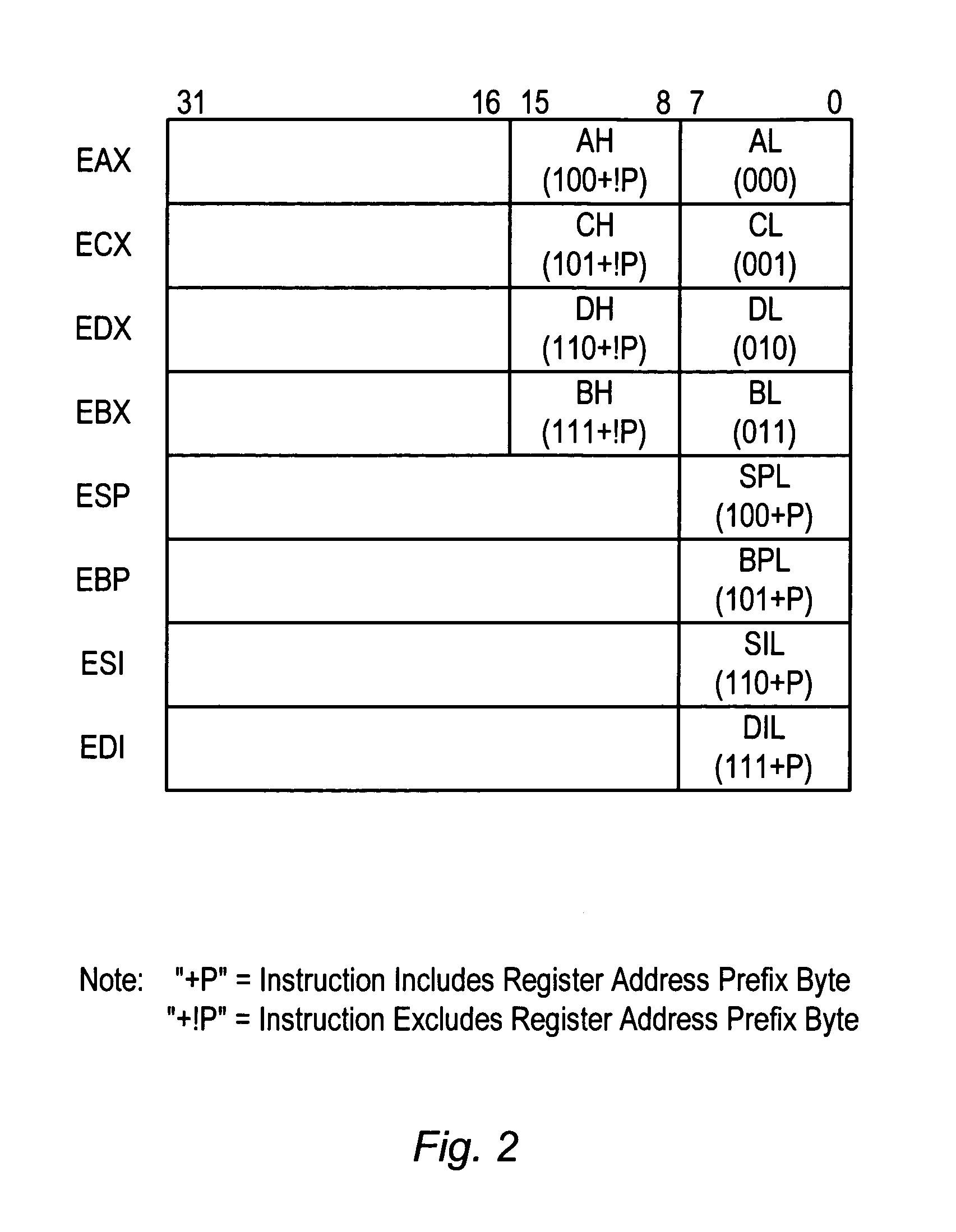

Uniform register addressing using prefix byte

InactiveUS6981132B2Simple designMaintain compatibilityRegister arrangementsInstruction analysisProcessor registerParallel computing

A processor changes the mapping of register addresses to registers dependent on an instruction field. In one particular embodiment, the mapping may be changed for byte addressing of the registers. A register mapping in which each register address maps to either the least significant byte or the next least significant byte of a subset of the registers may be supported, as well as a register mapping in which each register address maps to the least significant byte of each register, in one implementation. In one particular implementation, the instruction field may be a prefix field (e.g. a prefix byte). The processor may provide for uniform addressing of registers (e.g. byte addressing of the registers) responsive to a prefix field, in other embodiments, irrespective of the addressing provided if the prefix field is not included, or is encoded differently than the encoding which results in the uniform addressing.

Owner:ADVANCED MICRO DEVICES INC

Creating and maintaining order of a log stream without use of a lock or latch

InactiveUS20120203805A1Digital data information retrievalSpecial data processing applicationsByte addressingByte

Provided are techniques for using a series of compare and swap operations to assign a Relative Byte Address (RBA) and a Logical Record Sequence Number (LRSN) to a log record. One or more log buffers for storing the log record are identified, and the log record is moved to the one or more log buffers.

Owner:INT BUSINESS MASCH CORP

Low-overhead built-in timestamp column for relational database systems

Owner:INT BUSINESS MASCH CORP

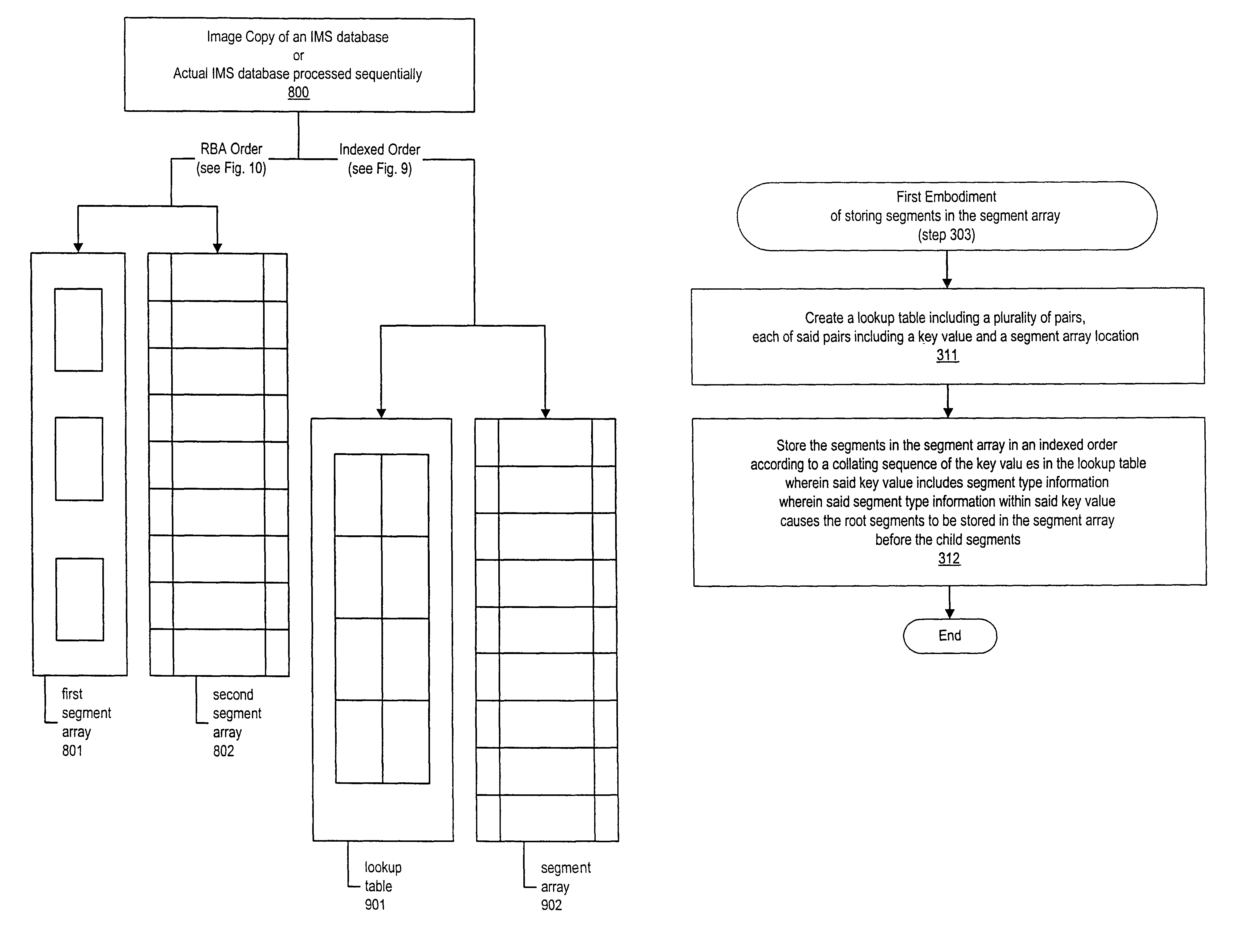

Sequential unload processing of IMS databases

InactiveUS7720805B1Digital data processing detailsHierarchical databasesArray data structureByte addressing

A method and system for unloading an IMS database. Segments in the segment array are stored in an indexed order or are stored in a relative byte address (RBA) order. In both cases, either an image copy of an IMS database or an actual IMS database processed sequentially may be utilized. For indexed order storage, a lookup table may be created to include a key value and a segment array location. A segment array may be created to store both the root and child segments from the IMS database. For RBA ordered storage, a first segment array may be created to store the root segments from the IMS database in a sequential order. Additionally, a second segment array may be created to store the child segments from the IMS database in a relative byte address (RBA) order.

Owner:BMC SOFTWARE

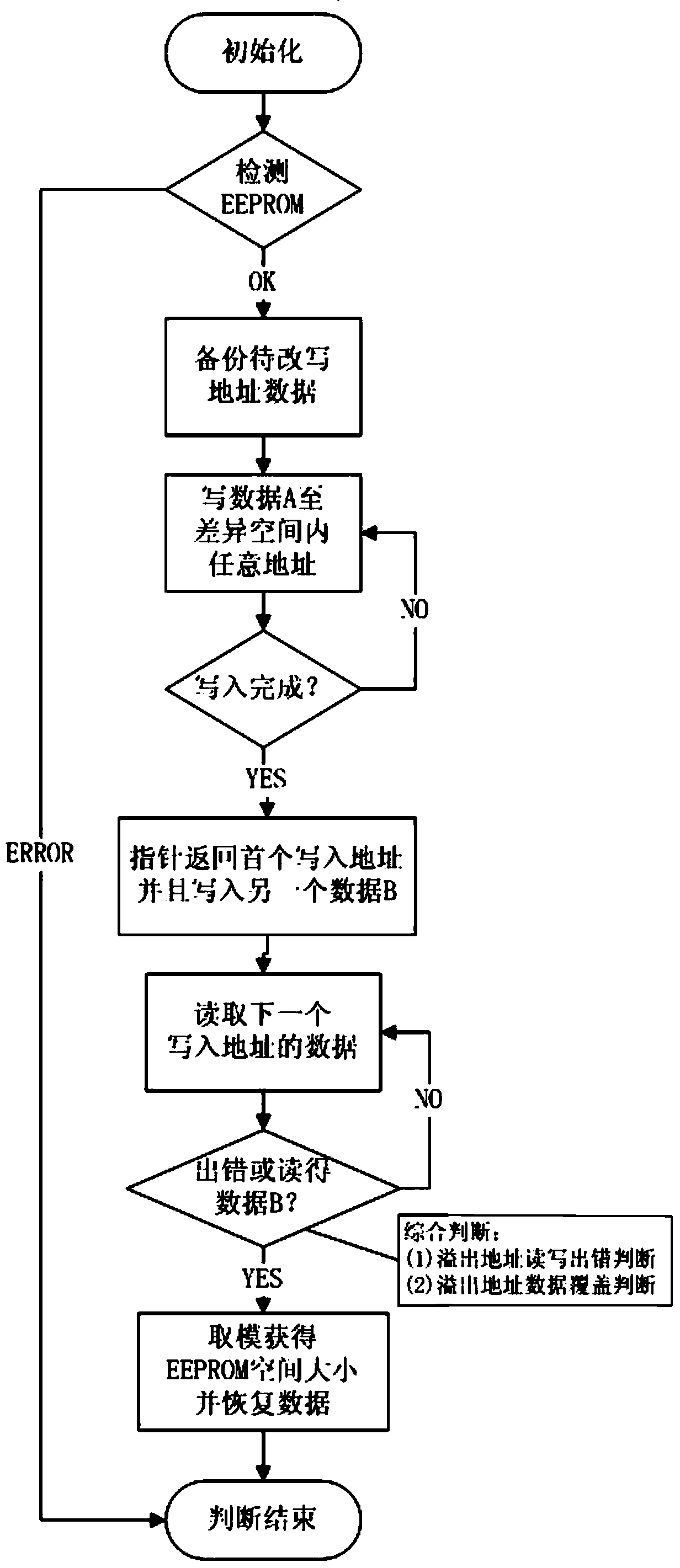

Method for automatically obtaining EEPROM (Electrically Erasable Programmable Read-Only Memory) storage capacity

InactiveCN103777907ASave resourcesImprove versatilityInput/output to record carriersProgrammable read-only memoryByte addressing

The invention relates to an EEPROM, aims at solving the problem that the function of automatically obtaining the EEPROM storage capacity cannot be obtained in the prior art and provides a method for automatically obtaining the EEPROM storage capacity. The method for automatically obtaining the EEPROM storage capacity comprises detecting whether the EEPROM is connected through a system, if so, entering the next step, and if not, finishing the operation; secondly, determining an address which can represent differences and writing the address in data through the system according to different ranges of the size of the EEPROM storage space; thirdly, rewriting data of the first byte address written in the data to another certain data through the system and marking the data as B; finally, judging read-write error and data coverage of difference addresses of the EEPROM through the system, calculating the actual size of the EEPROM storage space after the judgment is finished, and finishing the operation. According to the method for automatically obtaining the EEPROM storage capacity, by means of the directional testing of any effective address in difference storage space of EEPROMs of different types, the sizes of the storage space of different EEPROMs can be automatically judged and obtained.

Owner:四川长虹空调有限公司

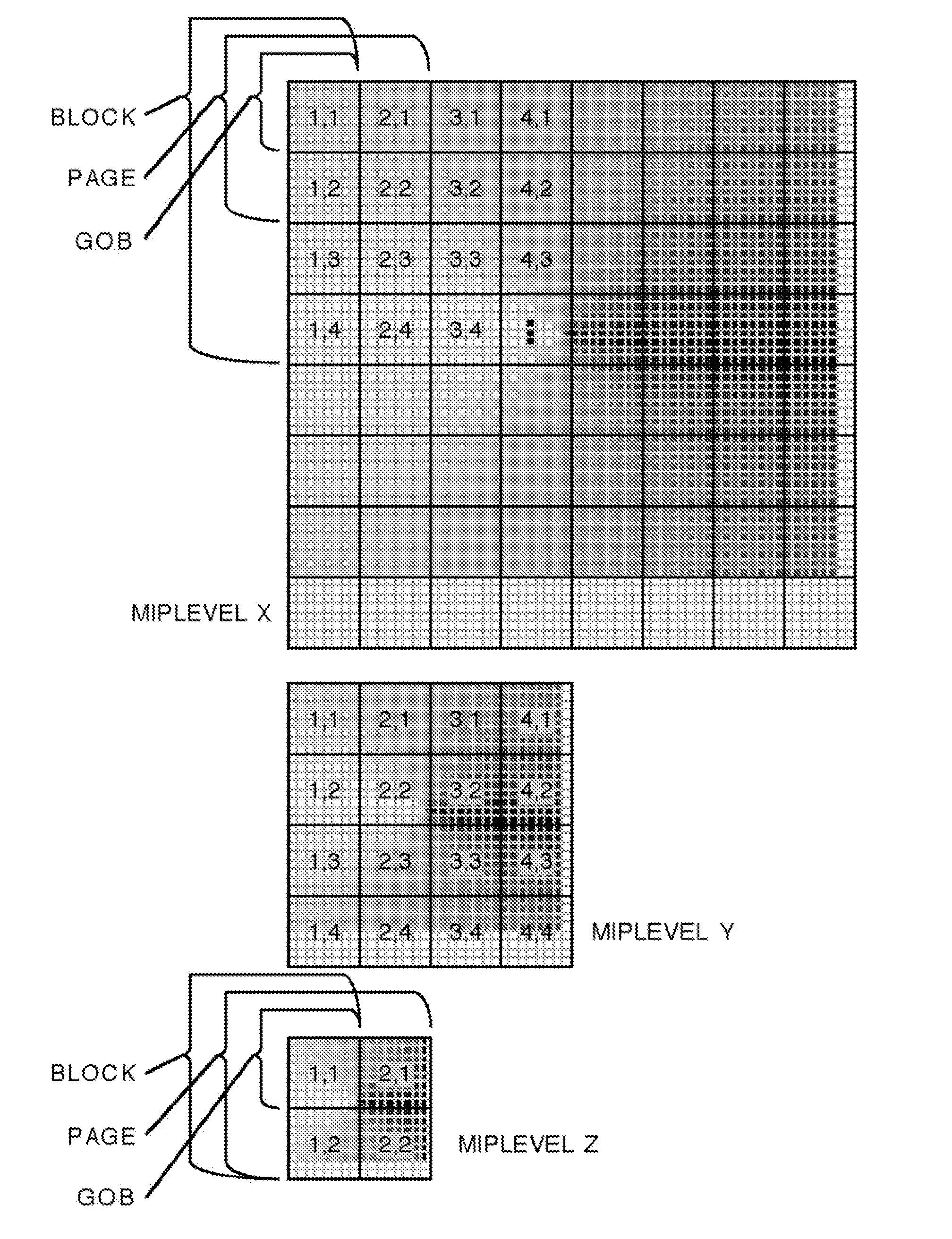

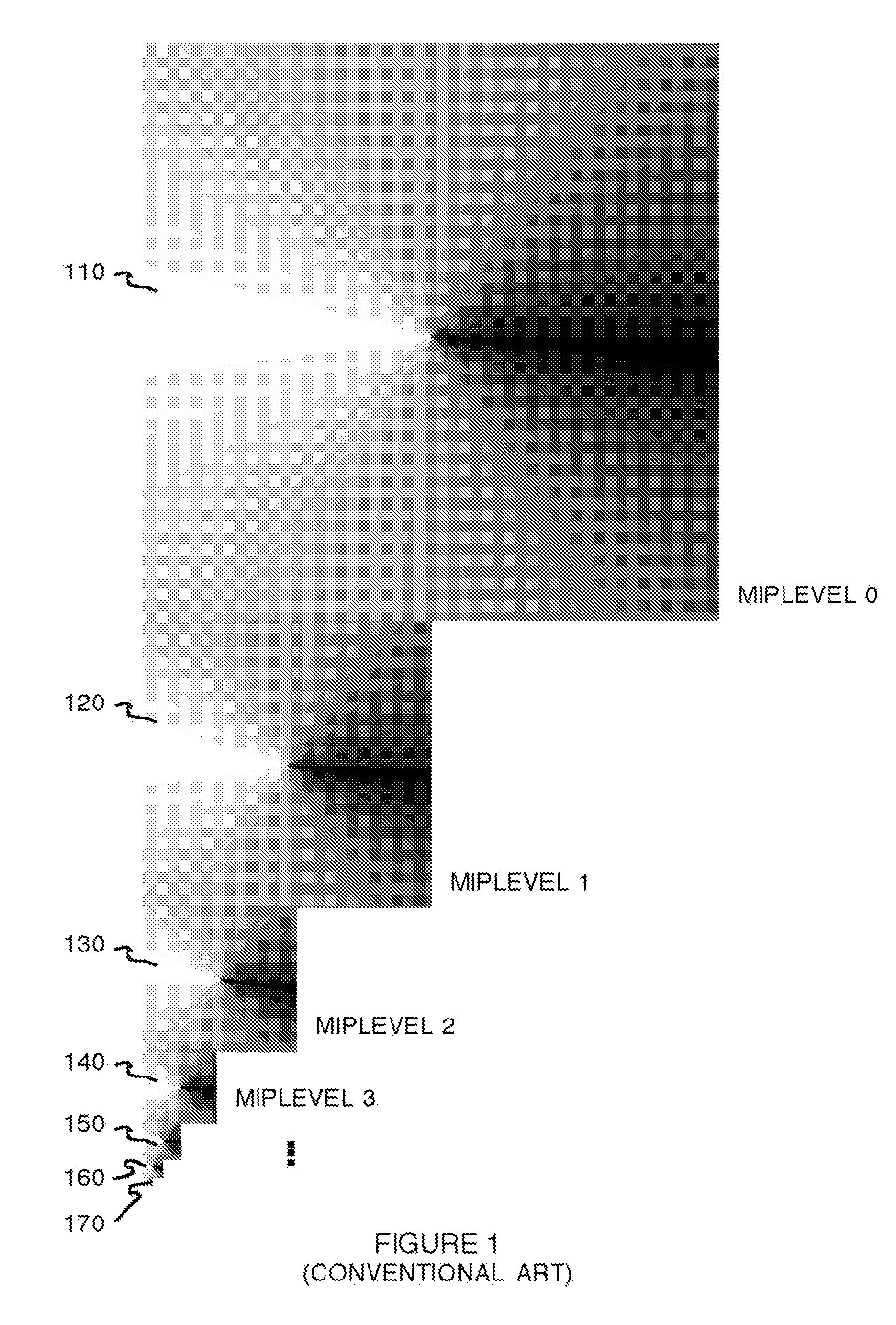

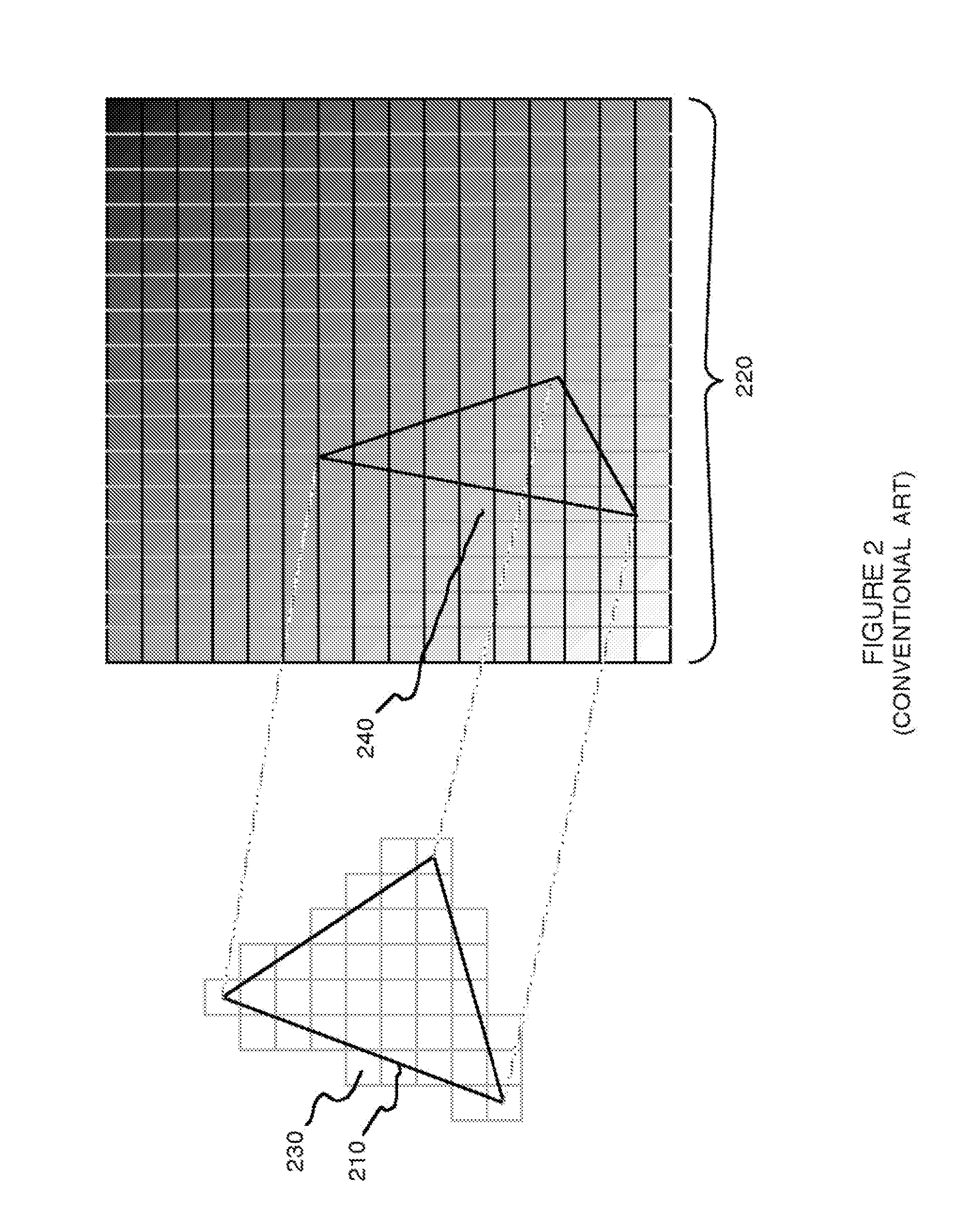

Block linear memory ordering of texture data

ActiveUS20110169850A1Memory adressing/allocation/relocationImage memory managementMemory orderingParallel computing

Owner:NVIDIA CORP

SPI bank addressing scheme for memory densities above 128Mb

ActiveUS7979625B2Without costly and time-consume redesignMemory architecture accessing/allocationMemory adressing/allocation/relocationMemory bankByte addressing

Systems and methods of addressing two or more banks of memory utilizing a single-bank serial peripheral interface and an at least three-byte address protocol are provided. In one embodiment, a serial peripheral interface comprises a serial processing component configured to address one of the memory banks using the three-byte addressing scheme, and to write data to or read data from the addressed bank, and a bank register pointer component coupled to the serial processing component, the pointer component comprising two or more bank register pointers associated with respective memory banks, and configured to select one of the memory banks based on the two or more bank register pointers, wherein the bank register pointer component selects one of the two or more memory banks, and the serial processing component writes data to or reads data from the selected bank of memory according to the three-byte addressing scheme.

Owner:MONTEREY RES LLC

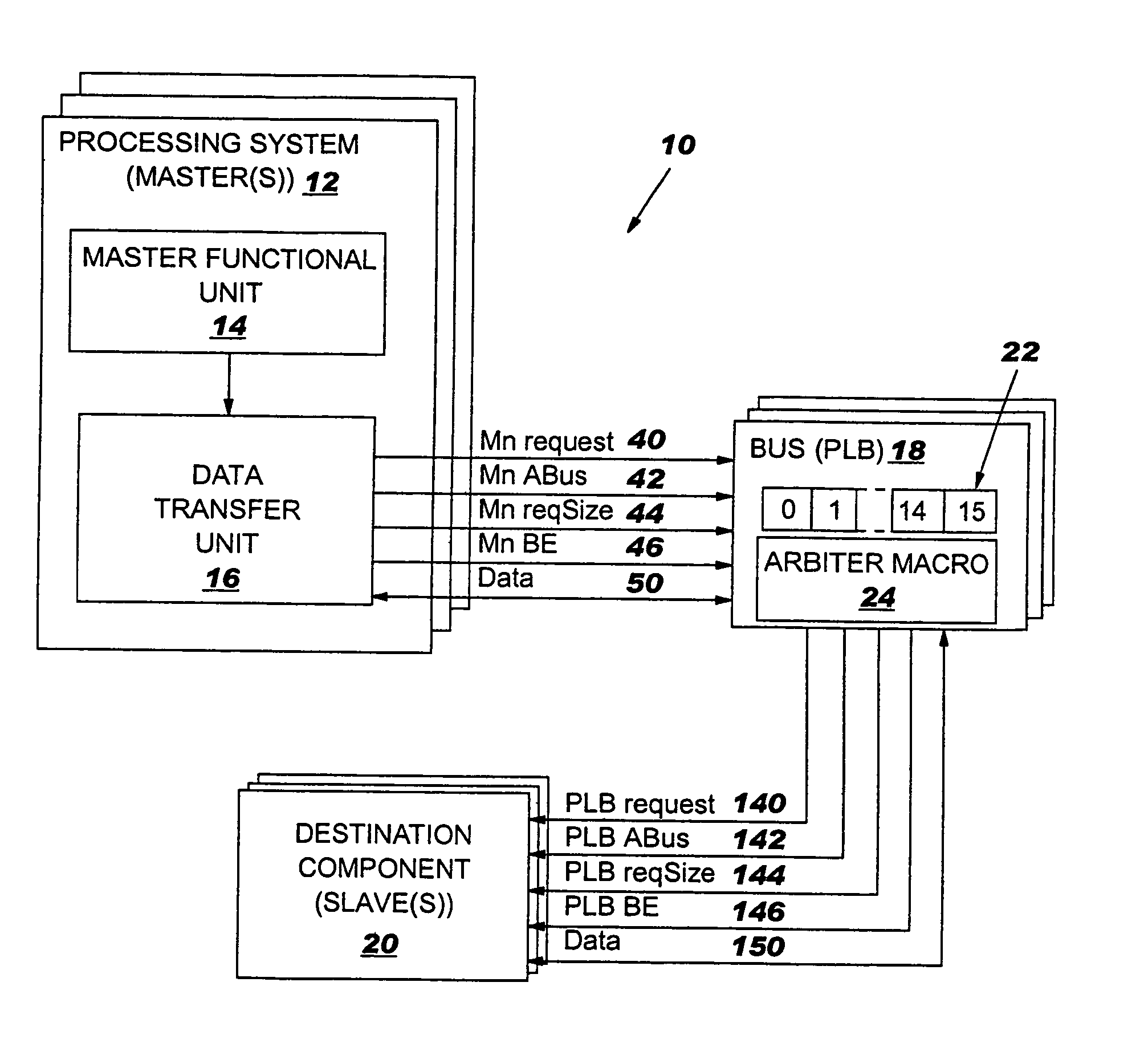

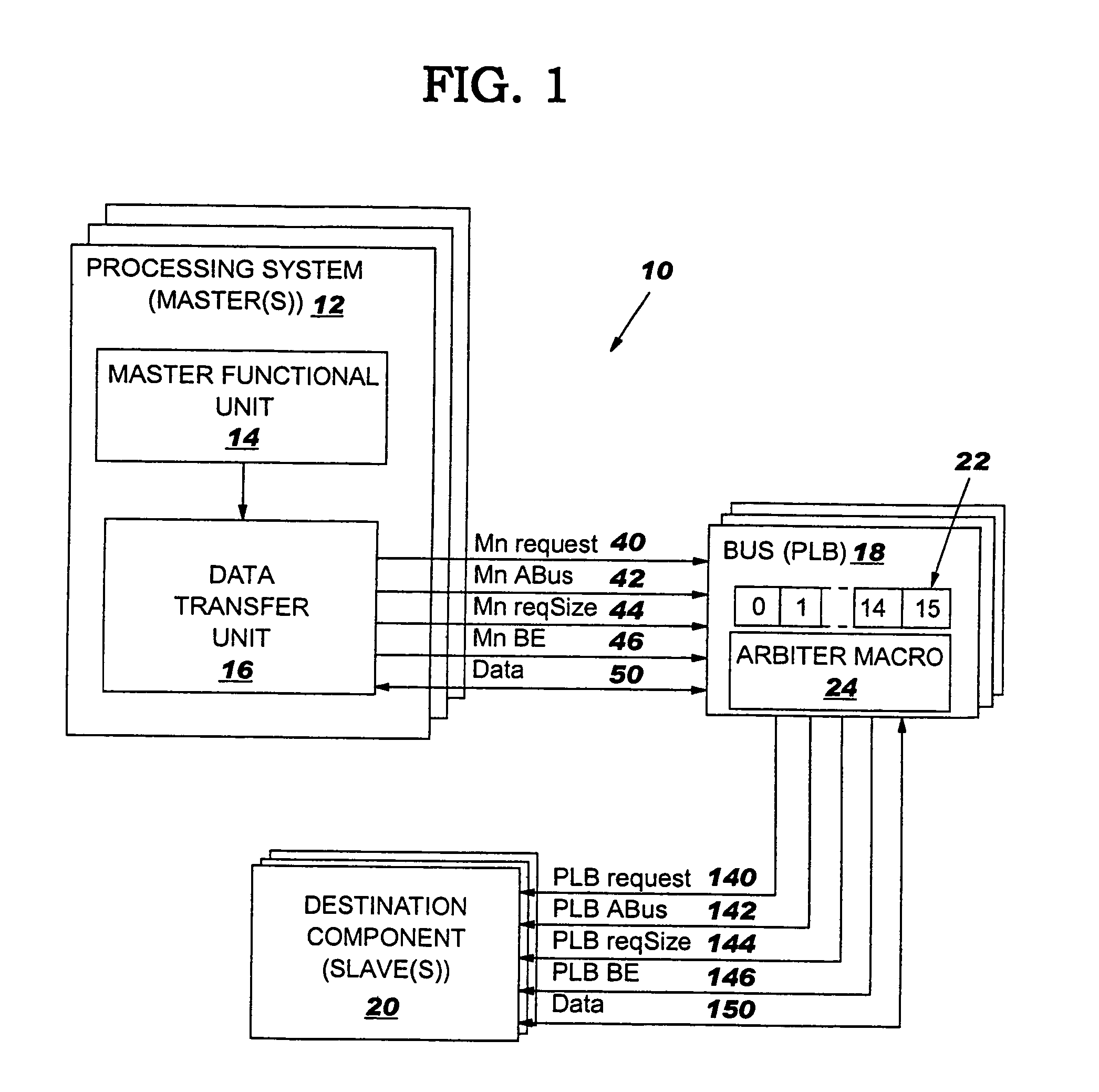

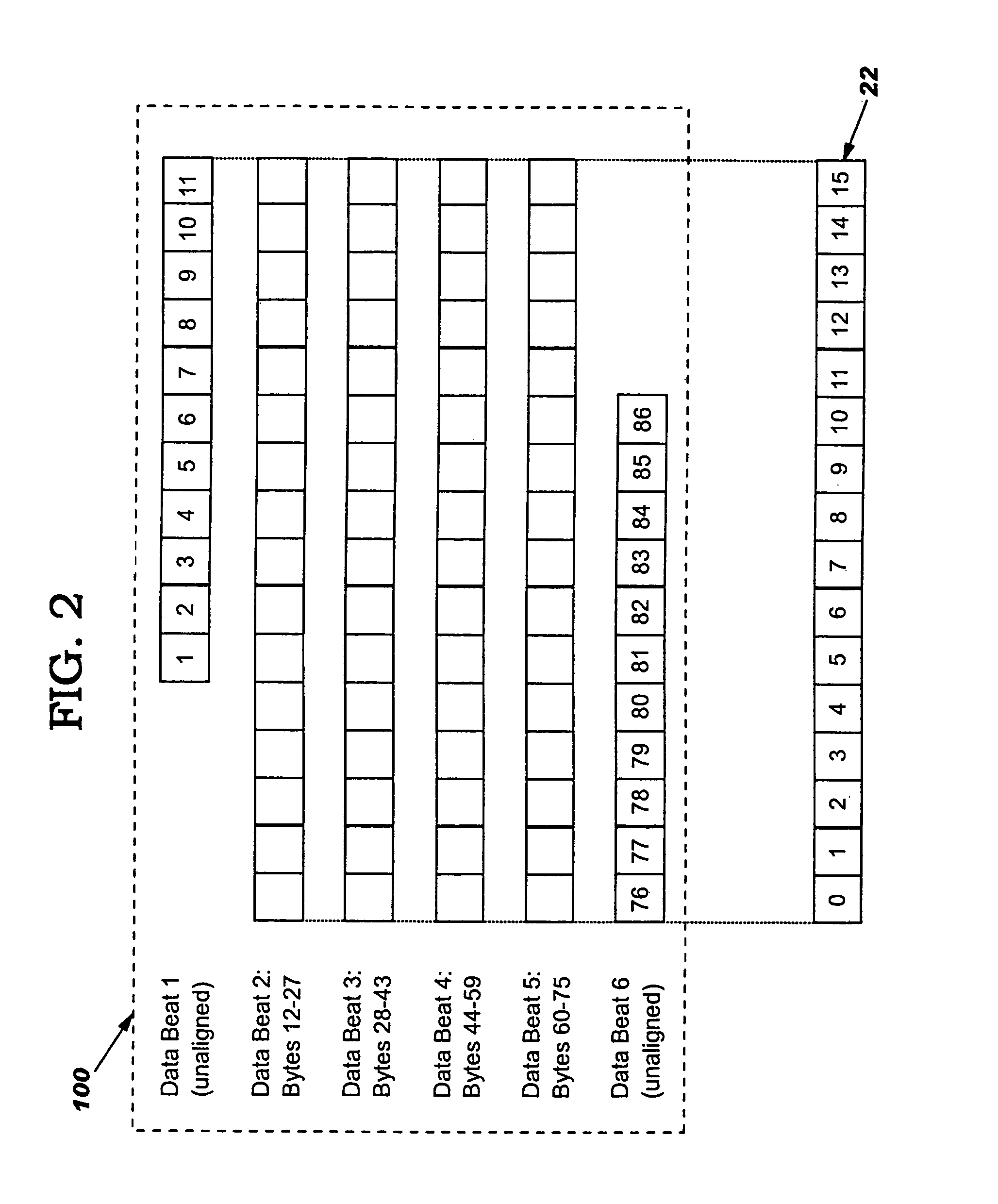

Single request data transfer regardless of size and alignment

InactiveUS7093058B2Reduce amountReduce the amount of dataEnergy efficient ICTData switching by path configurationComputerized systemByte addressing

A method, computer system and set of signals are disclosed allowing for communication of a data transfer, via a bus, between a master and a slave using a single transfer request regardless of transfer size and alignment. The invention provides three transfer qualifier signals including: a first signal including a starting byte address of the data transfer; a second signal including a size of the data transfer in data beats; and a third signal including a byte enable for each byte required during a last data beat of the data transfer. The invention is usable with single or multiple beat, aligned or unaligned data transfers. Usage of the three transfer qualifier signals provides the slave with how many data beats it will transfer at the start of the transfer, and the alignment of both the starting and ending data beats. As a result, the slave need not calculate the number of bytes it will transfer. In terms of multiple beat transfers, the number of data transfer requests are reduced, which reduces the amount of switching, bus arbitration and power consumption required. In addition, the invention allows byte enable signals to be used for subsequent data transfer requests prior to the completion of the initial data transfer, which reduces power consumption and allows for pipelining of data transfer requests.

Owner:INT BUSINESS MASCH CORP

Vehicle driving safety management system

PendingCN105467970AImprove reliabilityImprove efficiencyElectric testing/monitoringSafety management systemsByte addressing

The invention discloses a vehicle driving safety management system, which is characterized in that a vehicle ESP is adopted to store and manage fault codes, the vehicle can perform driving according to an intention of a driver while the driving stability of the vehicle is ensured, the driving safety of the vehicle is greatly improved, the vehicle ESP fault code storage and management are a mode of defining, storing and reading the fault codes by an ESP fault diagnosis system, the ESP defines the fault codes firstly according to a fault type, and each fault code is in one-to-one correspondence with each byte address in a specified storage unit. The system reliability is improved, nonvolatility and historicality of system diagnosis result storage data can be ensured, and the algorithm is simple, high in efficiency and short in operation period.

Owner:XIAN HUIZE INTPROP OPERATIONS MANAGEMENT CO LTD

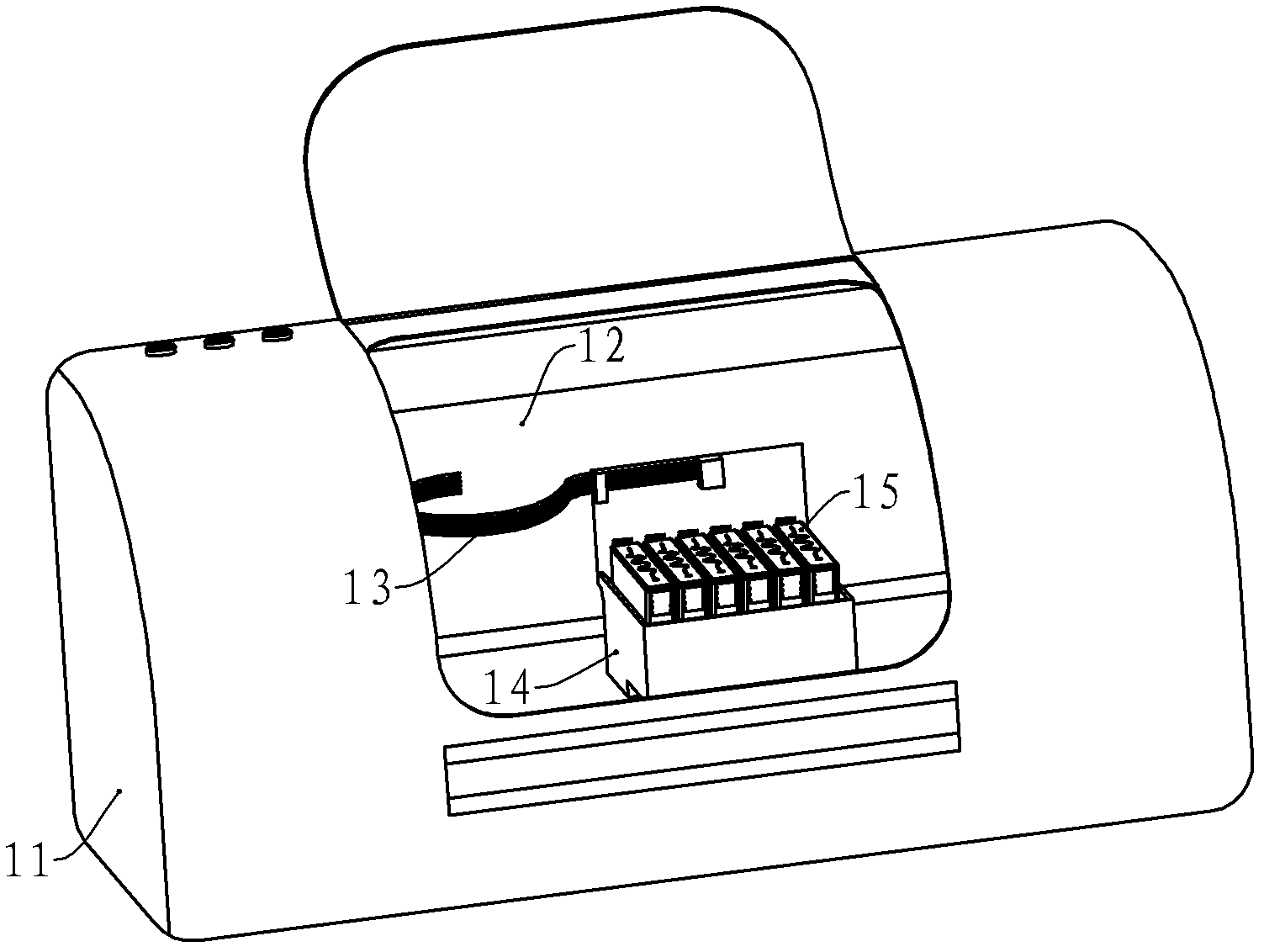

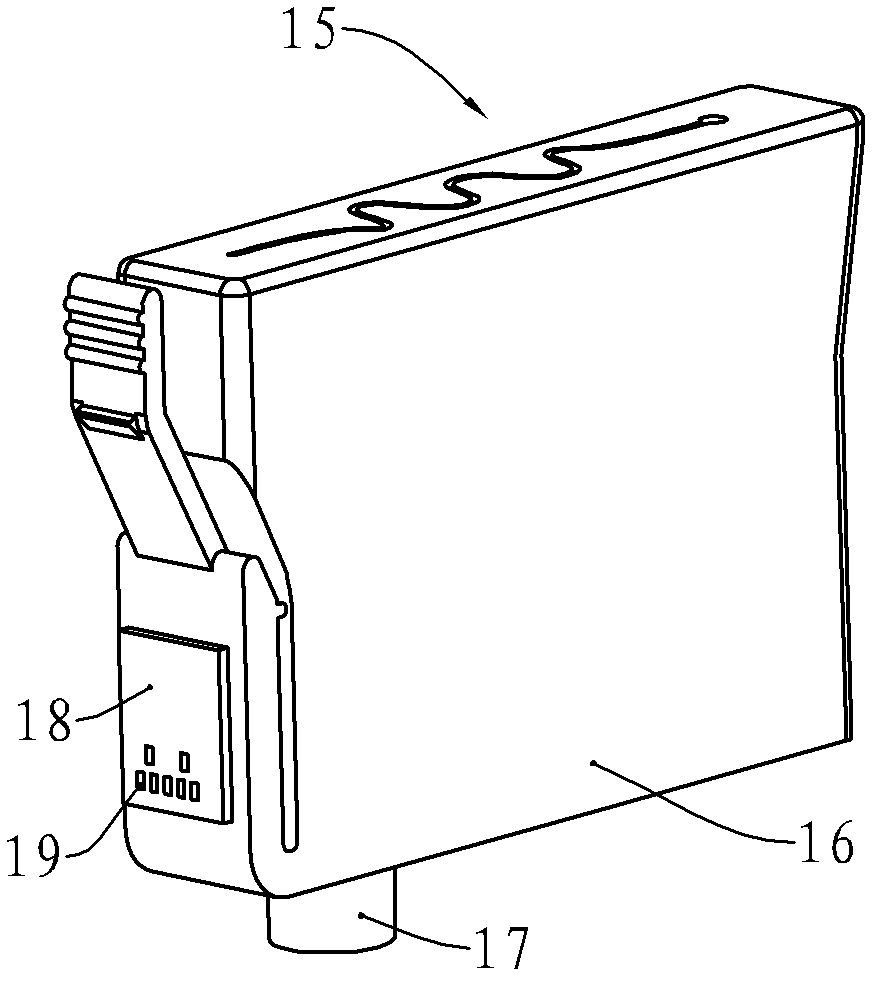

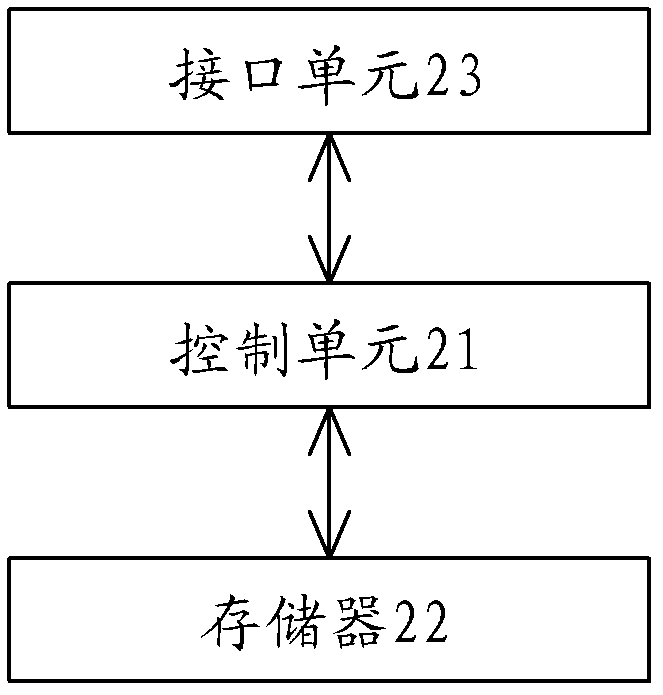

Consumable chip, data writing method thereof and consumable container of consumable chip

InactiveCN103129150AIncrease write speedPrevent lossElectrographic process apparatusPrintingCode moduleData needs

The invention provides a consumable chip, a data writing method of the consumable chip and a consumable container of the consumable chip. An interface unit, a control unit and a nonvolatile memory are arranged on an electronic module of the chip. The nonvolatile memory is divided into more than two pages of memory intervals, wherein each page of memory intervals are provided with a plurality of memory bytes. A read-write control circuit is arranged inside the control unit, and is provided with an address coding module which is used for receiving address information and coding the address information to form memory byte address information in one page of memory intervals. A data latching device provided with a plurality of data registers is provided with a plurality of state register groups of state registers, wherein the number of the state register groups is equal to the number of the data registers. The control unit is provided with a read-write controller for receiving data needing to be written into the nonvolatile memory and for writing the received data into the data registers. According to the data writing method, the received data is written into the data latching device, and after all data is received, the received data is written into the nonvolatile memory. By means of the data writing method, read-in data speed of the nonvolatile memory of the consumable chip can be improved.

Owner:ZHUHAI TIANWEI TECH DEV CO LTD

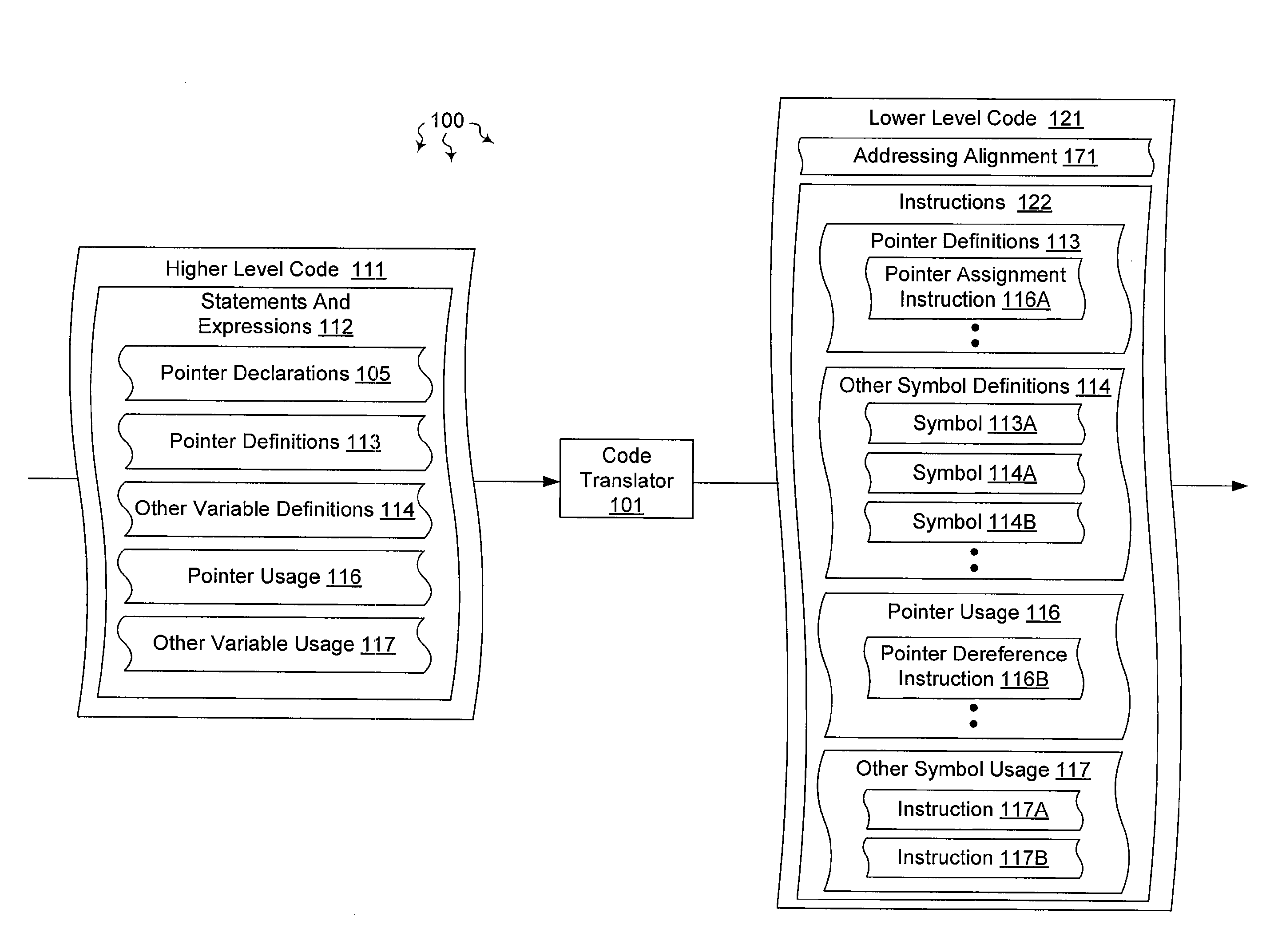

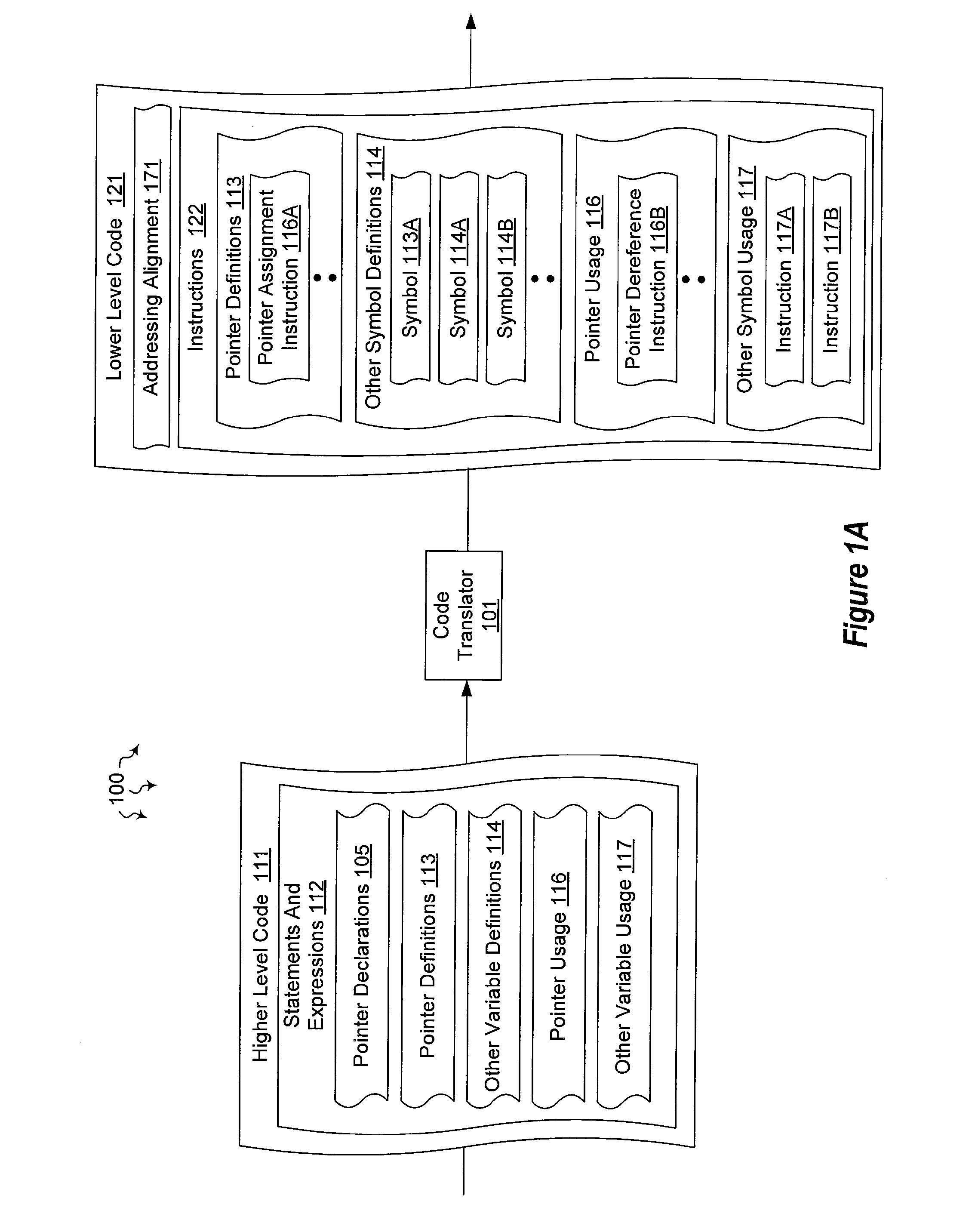

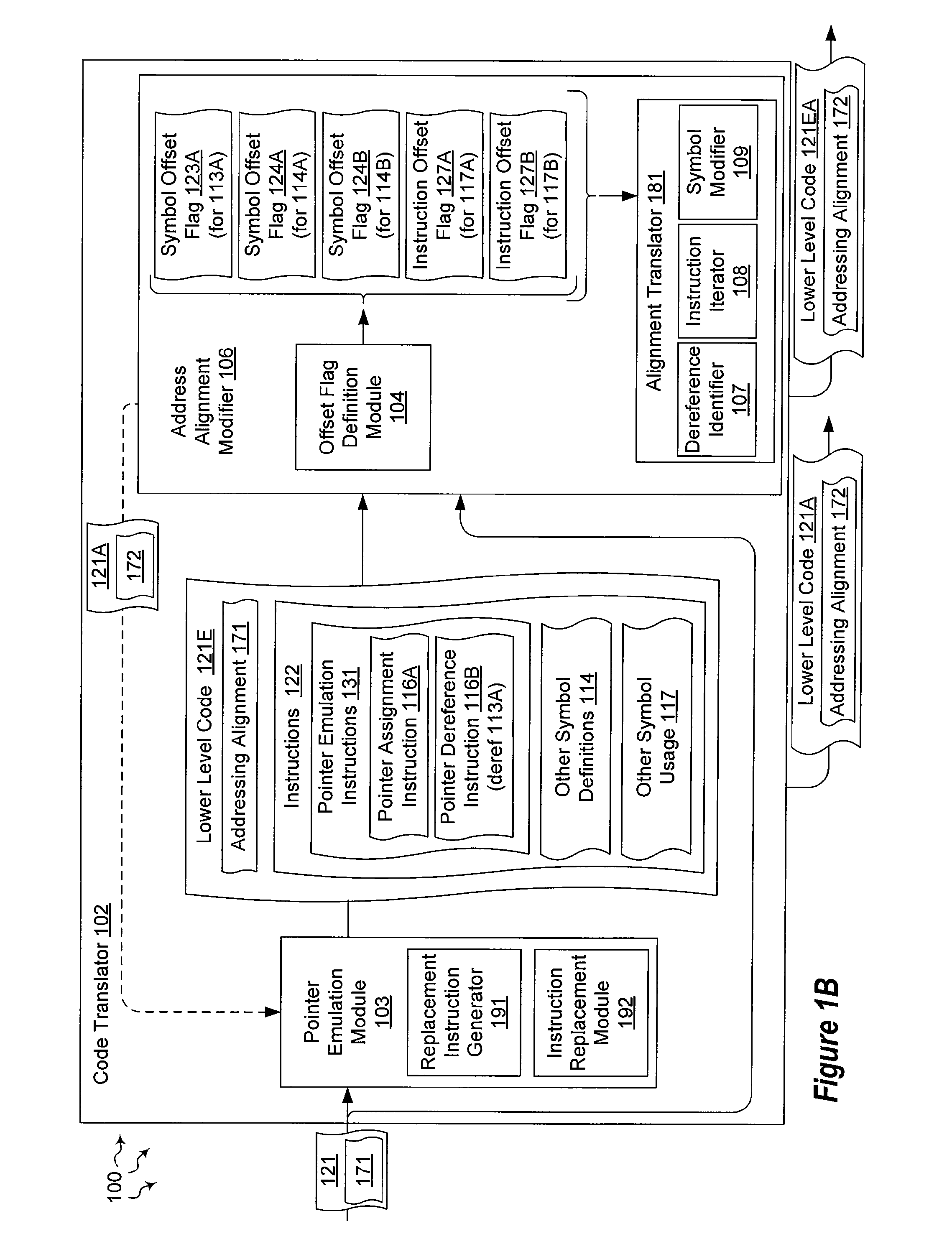

Transforming addressing alignment during code generation

ActiveUS20120317394A1Digital computer detailsSpecific program execution arrangementsByte addressingByte

The present invention extends to methods, systems, and computer program products for changing addressing mode during code generation. Generally, embodiments of the invention use a compiler transformation to transform lower level code from one address alignment to another address alignment. The transformation can be based upon assumptions of a source programming language. Based on the assumptions, the transformation can eliminate arithmetic operations that compensate for different addressing alignment, resulting in more efficient code. Some particular embodiments use a compiler transformation to transform an Intermediate Representation (“IR”) from one-byte addressing alignment into multi-byte (e.g., four-byte) addressing alignment.

Owner:MICROSOFT TECH LICENSING LLC

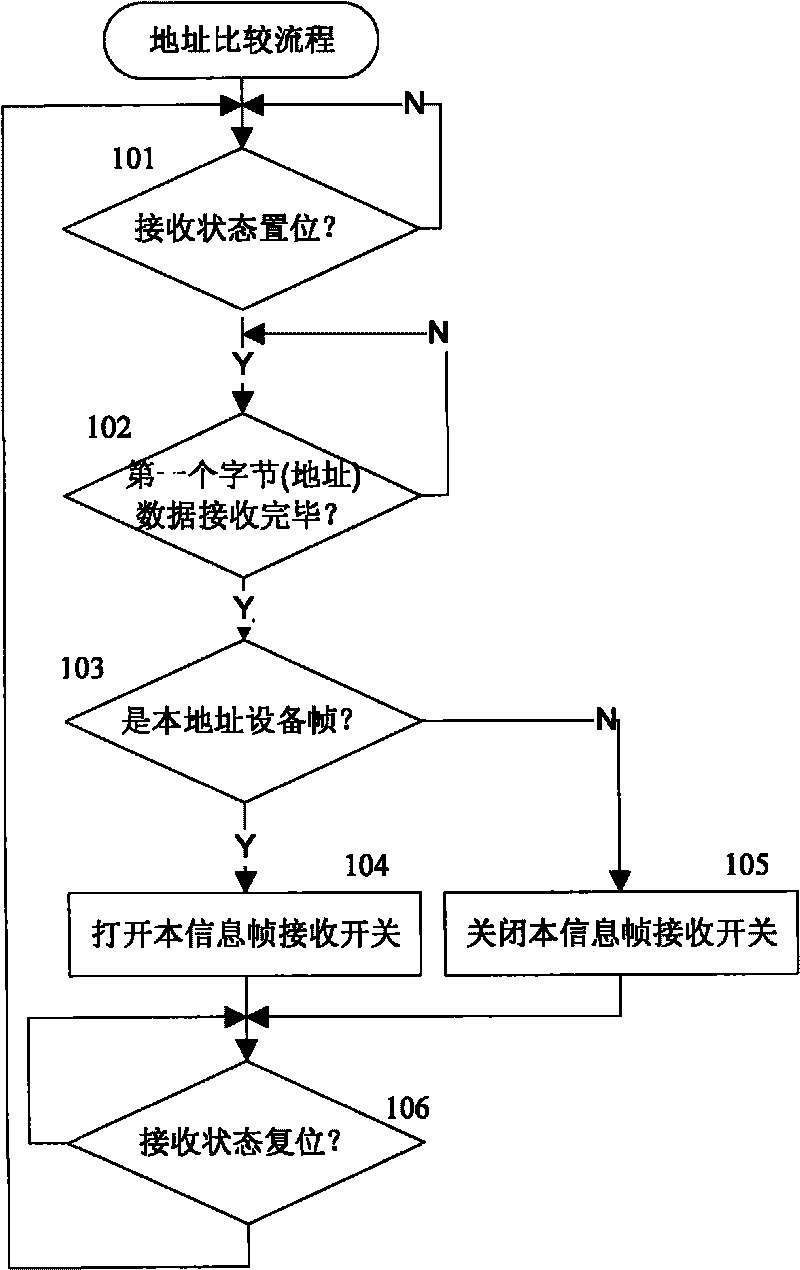

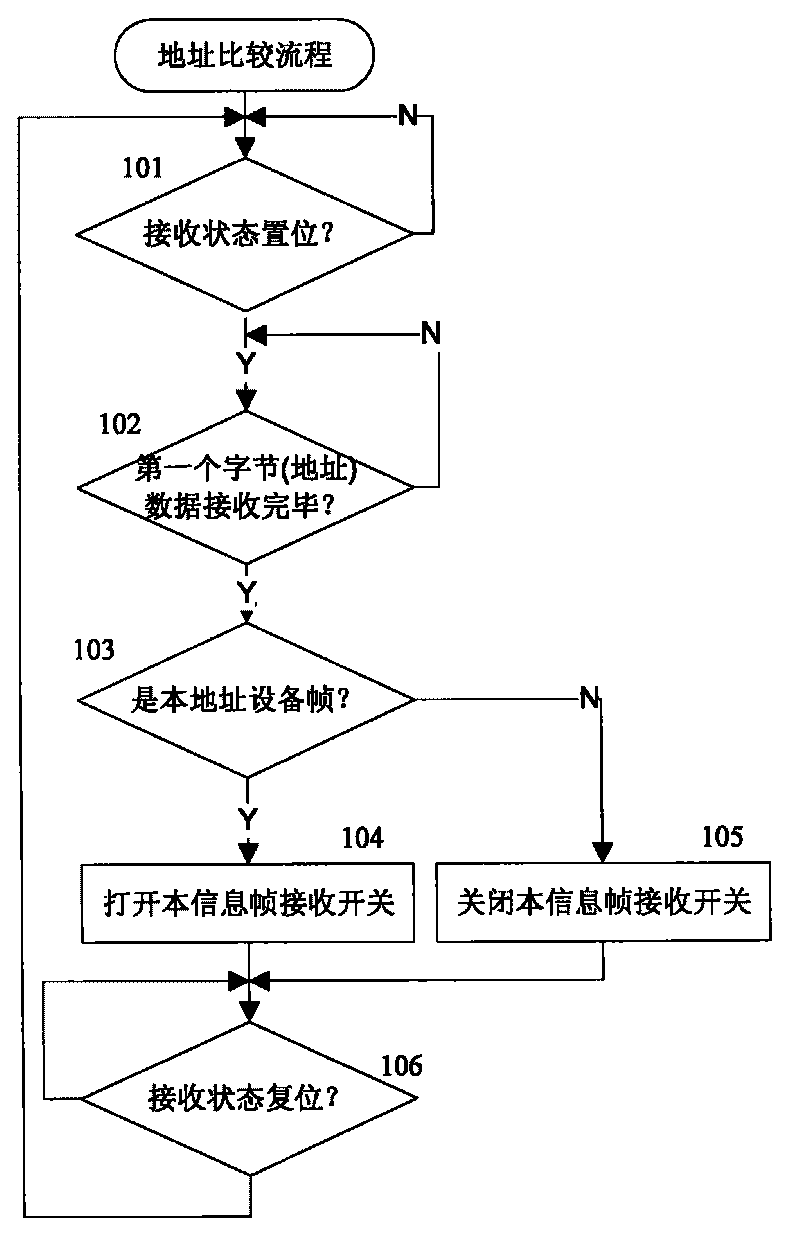

Method for identifying frame address in asynchronous communication control

InactiveCN101764792ARealize automatic identificationRealize automatic identification functionTransmissionModbusAsynchronous communication

The invention relates to the field of asynchronous communication of a universal asynchronous receiver / transmitter (URAT), in particular to a method for identifying a frame address in asynchronous communication control, comprising the following steps of: first receiving the first byte of an information frame by using the first byte of the information frame as address information; and receiving the information frame when judging whether the address information is as same as the address information of a computer or not. Through adopting the method, when the first byte of the transmitted information frame is the address, the automatic identification of the frame address can be realized. The information frame is received when the address of the information frame is as same as the address of the computer, the finish breakage is automatically generated after the reception of the information frame is finished, and then a Central Processing Unit (CPU) is notified that the reception of the information frame of the equipment is finished. In the communication (such as MODBUS-radio teletypewriter communication (RTC)) adopting the time to judge whether the frame is finished or not, a timer need not to be arranged in the CPU to judge whether the reception of the information frame is finished overtime or not so that the automatic identification function and the frame finish breakage control of eight-byte address hardware are realized, the URAT has good universality, and meanwhile, the running efficiency of the CPU is greatly enhanced.

Owner:CHONGQING CHUANYI AUTOMATION

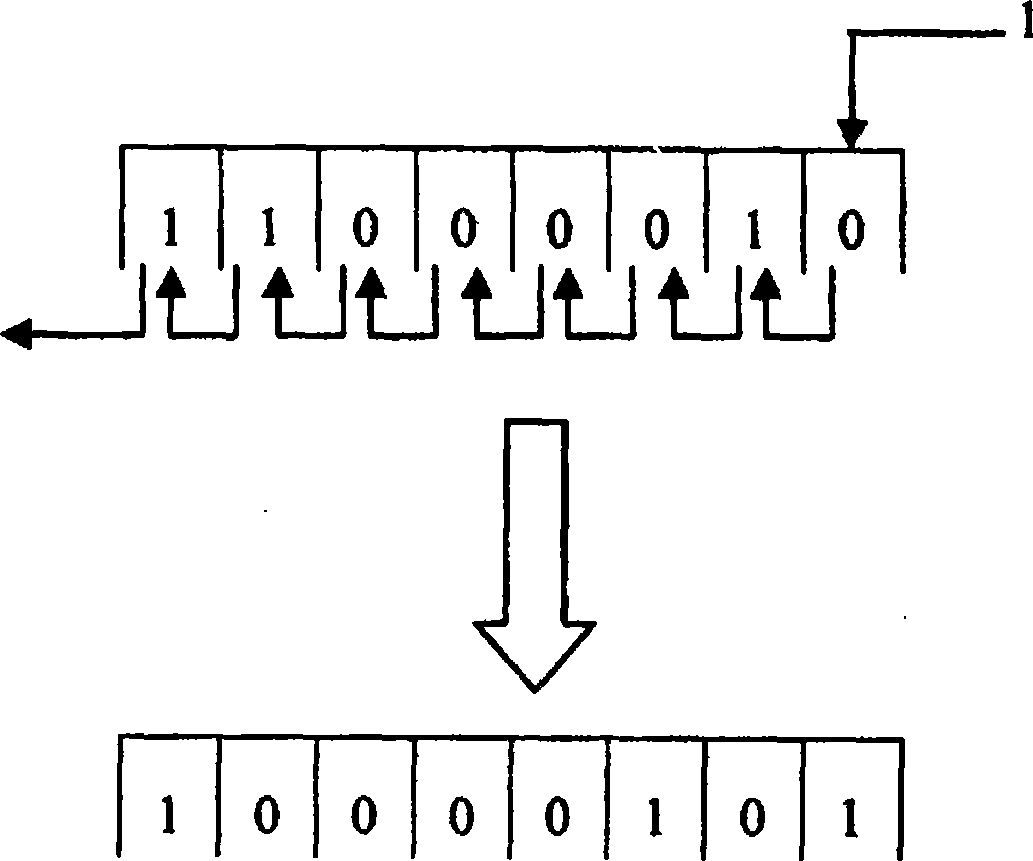

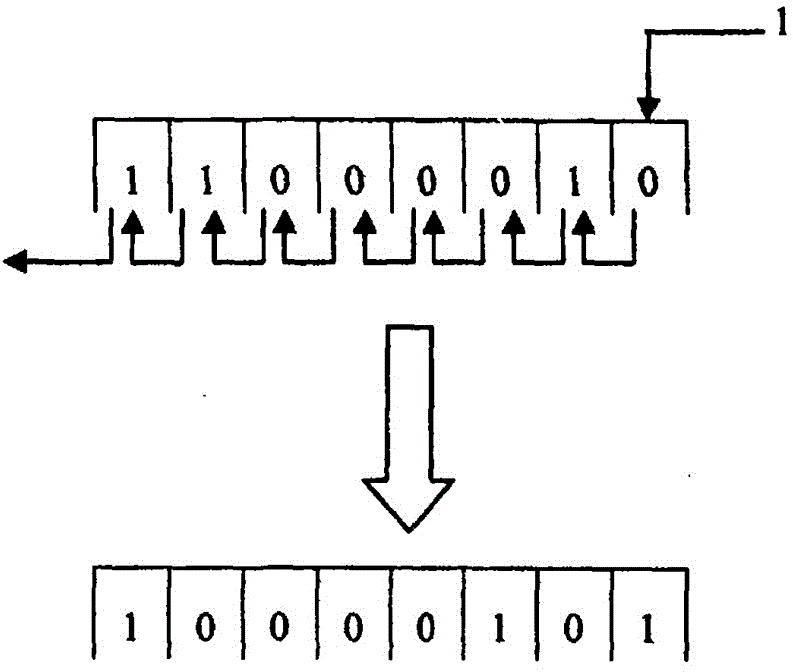

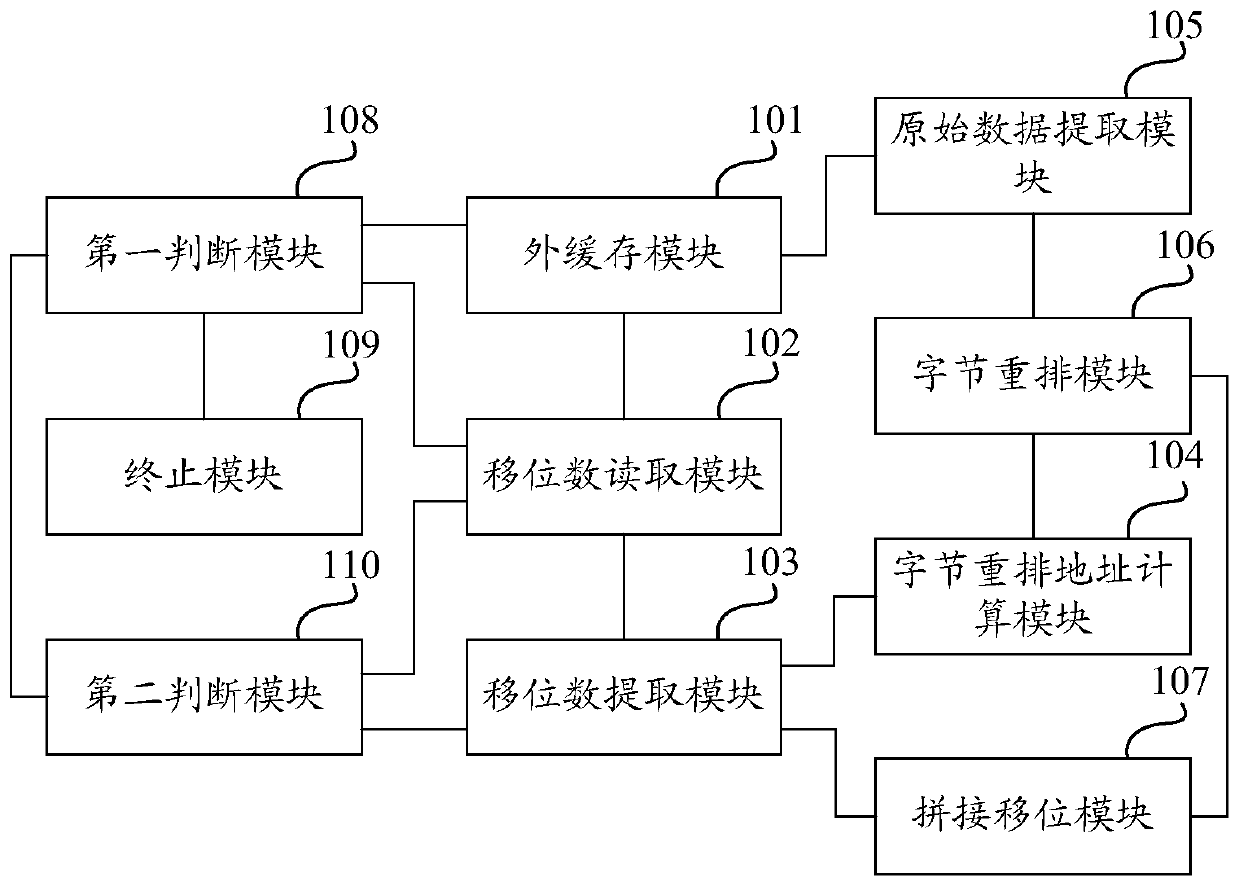

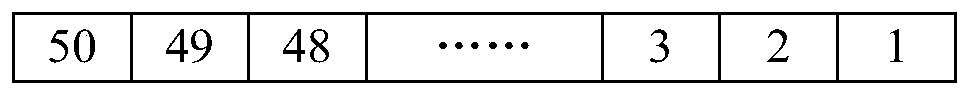

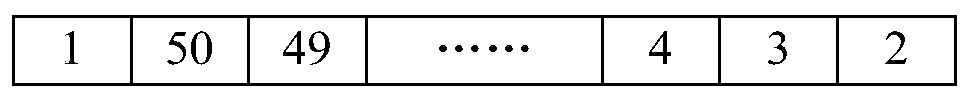

Cyclic shift processing device and method

ActiveCN109756231ASmall amount of calculationImprove processing efficiencyError correction/detection using multiple parity bitsByte addressingCyclic shift

The invention discloses a cyclic shift processing device and method, a byte rearrangement address calculation module in the device calculates a high 8-bit byte address and a low 8-bit byte address corresponding to data required by each byte in a cyclic shift result in original data according to a first part of an extracted shift number; The byte rearrangement module is used for carrying out byte rearrangement on the extracted original data according to the high 8-bit byte address and the low 8-bit byte address respectively to obtain high 8-bit byte data and low 8-bit byte data required by eachbyte; The splicing shifting module is used for splicing the high 8-bit byte data and the low 8-bit byte data required by each byte in parallel to obtain splicing data corresponding to each byte; Andaccording to the extracted second part of the shift number, performing shift processing on the spliced data corresponding to all bytes to obtain a cyclic shift result. According to the scheme, bit-level cyclic shift is achieved, and long data can be subjected to cyclic shift processing conveniently and quickly.

Owner:上海思朗科技有限公司

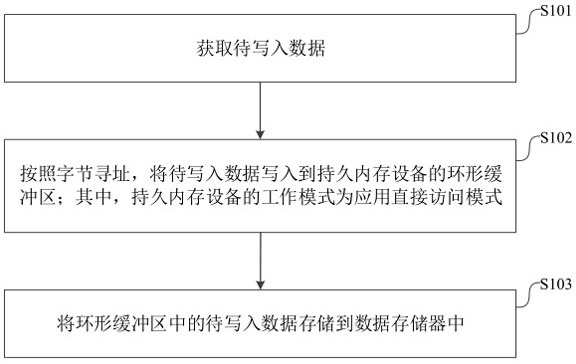

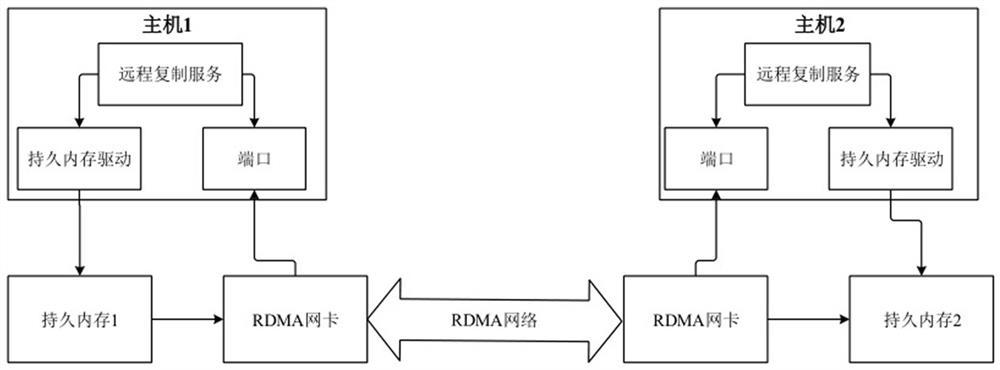

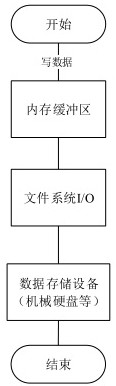

Data writing method, device and system, electronic equipment and storage medium

InactiveCN113360098AIncrease write speedReduce the possibility of lossInput/output to record carriersMemory adressing/allocation/relocationByte addressingData memory

The invention discloses a data writing method, device and system, electronic equipment and a computer readable storage medium. The method comprises the steps of obtaining to-be-written data; according to byte addressing, writing the to-be-written data into an annular buffer area of the persistent memory equipment, wherein the working mode of the persistent memory device is an application direct access mode; storing the to-be-written data in the annular buffer area into a data memory. According to the invention, addressing is carried out according to bytes, the to-be-written data is written into the annular buffer area of the persistent memory device, and the writing speed and bandwidth which are provided by the persistent memory device and are several times that of a traditional data memory are utilized, so that the writing speed of the data is improved, and the possibility of data loss during a fault is reduced; and the to-be-written data is transferred and stored by using the annular buffer area in the persistent memory equipment, so that the to-be-written data can be continuously written, and the technical use cost is reduced while the data persistence speed is increased.

Owner:SUZHOU LANGCHAO INTELLIGENT TECH CO LTD