PCI express tlp processing circuit and relay device provided with this

a relay device and processing circuit technology, applied in the field of pci express devices, can solve the problem that errors cannot be detected at the reception destination of tlps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

embodiment

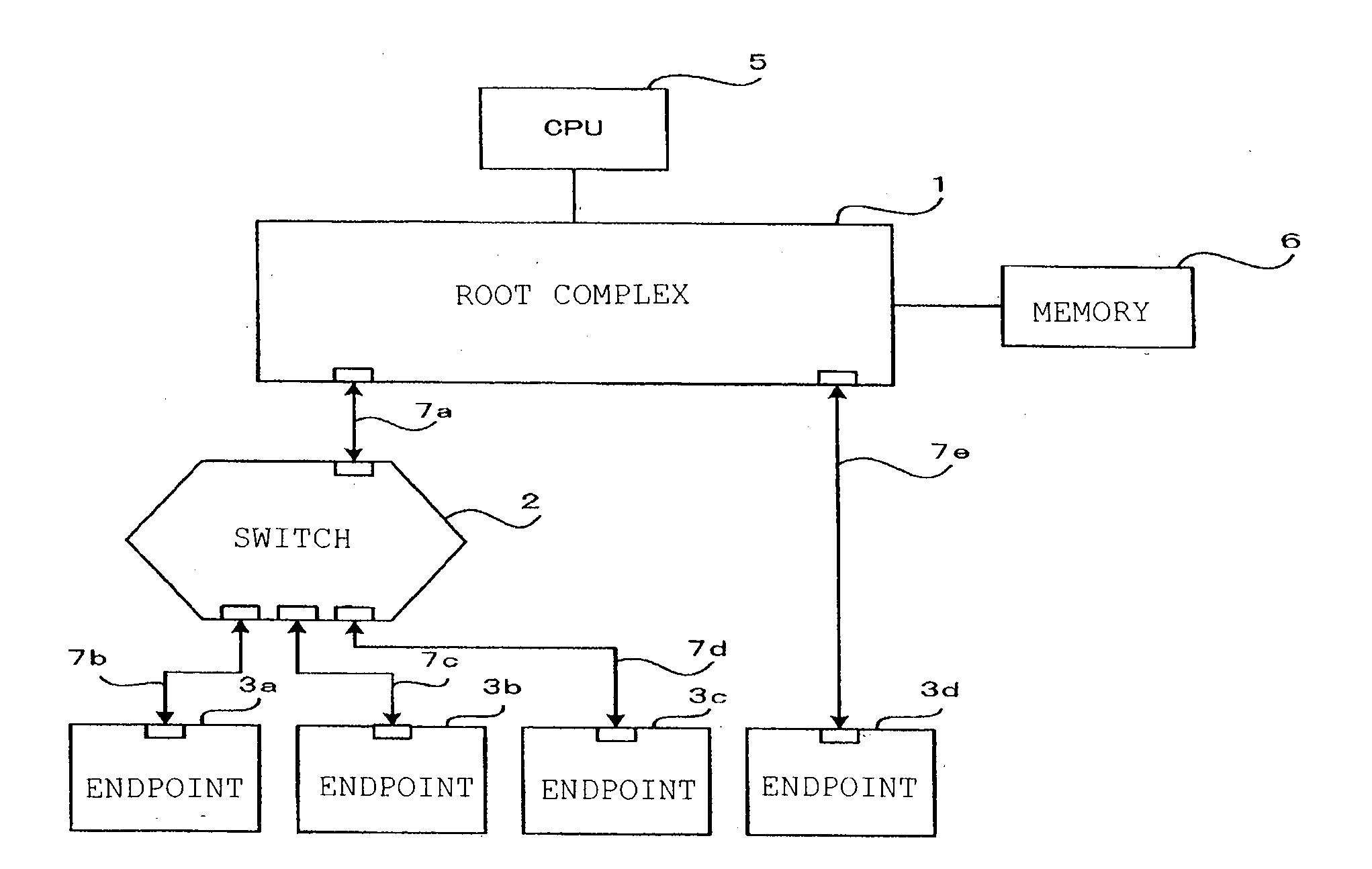

[0061]An embodiment of the present invention will now be described with reference to FIG. 4. FIG. 4 is a layout diagram of a TLP processing circuit of data transmitted in an upstream direction to the root complex 1 from endpoints 3a to 3c via a switch 2a constituting a relay device of a PCI Express system according to the present invention. The TLP processing circuit 10 in the downstream direction is the same in construction as that of FIG. 1, so a description thereof is omitted.

[0062]A switch 2a is provided between a root complex 1 and a plurality of endpoints 3a to 3c; the path of the root complex 1 and endpoint 3a (or 3b, 3c) is set beforehand by the PCI Express configuration software.

[0063]Also, on the link between the root complex 1 and the switch 2a and the link between the switch 2a and the endpoint 3a (or 3b, 3c), delivery confirmation and flow control are separately performed.

[0064]This flow control is not the subject of the gist of the present invention, so a description t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More